# E·XFL

### NXP USA Inc. - MSC7112VM800 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                             |

|-------------------------|----------------------------------------------------------------------|

| Туре                    | SC1400 Core                                                          |

| Interface               | Host Interface, I <sup>2</sup> C, UART                               |

| Clock Rate              | 200MHz                                                               |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 208kB                                                                |

| Voltage - I/O           | 3.30V                                                                |

| Voltage - Core          | 1.20V                                                                |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                   |

| Mounting Type           | Surface Mount                                                        |

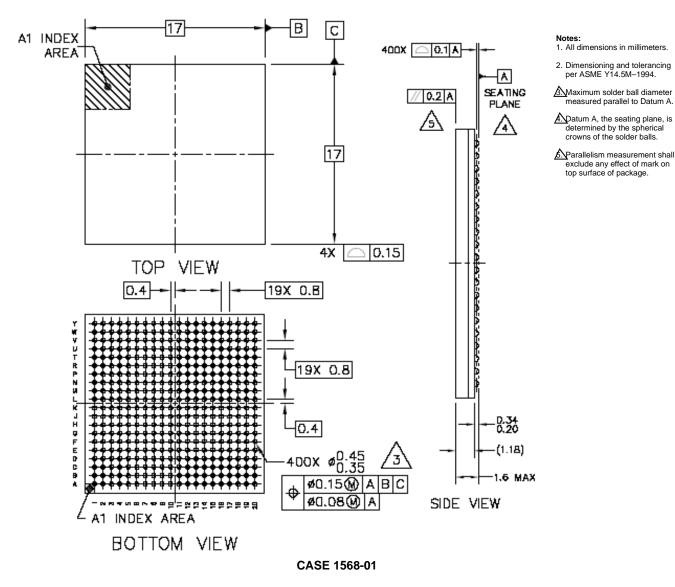

| Package / Case          | 400-LFBGA                                                            |

| Supplier Device Package | 400-LFBGA (17x17)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc7112vm800 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | 1 Pin Assignments |                                      |  |  |  |  |  |

|---|-------------------|--------------------------------------|--|--|--|--|--|

|   | 1.1               | MAP-BGA Ball Layout Diagrams         |  |  |  |  |  |

|   | 1.2               | Signal List By Ball Location         |  |  |  |  |  |

| 2 | Spec              | ifications                           |  |  |  |  |  |

|   | 2.1               | Maximum Ratings                      |  |  |  |  |  |

|   | 2.2               | Recommended Operating Conditions     |  |  |  |  |  |

|   | 2.3               | Thermal Characteristics              |  |  |  |  |  |

|   | 2.4               | DC Electrical Characteristics        |  |  |  |  |  |

|   | 2.5               | AC Timings                           |  |  |  |  |  |

| 3 | Hard              | ware Design Considerations           |  |  |  |  |  |

|   | 3.1               | Thermal Design Considerations        |  |  |  |  |  |

|   | 3.2               | Power Supply Design Considerations   |  |  |  |  |  |

|   | 3.3               | Estimated Power Usage Calculations46 |  |  |  |  |  |

|   | 3.4               | Reset and Boot48                     |  |  |  |  |  |

|   | 3.5               | DDR Memory System Guidelines         |  |  |  |  |  |

| 4 | Order             | ring Information                     |  |  |  |  |  |

| 5 | Packa             | age Information                      |  |  |  |  |  |

| 6 | Produ             | uct Documentation                    |  |  |  |  |  |

| 7 | Revis             | sion History                         |  |  |  |  |  |

|   |                   | Figures                              |  |  |  |  |  |

| MSC7112 Block Diagram                             |

|---------------------------------------------------|

| MSC7112 Molded Array Process-Ball Grid Array      |

| (MAP-BGA), Top View                               |

| MSC7112 Molded Array Process-Ball Grid Array      |

| (MAP-BGA), Bottom View                            |

| Timing Diagram for a Reset Configuration Write 24 |

| DDR DRAM Input Timing Diagram 24                  |

|                                                   |

| Figure 6.  | DDR DRAM Output Timing Diagram                 |

|------------|------------------------------------------------|

| Figure 7.  | DDR DRAM AC Test Load                          |

| Figure 8.  | TDM Receive Signals                            |

| Figure 9.  | TDM Transmit Signals                           |

| Figure 10. | Read Timing Diagram, Single Data Strobe 29     |

| Figure 11. | Read Timing Diagram, Double Data Strobe        |

| Figure 12. | Write Timing Diagram, Single Data Strobe       |

| Figure 13. | Write Timing Diagram, Double Data Strobe       |

| Figure 14. | Host DMA Read Timing Diagram, HPCR[OAD] = 031  |

| Figure 15. | Host DMA Write Timing Diagram, HPCR[OAD] = 032 |

| Figure 16. | I2C Timing Diagram                             |

| Figure 17. | UART Input Timing                              |

| Figure 18. | UART Output Timing                             |

| Figure 19. | EE Pin Timing                                  |

| Figure 20. | EVNT Pin Timing                                |

| Figure 21. | GPI/GPO Pin Timing                             |

| Figure 22. | Test Clock Input Timing Diagram                |

| Figure 23. | Boundary Scan (JTAG) Timing Diagram            |

| Figure 24. | Test Access Port Timing Diagram                |

| Figure 25. | TRST Timing Diagram                            |

| Figure 26. | Voltage Sequencing Case 1 40                   |

| Figure 27. | Voltage Sequencing Case 2 41                   |

| Figure 28. | Voltage Sequencing Case 3 42                   |

| Figure 29. | Voltage Sequencing Case 4                      |

| Figure 30. | Voltage Sequencing Case 5 44                   |

| Figure 31. | PLL Power Supply Filter Circuits               |

| Figure 32. | SSTL Termination Techniques 50                 |

| Figure 33. | SSTL Power Value                               |

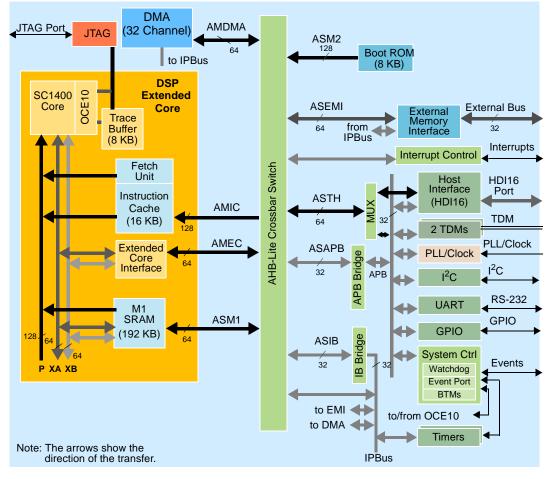

Figure 1. MSC7112 Block Diagram

# 1.2 Signal List By Ball Location

Table 1 lists the signals sorted by ball number and configuration.

Table 1. MSC7112 Signals by Ball Designator

|             | Signal Names     |                          |                      |             |            |           |  |  |  |

|-------------|------------------|--------------------------|----------------------|-------------|------------|-----------|--|--|--|

| Number      |                  | S                        | ed                   | Hardware    | Controlled |           |  |  |  |

|             | End of Reset     | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary    | Alternate |  |  |  |

| A1          |                  |                          | G                    | ND          |            |           |  |  |  |

| A2          |                  |                          | G                    | ND          |            |           |  |  |  |

| A3          |                  |                          | DC                   | QM1         |            |           |  |  |  |

| A4          |                  |                          | DC                   | QS2         |            |           |  |  |  |

| A5          |                  |                          | C                    | к           |            |           |  |  |  |

| A6          |                  |                          | C                    | Ж           |            |           |  |  |  |

| A7          |                  | GPIC7                    |                      | GPOC7       | Н          | D15       |  |  |  |

| A8          |                  | GPIC4                    |                      | GPOC4       | Н          | D12       |  |  |  |

| A9          |                  | GPIC2                    |                      | GPOC2       | Н          | D10       |  |  |  |

| A10         |                  | rese                     | rved                 |             | F          | ID7       |  |  |  |

| A11         |                  | rese                     | rved                 |             | F          | ID6       |  |  |  |

| A12         |                  | rese                     | rved                 |             | F          | ID4       |  |  |  |

| A13         |                  | rese                     | rved                 |             | F          | ID1       |  |  |  |

| A14         |                  | rese                     | rved                 |             | HD0        |           |  |  |  |

| A15         |                  |                          | G                    | ND          |            |           |  |  |  |

| A16 (1L44X) |                  |                          | Ν                    | IC          |            |           |  |  |  |

| A16 (1M88B) | BM3              | GP                       | ID8                  | GPOD7       | res        | erved     |  |  |  |

| A17         |                  |                          | Ν                    | IC          |            |           |  |  |  |

| A18         |                  |                          | Ν                    | IC          |            |           |  |  |  |

| A19         |                  |                          |                      | IC          |            |           |  |  |  |

| A20         |                  |                          |                      | IC          |            |           |  |  |  |

| B1          |                  |                          |                      | DDM         |            |           |  |  |  |

| B2          |                  |                          |                      | IC          |            |           |  |  |  |

| B3          |                  |                          |                      | <u>S0</u>   |            |           |  |  |  |

| B4          |                  | DQM2                     |                      |             |            |           |  |  |  |

| B5          | DQS3             |                          |                      |             |            |           |  |  |  |

| B6          | DQS0             |                          |                      |             |            |           |  |  |  |

| B7          | CKE              |                          |                      |             |            |           |  |  |  |

| B8          |                  | WE                       |                      |             |            |           |  |  |  |

| B9          | GPIC6 GPOC6 HD14 |                          |                      |             |            |           |  |  |  |

| B10         | GPIC3 GPOC3      |                          |                      |             |            | D11       |  |  |  |

| B11         |                  | GPIC0                    |                      | ID8         |            |           |  |  |  |

| B12         |                  |                          | rved                 | GPOC0       |            | ID5       |  |  |  |

| B13         |                  |                          | rved                 |             |            | ID2       |  |  |  |

| B14         |                  |                          |                      | IC          |            |           |  |  |  |

| B15 (1L44X) |                  |                          |                      | IC          |            |           |  |  |  |

|        | Signal Names           |                                       |                      |             |            |           |  |  |  |

|--------|------------------------|---------------------------------------|----------------------|-------------|------------|-----------|--|--|--|

| Number |                        | So                                    | ed                   | Hardware    | Controlled |           |  |  |  |

|        | End of Reset           | GPI Enabled<br>(Default)              | Interrupt<br>Enabled | GPO Enabled | Primary    | Alternate |  |  |  |

| D13    |                        |                                       | VD                   | DIO         |            |           |  |  |  |

| D14    |                        |                                       |                      | DIO         |            |           |  |  |  |

| D15    |                        |                                       |                      | DIO         |            |           |  |  |  |

| D16    |                        |                                       |                      | DIO         |            |           |  |  |  |

| D17    |                        |                                       | V <sub>E</sub>       | DDC         |            |           |  |  |  |

| D18    |                        |                                       | N                    | IC          |            |           |  |  |  |

| D19    |                        |                                       | Ν                    | IC          |            |           |  |  |  |

| D20    |                        |                                       | N                    | IC          |            |           |  |  |  |

| E1     |                        |                                       | GI                   | ND          |            |           |  |  |  |

| E2     |                        |                                       | D                    | 26          |            |           |  |  |  |

| E3     |                        |                                       | D                    | 31          |            |           |  |  |  |

| E4     |                        |                                       | V <sub>D</sub>       | DM          |            |           |  |  |  |

| E5     |                        |                                       |                      | DM          |            |           |  |  |  |

| E6     |                        |                                       |                      | DDC         |            |           |  |  |  |

| E7     |                        |                                       |                      | DDC         |            |           |  |  |  |

| E8     |                        |                                       |                      | DDC         |            |           |  |  |  |

| E9     |                        |                                       |                      | DDC         |            |           |  |  |  |

| E10    |                        |                                       |                      | DDM         |            |           |  |  |  |

| E11    |                        |                                       |                      | DIO         |            |           |  |  |  |

| E12    |                        |                                       |                      | DIO         |            |           |  |  |  |

| E13    |                        |                                       |                      | DIO         |            |           |  |  |  |

| E14    |                        |                                       |                      | DIO         |            |           |  |  |  |

| E15    |                        |                                       |                      |             |            |           |  |  |  |

| E16    |                        | V <sub>DDIO</sub><br>V <sub>DDC</sub> |                      |             |            |           |  |  |  |

| E17    |                        |                                       |                      |             |            |           |  |  |  |

| E18    | V <sub>DDC</sub><br>NC |                                       |                      |             |            |           |  |  |  |

| E19    |                        |                                       |                      | IC          |            |           |  |  |  |

| E20    | 1                      | NC                                    |                      |             |            |           |  |  |  |

| F1     |                        |                                       |                      | DM          |            |           |  |  |  |

| F2     |                        |                                       |                      | 15          |            |           |  |  |  |

| F3     |                        |                                       |                      | 29          |            |           |  |  |  |

| F4     |                        |                                       |                      | DDC         |            |           |  |  |  |

| F5     |                        |                                       |                      | DDC         |            |           |  |  |  |

| F6     |                        |                                       |                      | DDC         |            |           |  |  |  |

| F7     |                        | GND                                   |                      |             |            |           |  |  |  |

| F8     |                        | GND<br>GND                            |                      |             |            |           |  |  |  |

| F9     |                        |                                       |                      | ND          |            |           |  |  |  |

| F10    |                        |                                       |                      | DM          |            |           |  |  |  |

### Table 1. MSC7112 Signals by Ball Designator (continued)

|             | Signal Names |                                |                      |             |           |                     |  |  |  |

|-------------|--------------|--------------------------------|----------------------|-------------|-----------|---------------------|--|--|--|

| Number      |              | Software Controlled            |                      |             |           | Hardware Controlled |  |  |  |

|             | End of Reset | GPI Enabled<br>(Default)       | Interrupt<br>Enabled | GPO Enabled | Primary   | Alternate           |  |  |  |

| H9          |              |                                | GI                   | ND          |           |                     |  |  |  |

| H10         |              |                                | GI                   | ND          |           |                     |  |  |  |

| H11         |              |                                | GI                   | ND          |           |                     |  |  |  |

| H12         |              |                                | GI                   | ND          |           |                     |  |  |  |

| H13         |              |                                | GI                   | ND          |           |                     |  |  |  |

| H14         |              |                                | GI                   | ND          |           |                     |  |  |  |

| H15         |              |                                | V <sub>D</sub>       | DIO         |           |                     |  |  |  |

| H16         |              |                                | V <sub>D</sub>       | DIO         |           |                     |  |  |  |

| H17         |              |                                | VD                   | DC          |           |                     |  |  |  |

| H18         |              |                                | Ν                    | C           |           |                     |  |  |  |

| H19         |              | rese                           | erved                |             | H         | A2                  |  |  |  |

| H20         |              | rese                           | erved                |             | H         | A1                  |  |  |  |

| J1          |              |                                | D                    | 10          |           |                     |  |  |  |

| J2          |              |                                | V <sub>D</sub>       | DM          |           |                     |  |  |  |

| J3          |              |                                | D                    | 99          |           |                     |  |  |  |

| J4          |              |                                | V <sub>D</sub>       | DM          |           |                     |  |  |  |

| J5          |              |                                |                      | DM          |           |                     |  |  |  |

| J6          |              |                                | V <sub>D</sub>       | DM          |           |                     |  |  |  |

| J7          |              |                                | GI                   | ND          |           |                     |  |  |  |

| J8          |              |                                | GI                   | ND          |           |                     |  |  |  |

| J9          |              |                                | GI                   | ND          |           |                     |  |  |  |

| J10         |              |                                | GI                   | ND          |           |                     |  |  |  |

| J11         |              |                                | GI                   | ND          |           |                     |  |  |  |

| J12         |              |                                | GI                   | ND          |           |                     |  |  |  |

| J13         |              |                                | GI                   | ND          |           |                     |  |  |  |

| J14         |              | GND                            |                      |             |           |                     |  |  |  |

| J15         |              | GND                            |                      |             |           |                     |  |  |  |

| J16         |              | V <sub>DDIO</sub>              |                      |             |           |                     |  |  |  |

| J17         |              |                                | VD                   | DC          |           |                     |  |  |  |

| J18 (1L44X) |              | rese                           | erved                |             | н.        | A3                  |  |  |  |

| J18 (1M88B) |              | GPIC11                         |                      | GPOC11      | H         | A3                  |  |  |  |

| J19         |              | reserved HACK/HACK or HRRQ/HRF |                      |             |           | or HRRQ/HRRQ        |  |  |  |

| J20         | HDSP         |                                | reserved             |             | HREQ/HREQ | or HTRQ/HTRQ        |  |  |  |

| K1          |              | D0                             |                      |             |           |                     |  |  |  |

| K2          |              | GND                            |                      |             |           |                     |  |  |  |

| K3          |              |                                | D                    | 08          |           |                     |  |  |  |

| K4          |              |                                | VD                   | DC          |           |                     |  |  |  |

| K5          |              |                                | V <sub>D</sub>       | DM          |           |                     |  |  |  |

### Table 1. MSC7112 Signals by Ball Designator (continued)

|             | Signal Names |                          |                      |             |          |            |  |  |

|-------------|--------------|--------------------------|----------------------|-------------|----------|------------|--|--|

| Number      |              | S                        | oftware Controlle    | ed          | Hardware | Controlled |  |  |

|             | End of Reset | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |

| K6          |              |                          | GI                   | ND          |          |            |  |  |

| K7          |              |                          | GI                   | ND          |          |            |  |  |

| K8          |              |                          | GI                   | ND          |          |            |  |  |

| K9          |              |                          | GI                   | ND          |          |            |  |  |

| K10         |              |                          | GI                   | ND          |          |            |  |  |

| K11         |              |                          | GI                   | ND          |          |            |  |  |

| K12         |              |                          | GI                   | ND          |          |            |  |  |

| K13         |              |                          | GI                   | ND          |          |            |  |  |

| K14         |              |                          | GI                   | ND          |          |            |  |  |

| K15         |              |                          | VD                   | DIO         |          |            |  |  |

| K16         |              |                          | V <sub>D</sub>       | DIO         |          |            |  |  |

| K17         |              |                          | V                    | DC          |          |            |  |  |

| K18         |              | rese                     | erved                |             | F        | 1A0        |  |  |

| K19         |              | rese                     | erved                |             | Н        | DDS        |  |  |

| K20         |              | rese                     | erved                |             | HDS/HDS  | or HWR/HWR |  |  |

| L1          |              |                          | C                    | 01          |          |            |  |  |

| L2          |              |                          | GI                   | ND          |          |            |  |  |

| L3          |              |                          | C                    | 03          |          |            |  |  |

| L4          |              |                          | V                    | DC          |          |            |  |  |

| L5          |              |                          |                      | DM          |          |            |  |  |

| L6          |              |                          |                      | ND          |          |            |  |  |

| L7          |              |                          | GI                   | ND          |          |            |  |  |

| L8          |              |                          | GI                   | ND          |          |            |  |  |

| L9          |              |                          | GI                   | ND          |          |            |  |  |

| L10         |              |                          | GI                   | ND          |          |            |  |  |

| L11         |              |                          | GI                   | ND          |          |            |  |  |

| L12         |              |                          | GI                   | ND          |          |            |  |  |

| L13         |              | GND                      |                      |             |          |            |  |  |

| L14         |              |                          | VD                   | DIO         |          |            |  |  |

| L15         |              |                          | VD                   | DIO         |          |            |  |  |

| L16         |              |                          | VD                   | DIO         |          |            |  |  |

| L17         |              |                          | V                    | DC          |          |            |  |  |

| L18 (1L44X) |              | reserved HCS2/HCS2       |                      |             |          |            |  |  |

| _18 (1M88B) |              | GPIB11                   |                      | GPOB11      | HCS      | 2/HCS2     |  |  |

| L19         |              | rese                     | erved                |             | HCS      | 1/HCS1     |  |  |

| L20         |              | reserved HRW or HRD/HRD  |                      |             |          |            |  |  |

| M1          |              |                          | C                    | 02          |          |            |  |  |

| M2          |              |                          | Vr                   | DM          |          |            |  |  |

### Table 1. MSC7112 Signals by Ball Designator (continued)

|        | Signal Names        |                          |                      |             |                     |           |  |  |  |

|--------|---------------------|--------------------------|----------------------|-------------|---------------------|-----------|--|--|--|

| Number | Software Controlled |                          |                      |             | Hardware Controlled |           |  |  |  |

|        | End of Reset        | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary             | Alternate |  |  |  |

| M3     |                     |                          | D                    | 5           |                     |           |  |  |  |

| M4     |                     |                          | V <sub>D</sub>       | DM          |                     |           |  |  |  |

| M5     |                     |                          | V <sub>D</sub>       | DM          |                     |           |  |  |  |

| M6     |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M7     |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M8     |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M9     |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M10    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M11    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M12    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M13    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M14    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M15    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| M16    |                     |                          | VD                   | DC          |                     |           |  |  |  |

| M17    |                     |                          |                      | DC          |                     |           |  |  |  |

| M18    | GPI                 | A14                      | IRQ15                | GPOA14      | SDA                 |           |  |  |  |

| M19    | GP                  | A12                      | IRQ3                 | GPOA12      | UTXD                |           |  |  |  |

| M20    | GPI                 | A13                      | IRQ2                 | GPOA13      | URXD                |           |  |  |  |

| N1     |                     |                          | D                    | 4           |                     |           |  |  |  |

| N2     |                     |                          | D                    | 6           |                     |           |  |  |  |

| N3     |                     |                          | V <sub>F</sub>       | EF          |                     |           |  |  |  |

| N4     |                     |                          |                      | DM          |                     |           |  |  |  |

| N5     |                     |                          |                      | DM          |                     |           |  |  |  |

| N6     |                     |                          |                      | DM          |                     |           |  |  |  |

| N7     |                     |                          |                      | ND          |                     |           |  |  |  |

| N8     |                     |                          | GI                   | ND          |                     |           |  |  |  |

| N9     |                     |                          | GI                   | ND          |                     |           |  |  |  |

| N10    |                     |                          |                      | ND          |                     |           |  |  |  |

| N11    |                     |                          |                      | ND          |                     |           |  |  |  |

| N12    |                     |                          | GI                   | ND          |                     |           |  |  |  |

| N13    |                     |                          |                      | ND          |                     |           |  |  |  |

| N14    |                     |                          |                      | ND          |                     |           |  |  |  |

| N15    |                     |                          |                      | DIO         |                     |           |  |  |  |

| N16    |                     |                          |                      | DC          |                     |           |  |  |  |

| N17    | V <sub>DDC</sub>    |                          |                      |             |                     |           |  |  |  |

| N18    |                     |                          | CL                   |             |                     |           |  |  |  |

| N19    | GPI                 | A15                      | IRQ14                | GPOA15      | S                   | CL        |  |  |  |

| N20    |                     |                          | V <sub>SS</sub>      |             |                     |           |  |  |  |

### Table 1. MSC7112 Signals by Ball Designator (continued)

|        | Signal Names        |                          |                      |             |          |            |  |  |  |

|--------|---------------------|--------------------------|----------------------|-------------|----------|------------|--|--|--|

| Number | Software Controlled |                          |                      |             | Hardware | Controlled |  |  |  |

|        | End of Reset        | GPI Enabled<br>(Default) | Interrupt<br>Enabled | GPO Enabled | Primary  | Alternate  |  |  |  |

| U17    |                     |                          | V                    | DDC         |          |            |  |  |  |

| U18    |                     |                          | 1                    | ١C          |          |            |  |  |  |

| U19    |                     |                          | т                    | СК          |          |            |  |  |  |

| U20    |                     |                          | TF                   | RST         |          |            |  |  |  |

| V1     |                     |                          | V                    | DDM         |          |            |  |  |  |

| V2     |                     |                          | ٦                    | 1C          |          |            |  |  |  |

| V3     |                     |                          | A                    | .13         |          |            |  |  |  |

| V4     |                     |                          | Ą                    | .11         |          |            |  |  |  |

| V5     |                     |                          | Ą                    | .10         |          |            |  |  |  |

| V6     |                     |                          | /                    | 45          |          |            |  |  |  |

| V7     |                     |                          |                      | A2          |          |            |  |  |  |

| V8     |                     |                          | В                    | A0          |          |            |  |  |  |

| V9     |                     |                          | 1                    | ۱C          |          |            |  |  |  |

| V10    |                     | resei                    | rved                 |             | EVN      | NT0        |  |  |  |

| V11    | SWTE                | GPIA16                   | IRQ12                | GPOA16      | EVNT4    |            |  |  |  |

| V12    | GP                  | IA8                      | IRQ6                 | GPOA8       | TOTCK    |            |  |  |  |

| V13    | GP                  | IA4                      | IRQ1                 | GPOA4       | T1RFS    |            |  |  |  |

| V14    | GP                  | IA0                      | IRQ11                | GPOA0       | T1TD     |            |  |  |  |

| V15    | GPI                 | A28                      | IRQ17                | GPOA28      | reserved | reserved   |  |  |  |

| V16    |                     | GPID6                    |                      | GPOD6       | reserved | reserved   |  |  |  |

| V17    | GPI                 | A22                      | IRQ22                | GPOA22      | reserved |            |  |  |  |

| V18    | GPI                 | A24                      | IRQ24                | GPOA24      | reserved |            |  |  |  |

| V19    |                     |                          | ٦                    | 1C          |          |            |  |  |  |

| V20    |                     |                          | Т                    | DI          |          |            |  |  |  |

| W1     |                     |                          | G                    | ND          |          |            |  |  |  |

| W2     |                     |                          | V                    | DDM         |          |            |  |  |  |

| W3     |                     |                          |                      | .12         |          |            |  |  |  |

| W4     |                     |                          | ,                    | 48          |          |            |  |  |  |

| W5     |                     |                          |                      | 47          |          |            |  |  |  |

| W6     |                     |                          |                      | 46          |          |            |  |  |  |

| W7     |                     | A3                       |                      |             |          |            |  |  |  |

| W8     |                     |                          | 1                    | ۱C          |          |            |  |  |  |

| W9     | GPIA17              |                          | IRQ13                | GPOA17      | EVNT1    | CLKO       |  |  |  |

| W10    |                     |                          | C14                  | GPOC14      | EVN      | NT2        |  |  |  |

| W11    | GPI                 | A10                      | IRQ5                 | GPOA10      | TOR      | RFS        |  |  |  |

| W12    | GP                  | IA7                      | IRQ7                 | GPOA7       | тот      | FS         |  |  |  |

| W13    | GP                  | IA3                      | IRQ8                 | GPOA3       | T1RD     |            |  |  |  |

| W14    | GP                  | IA1                      | IRQ10                | GPOA1       | T1T      | FS         |  |  |  |

### Table 1. MSC7112 Signals by Ball Designator (continued)

# **Specifications**

This chapter covers power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the MSC711x Reference Manual.

Note: The MSC7112 electrical specifications are preliminary and many are from design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications will be published after thorough characterization and device qualifications have been completed.

#### **Maximum Ratings** 2.1

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 describes the maximum electrical ratings for the MSC7112.

| Rating                        | Symbol             | Value              | Unit |

|-------------------------------|--------------------|--------------------|------|

| Core supply voltage           | V <sub>DDC</sub>   | 1.5                | V    |

| Memory supply voltage         | V <sub>DDM</sub>   | 4.0                | V    |

| PLL supply voltage            | V <sub>DDPLL</sub> | 1.5                | V    |

| I/O supply voltage            | V <sub>DDIO</sub>  | -0.2 to 4.0        | V    |

| Input voltage                 | V <sub>IN</sub>    | (GND – 0.2) to 4.0 | V    |

| Reference voltage             | V <sub>REF</sub>   | 4.0                | V    |

| Maximum operating temperature | TJ                 | 105                | °C   |

| Minimum operating temperature | T <sub>A</sub>     | -40                | °C   |

| Storage temperature range     | T <sub>STG</sub>   | -55 to +150        | °C   |

Table 2. Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond 2. the listed limits may affect device reliability or cause permanent damage.

3. Section 3.1. Thermal Design Considerations includes a formula for computing the chip junction temperature (T<sub>1</sub>).

| CLKC.                                                   | TRL[CKSEL]                                                                                                                 | CLKCTRL[RNG] | Resulting<br>Division<br>Factor | Allowed Range<br>of Core Clock            | Comments                |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|-------------------------------------------|-------------------------|--|--|--|--|

|                                                         | 11                                                                                                                         | 1            | 1                               | Reserved                                  | Reserved                |  |  |  |  |

|                                                         | 11                                                                                                                         | 0            | 2                               | $150 \leq Core\_Clk \leq 200 \text{ MHz}$ | Limited by range of PLL |  |  |  |  |

| 01 1 2 150 ≤ Core_Clk ≤ 200 MHz Limited by range of PLL |                                                                                                                            |              |                                 |                                           |                         |  |  |  |  |

|                                                         | 01                                                                                                                         | 0            | 4                               | $75 \le Core\_Clk \le 150 MHz$            | Limited by range of PLL |  |  |  |  |

| Note:                                                   | Note: This table results from the allowed range for F <sub>OUT</sub> , which depends on clock selected via CLKCTRL[CKSEL]. |              |                                 |                                           |                         |  |  |  |  |

Table 13. Resulting Ranges Permitted for the Core Clock

### 2.5.2.5 Core Clock Frequency Range When Using DDR Memory

The core clock can also be limited by the frequency range of the DDR devices in the system. **Table 14** summarizes this restriction.

| DDR Type          | Allowed Frequency<br>Range for DDR CK | Corresponding Range<br>for the Core Clock | Comments                                         |

|-------------------|---------------------------------------|-------------------------------------------|--------------------------------------------------|

| DDR 200 (PC-1600) | 83–100 MHz                            | $166 \le core \ clock \le 200 \ MHz$      | Core limited to $2 \times maximum DDR$ frequency |

| DDR 266 (PC-2100) | 83–133 MHz                            | $166 \le core \ clock \le 266 \ MHz$      | Core limited to $2 \times maximum DDR$ frequency |

| DDR 333 (PC-2600) | 83–150 MHz                            | $166 \le core \ clock \le 300 \ MHz$      | Core limited to $2 \times maximum DDR$ frequency |

### Table 14. Core Clock Ranges When Using DDR

### 2.5.3 Reset Timing

The MSC7112 device has several inputs to the reset logic. All MSC7112 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. **Table 15** describes the reset sources.

| Table 15. Reset | Sources |

|-----------------|---------|

|-----------------|---------|

| Name                                       | Direction     | Description                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)                | Input         | Initiates the power-on reset flow that resets the MSC7112 and configures various attributes of the MSC7112. On PORESET, the entire MSC7112 device is reset. SPLL and DLL states are reset, HRESET is driven, the SC1400 extended core is reset, and system configuration is sampled. The system is configured only when PORESET is asserted. |

| External Hard<br>reset (HRESET)            | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC7112. While HRESET is asserted, HRESET is an open-drain output. Upon hard reset, HRESET is driven and the SC1400 extended core is reset.                                                                                                                          |

| Software<br>watchdog reset                 | Internal      | When the MSC7112 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                    |

| Bus monitor<br>reset                       | Internal      | When the MSC7112 bus monitor count reaches zero, a bus monitor hard reset is asserted. The enabled bus monitor event then generates an internal hard reset sequence.                                                                                                                                                                         |

| JTAG EXTEST,<br>CLAMP, or<br>HIGHZ command | Internal      | When a Test Access Port (TAP) executes an EXTEST, CLAMP, or HIGHZ command, the TAP logic asserts an internal reset signal that generates an internal soft reset sequence.                                                                                                                                                                    |

Table 16 summarizes the reset actions that occur as a result of the different reset sources.

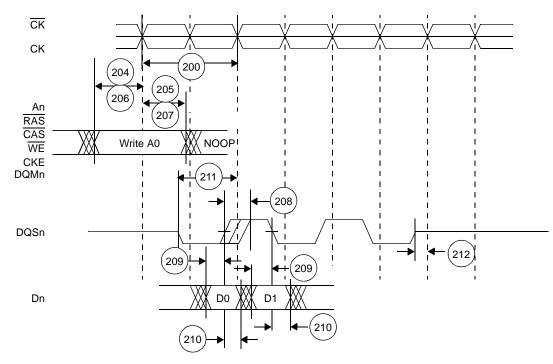

Figure 6 shows the DDR DRAM output timing diagram.

#### Figure 6. DDR DRAM Output Timing Diagram

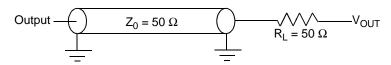

Figure 7 provides the AC test load for the DDR DRAM bus.

Figure 7. DDR DRAM AC Test Load

### Table 20. DDR DRAM Measurement Conditions

|                               |          | Symbol                                                                    | DDR DRAM                  | Unit |

|-------------------------------|----------|---------------------------------------------------------------------------|---------------------------|------|

| V <sub>TH</sub> <sup>1</sup>  |          |                                                                           | V <sub>REF</sub> ± 0.31 V | V    |

| V <sub>OUT</sub> <sup>2</sup> |          |                                                                           | $0.5 	imes V_{DDM}$       | V    |

| Notes:                        | 1.<br>2. | Data input threshold measurement point.<br>Data output measurement point. |                           |      |

### 2.5.5 TDM Timing

#### Table 21. TDM Timing

| No. | Characteristic                       | Expression   | Min  | Max | Units |

|-----|--------------------------------------|--------------|------|-----|-------|

| 300 | TDMxRCK/TDMxTCK                      | TC           | 20.0 | —   | ns    |

| 301 | TDMxRCK/TDMxTCK High Pulse Width     | 0.4 	imes TC | 8.0  | —   | ns    |

| 302 | TDMxRCK/TDMxTCK Low Pulse Width      | 0.4 	imes TC | 8.0  | —   | ns    |

| 303 | TDM all input Setup time             |              | 3.0  | —   | ns    |

| 304 | TDMxRD Hold time                     |              | 3.5  | —   | ns    |

| 305 | TDMxTFS/TDMxRFS input Hold time      |              | 2.0  | _   | ns    |

| 306 | TDMxTCK High to TDMxTD output active |              | 4.0  |     | ns    |

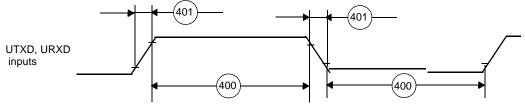

## 2.5.8 UART Timing

| No. | Characteristics                        | Expression               |       | k Set<br>14X | Mask Set<br>1M88B |     | Unit |

|-----|----------------------------------------|--------------------------|-------|--------------|-------------------|-----|------|

|     |                                        |                          | Min   | Max          | Min               | Мах |      |

| _   | Internal bus clock (APBCLK)            | F <sub>CORE</sub> /2     | _     | 100          | —                 | 133 | MHz  |

| —   | Internal bus clock period (1/APBCLK)   | T <sub>APBCLK</sub>      | 10.0  |              | 7.52              |     | ns   |

| 400 | URXD and UTXD inputs high/low duration | 16 × T <sub>APBCLK</sub> | 160.0 |              | 120.3             |     | ns   |

| 401 | URXD and UTXD inputs rise/fall time    |                          | —     | 5            | —                 | 5   | ns   |

| 402 | UTXD output rise/fall time             |                          |       | 5            | —                 | 5   | ns   |

### Table 24. UART Timing

Figure 17. UART Input Timing

Figure 18. UART Output Timing

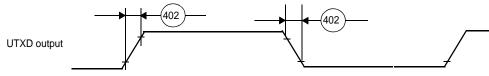

### 2.5.9 EE Timing

### Table 25. EE0 Timing

| Number |                                                                                                                              |  | Characteristics               | Туре                      | Min                  |

|--------|------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------|---------------------------|----------------------|

| 65     |                                                                                                                              |  | EE0 input to the core         | Asynchronous              | 4 core clock periods |

| 66     | 66                                                                                                                           |  | EE0 output from the core      | Synchronous to core clock | 1 core clock period  |

| Notes: | Notes: 1. The core clock is the SC1400 core clock. The ratio between the core clock and CLKOUT is configured during power-on |  |                               |                           |                      |

|        | 2. Configure the direction of the EE pin in the EE_CTRL register (see the SC1400 Core Reference Manual for deta              |  | Reference Manual for details. |                           |                      |

|        | 3. Refer to <b>Table 15</b> for details on EE pin functionality.                                                             |  |                               |                           |                      |

Figure 19 shows the signal behavior of the EE pin.

Figure 19. EE Pin Timing

# 3 Hardware Design Considerations

This section described various areas to consider when incorporating the MSC7112 device into a system design.

### 3.1 Thermal Design Considerations

An estimation of the chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

$$T_J = T_A + (R_{\bigcup JA} \times P_D) \qquad \qquad Eqn.$$

where

$T_A$  = ambient temperature near the package (°C)

$R_{\text{HJA}} =$ junction-to-ambient thermal resistance (°C/W)

$P_D = P_{INT} + P_{I/O} =$  power dissipation in the package (W)

$P_{INT} = I_{DD} \times V_{DD}$  = internal power dissipation (W)

$P_{I/O}$  = power dissipated from device on output pins (W)

The power dissipation values for the MSC7112 are listed in **Table 4**. The ambient temperature for the device is the air temperature in the immediate vicinity that would cool the device. The junction-to-ambient thermal resistances are JEDEC standard values that provide a quick and easy estimation of thermal performance. There are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. The value that more closely approximates a specific application depends on the power dissipated by other components on the printed circuit board (PCB). The value obtained using a single layer board is appropriate for tightly packed PCB configurations. The value obtained using a board with internal planes is more appropriate for boards with low power dissipation (less than  $0.02 \text{ W/cm}^2$  with natural convection) and well separated components. Based on an estimation of junction temperature using this technique, determine whether a more detailed thermal analysis is required. Standard thermal management techniques can be used to maintain the device thermal junction temperature below its maximum. If T<sub>J</sub> appears to be too high, either lower the ambient temperature or the power dissipation of the chip.

You can verify the junction temperature by measuring the case temperature using a small diameter thermocouple (40 gauge is recommended) or an infrared temperature sensor on a spot on the device case. Use the following equation to determine  $T_J$ :

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

Eqn. 2

where

$T_T$  = thermocouple (or infrared) temperature on top of the package (°C)  $\Psi_{JT}$  = thermal characterization parameter (°C/W)  $P_D$  = power dissipation in the package (W)

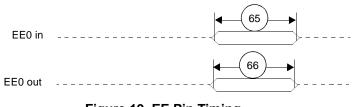

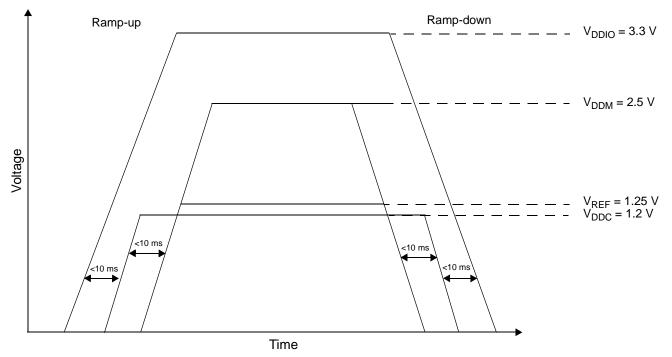

### 3.2.2.1 Case 1

The power-up sequence is as follows:

- 1. Turn on the  $V_{DDIO}$  (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn on the  $V_{DDM}$  (2.5 V) supply third.

- 4. Turn on the  $V_{REF}$  (1.25 V) supply fourth (last).

The power-down sequence is as follows:

- 1. Turn off the  $V_{REF}$  (1.25 V) supply first.

- 2. Turn off the  $V_{DDM}$  (2.5 V) supply second.

- 3. Turn off the  $V_{DDC}$  (1.2 V) supply third.

- 4. Turn of the  $V_{DDIO}$  (3.3 V) supply fourth (last).

Use the following guidelines:

- Make sure that the time interval between the ramp-down of  $V_{DDIO}$  and  $V_{DDC}$  is less than 10 ms.

- Make sure that the time interval between the ramp-up or ramp-down for V<sub>DDC</sub> and V<sub>DDM</sub> is less than 10 ms for power-up and power-down.

- Refer to **Figure 26** for relative timing for power sequencing case 1.

Time Figure 26. Voltage Sequencing Case 1

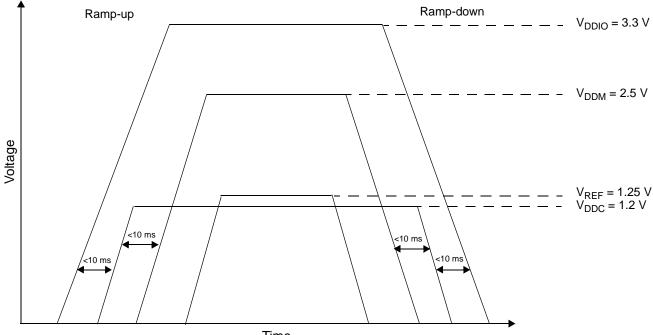

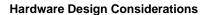

### 3.2.2.3 Case 3

The power-up sequence is as follows:

- 1. Turn on the  $V_{DDIO}$  (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn on the  $V_{DDM}$  (2.5 V) and  $V_{REF}$  (1.25 V) supplies simultaneously (third).

Note: Make sure that the time interval between the ramp-up of  $V_{DDIO}$  and  $V_{DDC}$  is less than 10 ms.

The power-down sequence is as follows:

- 1. Turn off the  $V_{DDM}$  (2.5 V) and  $V_{REF}$  (1.25 V) supplies simultaneously (first).

- 2. Turn off the  $V_{DDC}$  (1.2 V) supply second.

- 3. Turn of the  $V_{DDIO}$  (3.3 V) supply third (last).

Use the following guidelines:

- Make sure that the time interval between the ramp-down for V<sub>DDIO</sub> and V<sub>DDC</sub> is less than 10 ms.

- Make sure that the time interval between the ramp-up or ramp-down time for V<sub>DDC</sub> and V<sub>DDM</sub> is less than 10 ms for power-up and power-down.

- Refer to **Figure 28** for relative timing for Case 3.

Figure 28. Voltage Sequencing Case 3

### 3.2.2.4 Case 4

The power-up sequence is as follows:

- 1. Turn on the  $V_{DDIO}$  (3.3 V) supply first.

- 2. Turn on the  $V_{DDC}$  (1.2 V),  $V_{DDM}$  (2.5 V), and  $V_{REF}$  (1.25 V) supplies simultaneously (second).

Note: Make sure that the time interval between the ramp-up of  $V_{DDIO}$  and  $V_{DDC}$  is less than 10 ms.

The power-down sequence is as follows:

- 1. Turn off the V<sub>DDC</sub> (1.2 V), V<sub>REF</sub> (1.25 V), and V<sub>DDM</sub> (2.5 V) supplies simultaneously (first).

- 2. Turn of the  $V_{DDIO}$  (3.3 V) supply last.

Use the following guidelines:

- Make sure that the time interval between the ramp-up or ramp-down time for  $V_{DDC}$  and  $V_{DDM}$  is less than 10 ms for power-up and power-down.

- Refer to **Figure 29** for relative timing for Case 4.

Figure 29. Voltage Sequencing Case 4

### 3.4.3.2 I<sup>2</sup>C Boot

When the MSC7112 device is configured to boot from the  $I^2C$  port, the boot program configures the GPIO pins shared with the  $I^2C$  pins as  $I^2C$  pins. The  $I^2C$  interface is configured as follows:

- I<sup>2</sup>C in master mode.

- EPROM in slave mode.

For details on the boot procedure, see the "Boot Program" chapter of the MSC711x Reference Manual.

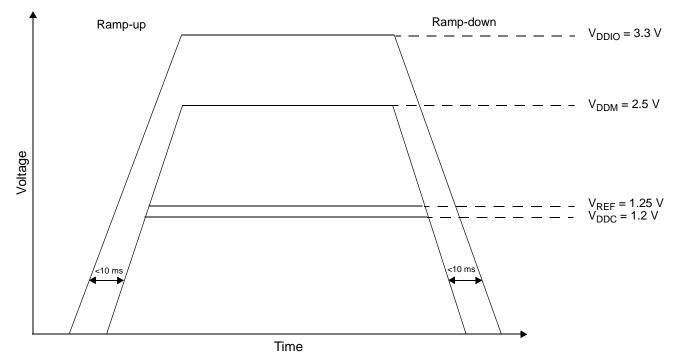

# 3.5 DDR Memory System Guidelines

MSC7112 devices contain a memory controller that provides a glueless interface to external double data rate (DDR) SDRAM memory modules with Class 2 Series Stub Termination Logic 2.5 V (SSTL\_2). There are two termination techniques, as shown in Figure 32. Technique B is the most popular termination technique.

Figure 32. SSTL Termination Techniques

Figure 33 illustrates the power wattage for the resistors. Typical values for the resistors are as follows:

- $RS = 22 \Omega$

- $RT = 24 \Omega$

# 3.6 Connectivity Guidelines

This section summarizes the connections and special conditions, such as pull-up or pull-down resistors, for the MSC7112 device. Following are guidelines for signal groups and configuration settings:

- Clock and reset signals.

- SWTE is used to configure the MSC7112 device and is sampled on the deassertion of PORESET, so it should be tied to V<sub>DDC</sub> or GND either directly or through pull-up or pull-down resistors until PORESET is deasserted. After PORESET, this signal can be left floating.

- BM[0–1] configure the MSC7112 device and are sampled until PORESET is deasserted, so they should be tied to V<sub>DDIO</sub> or GND either directly or through pull-up or pull-down resistors.

- **HRESET** should be pulled up.

- Interrupt signals. When used, **IRQ** pins must be pulled up.

- HDI16 signals.

- When they are configured for open-drain, the HREQ/HREQ or HTRQ/HTRQ signals require a pull-up resistor. However, these pins are also sampled at power-on reset to determine the HDI16 boot mode and may need to be pulled down. When these pins must be pulled down on reset and pulled up otherwise, a buffer can be used with the HRESET signal as the enable.

- When the device boots through the HDI16, the HDDS, HDSP and H8BIT pins should be pulled up or down, depending on the required boot mode settings.

- $I^2C$  signals. The SCL and SDA signals, when programmed for  $I^2C$ , requires an external pull-up resistor.

- *General-purpose I/O (GPIO) signals*. An unused GPIO pin can be disconnected. After boot, program it as an output pin.

- Other signals.

- The  $\overline{\mathsf{TEST0}}$  pin must be connected to ground.

- The TPSEL pin should be pulled up to enable debug access via the EOnCE port and pulled down for boundary scan.

- Pins labelled NO CONNECT (NC) must not be connected.

- When a 16-pin double data rate (DDR) interface is used, the 16 unused data pins should be no connects (floating) if the used lines are terminated.

- Do not connect DBREQ to DONE (as you would for the MSC8101 device). Connect DONE to one of the EVNT pins, and DBREQ to HRRQ.

# 4 Ordering Information

Consult a Freescale Semiconductor sales office or authorized distributor to determine product availability and place an order.

| Part             | Supply<br>Voltage        | Package Type                                      | Pin<br>Count | Core<br>Frequency<br>(MHz) | Solder Spheres | Order Number  |

|------------------|--------------------------|---------------------------------------------------|--------------|----------------------------|----------------|---------------|

| MSC7112<br>(mask | 1.2 V core<br>2.5 V mem. | Molded Array Process-Ball Grid<br>Array (MAP-BGA) | 400          | 200                        | Lead-free      | MSC7112VM800  |

| 1L44X            | 3.3 V I/O                |                                                   |              |                            | Lead-bearing   | MSC7112VF800  |

| MSC7112<br>(mask | 1.2 V core<br>2.5 V mem  | Molded Array Process-Ball Grid<br>Array (MAP-BGA) | 400          | 266                        | Lead-free      | MSC7112VM1000 |

| 1M88B)           | 3.3 V I/O                |                                                   |              |                            | Lead-bearing   | MSC7112VF1000 |

age information

# 5 Package Information

# 6 **Product Documentation**

- *MSC711x Reference Manual* (MSC711xRM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC7112 device.

- *SC140/SC1400 DSP Core Reference Manual*. Covers the SC140 and SC1400 core architecture, control registers, clock registers, program control, and instruction set.

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support: http://www.freescale.com/support

### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MSC7112 Rev. 11 4/2008 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale™, the Freescale logo, CodeWarrior, fieldBIST, and StarCore are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2004, 2008. All rights reserved.