# E·XFL

#### NXP USA Inc. - MC9S08DZ128MLH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 53                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 24x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08dz128mlh |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Chapter

# **List of Chapters**

Title

| Chapter 1  | Device Overview21                                   |

|------------|-----------------------------------------------------|

| Chapter 2  | Pins and Connections27                              |

| Chapter 3  | Modes of Operation                                  |

| Chapter 4  | Memory45                                            |

| Chapter 5  | Resets, Interrupts, and General System Control85    |

| Chapter 6  | Parallel Input/Output Control101                    |

| Chapter 7  | Central Processor Unit (S08CPUV5)143                |

| Chapter 8  | Multi-Purpose Clock Generator (S08MCGV2)165         |

| Chapter 9  | 5-V Analog Comparator (S08ACMPV3)199                |

| Chapter 10 | Analog-to-Digital Converter (S08ADC12V1)207         |

| Chapter 11 | Inter-Integrated Circuit (S08IICV2)233              |

| Chapter 12 | Freescale's Controller Area Network (S08MSCANV1)253 |

| Chapter 13 | Serial Peripheral Interface (S08SPIV3)              |

| Chapter 14 | Serial Communications Interface (S08SCIV4)323       |

| Chapter 15 | Real-Time Counter (S08RTCV1)                        |

| Chapter 16 | Timer Pulse-Width Modulator (S08TPMV3)353           |

| Chapter 17 | Development Support                                 |

| Chapter 18 | Debug Module (S08DBGV3) (128K)                      |

| Appendix A | Electrical Characteristics419                       |

| Appendix B | Ordering Information and Mechanical Drawings447     |

|            |                                                     |

Page

NP

**Chapter 4 Memory**

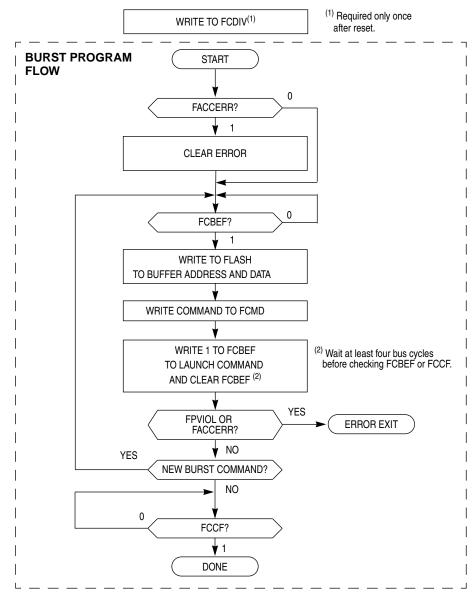

Figure 4-12. Burst Program Flowchart

MC9S08DZ128 Series Data Sheet, Rev. 1

### Table 4-13. FCDIV Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD  | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH and EEPROM.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH and EEPROM.</li> </ul>                                                                                                                                                                     |

| 6<br>PRDIV8 | <ul> <li>Prescale (Divide) FLASH and EEPROM Clock by 8 (This bit is write once.)</li> <li>0 Clock input to the FLASH and EEPROM clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH and EEPROM clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| 5:0<br>DIV  | <b>Divisor for FLASH and EEPROM Clock Divider</b> — The FLASH and EEPROM clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV field plus one. The resulting frequency of the internal FLASH and EEPROM clock must fall within the range of 200 kHz to 150 kHz for proper FLASH and EEPROM operations. Program/Erase timing pulses are one cycle of this internal FLASH and EEPROM clock which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. |

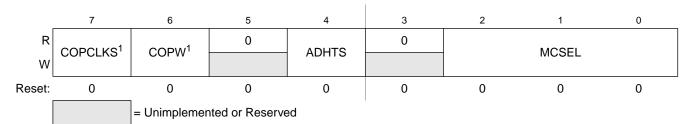

# 5.8.5 System Options Register 2 (SOPT2)

This high page register contains bits to configure MCU specific features on the MC9S08DZ128 Series devices.

#### Figure 5-6. System Options Register 2 (SOPT2)

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPCLKS | <ul> <li>COP Watchdog Clock Select — This write-once bit selects the clock source of the COP watchdog. See Table 5-6 for details.</li> <li>0 Internal 1-kHz clock is source to COP.</li> <li>1 Bus clock is source to COP.</li> </ul>                                                                                                                                                  |

| 6<br>COPW    | <ul> <li>COP Window — This write-once bit selects the COP operation mode. When set, the 0x55-0xAA write sequence to the SRS register must occur in the last 25% of the selected period. Any write to the SRS register during the first 75% of the selected period will reset the MCU.</li> <li>0 Normal COP operation.</li> <li>1 Window COP operation (only if COPCLKS=1).</li> </ul> |

| 4<br>ADHTS   | <ul> <li>ADC Hardware Trigger Select — This bit selects which hardware trigger initiates conversion for the analog to digital converter when the ADC hardware trigger is enabled (ADCTRG is set in ADCSC2 register).</li> <li>0 Real Time Counter (RTC) overflow.</li> <li>1 External Interrupt Request (IRQ) pin.</li> </ul>                                                          |

| 2:0<br>MCSEL | MCLK Divide Select— These bits enable the MCLK output on PTA0 pin and select the divide ratio for the MCLK output according to the formula below when the MCSEL bits are not equal to all zeroes. In case that the MCSEL bits are all zeroes, the MCLK output is disabled.<br>MCLK frequency = Bus Clock frequency ÷ (2 * MCSEL)                                                       |

#### Table 5-7. SOPT2 Register Field Descriptions

# Chapter 6 Parallel Input/Output Control

This section explains software controls related to parallel input/output (I/O) and pin control. The MC9S08DZ128 Series has up to 11 parallel I/O ports which include a total of up to 87 I/O pins and one input-only pin. See Chapter 2, "Pins and Connections," for more information about pin assignments and external hardware considerations of these pins.

Many of these pins are shared with on-chip peripherals such as timer systems, communication systems, or pin interrupts as shown in Table 2-1. The peripheral modules have priority over the general-purpose I/O functions so that when a peripheral is enabled, the I/O functions associated with the shared pins are disabled.

After reset, the shared peripheral functions are disabled and the pins are configured as inputs (PTxDDn = 0). The pin control functions for each pin are configured as follows: slew rate control enabled (PTxSEn = 1), low drive strength selected (PTxDSn = 0), and internal pull-ups disabled (PTxPEn = 0).

### NOTE

Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program must either enable on-chip pull-up devices or change the direction of unconnected pins to outputs so the pins do not float.

# 6.1 Port Data and Data Direction

Reading and writing of parallel I/Os are performed through the port data registers. The direction, either input or output, is controlled through the port data direction registers. The parallel I/O port function for an individual pin is illustrated in the block diagram shown in Figure 6-1.

The data direction control bit (PTxDDn) determines whether the output buffer for the associated pin is enabled, and also controls the source for port data register reads. The input buffer for the associated pin is always enabled unless the pin is enabled as an analog function or is an output-only pin.

When a shared digital function is enabled for a pin, the output buffer is controlled by the shared function. However, the data direction register bit will continue to control the source for reads of the port data register.

When a shared analog function is enabled for a pin, both the input and output buffers are disabled. A value of 0 is read for any port data bit where the bit is an input (PTxDDn = 0) and the input buffer is disabled. In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

#### Chapter 6 Parallel Input/Output Control

PTxSC provided all enabled port inputs are at their deasserted levels. PTxIF will remain set if any enabled port pin is asserted while attempting to clear by writing a 1 to PTxACK.

# 6.3.3 Pull-up/Pull-down Resistors

The port interrupt pins can be configured to use an internal pull-up/pull-down resistor using the associated I/O port pull-up enable register. If an internal resistor is enabled, the PTxES register is used to select whether the resistor is a pull-up (PTxESn = 0) or a pull-down (PTxESn = 1).

# 6.3.4 Pin Interrupt Initialization

When an interrupt pin is first enabled, it is possible to get a false interrupt flag. To prevent a false interrupt request during pin interrupt initialization, the user should do the following:

- 1. Mask interrupts by clearing PTxIE in PTxSC.

- 2. Select the pin polarity by setting the appropriate PTxESn bits in PTxES.

- 3. If using internal pull-up/pull-down device, configure the associated pull enable bits in PTxPE.

- 4. Enable the interrupt pins by setting the appropriate PTxPSn bits in PTxPS.

- 5. Write to PTxACK in PTxSC to clear any false interrupts.

- 6. Set PTxIE in PTxSC to enable interrupts.

# 6.4 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, peripherals may require initialization to be restored to their pre-stop condition. This can be done using data previously stored in RAM if it was saved before the STOP instruction was executed. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

# 6.5 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale

Chapter 6 Parallel Input/Output Control

# 6.5.5.5 Port E Drive Strength Selection Register (PTEDS)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1                   | 0      |

|--------|--------|--------|--------|--------|--------|--------|---------------------|--------|

| R<br>W | PTEDS7 | PTEDS6 | PTEDS5 | PTEDS4 | PTEDS3 | PTEDS2 | PTEDS1 <sup>1</sup> | PTEDS0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0                   | 0      |

Figure 6-36. Drive Strength Selection for Port E Register (PTEDS)

<sup>1</sup> PTEDS1 has no effect on the input-only PTE1 pin.

#### Table 6-34. PTEDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDS[7:0] | <ul> <li>Output Drive Strength Selection for Port E Bits — Each of these control bits selects between low and high output drive for the associated PTE pin. For port E pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port E bit n.</li> <li>1 High output drive strength selected for port E bit n.</li> </ul> |

# 6.5.8 Port H Registers

Port H is controlled by the registers listed below.

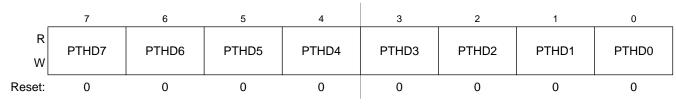

### 6.5.8.1 Port H Data Register (PTHD)

#### Figure 6-47. Port H Data Register (PTHD)

#### Table 6-45. PTHD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTHD[7:0] | Port H Data Register Bits — For port H pins that are inputs, reads return the logic level on the pin. For port H pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port H pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTHD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

### 6.5.8.2 Port H Data Direction Register (PTHDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTHDD7 | PTHDD6 | PTHDD5 | PTHDD4 | PTHDD3 | PTHDD2 | PTHDD1 | PTHDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-48. Port H Data Direction Register (PTHDD)

#### Table 6-46. PTHDD Register Field Descriptions

| Field             | Description                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTHDD[7:0] | <b>Data Direction for Port H Bits</b> — These read/write bits control the direction of port H pins and what is read for PTHD reads.                                             |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port H bit n and PTHD reads return the contents of PTHDn.</li> </ol> |

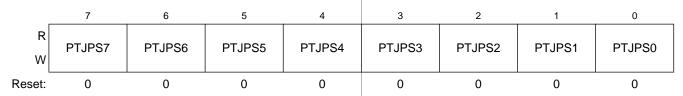

# 6.5.9.7 Port J Interrupt Pin Select Register (PTJPS)

Figure 6-58. Port J Interrupt Pin Select Register (PTJPS)

#### Table 6-56. PTJPS Register Field Descriptions

| Field | Description                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port J Interrupt Pin Selects — Each of the PTJPSn bits enable the corresponding port J interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

### 6.5.9.8 Port J Interrupt Edge Select Register (PTJES)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTJES7 | PTJES6 | PTJES5 | PTJES4 | PTJES3 | PTJES2 | PTJES1 | PTJES0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-59. Port J Edge Select Register (PTJES)

#### Table 6-57. PTJES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port J Edge Selects — Each of the PTJESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

# 7.3 Addressing Modes

Addressing modes define the way the CPU accesses operands and data. In the HCS08, memory, status and control registers, and input/output (I/O) ports share a single 64-Kbyte CPU address space. This arrangement means that the same instructions that access variables in RAM can also be used to access I/O and control registers or nonvolatile program space.

### NOTE

For more information about extended addressing modes, see the Memory Management Unit section in the Memory chapter.

MCU derivatives with more than 64-Kbytes of memory also include a memory management unit (MMU) to support extended memory space. A PPAGE register is used to manage 16-Kbyte pages of memory which can be accessed by the CPU through a 16-Kbyte window from 0x8000 through 0xBFFF. The CPU includes two special instructions (CALL and RTC). CALL operates like the JSR instruction except that CALL saves the current PPAGE value on the stack and provides a new PPAGE value for the destination. RTC works like the RTS instruction except RTC restores the old PPAGE value in addition to the PC during the return from the called routine. The MMU also includes a linear address pointer register and data access registers so that the extended memory space operates as if it was a single linear block of memory. For additional information about the MMU, refer to the Memory chapter of this data sheet.

Some instructions use more than one addressing mode. For instance, move instructions use one addressing mode to specify the source operand and a second addressing mode to specify the destination address. Instructions such as BRCLR, BRSET, CBEQ, and DBNZ use one addressing mode to specify the location of an operand for a test and then use relative addressing mode to specify the branch destination address when the tested condition is true. For BRCLR, BRSET, CBEQ, and DBNZ, the addressing mode listed in the instruction set tables is the addressing mode needed to access the operand to be tested, and relative addressing mode is implied for the branch destination.

# 7.3.1 Inherent Addressing Mode (INH)

In this addressing mode, operands needed to complete the instruction (if any) are located within CPU registers so the CPU does not need to access memory to get any operands.

# 7.3.2 Relative Addressing Mode (REL)

Relative addressing mode is used to specify the destination location for branch instructions. A signed 8-bit offset value is located in the memory location immediately following the opcode. During execution, if the branch condition is true, the signed offset is sign-extended to a 16-bit value and is added to the current contents of the program counter, which causes program execution to continue at the branch destination address.

# 7.3.3 Immediate Addressing Mode (IMM)

In immediate addressing mode, the operand needed to complete the instruction is included in the object code immediately following the instruction opcode in memory. In the case of a 16-bit immediate operand,

Chapter 8 Multi-Purpose Clock Generator (S08MCGV2)

- IREFS (bit 2) set to 1 to select the internal reference clock as the reference clock source

- RDIV (bits 5-3) remain unchanged because the reference divider does not affect the internal reference.

- b) Loop until IREFST (bit 4) in MCGSC is 1, indicating the internal reference clock has been selected as the reference clock source

- c) Loop until CLKST (bits 3 and 2) in MCGSC are %01, indicating that the internal reference clock is selected to feed MCGOUT

- 4. Lastly, FBI transitions into BLPI mode.

- a) MCGC2 = 0x08 (%00001000)

- LP (bit 3) in MCGSC is 1

- RANGE, HGO, EREFS, ERCLKEN, and EREFSTEN bits are ignored when the IREFS bit (bit2) in MCGC is set. They can remain set, or be cleared at this point.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV2)

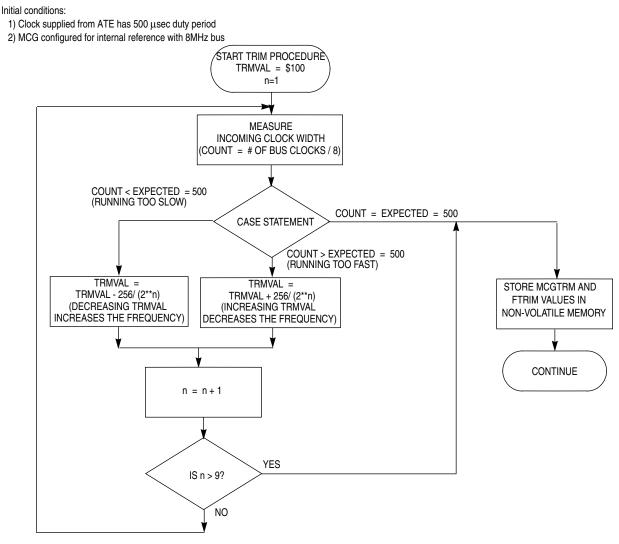

Figure 8-13. Trim Procedure

In this particular case, the MCU has been attached to a PCB and the entire assembly is undergoing final test with automated test equipment. A separate signal or message is provided to the MCU operating under user provided software control. The MCU initiates a trim procedure as outlined in Figure 8-13 while the tester supplies a precision reference signal.

If the intended bus frequency is near the maximum allowed for the device, it is recommended to trim using a reference divider value (RDIV setting) of twice the final value. After the trim procedure is complete, the reference divider can be restored. This will prevent accidental overshoot of the maximum clock frequency.

Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

# 10.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer is in its high impedance state and the pullup is disabled. Also, the input buffer draws DC current when its input is not at  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of  $0.01 \,\mu\text{F}$  capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to  $V_{SSA}$ .

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to 0xFFF (full scale 12-bit representation), 0x3FF (full scale 10-bit representation) or 0xFF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to 0x000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There is a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

# 10.6.2 Sources of Error

Several sources of error exist for A/D conversions. These are discussed in the following sections.

# 10.6.2.1 Sampling Error

For proper conversions, the input must be sampled long enough to achieve the proper accuracy. Given the maximum input resistance of approximately  $7k\Omega$  and input capacitance of approximately 5.5 pF, sampling to within 1/4LSB (at 12-bit resolution) can be achieved within the minimum sample window (3.5 cycles @ 8 MHz maximum ADCK frequency) provided the resistance of the external analog source ( $R_{AS}$ ) is kept below 2 k $\Omega$ .

Higher source resistances or higher-accuracy sampling is possible by setting ADLSMP (to increase the sample window to 23.5 cycles) or decreasing ADCK frequency to increase sample time.

# 10.6.2.2 Pin Leakage Error

Leakage on the I/O pins can cause conversion error if the external analog source resistance ( $R_{AS}$ ) is high. If this error cannot be tolerated by the application, keep  $R_{AS}$  lower than  $V_{DDAD} / (2^{N*}I_{LEAK})$  for less than 1/4LSB leakage error (N = 8 in 8-bit, 10 in 10-bit or 12 in 12-bit mode).

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SDA Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 00           | 20             | 7                 | 6                            | 11                          |

| 01           | 22             | 7                 | 7                            | 12                          |

| 02           | 24             | 8                 | 8                            | 13                          |

| 03           | 26             | 8                 | 9                            | 14                          |

| 04           | 28             | 9                 | 10                           | 15                          |

| 05           | 30             | 9                 | 11                           | 16                          |

| 06           | 34             | 10                | 13                           | 18                          |

| 07           | 40             | 10                | 16                           | 21                          |

| 08           | 28             | 7                 | 10                           | 15                          |

| 09           | 32             | 7                 | 12                           | 17                          |

| 0A           | 36             | 9                 | 14                           | 19                          |

| 0B           | 40             | 9                 | 16                           | 21                          |

| 0C           | 44             | 11                | 18                           | 23                          |

| 0D           | 48             | 11                | 20                           | 25                          |

| 0E           | 56             | 13                | 24                           | 29                          |

| 0F           | 68             | 13                | 30                           | 35                          |

| 10           | 48             | 9                 | 18                           | 25                          |

| 11           | 56             | 9                 | 22                           | 29                          |

| 12           | 64             | 13                | 26                           | 33                          |

| 13           | 72             | 13                | 30                           | 37                          |

| 14           | 80             | 17                | 34                           | 41                          |

| 15           | 88             | 17                | 38                           | 45                          |

| 16           | 104            | 21                | 46                           | 53                          |

| 17           | 128            | 21                | 58                           | 65                          |

| 18           | 80             | 9                 | 38                           | 41                          |

| 19           | 96             | 9                 | 46                           | 49                          |

| 1A           | 112            | 17                | 54                           | 57                          |

| 1B           | 128            | 17                | 62                           | 65                          |

| 1C           | 144            | 25                | 70                           | 73                          |

| 1D           | 160            | 25                | 78                           | 81                          |

| 1E           | 192            | 33                | 94                           | 97                          |

| 1F           | 240            | 33                | 118                          | 121                         |

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SCL Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 20           | 160            | 17                | 78                           | 81                          |

| 21           | 192            | 17                | 94                           | 97                          |

| 22           | 224            | 33                | 110                          | 113                         |

| 23           | 256            | 33                | 126                          | 129                         |

| 24           | 288            | 49                | 142                          | 145                         |

| 25           | 320            | 49                | 158                          | 161                         |

| 26           | 384            | 65                | 190                          | 193                         |

| 27           | 480            | 65                | 238                          | 241                         |

| 28           | 320            | 33                | 158                          | 161                         |

| 29           | 384            | 33                | 190                          | 193                         |

| 2A           | 448            | 65                | 222                          | 225                         |

| 2B           | 512            | 65                | 254                          | 257                         |

| 2C           | 576            | 97                | 286                          | 289                         |

| 2D           | 640            | 97                | 318                          | 321                         |

| 2E           | 768            | 129               | 382                          | 385                         |

| 2F           | 960            | 129               | 478                          | 481                         |

| 30           | 640            | 65                | 318                          | 321                         |

| 31           | 768            | 65                | 382                          | 385                         |

| 32           | 896            | 129               | 446                          | 449                         |

| 33           | 1024           | 129               | 510                          | 513                         |

| 34           | 1152           | 193               | 574                          | 577                         |

| 35           | 1280           | 193               | 638                          | 641                         |

| 36           | 1536           | 257               | 766                          | 769                         |

| 37           | 1920           | 257               | 958                          | 961                         |

| 38           | 1280           | 129               | 638                          | 641                         |

| 39           | 1536           | 129               | 766                          | 769                         |

| 3A           | 1792           | 257               | 894                          | 897                         |

| 3B           | 2048           | 257               | 1022                         | 1025                        |

| 3C           | 2304           | 385               | 1150                         | 1153                        |

| 3D           | 2560           | 385               | 1278                         | 1281                        |

| 3E           | 3072           | 513               | 1534                         | 1537                        |

| 3F           | 3840           | 513               | 1918                         | 1921                        |

#### Table 11-5. IIC Divider and Hold Values

| Field                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHnF             | Channel n flag. When channel n is an input-capture channel, this read/write bit is set when an active edge occurs<br>on the channel n pin. When channel n is an output compare or edge-aligned/center-aligned PWM channel, CHnF<br>is set when the value in the TPM counter registers matches the value in the TPM channel n value registers. When<br>channel n is an edge-aligned/center-aligned PWM channel and the duty cycle is set to 0% or 100%, CHnF will<br>not be set even when the value in the TPM counter registers matches the value in the TPM channel n value<br>registers.<br>A corresponding interrupt is requested when CHnF is set and interrupts are enabled (CHnIE = 1). Clear CHnF by<br>reading TPMxCnSC while CHnF is set and then writing a logic 0 to CHnF. If another interrupt request occurs<br>before the clearing sequence is complete, the sequence is reset so CHnF remains set after the clear sequence<br>completed for the earlier CHnF. This is done so a CHnF interrupt request cannot be lost due to clearing a previous<br>CHnF.<br>Reset clears the CHnF bit. Writing a logic 1 to CHnF has no effect. |

|                       | <ul><li>0 No input capture or output compare event occurred on channel n</li><li>1 Input capture or output compare event on channel n</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>CHnIE            | <ul> <li>Channel n interrupt enable. This read/write bit enables interrupts from channel n. Reset clears CHnIE.</li> <li>0 Channel n interrupt requests disabled (use for software polling)</li> <li>1 Channel n interrupt requests enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5<br>MSnB             | Mode select B for TPM channel n. When CPWMS=0, MSnB=1 configures TPM channel n for edge-aligned PWM mode. Refer to the summary of channel mode and setup controls in Table 16-6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4<br>MSnA             | <ul> <li>Mode select A for TPM channel n. When CPWMS=0 and MSnB=0, MSnA configures TPM channel n for input-capture mode or output compare mode. Refer to Table 16-6 for a summary of channel mode and setup controls.</li> <li>Note: If the associated port pin is not stable for at least two bus clock cycles before changing to input capture mode, it is possible to get an unexpected indication of an edge trigger.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3–2<br>ELSnB<br>ELSnA | Edge/level select bits. Depending upon the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 16-6, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general purpose I/O pin not related to any timer functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin.                                                                                                                                                                                                                                                                                                                                                                                                           |

#### Table 16-5. TPMxCnSC Field Descriptions

| Table 16-6. | Mode, | Edge, | and | Level | Selection |

|-------------|-------|-------|-----|-------|-----------|

|-------------|-------|-------|-----|-------|-----------|

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                                                                             | Configuration |  |  |  |  |

|-------|-----------|-------------|----------------------------------------------------------------------------------|---------------|--|--|--|--|

| X     | XX        | 00          | Pin not used for TPM - revert to general purpose I/O or other peripheral control |               |  |  |  |  |

### 18.3.2

### Table 18-2. Register Bit Summary

|        | 7      | 6      | 5      | 4      | 3        | 2      | 1     | 0      |

|--------|--------|--------|--------|--------|----------|--------|-------|--------|

| DBGCAH | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10 | Bit 9 | Bit 8  |

| DBGCAL | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1 | Bit 0  |

| DBGCBH | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10 | Bit 9 | Bit 8  |

| DBGCBL | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1 | Bit 0  |

| DBGCCH | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10 | Bit 9 | Bit 8  |

| DBGCCL | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1 | Bit 0  |

| DBGFH  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11   | Bit 10 | Bit 9 | Bit 8  |

| DBGFL  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2  | Bit 1 | Bit 0  |

| DBGCAX | RWAEN  | RWA    | PAGSEL | 0      | 0        | 0      | 0     | bit-16 |

| DBGCBX | RWBEN  | RWB    | PAGSEL | 0      | 0        | 0      | 0     | bit-16 |

| DBGCCX | RWCEN  | RWC    | PAGSEL | 0      | 0        | 0      | 0     | bit-16 |

| DBGFX  | PPACC  | 0      | 0      | 0      | 0        | 0      | 0     | bit-16 |

| DBGC   | DBGEN  | ARM    | TAG    | BRKEN  | -        | -      | -     | LOOP1  |

| DBGT   | TRGSEL | BEGIN  | 0      | 0      | TRG[3:0] |        |       |        |

| DBGS   | AF     | BF     | CF     | 0      | 0        | 0      | 0     | ARMF   |

| DBGCNT | 0      | 0      | 0      | 0      |          | CNT    | [3:0] |        |

| Field    | Description                                                                                                                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits 7–0 | <ul> <li>Comparator A Low Compare Bits — The Comparator A Low compare bits control whether Comparator A will compare the address bus bits [7:0] to a logic 1 or logic 0.</li> <li>0 Compare corresponding address bit to a logic 0</li> <li>1 Compare corresponding address bit to a logic 1</li> </ul> |

#### Table 18-4. DBGCAL Field Descriptions

# 18.3.3.3 Debug Comparator B High Register (DBGCBH)

Module Base + 0x0002

|                               | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|-------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| R<br>W                        | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| POR<br>or non-<br>end-run     | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| Reset<br>end-run <sup>1</sup> | U      | U      | U      | U      | U      | U      | U     | U     |

#### Figure 18-4. Debug Comparator B High Register (DBGCBH)

<sup>1</sup> In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, the bits in this register do not change after reset.

#### Table 18-5. DBGCBH Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits 15–8 | <ul> <li>Comparator B High Compare Bits — The Comparator B High compare bits control whether Comparator B will compare the address bus bits [15:8] to a logic 1 or logic 0. Not used in Full mode.</li> <li>0 Compare corresponding address bit to a logic 0</li> <li>1 Compare corresponding address bit to a logic 1</li> </ul> |

# 18.3.3.4 Debug Comparator B Low Register (DBGCBL)

Module Base + 0x0003

| -                             | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W                        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| POR<br>or non-<br>end-run     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Reset<br>end-run <sup>1</sup> | U     | U     | U     | U     | U     | U     | U     | U     |

Figure 18-5. Debug Comparator B Low Register (DBGCBL)

MC9S08DZ128 Series Data Sheet, Rev. 1

Chapter 18 Debug Module (S08DBGV3) (128K)

| TRG Value         | Meaning    |

|-------------------|------------|

| 1001<br>↓<br>1111 | No Trigger |

Table 18-17. Trigger Mode Encoding

#### NOTE

The DBG trigger register (DBGT) can not be changed unless ARM=0.

# 18.3.3.15 Debug Status Register (DBGS)

Module Base + 0x000E

|                               | 7  | 6                           | 5  | 4 | 3 | 2 | 1 | 0    |  |

|-------------------------------|----|-----------------------------|----|---|---|---|---|------|--|

| R                             | AF | BF                          | CF | 0 | 0 | 0 | 0 | ARMF |  |

| w                             |    |                             |    |   |   |   |   |      |  |

| POR<br>or non-<br>end-run     | 0  | 0                           | 0  | 0 | 0 | 0 | 0 | 1    |  |

| Reset<br>end-run <sup>1</sup> | U  | U                           | U  | 0 | 0 | 0 | 0 | 0    |  |

|                               |    | = Unimplemented or Reserved |    |   |   |   |   |      |  |

#### Figure 18-16. Debug Status Register (DBGS)

<sup>1</sup> In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, ARMF gets cleared by reset but AF, BF, and CF do not change after reset.

#### Table 18-18. DBGS Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>AF   | <ul> <li>Trigger A Match Bit — The AF bit indicates if Trigger A match condition was met since arming.</li> <li>0 Comparator A did not match</li> <li>1 Comparator A match</li> </ul>                                                                                                                                                                     |  |  |  |  |

| 6<br>BF   | <ul> <li>Trigger B Match Bit — The BF bit indicates if Trigger B match condition was met since arming.</li> <li>0 Comparator B did not match</li> <li>1 Comparator B match</li> </ul>                                                                                                                                                                     |  |  |  |  |

| 5<br>CF   | <ul> <li>Trigger C Match Bit — The CF bit indicates if Trigger C match condition was met since arming.</li> <li>0 Comparator C did not match</li> <li>1 Comparator C match</li> </ul>                                                                                                                                                                     |  |  |  |  |

| 0<br>ARMF | <ul> <li>Arm Flag Bit — The ARMF bit indicates whether the debugger is waiting for trigger or waiting for the FIFO to fill.</li> <li>While DBGEN = 1, this status bit is a read-only image of the ARM bit in DBGC. See Section 18.4.4.2, "Arming the DBG Module" for more information.</li> <li>0 Debugger not armed</li> <li>1 Debugger armed</li> </ul> |  |  |  |  |

<sup>1</sup> When BRKEN = 0, TAG is do not care (x in the table).

$^{2}$  In end trace configurations (BEGIN = 0) where a CPU breakpoint is enabled (BRKEN = 1), TRGSEL should agree with TAG. In this case, where TRGSEL = 0 to select no opcode tracking qualification and TAG = 1 to specify a tag-type CPU breakpoint, the CPU breakpoint would not take effect until sometime after the FIFO stopped storing values. Depending on program loops or interrupts, the delay could be very long.

$^{3}$  In end trace configurations (BEGIN = 0) where a CPU breakpoint is enabled (BRKEN = 1), TRGSEL should agree with TAG. In this case, where TRGSEL = 1 to select opcode tracking qualification and TAG = 0 to specify a force-type CPU breakpoint, the CPU breakpoint would erroneously take effect before the FIFO stopped storing values and the debug run would not complete normally.

4 In begin trace configurations (BEGIN = 1) where a CPU breakpoint is enabled (BRKEN = 1), TAG should not be set to 1. In begin trace debug runs, the CPU breakpoint corresponds to the FIFO full condition which does not correspond to a taggable instruction fetch.

# 18.4.5 FIFO

The FIFO is an eight word deep FIFO. In all trigger modes except for event only, the data stored in the FIFO will be change of flow addresses. In the event only trigger modes only the data bus value corresponding to the event is stored. In event only trigger modes, the high byte of the valid data from the FIFO will always read a 0x00 and the extended information byte in DBGFX will always read 0x00.

### 18.4.5.1 Storing Data in FIFO

In all trigger modes except for the event only modes, the address stored in the FIFO will be determined by the change of flow indicators from the core. The signal core\_cof[1] indicates the current core address is the destination address of an indirect JSR or JMP instruction, or a RTS, RTC, or RTI instruction or interrupt vector and the destination address should be stored. The signal core\_cof[0] indicates that a conditional branch was taken and that the source address of the conditional branch should be stored.

### 18.4.5.2 Storing with Begin-Trigger

Storing with Begin-Trigger can be used in all trigger modes. Once the DBG module is enabled and armed in the begin-trigger mode, data is not stored in the FIFO until the trigger condition is met. Once the trigger condition is met the DBG module will remain armed until 8 words are stored in the FIFO. If the core\_cof[1] signal becomes asserted, the current address is stored in the FIFO. If the core\_cof[0] signal becomes asserted, the address registered during the previous last cycle is decremented by two and stored in the FIFO.

### 18.4.5.3 Storing with End-Trigger

Storing with End-Trigger cannot be used in event-only trigger modes. Once the DBG module is enabled and armed in the end-trigger mode, data is stored in the FIFO until the trigger condition is met. If the core\_cof[1] signal becomes asserted, the current address is stored in the FIFO. If the core\_cof[0] signal becomes asserted, the address registered during the previous last cycle is decremented by two and stored in the FIFO. When the trigger condition is met, the ARM and ARMF will be cleared and no more data will be stored. In non-event only end-trigger modes, if the trigger is at a change of flow address the trigger event will be stored in the FIFO.

### 18.4.5.4 Reading Data from FIFO

The data stored in the FIFO can be read using BDM commands provided the DBG module is enabled and not armed (DBGEN=1 and ARM=0). The FIFO data is read out first-in-first-out. By reading the CNT bits

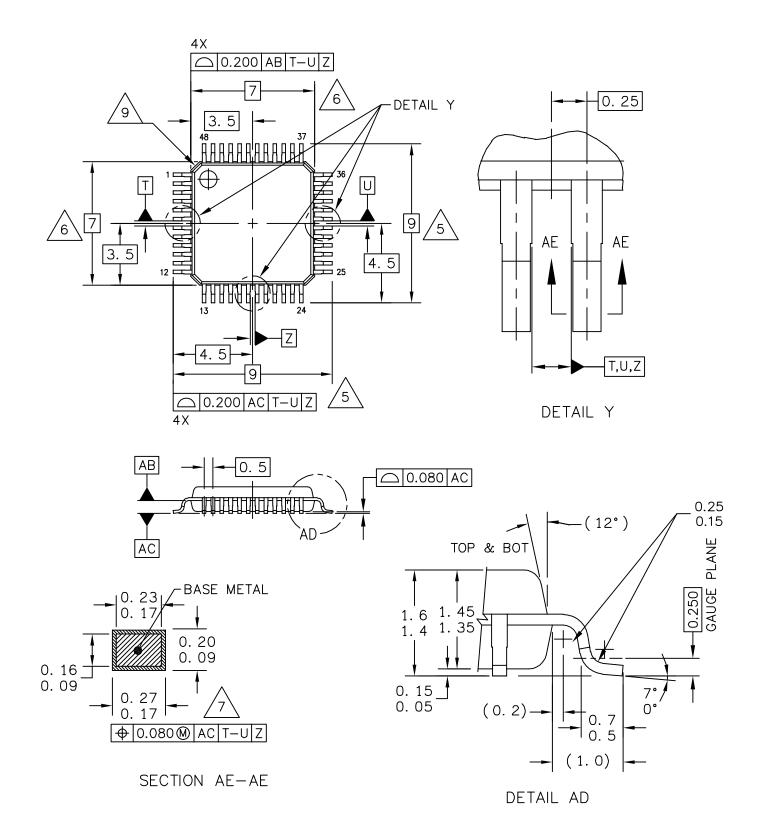

| © FREESCALE SEMICONDUCTOR, INC.<br>All rights reserved. |  | LOUTLINE       | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------|--|----------------|------------------|-------------|

| TITLE:                                                  |  | ): 98ASH00962A | REV: G           |             |

| LQFP, 48 LEAD, 0.                                       |  | CASE NUMBER    | 8: 932–03        | 14 APR 2005 |

| (7.0 X 7.0 X                                            |  | STANDARD: JE   | DEC MS-026-BBC   |             |