Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 39                                                         |

| Program Memory Size        | 96KB (96K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 2K x 8                                                     |

| RAM Size                   | 6K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 16x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 48-LQFP                                                    |

| Supplier Device Package    | 48-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dz96clf |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section Number**

## Title

## Page

| 10.6 | Application Information          | 229 |

|------|----------------------------------|-----|

|      | 10.6.1 External Pins and Routing | 229 |

|      | 10.6.2 Sources of Error          | 230 |

## Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | Introduction                   |                      |

|------|--------------------------------|----------------------|

|      | 11.1.1 IIC1 Configuration      | Information          |

|      | 11.1.2 Features                |                      |

|      | 11.1.3 Modes of Operation      |                      |

|      | 11.1.4 Block Diagram           |                      |

| 11.2 | External Signal Description    |                      |

|      | 11.2.1 SCL — Serial Cloc       | k Line               |

|      | 11.2.2 SDA — Serial Data       | Line                 |

| 11.3 | Register Definition            |                      |

|      | 11.3.1 IIC Address Registe     | er (IICxA)           |

|      | 11.3.2 IIC Frequency Divi      | der Register (IICxF) |

|      | 11.3.3 IIC Control Registe     | r (IICxC1)           |

|      | 11.3.4 IIC Status Register     | (IICxS)              |

|      | 11.3.5 IIC Data I/O Regist     | er (IICxD)           |

|      | 11.3.6 IIC Control Registe     | r 2 (IICxC2)         |

| 11.4 | Functional Description         |                      |

|      | 11.4.1 IIC Protocol            |                      |

|      | 11.4.2 10-bit Address          |                      |

|      | 11.4.3 General Call Addre      | ss                   |

| 11.5 | Resets                         |                      |

| 11.6 | Interrupts                     |                      |

|      | 11.6.1 Byte Transfer Intern    | upt                  |

|      | 11.6.2 Address Detect Inte     | rrupt                |

|      | 11.6.3 Arbitration Lost Int    | errupt               |

| 11.7 | Initialization/Application Inf | formation            |

# Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

| 12.1 | Introduction                              |  |

|------|-------------------------------------------|--|

|      | 12.1.1 Features                           |  |

|      | 12.1.2 Modes of Operation                 |  |

|      | 12.1.3 Block Diagram                      |  |

| 12.2 | External Signal Description               |  |

|      | 12.2.1 RXCAN — CAN Receiver Input Pin     |  |

|      | 12.2.2 TXCAN — CAN Transmitter Output Pin |  |

|      | 12.2.3 CAN System                         |  |

|      |                                           |  |

# **Section Number**

## Title

## Page

| 12.3 | Register Definition                                                   |  |

|------|-----------------------------------------------------------------------|--|

|      | 12.3.1 MSCAN Control Register 0 (CANCTL0)                             |  |

|      | 12.3.2 MSCAN Control Register 1 (CANCTL1)                             |  |

|      | 12.3.3 MSCAN Bus Timing Register 0 (CANBTR0)                          |  |

|      | 12.3.4 MSCAN Bus Timing Register 1 (CANBTR1)                          |  |

|      | 12.3.5 MSCAN Receiver Interrupt Enable Register (CANRIER)             |  |

|      | 12.3.6 MSCAN Transmitter Flag Register (CANTFLG)                      |  |

|      | 12.3.7 MSCAN Transmitter Interrupt Enable Register (CANTIER)          |  |

|      | 12.3.8 MSCAN Transmitter Message Abort Request Register (CANTARQ)     |  |

|      | 12.3.9 MSCAN Transmitter Message Abort Acknowledge Register (CANTAAK) |  |

|      | 12.3.10MSCAN Transmit Buffer Selection Register (CANTBSEL)            |  |

|      | 12.3.11MSCAN Identifier Acceptance Control Register (CANIDAC)         |  |

|      | 12.3.12MSCAN Miscellaneous Register (CANMISC)                         |  |

|      | 12.3.13MSCAN Receive Error Counter (CANRXERR)                         |  |

|      | 12.3.14MSCAN Transmit Error Counter (CANTXERR)                        |  |

|      | 12.3.15MSCAN Identifier Acceptance Registers (CANIDAR0-7)             |  |

|      | 12.3.16MSCAN Identifier Mask Registers (CANIDMR0-CANIDMR7)            |  |

| 12.4 | Programmer's Model of Message Storage                                 |  |

|      | 12.4.1 Identifier Registers (IDR0–IDR3)                               |  |

|      | 12.4.2 IDR0–IDR3 for Standard Identifier Mapping                      |  |

|      | 12.4.3 Data Segment Registers (DSR0-7)                                |  |

|      | 12.4.4 Data Length Register (DLR)                                     |  |

|      | 12.4.5 Transmit Buffer Priority Register (TBPR)                       |  |

|      | 12.4.6 Time Stamp Register (TSRH–TSRL)                                |  |

| 12.5 | Functional Description                                                |  |

|      | 12.5.1 General                                                        |  |

|      | 12.5.2 Message Storage                                                |  |

|      | 12.5.3 Identifier Acceptance Filter                                   |  |

|      | 12.5.4 Modes of Operation                                             |  |

|      | 12.5.5 Low-Power Options                                              |  |

|      | 12.5.6 Reset Initialization                                           |  |

|      | 12.5.7 Interrupts                                                     |  |

| 12.6 | Initialization/Application Information                                |  |

|      | 12.6.1 MSCAN initialization                                           |  |

|      | 12.6.2 Bus-Off Recovery                                               |  |

|      | -                                                                     |  |

# Chapter 13 Serial Peripheral Interface (S08SPIV3)

| 13.1 | Introduction                    | .307 |

|------|---------------------------------|------|

|      | 13.1.1 Features                 | .309 |

|      | 13.1.2 Block Diagrams           | .309 |

|      | 13.1.3 SPI Baud Rate Generation |      |

|      |                                 |      |

# **Section Number**

### Title

Page

# Chapter 17 Development Support

| 17.1 | Introducti        | on                                                   | 379 |

|------|-------------------|------------------------------------------------------|-----|

|      | 17.1.1 F          | Forcing Active Background                            | 379 |

|      | 17.1.2 F          | Features                                             | 380 |

| 17.2 | Backgrou          | nd Debug Controller (BDC)                            | 380 |

|      | 17.2.1 E          | 3KGD Pin Description                                 | 381 |

|      | 17.2.2 0          | Communication Details                                | 381 |

|      | 17.2.3 E          | 3DC Commands                                         | 385 |

|      | 17.2.4 E          | 3DC Hardware Breakpoint                              | 387 |

| 17.3 | Register <b>E</b> | Definition                                           | 387 |

|      | 17.3.1 E          | BDC Registers and Control Bits                       | 388 |

|      | 17.3.2 S          | System Background Debug Force Reset Register (SBDFR) | 390 |

# Chapter 18 Debug Module (S08DBGV3) (128K)

| 18.1 | Introduction                       |     |

|------|------------------------------------|-----|

|      | 18.1.1 Features                    |     |

|      | 18.1.2 Modes of Operation          |     |

|      | 18.1.3 Block Diagram               |     |

| 18.2 | Signal Description                 |     |

| 18.3 | Memory Map and Registers           |     |

|      | 18.3.1 Module Memory Map           |     |

|      | 18.3.2                             | 396 |

|      | 18.3.3 Register Descriptions       |     |

| 18.4 | Functional Description             | 410 |

|      | 18.4.1 Comparator                  |     |

|      | 18.4.2 Breakpoints                 |     |

|      | 18.4.3 Trigger Selection           | 411 |

|      | 18.4.4 Trigger Break Control (TBC) |     |

|      | 18.4.5 FIFO                        |     |

|      | 18.4.6 Interrupt Priority          |     |

|      | Resets                             |     |

| 18.6 | Interrupts                         |     |

| 18.7 | Electrical Specifications          |     |

## Appendix A Electrical Characteristics

| A.1 | Introduction             | 419 |

|-----|--------------------------|-----|

| A.2 | Parameter Classification | 419 |

| A.3 | Absolute Maximum Ratings | 419 |

|     | Thermal Characteristics  |     |

address of the FLASH memory location to be addressed. When accessing data using LBP, the contents of LAP2:LAP0 will increment after the read or write is complete.

Accessing LBP does the same thing as accessing LWP. The MMU register ordering of LWP followed by LBP, allow the user to access data by words using the LDHX or STHX instructions with the address of the LWP register.

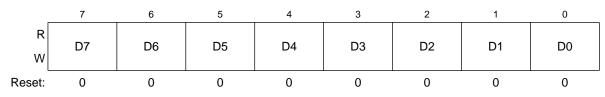

Figure 4-8. Linear Byte Post Increment Register (LBP)

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>D7:D0 | Reads of this register will first return the data value pointed to by the linear address pointer, LAP2:LAP0 and then will increment LAP2:LAP0. Writes to this register will first write the data value to the memory location specified by the linear address pointer and then will increment LAP2:LAP0. Writes to this register are most commonly used when writing to the FLASH block(s) during programming. |

### 4.4.3.5 Linear Byte Register (LB)

This register is one of three data registers that the user can use to access any FLASH memory location in the extended address map. When LB is accessed the contents of LAP2:LAP0 make up the extended address of the FLASH memory location to be addressed.

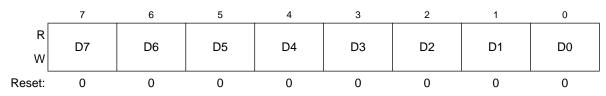

Figure 4-9. Linear Byte Register (LB)

#### Table 4-10. Linear Data Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>D7:D0 | Reads of this register returns the data value pointed to by the linear address pointer, LAP2:LAP0. Writes to this register will write the data value to the memory location specified by the linear address pointer. Writes to this register are most commonly used when writing to the FLASH block(s) during programming. |

## 4.4.3.6 Linear Address Pointer Add Byte Register (LAPAB)

The user can increase or decrease the contents of LAP2:LAP0 by writing a 2s complement value to LAPAB. The value written will be added to the current contents of LAP2:LAP0.

NP

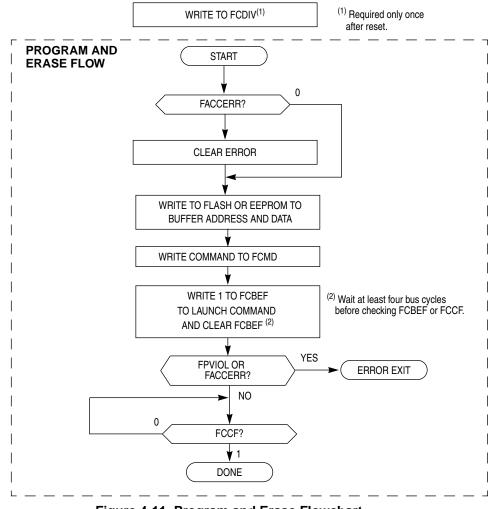

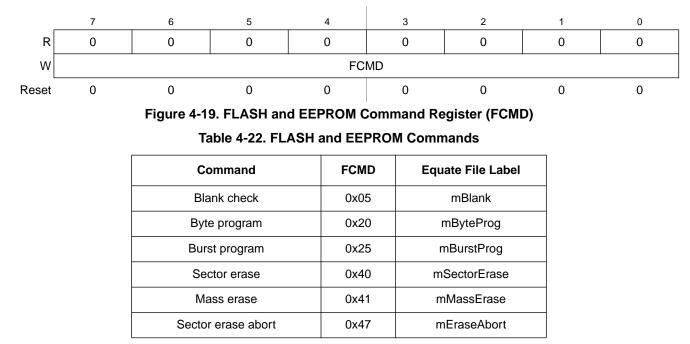

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-11 is a flowchart for executing all of the commands except for burst programming and sector erase abort.

4. Wait until the FCCF bit in FSTAT is set. As soon as FCCF= 1, the operation has completed successfully.

Figure 4-11. Program and Erase Flowchart

# 4.6.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When

Command Execution," for a detailed discussion of FLASH and EEPROM programming and erase operations.

It is not necessary to perform a blank check command after a mass erase operation. Only blank check is required as part of the security unlocking mechanism.

Chapter 5 Resets, Interrupts, and General System Control

# 5.8.2 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                   | 7   | 6                   | 5                   | 4                   | 3                   | 2              | 1    | 0 |

|---------------------|-----|---------------------|---------------------|---------------------|---------------------|----------------|------|---|

| R                   | POR | PIN                 | COP                 | ILOP                | ILAD                | LOC            | LVD  | 0 |

| w                   |     | Wi                  | iting 0x55, 0xA     | A to SRS addr       | ess clears CO       | P watchdog tim | ier. |   |

| POR:                | 1   | 0                   | 0                   | 0                   | 0                   | 0              | 1    | 0 |

| LVD:                | 0   | 0                   | 0                   | 0                   | 0                   | 0              | 1    | 0 |

| Any other<br>reset: | 0   | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | Note <sup>(1)</sup> | 0              | 0    | 0 |

<sup>1</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

#### Figure 5-3. System Reset Status (SRS)

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                 |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                         |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPT bits = 0:0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                      |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP<br>instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is<br>considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.0Reset not caused by an illegal opcode.1Reset caused by an illegal opcode. |

| 3<br>ILAD | <ul> <li>Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.</li> <li>0 Reset not caused by an illegal address.</li> <li>1 Reset caused by an illegal address.</li> </ul>                                                                                                                                                    |

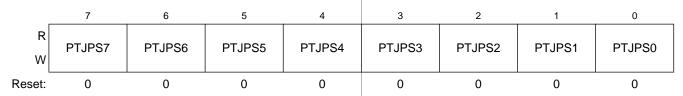

## 6.5.9.7 Port J Interrupt Pin Select Register (PTJPS)

Figure 6-58. Port J Interrupt Pin Select Register (PTJPS)

#### Table 6-56. PTJPS Register Field Descriptions

| Field | Description                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port J Interrupt Pin Selects — Each of the PTJPSn bits enable the corresponding port J interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

### 6.5.9.8 Port J Interrupt Edge Select Register (PTJES)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTJES7 | PTJES6 | PTJES5 | PTJES4 | PTJES3 | PTJES2 | PTJES1 | PTJES0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-59. Port J Edge Select Register (PTJES)

#### Table 6-57. PTJES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port J Edge Selects — Each of the PTJESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

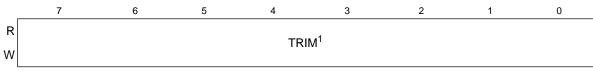

# 8.3.3 MCG Trim Register (MCGTRM)

#### Figure 8-5. MCG Trim Register (MCGTRM)

<sup>1</sup> A value for TRIM is loaded during reset from a factory programmed location when not in any BDM mode. If in a BDM mode, a default value of 0x80 is loaded.

| Field       | Description                                                                                                                                                                                                                                                                                                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>TRIM | MCG <b>Trim Setting</b> — Controls the internal reference clock frequency by controlling the internal reference clock period. The TRIM bits are binary weighted (i.e., bit 1 will adjust twice as much as bit 0). Increasing the binary value in TRIM will increase the period, and decreasing the value will decrease the period. |

|             | An additional fine trim bit is available in MCGSC as the FTRIM bit.                                                                                                                                                                                                                                                                |

|             | If a TRIM[7:0] value stored in nonvolatile memory is to be used, it's the user's responsibility to copy that value from the nonvolatile memory location to this register.                                                                                                                                                          |

#### Table 8-5. MCG Trim Register Field Descriptions

### 8.4.1.6 PLL Bypassed External (PBE)

In PLL bypassed external (PBE) mode, the MCGOUT clock is derived from the external reference clock and the PLL is operational but its output clock is not used. This mode is useful to allow the PLL to acquire its target frequency while the MCGOUT clock is driven from the external reference clock.

The PLL bypassed external mode is entered when all the following conditions occur:

- CLKS bits are written to 10

- IREFS bit is written to 0

- PLLS bit is written to 1

- RDIV bits are written to divide reference clock to be within the range of 1 MHz to 2 MHz

- LP bit is written to 0

In PLL bypassed external mode, the MCGOUT clock is derived from the external reference clock. The external reference clock which is enabled can be an external crystal/resonator or it can be another external clock source. The PLL clock frequency locks to a multiplication factor, as selected by the VDIV bits, times the external reference frequency, as selected by the RDIV, RANGE and DIV32 bits. If BDM is enabled then the MCGLCLK is derived from the DCO (open-loop mode) divided by two. If BDM is not enabled then the FLL is disabled in a low power state.

In this mode, the DRST bit reads 0 regardless of whether the DRS bit is set to 1 or 0.

### 8.4.1.7 Bypassed Low Power Internal (BLPI)

The bypassed low power internal (BLPI) mode is entered when all the following conditions occur:

- CLKS bits are written to 01

- IREFS bit is written to 1

- PLLS bit is written to 0

- LP bit is written to 1

- BDM mode is not active

In bypassed low power internal mode, the MCGOUT clock is derived from the internal reference clock.

The PLL and the FLL are disabled at all times in BLPI mode and the MCGLCLK will not be available for BDC communications If the BDM becomes active the mode will switch to FLL bypassed internal (FBI) mode.

In this mode, the DRST bit reads 0 regardless of whether the DRS bit is set to 1 or 0.

## 8.4.1.8 Bypassed Low Power External (BLPE)

The bypassed low power external (BLPE) mode is entered when all the following conditions occur:

- CLKS bits are written to 10

- IREFS bit is written to 0

- PLLS bit is written to 0 or 1

- LP bit is written to 1

# Chapter 9 5-V Analog Comparator (S08ACMPV3)

# 9.1 Introduction

The analog comparator module (ACMP) provides a circuit for comparing two analog input voltages or for comparing one analog input voltage to an internal reference voltage. The comparator circuit is designed to operate across the full range of the supply voltage (rail-to-rail operation).

All MC9S08DZ128 Series MCUs have two full function ACMPs. MCUs in the 48-pin package have two ACMPs, but the output of ACMP2 is not accessible.

### NOTE

MC9S08DZ128 Series devices operate at a higher voltage range (2.7 V to 5.5 V) and do not include stop1 mode. Please ignore references to stop1.

ACMP2O is not available in the 48-pin package.

# 9.1.1 ACMP Configuration Information

When using the bandgap reference voltage for input to ACMP+, the user must enable the bandgap buffer by setting BGBE =1 in SPMSC1 see Section 5.8.7, "System Power Management Status and Control 1 Register (SPMSC1)." For value of bandgap voltage reference see Appendix A, "Electrical Characteristics"

# 9.4 Functional Description

The analog comparator can be used to compare two analog input voltages applied to ACMPx+ and ACMPx-; or it can be used to compare an analog input voltage applied to ACMPx- with an internal bandgap reference voltage. ACBGS is used to select between the bandgap reference voltage or the ACMPx+ pin as the input to the non-inverting input of the analog comparator. The comparator output is high when the non-inverting input is greater than the inverting input, and is low when the non-inverting input is less than the inverting input. ACMOD is used to select the condition which will cause ACF to be set. ACF can be set on a rising edge of the comparator output, a falling edge of the comparator output, or either a rising or a falling edge (toggle). The comparator output can be read directly through ACO. The comparator output can be driven onto the ACMPxO pin using ACOPE.

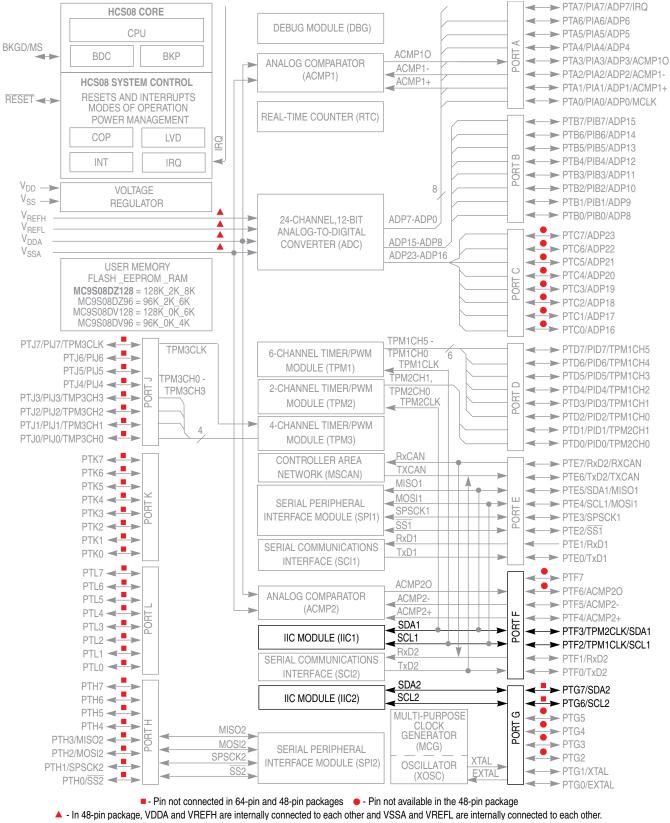

#### Chapter 11 Inter-Integrated Circuit (S08IICV2)

Figure 11-1. MC9S08DZ128 Block Diagram with IIC Highlighted

#### Table 11-9. IICxC2 Field Descriptions

| Field           | Description                                                                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>GCAEN      | <ul> <li>General Call Address Enable. The GCAEN bit enables or disables general call address.</li> <li>0 General call address is disabled</li> <li>1 General call address is enabled</li> </ul> |

| 6<br>ADEXT      | <ul> <li>Address Extension. The ADEXT bit controls the number of bits used for the slave address.</li> <li>0 7-bit address scheme</li> <li>1 10-bit address scheme</li> </ul>                   |

| 2–0<br>AD[10:8] | Slave Address. The AD[10:8] field contains the upper three bits of the slave address in the 10-bit address scheme. This field is only valid when the ADEXT bit is set.                          |

# 11.4 Functional Description

This section provides a complete functional description of the IIC module.

## 11.4.1 IIC Protocol

The IIC bus system uses a serial data line (SDA) and a serial clock line (SCL) for data transfer. All devices connected to it must have open drain or open collector outputs. A logic AND function is exercised on both lines with external pull-up resistors. The value of these resistors is system dependent.

Normally, a standard communication is composed of four parts:

- Start signal

- Slave address transmission

- Data transfer

- Stop signal

The stop signal should not be confused with the CPU stop instruction. The IIC bus system communication is described briefly in the following sections and illustrated in Figure 11-9.

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TDRE | Transmit Data Register Empty Flag — TDRE is set out of reset and when a transmit data value transfers from the transmit data buffer to the transmit shifter, leaving room for a new character in the buffer. To clear TDRE, read SCIxS1 with TDRE = 1 and then write to the SCI data register (SCIxD).         0       Transmit data register (buffer) full.         1       Transmit data register (buffer) empty.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6<br>TC   | Transmission Complete Flag — TC is set out of reset and when TDRE = 1 and no data, preamble, or break character is being transmitted.         0 Transmitter active (sending data, a preamble, or a break).         1 Transmitter idle (transmission activity complete).         TC is cleared automatically by reading SCIxS1 with TC = 1 and then doing one of the following three things:         • Write to the SCI data register (SCIxD) to transmit new data         • Queue a preamble by changing TE from 0 to 1         • Queue a break character by writing 1 to SBK in SCIxC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5<br>RDRF | Receive Data Register Full Flag — RDRF becomes set when a character transfers from the receive shifter into the receive data register (SCIxD). To clear RDRF, read SCIxS1 with RDRF = 1 and then read the SCI data register (SCIxD).         0       Receive data register empty.         1       Receive data register full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4<br>IDLE | Idle Line Flag — IDLE is set when the SCI receive line becomes idle for a full character time after a period of activity. When ILT = 0, the receiver starts counting idle bit times after the start bit. So if the receive character is all 1s, these bit times and the stop bit time count toward the full character time of logic high (10 or 11 bit times depending on the M control bit) needed for the receiver to detect an idle line. When ILT = 1, the receiver doesn't start counting idle bit times until after the stop bit. So the stop bit and any logic high bit times at the end of the previous character do not count toward the full character time of logic high needed for the receiver to detect an idle line.         To clear IDLE, read SCIxS1 with IDLE = 1 and then read the SCI data register (SCIxD). After IDLE has been cleared, it cannot become set again until after a new character has been received and RDRF has been set. IDLE will get set only once even if the receive line remains idle for an extended period.         0       No idle line detected.         1       Idle line was detected. |

| 3<br>OR   | <ul> <li>Receiver Overrun Flag — OR is set when a new serial character is ready to be transferred to the receive data register (buffer), but the previously received character has not been read from SCIxD yet. In this case, the new character (and all associated error information) is lost because there is no room to move it into SCIxD. To clear OR, read SCIxS1 with OR = 1 and then read the SCI data register (SCIxD).</li> <li>0 No overrun.</li> <li>1 Receive overrun (new SCI data lost).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2<br>NF   | <ul> <li>Noise Flag — The advanced sampling technique used in the receiver takes seven samples during the start bit and three samples in each data bit and the stop bit. If any of these samples disagrees with the rest of the samples within any bit time in the frame, the flag NF will be set at the same time as the flag RDRF gets set for the character. To clear NF, read SCIxS1 and then read the SCI data register (SCIxD).</li> <li>0 No noise detected.</li> <li>1 Noise detected in the received character in SCIxD.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Table 14-6. SCIxS1 Field Descriptions

Chapter 16 Timer/PWM Module (S08TPMV3)

- TPMxCnVH:L = (TPMxMODH:L 1) [SE110-TPM case 2]

- In this case, the TPM v3 produces almost 100% duty cycle. Instead, the TPM v2 produces 0% duty cycle.

- TPMxCnVH:L is changed from 0x0000 to a non-zero value [SE110-TPM case 3 and 5]

In this case, the TPM v3 waits for the start of a new PWM period to begin using the new duty cycle setting. Instead, the TPM v2 changes the channel output at the middle of the current PWM period (when the count reaches 0x0000).

- TPMxCnVH:L is changed from a non-zero value to 0x0000 [SE110-TPM case 4]

In this case, the TPM v3 finishes the current PWM period using the old duty cycle setting.

Instead, the TPM v2 finishes the current PWM period using the new duty cycle setting.

- 6. Write to TPMxMODH:L registers in BDM mode (Section 16.3.3, "TPM Counter Modulo Registers (TPMxMODH:TPMxMODL))

In the TPM v3 a write to TPMxSC register in BDM mode clears the write coherency mechanism of TPMxMODH:L registers. Instead, in the TPM v2 this coherency mechanism is not cleared when there is a write to TPMxSC register.

**Chapter 17 Development Support**

# 17.1.2 Features

Features of the BDC module include:

- Single pin for mode selection and background communications

- BDC registers are not located in the memory map

- SYNC command to determine target communications rate

- Non-intrusive commands for memory access

- Active background mode commands for CPU register access

- GO and TRACE1 commands

- BACKGROUND command can wake CPU from stop or wait modes

- One hardware address breakpoint built into BDC

- Oscillator runs in stop mode, if BDC enabled

- COP watchdog disabled while in active background mode

# 17.2 Background Debug Controller (BDC)

All MCUs in the HCS08 Family contain a single-wire background debug interface that supports in-circuit programming of on-chip nonvolatile memory and sophisticated non-intrusive debug capabilities. Unlike debug interfaces on earlier 8-bit MCUs, this system does not interfere with normal application resources. It does not use any user memory or locations in the memory map and does not share any on-chip peripherals.

BDC commands are divided into two groups:

- Active background mode commands require that the target MCU is in active background mode (the user program is not running). Active background mode commands allow the CPU registers to be read or written, and allow the user to trace one user instruction at a time, or GO to the user program from active background mode.

- Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

## 18.3.3 Register Descriptions

This section consists of the DBG register descriptions in address order.

Note: For all registers below, consider: U = Unchanged, bit maintain its value after reset.

### 18.3.3.1 Debug Comparator A High Register (DBGCAH)

Module Base + 0x0000

|                               | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0     |

|-------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| R<br>W                        | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| POR<br>or non-<br>end-run     | 1      | 1      | 1      | 1      | 1      | 1      | 1     | 1     |

| Reset<br>end-run <sup>1</sup> | U      | U      | U      | U      | U      | U      | U     | U     |

#### Figure 18-2. Debug Comparator A High Register (DBGCAH)

<sup>1</sup> In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, the bits in this register do not change after reset.

#### **Table 18-3. DBGCAH Field Descriptions**

|   | Field | Description                                                                                                                                                                                                                                                                                                |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B |       | <ul> <li>Comparator A High Compare Bits — The Comparator A High compare bits control whether Comparator A will compare the address bus bits [15:8] to a logic 1 or logic 0.</li> <li>0 Compare corresponding address bit to a logic 0</li> <li>1 Compare corresponding address bit to a logic 1</li> </ul> |

## 18.3.3.2 Debug Comparator A Low Register (DBGCAL)

7 6 5 4 3 2 1 0 R Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 W POR or non-1 1 1 1 1 1 1 0 end-run Reset U U U U U U U U end-run<sup>1</sup>

#### Figure 18-3. Debug Comparator A Low Register (DBGCAL)

<sup>1</sup> In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, the bits in this register do not change after reset.

MC9S08DZ128 Series Data Sheet, Rev. 1

Module Base + 0x0001

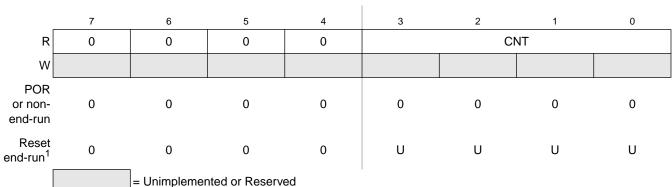

### 18.3.3.16 Debug Count Status Register (DBGCNT)

Module Base + 0x000F

#### Figure 18-17. Debug Count Status Register (DBGCNT)

<sup>1</sup> In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, the CNT[3:0] bits do not change after reset.

#### Table 18-19. DBGS Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–0<br>CNT | <b>FIFO Valid Count Bits</b> — The CNT bits indicate the amount of valid data stored in the FIFO. Table 18-20 shows the correlation between the CNT bits and the amount of valid data in FIFO. The CNT will stop after a count to eight even if more data is being stored in the FIFO. The CNT bits are cleared when the DBG module is armed, and the count is incremented each time a new word is captured into the FIFO. The host development system is responsible for checking the value in CNT[3:0] and reading the correct number of words from the FIFO because the count does not decrement as data is read out of the FIFO at the end of a trace run. |

| CNT Value | Meaning       |

|-----------|---------------|

| 0000      | No data valid |

| 0001      | 1 word valid  |

| 0010      | 2 words valid |

| 0011      | 3 words valid |

| 0100      | 4 words valid |

| 0101      | 5 words valid |

| 0110      | 6 words valid |

| 0111      | 7 words valid |

| 1000      | 8 words valid |

#### Table 18-20. CNT Bits

**Appendix A Electrical Characteristics**

| Num | С | Rating                                                                                             | Symbol                        | Min    | Typical            | Max                                                      | Unit              |

|-----|---|----------------------------------------------------------------------------------------------------|-------------------------------|--------|--------------------|----------------------------------------------------------|-------------------|

| 15  | D | PLL reference frequency range                                                                      | f <sub>pll_ref</sub>          | 1.0    | _                  | 2.0                                                      | MHz               |

| 16  | т | RMS frequency variation of a single clock cycle measured 2 ms after reference edge. <sup>6</sup>   | f <sub>pll_cycjit_2ms</sub>   | _      | 0.590 <sup>5</sup> | _                                                        | %f <sub>pll</sub> |

| 17  | Т | Maximum frequency variation averaged over 2 ms window.                                             | f <sub>pll_maxjit_2ms</sub>   | _      | 0.001              | _                                                        | %f <sub>pll</sub> |

| 18  | т | RMS frequency variation of a single clock cycle measured 625 ns after reference edge. <sup>7</sup> | f <sub>pll_cycjit_625ns</sub> | _      | 0.566 <sup>5</sup> | _                                                        | %f <sub>pll</sub> |

| 19  | Т | Maximum frequency variation averaged over 625 ns window.                                           | f <sub>pll_maxjit_625ns</sub> | —      | 0.113              | _                                                        | %f <sub>pll</sub> |

| 20  | D | Lock entry frequency tolerance <sup>8</sup>                                                        | D <sub>lock</sub>             | ± 1.49 |                    | ± 2.98                                                   | %                 |

| 21  | D | Lock exit frequency tolerance 9                                                                    | D <sub>unl</sub>              | ± 4.47 |                    | ± 5.97                                                   | %                 |

| 22  | D | Lock time - FLL                                                                                    | t <sub>fll_lock</sub>         |        | _                  | t <sub>fll_acquire+</sub><br>1075(1/ <sup>f</sup> int_t) | s                 |

#### Table A-12. MCG Frequency Specifications (Temperature Range = -40 to 125°C Ambient) (continued)

<sup>1</sup> This applies when TRIM register at value (0x80) and FTRIM control bit at value (0x0). These values load when in BDM modes.

<sup>2</sup> The resulting bus clock frequency should not exceed the maximum specified bus clock frequency of the device.

<sup>3</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bit is changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>4</sup> This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>5</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>BUS</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval. These jitter measurements are based upon a 40 MHz MCGOUT clock frequency.

<sup>6</sup> In some specifications, this value is described as, "Long term accuracy of PLL output clock (averaged over 2 ms)" with symbol "f<sub>pll jitter 2ms</sub>." The parameter is unchanged, but the description has been changed for clarification purposes.

<sup>7</sup> In some specifications, this value is described as "Jitter of PLL output clock measured over 625 ns" with symbol "f<sub>pll\_jitter\_625ns</sub>." The parameter is unchanged, but the description has been changed for clarification purposes.

<sup>8</sup> Below D<sub>lock</sub> minimum, the MCG is guaranteed to enter lock. Above D<sub>lock</sub> maximum, the MCG will not enter lock. But if the MCG is already in lock, then the MCG may stay in lock.

<sup>9</sup> Below D<sub>unl</sub> minimum, the MCG will not exit lock if already in lock. Above D<sub>unl</sub> maximum, the MCG is guaranteed to exit lock.