Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                 |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 53                                                         |

| Program Memory Size        | 96KB (96K x 8)                                             |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 2K x 8                                                     |

| RAM Size                   | 6K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 24x12b                                                 |

| Oscillator Type            | External                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 64-LQFP                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08dz96mlh |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section Number**

## Title

## Page

| 10.6 | Application Information          | 229 |

|------|----------------------------------|-----|

|      | 10.6.1 External Pins and Routing | 229 |

|      | 10.6.2 Sources of Error          | 230 |

## Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 11.1 | Introduction                   |                      |

|------|--------------------------------|----------------------|

|      | 11.1.1 IIC1 Configuration      | Information          |

|      | 11.1.2 Features                |                      |

|      | 11.1.3 Modes of Operation      |                      |

|      | 11.1.4 Block Diagram           |                      |

| 11.2 | External Signal Description    |                      |

|      | 11.2.1 SCL — Serial Cloc       | k Line               |

|      | 11.2.2 SDA — Serial Data       | Line                 |

| 11.3 | Register Definition            |                      |

|      | 11.3.1 IIC Address Registe     | er (IICxA)           |

|      | 11.3.2 IIC Frequency Divi      | der Register (IICxF) |

|      | 11.3.3 IIC Control Registe     | r (IICxC1)           |

|      | 11.3.4 IIC Status Register     | (IICxS)              |

|      | 11.3.5 IIC Data I/O Regist     | er (IICxD)           |

|      | 11.3.6 IIC Control Registe     | r 2 (IICxC2)         |

| 11.4 | Functional Description         |                      |

|      | 11.4.1 IIC Protocol            |                      |

|      | 11.4.2 10-bit Address          |                      |

|      | 11.4.3 General Call Addre      | ss                   |

| 11.5 | Resets                         |                      |

| 11.6 | Interrupts                     |                      |

|      | 11.6.1 Byte Transfer Intern    | upt                  |

|      | 11.6.2 Address Detect Inte     | rrupt                |

|      | 11.6.3 Arbitration Lost Int    | errupt               |

| 11.7 | Initialization/Application Inf | formation            |

# Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

| 12.1 | Introduction                              |  |

|------|-------------------------------------------|--|

|      | 12.1.1 Features                           |  |

|      | 12.1.2 Modes of Operation                 |  |

|      | 12.1.3 Block Diagram                      |  |

| 12.2 | External Signal Description               |  |

|      | 12.2.1 RXCAN — CAN Receiver Input Pin     |  |

|      | 12.2.2 TXCAN — CAN Transmitter Output Pin |  |

|      | 12.2.3 CAN System                         |  |

|      |                                           |  |

**Chapter 2 Pins and Connections**

$V_{\text{REFH}}$  and  $V_{\text{REFL}}$  are internally connected to  $V_{\text{DDA}}$  and  $V_{\text{SSA}}$ , respectively.

Figure 2-3. MC9S08DZ128 Series in 48-Pin LQFP

Chapter 2 Pins and Connections

| Pin Number |    |         | < Lowest <b>Priority</b> > Highest |                |                   |                     |  |

|------------|----|---------|------------------------------------|----------------|-------------------|---------------------|--|

| 100 64     |    | 0 64 48 |                                    | ort<br>terrupt | Alt 1             | Alt 2               |  |

| 51         | 33 | 25      | PTD2                               | PID2           |                   | TPM1CH0             |  |

| 52         | 34 | 26      | PTD3                               | PID3           |                   | TPM1CH1             |  |

| 53         | 35 | 27      | PTD4                               | PID4           |                   | TPM1CH2             |  |

| 54         | 36 | 28      | PTD5                               | PID5           |                   | TPM1CH3             |  |

| 55         | —  |         | PTH0                               |                |                   | SS2                 |  |

| 56         | —  | _       | PTH1                               |                |                   | SPSCK2              |  |

| 57         | —  | _       | PTH2                               |                |                   | MOSI2               |  |

| 58         | —  | _       | PTH3                               |                |                   | MISO2               |  |

| 59         | 37 |         | PTF7                               |                |                   |                     |  |

| 60         | —  | _       | PTL3                               |                |                   |                     |  |

| 61         | 38 | 29      |                                    |                |                   | V <sub>SS</sub>     |  |

| 62         | 39 | 30      |                                    |                |                   | V <sub>DD</sub>     |  |

| 63         | 40 | 31      | PTD6                               | PID6           |                   | TPM1CH4             |  |

| 64         | 41 | 32      | PTD7                               | PID7           |                   | TPM1CH5             |  |

| 65         | 42 | 33      |                                    |                | BKGD              | MS                  |  |

| 66         | —  |         | PTH4                               |                |                   |                     |  |

| 67         | —  |         | PTH5                               |                |                   |                     |  |

| 68         | —  |         | PTH6                               |                |                   |                     |  |

| 69         | —  |         | PTH7                               |                |                   |                     |  |

| 70         | 43 | _       | PTC0                               |                | ADP16             |                     |  |

| 71         | 44 | 34      | PTB0                               | PIB0           | ADP8              |                     |  |

| 72         | 45 | _       | PTC1                               |                | ADP17             |                     |  |

| 73         | 46 | 35      | PTA0                               | PIA0           | ADP0              | MCLK                |  |

| 74         | 47 | _       | PTC2                               |                | ADP18             |                     |  |

| 75         | 48 | 36      | PTB1                               | PIB1           | ADP9              |                     |  |

| 76         | 49 | 37      | PTA1                               | PIA1           | ADP1 <sup>4</sup> | ACMP1+ <sup>4</sup> |  |

| 77         | 50 | 38      | PTB2                               | PIB2           | ADP10             |                     |  |

| 78         | 51 | 39      | PTA2                               | PIA2           | ADP2 <sup>4</sup> | ACMP1-4             |  |

| 79         | 52 | _       | PTC3                               |                | ADP19             |                     |  |

| 80         | 53 | 40      | PTB3                               | PIB3           | ADP11             |                     |  |

| 81         | 54 | 41      | PTA3                               | PIA3           | ADP3              | ACMP10              |  |

| 82         | —  | _       | PTL4                               |                |                   |                     |  |

| 83         | —  | _       | PTK0                               |                |                   |                     |  |

| 84         | —  | _       | PTK1                               |                |                   |                     |  |

| 85         | —  | _       | PTK2                               |                |                   |                     |  |

| 86         | _  |         | PTK3                               |                |                   |                     |  |

| 87         | 55 | 40      |                                    |                |                   | V <sub>SSA</sub>    |  |

| 88         | 56 | 42      |                                    |                |                   | V <sub>REFL</sub>   |  |

Table 2-1. Pin Availability by Package Pin-Count (continued)

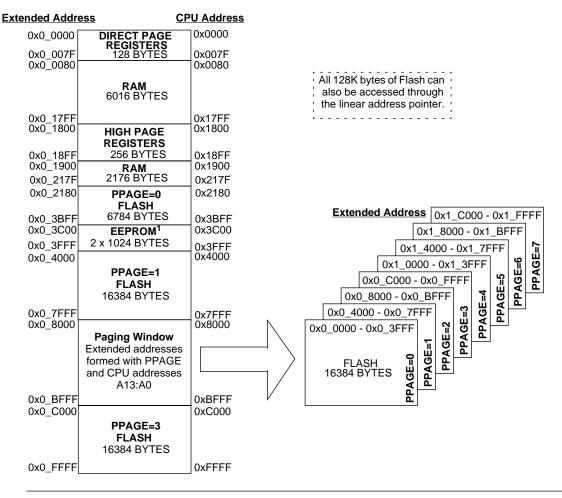

#### **Chapter 4 Memory**

<sup>1</sup> EEPROM address range shows half the total EEPROM. See Section 4.6.10, "EEPROM Mapping" for more

Figure 4-1. MC9S08DZ128 Series Memory Map

NP

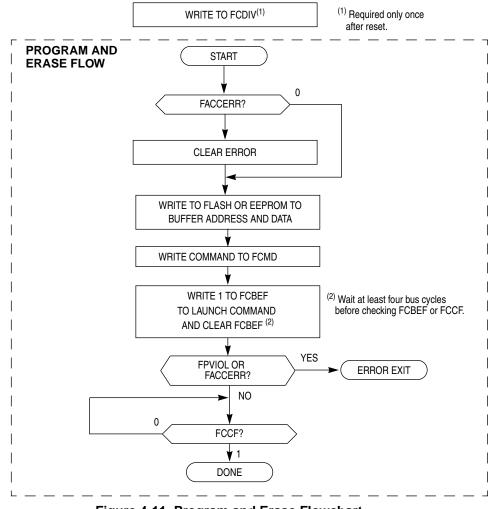

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-11 is a flowchart for executing all of the commands except for burst programming and sector erase abort.

4. Wait until the FCCF bit in FSTAT is set. As soon as FCCF= 1, the operation has completed successfully.

Figure 4-11. Program and Erase Flowchart

## 4.6.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When

### Table 4-13. FCDIV Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DIVLD  | <ul> <li>Divisor Loaded Status Flag — When set, this read-only status flag indicates that the FCDIV register has been written since reset. Reset clears this bit and the first write to this register causes this bit to become set regardless of the data written.</li> <li>0 FCDIV has not been written since reset; erase and program operations disabled for FLASH and EEPROM.</li> <li>1 FCDIV has been written since reset; erase and program operations enabled for FLASH and EEPROM.</li> </ul>                                                                                                                                                                     |

| 6<br>PRDIV8 | <ul> <li>Prescale (Divide) FLASH and EEPROM Clock by 8 (This bit is write once.)</li> <li>0 Clock input to the FLASH and EEPROM clock divider is the bus rate clock.</li> <li>1 Clock input to the FLASH and EEPROM clock divider is the bus rate clock divided by 8.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

| 5:0<br>DIV  | <b>Divisor for FLASH and EEPROM Clock Divider</b> — The FLASH and EEPROM clock divider divides the bus rate clock (or the bus rate clock divided by 8 if PRDIV8 = 1) by the value in the 6-bit DIV field plus one. The resulting frequency of the internal FLASH and EEPROM clock must fall within the range of 200 kHz to 150 kHz for proper FLASH and EEPROM operations. Program/Erase timing pulses are one cycle of this internal FLASH and EEPROM clock which corresponds to a range of 5 $\mu$ s to 6.7 $\mu$ s. The automated programming logic uses an integer number of these pulses to complete an erase or program operation. See Equation 4-1 and Equation 4-2. |

## 6.5.8.5 Port H Drive Strength Selection Register (PTHDS)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTHDS7 | PTHDS6 | PTHDS5 | PTHDS4 | PTHDS3 | PTHDS2 | PTHDS1 | PTHDS0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

Figure 6-51. Drive Strength Selection for Port H Register (PTHDS)

### Table 6-49. PTHDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTHDS[7:0] | <ul> <li>Output Drive Strength Selection for Port H Bits — Each of these control bits selects between low and high output drive for the associated PTH pin. For port H pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port H bit n.</li> <li>1 High output drive strength selected for port H bit n.</li> </ul> |

# Chapter 7 Central Processor Unit (S08CPUV5)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

## 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- 64-KB CPU address space with banked memory management unit for greater than 64 KB

- 16-bit stack pointer (any size stack anywhere in 64-KB CPU address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

### MC9S08DZ128 Series Data Sheet, Rev. 1

## 8.1.1 Features

Key features of the MCG module are:

- Frequency-locked loop (FLL)

- Internal or external reference can be used to control the FLL

- Phase-locked loop (PLL)

- Voltage-controlled oscillator (VCO)

- Modulo VCO frequency divider

- Phase/Frequency detector

- Integrated loop filter

- Lock detector with interrupt capability

- Internal reference clock

- Nine trim bits for accuracy

- Can be selected as the clock source for the MCU

- External reference clock

- Control for external oscillator

- Clock monitor with reset capability

- Can be selected as the clock source for the MCU

- Reference divider is provided

- Clock source selected can be divided down by 1, 2, 4, or 8

- BDC clock (MCGLCLK) is provided as a constant divide by 2 of the DCO output whether in an FLL or PLL mode.

- Two selectable digitally controlled oscillators (DCOs) optimized for different frequency ranges.

- Option to maximize DCO output frequency for a 32,768 Hz external reference clock source.

Chapter 8 Multi-Purpose Clock Generator (S08MCGV2)

# 8.3 Register Definition

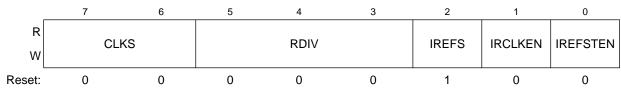

# 8.3.1 MCG Control Register 1 (MCGC1)

### Figure 8-3. MCG Control Register 1 (MCGC1)

### Table 8-1. MCG Control Register 1 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>CLKS   | Clock Source Select — Selects the system clock source.         00       Encoding 0 — Output of FLL or PLL is selected.         01       Encoding 1 — Internal reference clock is selected.         10       Encoding 2 — External reference clock is selected.         11       Encoding 3 — Reserved, defaults to 00.                                   |

| 5:3<br>RDIV   | <b>External Reference Divider</b> — Selects the amount to divide down the external reference clock. If the FLL is selected, the resulting frequency must be in the range 31.25 kHz to 39.0625 kHz. If the PLL is selected, the resulting frequency must be in the range 1 MHz to 2 MHz. See Table 8-2 and Table 8-3 for the divide-by factors.           |

| 2<br>IREFS    | Internal Reference Select — Selects the reference clock source.         1 Internal reference clock selected         0 External reference clock selected                                                                                                                                                                                                  |

| 1<br>IRCLKEN  | Internal Reference Clock Enable — Enables the internal reference clock for use as MCGIRCLK.<br>1 MCGIRCLK active<br>0 MCGIRCLK inactive                                                                                                                                                                                                                  |

| 0<br>IREFSTEN | <ul> <li>Internal Reference Stop Enable — Controls whether or not the internal reference clock remains enabled when the MCG enters stop mode.</li> <li>1 Internal reference clock stays enabled in stop if IRCLKEN is set or if MCG is in FEI, FBI, or BLPI mode before entering stop</li> <li>0 Internal reference clock is disabled in stop</li> </ul> |

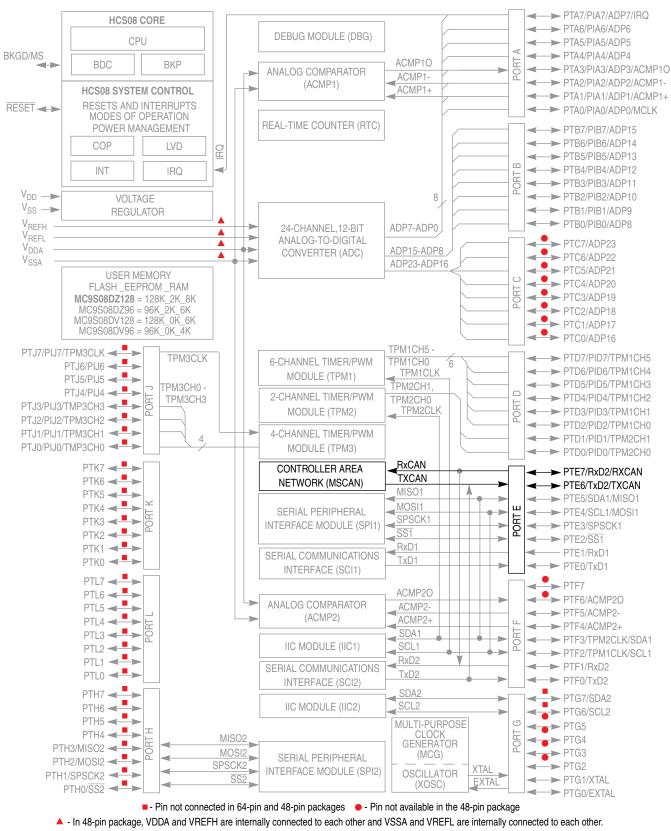

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

Figure 12-1. MC9S08DZ128 Block Diagram with MSCAN Highlighted

MC9S08DZ128 Series Data Sheet, Rev. 1

|      | Data Length Code |      |      |       |  |  |  |  |  |

|------|------------------|------|------|-------|--|--|--|--|--|

| DLC3 | DLC2             | DLC1 | DLC0 | Count |  |  |  |  |  |

| 0    | 0                | 0    | 0    | 0     |  |  |  |  |  |

| 0    | 0                | 0    | 1    | 1     |  |  |  |  |  |

| 0    | 0                | 1    | 0    | 2     |  |  |  |  |  |

| 0    | 0                | 1    | 1    | 3     |  |  |  |  |  |

| 0    | 1                | 0    | 0    | 4     |  |  |  |  |  |

| 0    | 1                | 0    | 1    | 5     |  |  |  |  |  |

| 0    | 1                | 1    | 0    | 6     |  |  |  |  |  |

| 0    | 1                | 1    | 1    | 7     |  |  |  |  |  |

| 1    | 0                | 0    | 0    | 8     |  |  |  |  |  |

Table 12-33. Data Length Codes

## 12.4.5 Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message transmit buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

- All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (start of frame) is sent.

- The transmission buffer with the lowest local priority field wins the prioritization.

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _ |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|---|

| R<br>W | PRIO7 | PRIO6 | PRIO5 | PRIO4 | PRIO3 | PRIO2 | PRIO1 | PRIO0 |   |

| Reset: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |   |

Figure 12-35. Transmit Buffer Priority Register (TBPR)

Read: Anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

Write: Anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

# 12.4.6 Time Stamp Register (TSRH–TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer as soon as a message has been acknowledged on the CAN bus (see

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

# 12.5.2 Message Storage

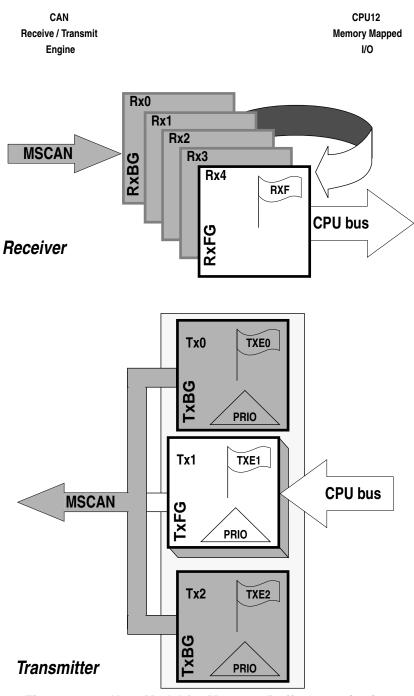

Figure 12-38. User Model for Message Buffer Organization

MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

```

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

```

## 12.5.4.3 Emulation Modes

In all emulation modes, the MSCAN module behaves just like normal system operation modes as described within this specification.

## 12.5.4.4 Listen-Only Mode

In an optional CAN bus monitoring mode (listen-only), the CAN node is able to receive valid data frames and valid remote frames, but it sends only "recessive" bits on the CAN bus. In addition, it cannot start a transmision. If the MAC sub-layer is required to send a "dominant" bit (ACK bit, overload flag, or active error flag), the bit is rerouted internally so that the MAC sub-layer monitors this "dominant" bit, although the CAN bus may remain in recessive state externally.

## 12.5.4.5 Security Modes

The MSCAN module has no security features.

## 12.5.4.6 Loopback Self Test Mode

Loopback self test mode is sometimes used to check software, independent of connections in the external system, to help isolate system problems. In this mode, the transmitter output is internally connected to the receiver input. The RXCAN input pin is ignored and the TXCAN output goes to the recessive state (logic 1). The MSCAN behaves as it does normally when transmitting and treats its own transmitted message as a message received from a remote node. In this state, the MSCAN ignores the bit sent during the ACK slot in the CAN frame acknowledge field to ensure proper reception of its own message. Both transmit and receive interrupts are generated.

# 12.5.5 Low-Power Options

If the MSCAN is disabled (CANE = 0), the MSCAN clocks are stopped for power saving.

If the MSCAN is enabled (CANE = 1), the MSCAN has two additional modes with reduced power consumption, compared to normal mode: sleep and power down mode. In sleep mode, power consumption is reduced by stopping all clocks except those to access the registers from the CPU side. In power down mode, all clocks are stopped and no power is consumed.

Table 12-36 summarizes the combinations of MSCAN and CPU modes. A particular combination of modes is entered by the given settings on the CSWAI and SLPRQ/SLPAK bits.

For all modes, an MSCAN wake-up interrupt can occur only if the MSCAN is in sleep mode (SLPRQ = 1 and SLPAK = 1), wake-up functionality is enabled (WUPE = 1), and the wake-up interrupt is enabled (WUPIE = 1).

Chapter 13 Serial Peripheral Interface (S08SPIV3)

## 16.2.1.1 EXTCLK — External Clock Source

Control bits in the timer status and control register allow the user to select nothing (timer disable), the bus-rate clock (the normal default source), a crystal-related clock, or an external clock as the clock which drives the TPM prescaler and subsequently the 16-bit TPM counter. The external clock source is synchronized in the TPM. The bus clock clocks the synchronizer; the frequency of the external source must be no more than one-fourth the frequency of the bus-rate clock, to meet Nyquist criteria and allowing for jitter.

The external clock signal shares the same pin as a channel I/O pin, so the channel pin will not be usable for channel I/O function when selected as the external clock source. It is the user's responsibility to avoid such settings. If this pin is used as an external clock source (CLKSB:CLKSA = 1:1), the channel can still be used in output compare mode as a software timer (ELSnB:ELSnA = 0:0).

## 16.2.1.2 TPMxCHn — TPM Channel n I/O Pin(s)

Each TPM channel is associated with an I/O pin on the MCU. The function of this pin depends on the channel configuration. The TPM pins share with general purpose I/O pins, where each pin has a port data register bit, and a data direction control bit, and the port has optional passive pullups which may be enabled whenever a port pin is acting as an input.

The TPM channel does not control the I/O pin when (ELSnB:ELSnA = 0:0) or when (CLKSB:CLKSA = 0:0) so it normally reverts to general purpose I/O control. When CPWMS = 1 (and ELSnB:ELSnA not = 0:0), all channels within the TPM are configured for center-aligned PWM and the TPMxCHn pins are all controlled by the TPM system. When CPWMS=0, the MSnB:MSnA control bits determine whether the channel is configured for input capture, output compare, or edge-aligned PWM.

When a channel is configured for input capture (CPWMS=0, MSnB:MSnA = 0:0 and ELSnB:ELSnA not = 0:0), the TPMxCHn pin is forced to act as an edge-sensitive input to the TPM. ELSnB:ELSnA control bits determine what polarity edge or edges will trigger input-capture events. A synchronizer based on the bus clock is used to synchronize input edges to the bus clock. This implies the minimum pulse width—that can be reliably detected—on an input capture pin is four bus clock periods (with ideal clock pulses as near as two bus clocks can be detected). TPM uses this pin as an input capture input to override the port data and data direction controls for the same pin.

When a channel is configured for output compare (CPWMS=0, MSnB:MSnA = 0:1 and ELSnB:ELSnA not = 0:0), the associated data direction control is overridden, the TPMxCHn pin is considered an output controlled by the TPM, and the ELSnB:ELSnA control bits determine how the pin is controlled. The remaining three combinations of ELSnB:ELSnA determine whether the TPMxCHn pin is toggled, cleared, or set each time the 16-bit channel value register matches the timer counter.

When the output compare toggle mode is initially selected, the previous value on the pin is driven out until the next output compare event—then the pin is toggled.

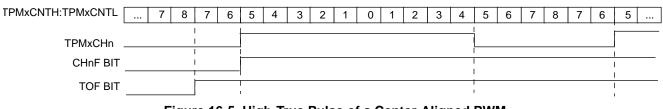

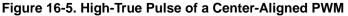

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter; the timer counter is counting up and the channel value register matches the timer counter; the timer counter is counter is counter; the timer counter is counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxMODH:TPMxMODL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxMODH:TPMxMODL = 0x0005

Figure 16-6. Low-True Pulse of a Center-Aligned PWM

#### **Chapter 17 Development Support**

when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

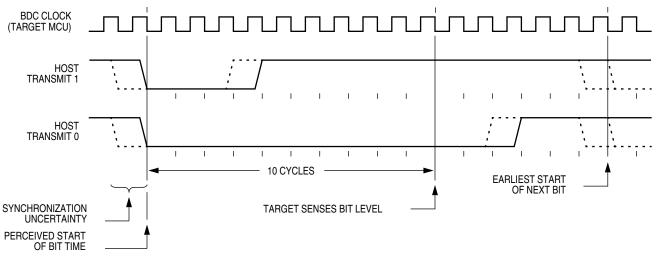

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.

Figure 17-2 shows an external host transmitting a logic 1 or 0 to the BKGD pin of a target HCS08 MCU. The host is asynchronous to the target so there is a 0-to-1 cycle delay from the host-generated falling edge to where the target perceives the beginning of the bit time. Ten target BDC clock cycles later, the target senses the bit level on the BKGD pin. Typically, the host actively drives the pseudo-open-drain BKGD pin during host-to-target transmissions to speed up rising edges. Because the target does not drive the BKGD pin during the host-to-target transmission period, there is no need to treat the line as an open-drain signal during this period.

Figure 17-2. BDC Host-to-Target Serial Bit Timing

## 18.3.2

### Table 18-2. Register Bit Summary

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1     | 0      |

|--------|--------|--------|--------|--------|--------|--------|-------|--------|

| DBGCAH | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  |

| DBGCAL | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

| DBGCBH | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  |

| DBGCBL | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

| DBGCCH | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  |

| DBGCCL | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

| DBGFH  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  |

| DBGFL  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  |

| DBGCAX | RWAEN  | RWA    | PAGSEL | 0      | 0      | 0      | 0     | bit-16 |

| DBGCBX | RWBEN  | RWB    | PAGSEL | 0      | 0      | 0      | 0     | bit-16 |

| DBGCCX | RWCEN  | RWC    | PAGSEL | 0      | 0      | 0      | 0     | bit-16 |

| DBGFX  | PPACC  | 0      | 0      | 0      | 0      | 0      | 0     | bit-16 |

| DBGC   | DBGEN  | ARM    | TAG    | BRKEN  | -      | -      | -     | LOOP1  |

| DBGT   | TRGSEL | BEGIN  | 0      | 0      |        | TRG    | [3:0] |        |

| DBGS   | AF     | BF     | CF     | 0      | 0      | 0      | 0     | ARMF   |

| DBGCNT | 0      | 0      | 0      | 0      |        | CNT    | [3:0] |        |

## 18.3.3.12 Debug FIFO Extended Information Register (DBGFX)

7 6 5 4 3 2 1 0 PPACC 0 0 0 0 0 0 R Bit 16 W POR 0 0 0 0 0 0 0 or non-0 end-run Reset 0 0 0 U U 0 0 0 end-run<sup>1</sup> = Unimplemented or Reserved

Module Base + 0x000B

#### □ Figure 18-13. Debug FIFO Extended Information Register (DBGFX)

<sup>1</sup> In the case of an end-trace to reset where DBGEN=1 and BEGIN=0, the bits in this register do not change after reset.

#### Table 18-14. DBGFX Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>PPACC  | <ul> <li>PPAGE Access Indicator Bit — This bit indicates whether the captured information in the current FIFO word is associated with an extended access through the PPAGE mechanism or not. This is indicated by the internal signal mmu_ppage_sel which is 1 when the access is through the PPAGE mechanism.</li> <li>0 The information in the corresponding FIFO word is event-only data or an unpaged 17-bit CPU address with bit-16 = 0</li> <li>1 The information in the corresponding FIFO word is a 17-bit flash address with PPAGE[2:0] in the three most significant bits and CPU address[13:0] in the 14 least significant bits</li> </ul> |

| 0<br>Bit 16 | Extended Address Bit 16 — This bit is the most significant bit of the 17-bit core address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |