# E·XFL

Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application charific microcontrollars are applicated to

#### Details

| 2 0 0 0 0 0             |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                   |

| Applications            | USB Hub/Microcontroller                                                    |

| Core Processor          | M8                                                                         |

| Program Memory Type     | OTP (8kB)                                                                  |

| Controller Series       | USB Hub                                                                    |

| RAM Size                | 256 x 8                                                                    |

| Interface               | I <sup>2</sup> C, USB, HAPI                                                |

| Number of I/O           | 31                                                                         |

| Voltage - Supply        | 4V ~ 5.25V                                                                 |

| Operating Temperature   | 0°C ~ 70°C                                                                 |

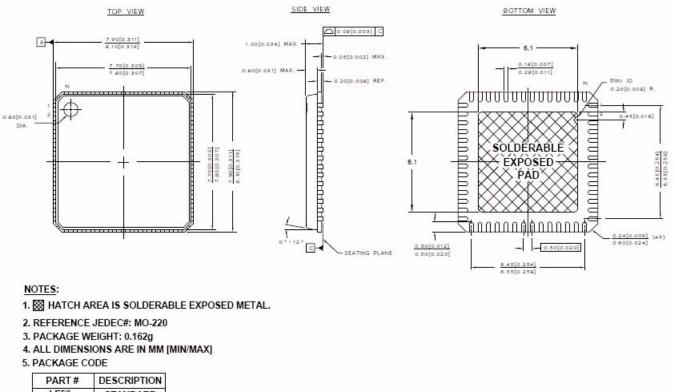

| Mounting Type           | Surface Mount                                                              |

| Package / Case          | 56-VFQFN Exposed Pad                                                       |

| Supplier Device Package | 56-QFN (8x8)                                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c66113c-lfxc |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

$V_{CC}$ P1[1] P1[0] P1[2] P1[4] P1[6] P3[0] D-[3] D+[3] P3[2] P3[4] D-[4] D+[4] P3[6] P2[0] P2[2] GND P2[4] P2[6] DAC[0]  $V_{\mathsf{PP}}$ P0[0] P0[2] P0[4] P0[6]

## **Pin Configurations**

|                  |   |      |                 |                 | TOP VIEW         |   |     |        |   |

|------------------|---|------|-----------------|-----------------|------------------|---|-----|--------|---|

|                  | С | :Y7C | 660130          | 2               |                  | С | Y7C | 661130 | 2 |

|                  |   |      | · / ·           | 1               |                  |   |     |        | L |

| XTALOUT          | Ľ | 1    | • <sub>48</sub> | V <sub>cc</sub> | XTALOUT          | Ц | 1   | 56     | Ľ |

| XTALIN           | Ľ | 2    | 47              | P1[1]           | XTALIN           |   | 2   | 55     |   |

| V <sub>REF</sub> | L | 3    | 46              | P1[0]           | V <sub>REF</sub> |   | 3   | 54     | Ц |

| P1[3]            | Ľ | 4    | 45              | P1[2]           | P1[3]            | D | 4   | 53     |   |

| P1[5]            | Ľ | 5    | 44              | P1[4]           | P1[5]            |   | 5   | 52     | Π |

| P1[7]            | Ľ | 6    | 43              | P1[6]           | P1[7]            |   | 6   | 51     | Π |

| P3[1]            | Ľ | 7    | 42              | P3[0]           | P3[1]            |   | 7   | 50     |   |

| D+[0]            | Ľ | 8    | 41              | D-[3]           | D+[0]            | D | 8   | 49     |   |

| D-[0]            | Γ | 9    | 40              | D+[3]           | D-[0]            |   | 9   | 48     | Д |

| P3[3]            | Ľ | 10   | 39              | P3[2]           | P3[3]            |   | 10  | 47     |   |

| GND              | Ľ | 11   | 38              | GND             | GND              |   | 11  | 46     |   |

| D+[1]            | Ľ | 12   | 37              | P3[4]           | P3[5]            | Е | 12  | 45     | Π |

| D-[1]            | Ľ | 13   | 36              | ] D-[4]         | D+[1]            |   | 13  | 44     |   |

| P2[1]            | Ľ | 14   | 35              | D+[4]           | D–[1]            |   | 14  | 43     |   |

| D+[2]            | Γ | 15   | 34              | P2[0]           | P2[1]            |   | 15  | 42     |   |

| D–[2]            | Ľ | 16   | 33              | _ P2[2]         | D+[2]            |   | 16  | 41     |   |

| P2[3]            | Ľ | 17   | 32              | GND             | D–[2]            |   | 17  | 40     |   |

| P2[5]            | Ľ | 18   | 31              | P2[4]           | P2[3]            |   | 18  | 39     |   |

| P2[7]            | Γ | 19   | 30              | P2[6]           | P2[5]            | Ε | 19  | 38     | Π |

| GND              | Γ | 20   | 29              | V <sub>PP</sub> | P2[7]            | Е | 20  | 37     | Π |

| P0[7]            | Γ | 21   | 28              | P0[0]           | DAC[7]           | Е | 21  | 36     | Π |

| P0[5]            | Γ | 22   | 27              | P0[2]           | P0[7]            | Е | 22  | 35     | Π |

| P0[3]            | Γ | 23   | 26              | P0[4]           | P0[5]            | Ľ | 23  | 34     | Π |

| P0[1]            | Γ | 24   | 25              | P0[6]           | P0[3]            | Γ | 24  | 33     | Π |

|                  |   |      |                 | 1               | P0[1]            | Γ | 25  | 32     |   |

DAC[5] 26

DAC[3] 27 DAC[1] 28 31 DAC[2]

29 DAC[6]

30

DAC[4]

#### Figure 1. CY7C66013C 48-Pin SSOP and CY7C66113C 56-Pin SSOP

#### Table 3. I/O Register Summary (continued)

| Register Name                           | I/O Address | Read/Write | Function                                                                                    | Page |

|-----------------------------------------|-------------|------------|---------------------------------------------------------------------------------------------|------|

| HAPI and I <sup>2</sup> C Configuration | 0x09        | R/W        | HAPI Width and I <sup>2</sup> C Position Configuration                                      | 22   |

| USB Device Address A                    | 0x10        | R/W        | USB Device Address A                                                                        | 38   |

| EP A0 Counter Register                  | 0x11        | R/W        | USB Address A, Endpoint 0 Counter                                                           | 40   |

| EP A0 Mode Register                     | 0x12        | R/W        | USB Address A, Endpoint 0 Configuration                                                     | 39   |

| EP A1 Counter Register                  | 0x13        | R/W        | USB Address A, Endpoint 1 Counter                                                           | 40   |

| EP A1 Mode Register                     | 0x14        | R/W        | USB Address A, Endpoint 1 Configuration                                                     | 40   |

| EP A2 Counter Register                  | 0x15        | R/W        | USB Address A, Endpoint 2 Counter                                                           | 40   |

| EP A2 Mode Register                     | 0x16        | R/W        | USB Address A, Endpoint 2 Configuration                                                     | 40   |

| USB Status & Control                    | 0x1F        | R/W        | USB Upstream Port Traffic Status and Control                                                | 37   |

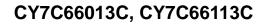

| Global Interrupt Enable                 | 0x20        | R/W        | Global Interrupt Enable                                                                     | 27   |

| Endpoint Interrupt Enable               | 0x21        | R/W        | USB Endpoint Interrupt Enables                                                              | 27   |

| Interrupt Vector                        | 0x23        | R          | Pending Interrupt Vector Read/Clear                                                         | 29   |

| Timer (LSB)                             | 0x24        | R          | Lower 8 Bits of Free-running Timer (1 MHz)                                                  | 21   |

| Timer (MSB)                             | 0x25        | R          | Upper 4 Bits of Free-running Timer                                                          | 21   |

| WDT Clear                               | 0x26        | W          | Watchdog Timer Clear                                                                        | 14   |

| I <sup>2</sup> C Control & Status       | 0x28        | R/W        | I <sup>2</sup> C Status and Control                                                         | 23   |

| I <sup>2</sup> C Data                   | 0x29        | R/W        | I <sup>2</sup> C Data                                                                       | 23   |

| DAC Data                                | 0x30        | R/W        | DAC Data                                                                                    | 19   |

| DAC Interrupt Enable                    | 0x31        | W          | Interrupt Enable for each DAC Pin                                                           | 20   |

| DAC Interrupt Polarity                  | 0x32        | W          | Interrupt Polarity for each DAC Pin                                                         | 20   |

| DAC Isink                               | 0x38-0x3F   | W          | Input Sink Current Control for each DAC Pin                                                 | 20   |

| USB Device Address B                    | 0x40        | R/W        | USB Device Address B (not used in 5-endpoint mode)                                          | 38   |

| EP B0 Counter Register                  | 0x41        | R/W        | USB Address B, Endpoint 0 Counter                                                           | 40   |

| EP B0 Mode Register                     | 0x42        | R/W        | USB Address B, Endpoint 0 Configuration, or<br>USB Address A, Endpoint 3 in 5-endpoint Mode | 39   |

| EP B1 Counter Register                  | 0x43        | R/W        | USB Address B, Endpoint 1 Counter                                                           | 40   |

| EP B1 Mode Register                     | 0x44        | R/W        | USB Address B, Endpoint 1 Configuration, or<br>USB Address A, Endpoint 4 in 5-endpoint Mode | 40   |

| Hub Port Connect Status                 | 0x48        | R/W        | Hub Downstream Port Connect Status                                                          | 32   |

| Hub Port Enable                         | 0x49        | R/W        | Hub Downstream Ports Enable                                                                 | 33   |

| Hub Port Speed                          | 0x4A        | R/W        | Hub Downstream Ports Speed                                                                  | 33   |

| Hub Port Control (Ports [4:1])          | 0x4B        | R/W        | Hub Downstream Ports Control                                                                | 34   |

| Hub Port Suspend                        | 0x4D        | R/W        | Hub Downstream Port Suspend Control                                                         | 35   |

| Hub Port Resume Status                  | 0x4E        | R          | Hub Downstream Ports Resume Status                                                          | 36   |

| Hub Ports SE0 Status                    | 0x4F        | R          | Hub Downstream Ports SE0 Status                                                             | 35   |

| Hub Ports Data                          | 0x50        | R          | Hub Downstream Ports Differential Data                                                      | 35   |

| Hub Downstream Force Low                | 0x51        | R/W        | Hub Downstream Ports Force LOW                                                              | 34   |

| Processor Status & Control              | 0xFF        | R/W        | Microprocessor Status and Control Register                                                  | 26   |

## **Suspend Mode**

The CY7C66x13C is placed into a low power state by setting the Suspend bit of the Processor Status and Control register. All logic blocks in the device are turned off except the GPIO interrupt logic and the USB receiver. The clock oscillator, PLL, and the free-running and WDTs are shut down. Only the occurrence of an enabled GPIO interrupt or non idle bus activity at a USB upstream or downstream port wakes the part from suspend. The Run bit in the Processor Status and Control Register must be set to resume a part out of suspend.

The clock oscillator restarts immediately after exiting suspend mode. The microcontroller returns to a fully functional state 1 ms after the oscillator is stable. The microcontroller executes the instruction following the I/O write that placed the device into suspend mode before servicing any interrupt requests. The GPIO interrupt allows the controller to wake up periodically and poll system components while maintaining a very low average power consumption. To achieve the lowest possible current during suspend mode, all I/O should be held at  $V_{CC}$  or Gnd. This also applies to internal port pins that may not be bonded in a particular package.

Typical code for entering suspend is given here:

... ; All GPIO set to low power state (no floating pins)

... ; Enable GPIO interrupts if desired for wakeup

mov a, 09h; Set suspend and run bits

iowr FFh; Write to Status and Control Register - Enter suspend, wait for USB activity

(or GPIO Interrupt)

nop ; This executes before any ISR

## General Purpose I/O (GPIO) Ports

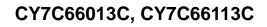

#### Figure 7. Block Diagram of a GPIO Pin

There are up to 31 GPIO pins (P0[7:0], P1[7:0], P2[7:0], and P3[6:0]) for the hardware interface. The number of GPIO pins changes based on the package type of the chip. Each port is configured as inputs with internal pull ups, open drain outputs, or traditional CMOS outputs. Port 3 offers a higher current drive, with typical current sink capability of 12 mA. The data for each GPIO port is accessible through the data registers. Port data registers are shown in Figure 8 through Figure 11, and are set to 1 on reset.

## **DAC Port**

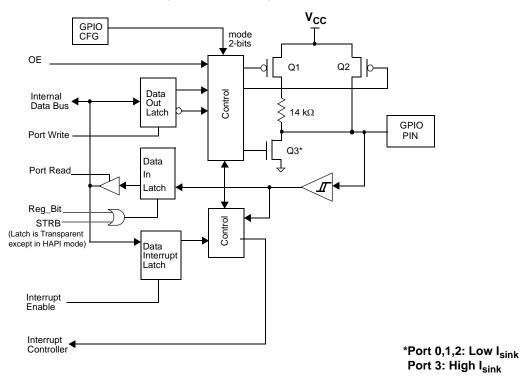

The CY7C66113CC features a programmable sink current 8-bit port, which is also known as DAC port. Each of these port I/O pins have a programmable current sink. Writing a '1' to a DAC I/O pin disables the output current sink ( $I_{sink}$  DAC) and drives the I/O pin HIGH through an integrated 14 k $\Omega$  resistor. When a '0' is written to a DAC I/O pin, the  $I_{sink}$  DAC is enabled and the pull up resistor is disabled. This causes the  $I_{sink}$  DAC to sink current to drive the output LOW. Figure 17 shows a block diagram of the DAC port pin.

Figure 17. Block Diagram of a DAC Pin

The amount of sink current for the DAC I/O pin is programmable over 16 values based on the contents of the DAC Isink Register (Figure 19) for that output pin. DAC[1:0] are high current outputs that are programmable from 3.2 mA to 16 mA (typical). DAC[7:2] are low current outputs, programmable from 0.2 mA to 1.0 mA (typical).

When the suspend bit in Processor Status and Control Register (Figure 28) is set, the Isink DAC block of the DAC circuitry is

disabled. Special care should be taken when the CY7C66113C device is placed in the suspend. The DAC Port Data Register (Figure 18) should normally be loaded with all '1's (Figure 28) before setting the suspend bit. If any of the DAC bits are set to '0' when the device is suspended, that DAC input floats. The floating pin could result in excessive current consumption by the device, unless an external load places the pin in a deterministic state.

#### Figure 18. DAC Port Data

#### DAC Port Data ADDRESS 0x30 Bit # 6 5 4 3 2 7 1 0 Bit Name DAC[7] DAC[6] DAC[5] DAC[4] DAC[3] DAC[2] DAC[1] DAC[0] Read/Write R/W R/W R/W R/W R/W R/W R/W R/W Reset 1 1 1 1 1 1 1 1

#### Bit [1..0]: High Current Output 3.2 mA to 16 mA typical

1= I/O pin is an output pulled HGH through the 14 k $\Omega$  resistor. 0 = I/O pin is an input with an internal 14 k $\Omega$  pull up resistor. Bit [7..2]: Low Current Output 0.2 mA to 1 mA typical

1= I/O pin is an output pulled HGH through the 14 k $\Omega$  resistor. 0 = I/O pin is an input with an internal 14 k $\Omega$  pull up resistor.

### Figure 26. I<sup>2</sup>C Data Register

| I <sup>2</sup> C Data |                         |                         |                         |                         |                         |                         | А                       | DDRESS 0x29             |

|-----------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| Bit #                 | 7                       | 6                       | 5                       | 4                       | 3                       | 2                       | 1                       | 0                       |

| Bit Name              | I <sup>2</sup> C Data 7 | I <sup>2</sup> C Data 6 | I <sup>2</sup> C Data 5 | I <sup>2</sup> C Data 4 | I <sup>2</sup> C Data 3 | I <sup>2</sup> C Data 2 | I <sup>2</sup> C Data 1 | I <sup>2</sup> C Data 0 |

| Read/Write            | R/W                     |

| Reset                 | Х                       | Х                       | Х                       | Х                       | Х                       | Х                       | Х                       | Х                       |

Bits [7..0]: I<sup>2</sup>C Data

Contains 8-bit data on the I<sup>2</sup>C Bus.

## Figure 27. I<sup>2</sup>C Status and Control Register

## 1<sup>2</sup>C Status and Control

| I <sup>2</sup> C Status and Control |           |                   |           |     |      |                     |                  |                         |

|-------------------------------------|-----------|-------------------|-----------|-----|------|---------------------|------------------|-------------------------|

| Bit #                               | 7         | 6                 | 5         | 4   | 3    | 2                   | 1                | 0                       |

| Bit Name                            | MSTR Mode | Continue/Bu<br>sy | Xmit Mode | ACK | Addr | ARB<br>Lost/Restart | Received<br>Stop | I <sup>2</sup> C Enable |

| Read/Write                          | R/W       | R/W               | R/W       | R/W | R/W  | R/W                 | R/W              | R/W                     |

| Reset                               | 0         | 0                 | 0         | 0   | 0    | 0                   | 0                | 0                       |

The I<sup>2</sup>C Status and Control register bits are defined in Table 9, with a more detailed description following.

## Table 9. I<sup>2</sup>C Status and Control Register Bit Definitions

| Bit | Name                    | Description                                                                                                                                                   |

|-----|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | I <sup>2</sup> C Enable | When set to '1', the I <sup>2</sup> C compatible function is enabled. When cleared, I <sup>2</sup> C GPIO pins operate normally.                              |

| 1   | Received Stop           | Reads 1 only in slave receive mode, when I <sup>2</sup> C Stop bit detected (unless firmware did not ACK the last transaction).                               |

| 2   | ARB Lost/Restart        | Reads 1 to indicate master has lost arbitration. Reads 0 otherwise.<br>Write to 1 in master mode to perform a restart sequence (also set Continue bit).       |

| 3   | Addr                    | Reads 1 during first byte after start/restart in slave mode, or if master loses arbitration.<br>Reads 0 otherwise. This bit should always be written as 0.    |

| 4   | ACK                     | In receive mode, write 1 to generate ACK, 0 for no ACK.<br>In transmit mode, reads 1 if ACK was received, 0 if no ACK received.                               |

| 5   | Xmit Mode               | Write to 1 for transmit mode, 0 for receive mode.                                                                                                             |

| 6   | Continue/Busy           | Write 1 to indicate ready for next transaction.<br>Reads 1 when I <sup>2</sup> C compatible block is busy with a transaction, 0 when transaction is complete. |

| 7   | MSTR Mode               | Write to 1 for master mode, 0 for slave mode. This bit is cleared if master loses arbitration. Clearing from 1 to 0 generates Stop bit.                       |

is serviced following the completion of the currently executing instruction.

When servicing an interrupt, the hardware does the following:

- 1. Disables all interrupts by clearing the Global Interrupt Enable bit in the CPU (the state of this bit is read at Bit 2 of the Processor Status and Control Register, Figure 28).

- 2. Clears the flip flop of the current interrupt.

- 3. Generates an automatic CALL instruction to the ROM address associated with the interrupt being serviced (that is, the Interrupt Vector).

The instruction in the interrupt table is typically a JMP instruction to the address of the Interrupt Service Routine (ISR). The user re-enables interrupts in the interrupt service routine by executing an El instruction. Interrupts are nested to a level limited only by the available stack space.

The Program Counter value and the Carry and Zero flags (CF, ZF) are stored onto the Program Stack by the automatic CALL instruction generated as part of the interrupt acknowledge process. The user firmware is responsible for ensuring that the processor state is preserved and restored during an interrupt.

The PUSH A instruction should typically be used as the first command in the ISR to save the accumulator value and the POP A instruction should be used to restore the accumulator value just before the RETI instruction. The program counter CF and ZF are restored and interrupts are enabled when the RETI instruction is executed.

The DI and EI instructions are used to disable and enable interrupts, respectively. These instructions affect only the Global Interrupt Enable bit of the CPU. If desired, EI is used to re-enable interrupts while inside an ISR, instead of waiting for the RETI that exists the ISR. While the global interrupt enable bit is cleared, the presence of a pending interrupt is detected by examining the IRQ Sense bit (Bit 7 in the Processor Status and Control Register).

#### **Interrupt Vectors**

The Interrupt Vectors supported by the USB Controller are listed in Table 11. The lowest numbered interrupt (USB Bus Reset interrupt) has the highest priority, and the highest numbered interrupt ( $I^2C$  interrupt) has the lowest priority.

#### Figure 31. Interrupt Controller Function Diagram

Although Reset is not an interrupt, the first instruction executed after a reset is at PROM address 0x0000h—which corresponds to the first entry in the Interrupt Vector Table. Because the JMP instruction is two bytes long, the interrupt vectors occupy two bytes.

**Table 11. Interrupt Vector Assignments**

| Interrupt Vector Number | ROM Address | Function                           |

|-------------------------|-------------|------------------------------------|

| Not Applicable          | 0x0000      | Execution after Reset begins here  |

| 1                       | 0x0002      | USB Bus Reset interrupt            |

| 2                       | 0x0004      | 128 µs timer interrupt             |

| 3                       | 0x0006      | 1.024 ms timer interrupt           |

| 4                       | 0x0008      | USB Address A Endpoint 0 interrupt |

| 5                       | 0x000A      | USB Address A Endpoint 1 interrupt |

| 6                       | 0x000C      | USB Address A Endpoint 2 interrupt |

| 7                       | 0x000E      | USB Address B Endpoint 0 interrupt |

| 8                       | 0x0010      | USB Address B Endpoint 1 interrupt |

| 9                       | 0x0012      | USB Hub interrupt                  |

| 10                      | 0x0014      | DAC interrupt                      |

| 11                      | 0x0016      | GPIO and HAPI interrupt            |

| 12                      | 0x0018      | I <sup>2</sup> C interrupt         |

#### Interrupt Latency

Interrupt latency is calculated from the following equation:

Interrupt latency = (Number of clock cycles remaining in the current instruction) + (10 clock cycles for the CALL instruction) + (5 clock cycles for the JMP instruction).

For example, if a five clock cycle instruction such as JC is being executed when an interrupt occurs, the first instruction of the Interrupt Service Routine executes a minimum of 16 clocks (1+10+5) or a maximum of 20 clocks (5+10+5) after the interrupt is issued. For a 12 MHz internal clock (6 MHz crystal), 20 clock periods is 20/12 MHz = 1.667  $\mu$ s.

#### **USB Bus Reset Interrupt**

The USB Controller recognizes a USB Reset when a Single Ended Zero (SE0) condition persists on the upstream USB port for 12–16  $\mu$ s. SE0 is defined as the condition in which both the D+ line and the D– line are LOW. A USB Bus Reset may be recognized for an SE0 as short as 12  $\mu$ s, but is always recognized for an SE0 longer than 16  $\mu$ s. When a USB Bus Reset is detected, bit 5 of the Processor Status and Control Register (Figure 28) is set to record this event. In addition, the controller clears the following registers:

| SIE Section: | USB Device Address Registers (0x10, 0x40)                                                                                                                                                                                                  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hub Section: | Hub Ports Connect Status (0x48)<br>Hub Ports Enable (0x49)<br>Hub Ports Speed (0x4A)<br>Hub Ports Suspend (0x4D)<br>Hub Ports Resume Status (0x4E)<br>Hub Ports SE0 Status (0x4F)<br>Hub Ports Data (0x50)<br>Hub Downstream Force (0x51). |

|              |                                                                                                                                                                                                                                            |

A USB Bus Reset Interrupt is generated at the end of the USB Bus Reset condition when the SE0 state is deasserted. If the USB reset occurs during the start up delay following a POR, the delay is aborted as described in Power on Reset on page 14.

#### **Timer Interrupt**

There are two periodic timer interrupts: the 128  $\mu$ s interrupt and the 1.024 ms interrupt. The user should disable both timer interrupts before going into the suspend mode to avoid possible conflicts between servicing the timer interrupts first or the suspend request first.

#### **USB Endpoint Interrupts**

There are five USB endpoint interrupts, one per endpoint. A USB endpoint interrupt is generated after the USB host writes to a USB endpoint FIFO or after the USB controller sends a packet to the USB host. The interrupt is generated on the last packet of the transaction. For example, on the host's ACK during an IN, or on the device ACK during on OUT. If no ACK is received during an IN transaction, no interrupt is generated.

#### **USB Hub Interrupt**

A USB hub interrupt is generated by the hardware after a connect/disconnect change, babble, or a resume event is detected by the USB repeater hardware. The babble and resume events are additionally gated by the corresponding bits of the Hub Port Enable Register (Figure 35). The connect and disconnect event on a port does not generate an interrupt if the SIE does not drive the port (that is, the port is being forced).

| Hub Ports Sp | Hub Ports Speed ADDRE |          |          |          |              |              |              |              |

|--------------|-----------------------|----------|----------|----------|--------------|--------------|--------------|--------------|

| Bit #        | 7                     | 6        | 5        | 4        | 3            | 2            | 1            | 0            |

| Bit Name     | Reserved              | Reserved | Reserved | Reserved | Port 4 Speed | Port 3 Speed | Port 2 Speed | Port 1 Speed |

| Read/Write   | R/W                   | R/W      | R/W      | R/W      | R/W          | R/W          | R/W          | R/W          |

| Reset        | 0                     | 0        | 0        | 0        | 0            | 0            | 0            | 0            |

#### Figure 34. Hub Ports Speed

#### Bit [0..3]: Port x Speed (where x = 1..4)

Set to 1 if the device plugged in to Port x is Low speed; Set to 0 if the device plugged in to Port x is Full speed.

#### Enabling and Disabling a USB Device

After a USB device connection is detected, firmware must update status change bits in the hub status change data structure that is polled periodically by the USB host. The host responds by sending a packet that instructs the hub to reset and enable the downstream port. Firmware then sets the bit in the Hub Ports Enable register, Figure 35, for the downstream port. The hub repeater hardware responds to an enable bit in the Hub Ports Enable register by enabling the downstream port, so that USB traffic flows to and from that port.

If a port is marked enabled and is not suspended, it receives all USB traffic from the upstream port, and USB traffic from the downstream port is passed to the upstream port (unless babble

#### Bit [7..4]: Reserved.

The Hub Ports Speed register is cleared to zero by reset or bus reset. This must be set by the firmware on issuing a port reset. The Reserved bits [7..4] should always read as '0.'

is detected). Low speed ports do not receive full speed traffic from the upstream port.

When firmware writes to the Hub Ports Enable register to enable a port, the port is not enabled until the end of any packet currently being transmitted. If there is no USB traffic, the port is enabled immediately.

When a USB device disconnection is detected, firmware must update status bits in the hub change status data structure that is polled periodically by the USB host. In suspend, a connect or disconnect event generates an interrupt (if the hub interrupt is enabled) even if the port is disabled.

#### Figure 35. Hub Ports Enable Register

#### Hub Ports Enable Register

| Hub Ports Enable Register ADDRESS 0X4 |          |          |          |          |                  |                  |                  |                  |  |

|---------------------------------------|----------|----------|----------|----------|------------------|------------------|------------------|------------------|--|

| Bit #                                 | 7        | 6        | 5        | 4        | 3                | 2                | 1                | 0                |  |

| Bit Name                              | Reserved | Reserved | Reserved | Reserved | Port 4<br>Enable | Port 3<br>Enable | Port 2<br>Enable | Port 1<br>Enable |  |

| Read/Write                            | R/W      | R/W      | R/W      | R/W      | R/W              | R/W              | R/W              | R/W              |  |

| Reset                                 | 0        | 0        | 0        | 0        | 0                | 0                | 0                | 0                |  |

#### Bit [0..3]: Port x Enable (where x = 1..4)

Set to 1 if Port x is enabled; Set to 0 if Port x is disabled.

#### Bit [7..4]: Reserved.

The Hub Ports Enable register is cleared to zero by reset or bus reset to disable all downstream ports as the default condition. A port is also disabled by internal hub hardware (enable bit cleared) if babble is detected on that downstream port. Babble is defined as:

- Any non idle downstream traffic on an enabled downstream port at EOF2

- Any downstream port with upstream connectivity established at EOF2 (that is, no EOP received by EOF2).

ADDDESS AV40

#### Figure 38. Hub Ports SE0 Status Register

| Hub Ports SE | Hub Ports SE0 Status         ADDRESS 0x4F |          |          |          |                      |                      |                      |                      |  |  |

|--------------|-------------------------------------------|----------|----------|----------|----------------------|----------------------|----------------------|----------------------|--|--|

| Bit #        | 7                                         | 6        | 5        | 4        | 3                    | 2                    | 1                    | 0                    |  |  |

| Bit Name     | Reserved                                  | Reserved | Reserved | Reserved | Port 4<br>SE0 Status | Port 3<br>SE0 Status | Port 2<br>SE0 Status | Port 1<br>SE0 Status |  |  |

| Read/Write   | -                                         | -        | -        | -        | R                    | R                    | R                    | R                    |  |  |

| Reset        | 0                                         | 0        | 0        | 0        | 0                    | 0                    | 0                    | 0                    |  |  |

#### Bit [0..3]: Port x SE0 Status (where x = 1..4)

Bit [7..4]: Reserved.

Set to 1 if a SE0 is output on the Port x bus; Set to 0 if a Non-SE0 is output on the Port x bus.

#### Figure 39. Hub Ports Data Register

#### **Hub Ports Data**

| Bit #      | 7        | 6        | 5        | 4        | 3                    | 2                    | 1                    | 0                    |  |

|------------|----------|----------|----------|----------|----------------------|----------------------|----------------------|----------------------|--|

| Bit Name   | Reserved | Reserved | Reserved | Reserved | Port 4 Diff.<br>Data | Port 3 Diff.<br>Data | Port 2 Diff.<br>Data | Port 1 Diff.<br>Data |  |

| Read/Write | -        | -        | -        | -        | R                    | R                    | R                    | R                    |  |

| Reset      | 0        | 0        | 0        | 0        | 0                    | 0                    | 0                    | 0                    |  |

#### Bit [0..3]: Port x Diff Data (where x = 1..4)

Bit [7..4]: Reserved.

Set to 1 if D+ > D- (forced differential 1, if signal is differential, i.e. not a SE0 or SE1). Set to 0 if D- > D+ (forced differential 0, if signal is differential, i.e., not a SE0 or SE1);

#### **Downstream Port Suspend and Resume**

The Hub Ports Suspend Register (Figure 40) and Hub Ports Resume Status Register (Figure 41) indicate the suspend and resume conditions on downstream ports. The suspend register must be set by firmware for any ports that are selectively suspended. Also, this register is only valid for ports that are selectively suspended.

If a port is marked as selectively suspended, normal USB traffic is not sent to that port. Resume traffic is also prevented from going to that port, unless the Resume comes from the selectively suspended port. If a resume condition is detected on the port, hardware reflects a Resume back to the port, sets the Resume bit in the Hub Ports Resume Register, and generates a hub interrupt. If a disconnect occurs on a port marked as selectively suspended, the suspend bit is cleared. The Device Remote Wakeup bit (bit 7) of the Hub Ports Suspend Register controls whether or not the resume signal is propagated by the hub after a connect or a disconnect event. If the Device Remote Wakeup bit is set, the hub automatically propagates the resume signal after a connect or a disconnect event. If the Device Remote Wakeup bit is cleared, the hub does not propagate the resume signal. The setting of the Device Remote Wakeup flag has no impact on the propagation of the resume signal after a downstream remote wakeup event. The hub automatically propagates the resume signal after a remote wakeup event, regardless of the state of the Device Remote of the hub interrupt. These registers are cleared on reset or USB bus reset.

#### Figure 40. Hub Ports Suspend Register

| Hub Ports Su | spend                      |          |          |          |                                |                                | AD                             | DRESS 0x4D                     |

|--------------|----------------------------|----------|----------|----------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Bit #        | 7                          | 6        | 5        | 4        | 3                              | 2                              | 1                              | 0                              |

| Bit Name     | Device<br>Remote<br>Wakeup | Reserved | Reserved | Reserved | Port 4<br>Selective<br>Suspend | Port 3<br>Selective<br>Suspend | Port 2<br>Selective<br>Suspend | Port 1<br>Selective<br>Suspend |

| Read/Write   | R/W                        | R/W      | R/W      | R/W      | R/W                            | R/W                            | R/W                            | R/W                            |

| Reset        | 0                          | 0        | 0        | 0        | 0                              | 0                              | 0                              | 0                              |

#### Bit [0..3]: Port x Selective Suspend (where x = 1..4)

Set to 1 if Port x is Selectively Suspended; Set to 0 if Port x Do not suspend.

#### Bit 7: Device Remote Wakeup.

When set to 1, Enable hardware upstream resume signaling for connect and disconnect events during global resume.

When set to 0, Disable hardware upstream resume signaling for connect and disconnect events during global resume.

ADDRESS 0x50

#### USB Upstream Port Status and Control

USB status and control is regulated by the USB Status and Control Register, as shown in Figure 42. All bits in the register are cleared during reset.

#### **USB Status and Control**

## Figure 42. USB Status and Control Register

| USB Status a | nd Control       |                  |                |            |              |                            | AD                         | DRESS                      | 0x1F |

|--------------|------------------|------------------|----------------|------------|--------------|----------------------------|----------------------------|----------------------------|------|

| Bit #        | 7                | 6                | 5              | 4          | 3            | 2                          | 1                          | 0                          |      |

| Bit Name     | Endpoint<br>Size | Endpoint<br>Mode | D+<br>Upstream | D-Upstream | Bus Activity | Control<br>Action<br>Bit 2 | Control<br>Action<br>Bit 1 | Control<br>Action<br>Bit 0 |      |

| Read/Write   | R/W              | R/W              | R              | R          | R/W          | R/W                        | R/W                        | R/W                        |      |

| Reset        | 0                | 0                | 0              | 0          | 0            | 0                          | 0                          | 0                          |      |

#### Bits[2..0]: Control Action

Set to control action as per Table 13. The three control bits allow the upstream port to be driven manually by firmware. For normal USB operation, all of these bits must be cleared. Table 13 shows how the control bits affect the upstream port.

#### Table 13. Control Bit Definition for Upstream Port

| Control Bits | Control Action                    |

|--------------|-----------------------------------|

| 000          | Not Forcing (SIE Controls Driver) |

| 001          | Force D+[0] HIGH, D-[0] LOW       |

| 010          | Force D+[0] LOW, D–[0] HIGH       |

| 011          | Force SE0; D+[0] LOW, D-[0] LOW   |

| 100          | Force D+[0] LOW, D-[0] LOW        |

| 101          | Force D+[0] HiZ, D-[0] LOW        |

| 110          | Force D+[0] LOW, D–[0] HiZ        |

| 111          | Force D+[0] HiZ, D–[0] HiZ        |

#### **Bit 3: Bus Activity**

This is a "sticky" bit that indicates if any non idle USB event has occurred on the upstream USB port. Firmware should check and clear this bit periodically to detect any loss of bus activity. Writing a '0' to the Bus Activity bit clears it, while writing a '1' preserves the current value. In other words, the firmware clears the Bus Activity bit, but only the SIE can set it.

#### Bits 4 and 5: D– Upstream and D+ Upstream

These bits give the state of each upstream port pin individually: 1 = HIGH, 0 = LOW.

#### **Bit 6: Endpoint Mode**

This bit used to configure the number of USB endpoints. See USB Device Endpoints for a detailed description.

#### Bit 7: Endpoint Size

This bit used to configure the number of USB endpoints. See USB Device Endpoints for a detailed description.

The hub generates an EOP at EOF1 in accordance with the USB 1.1 Specification, Section 11.2.2.

## **USB Mode Tables**

#### Table 15. USB Register Mode Encoding

| Mode                                                                 | Mode<br>Bits | SETUP            | IN                | OUT              | Comments                                                                        |

|----------------------------------------------------------------------|--------------|------------------|-------------------|------------------|---------------------------------------------------------------------------------|

| Disable                                                              | 0000         | ignore           | ignore            | ignore           | Ignore all USB traffic to this endpoint                                         |

| Nak In/Out                                                           | 0001         | accept           | NAK               | NAK              | Forced from Setup on Control endpoint, from modes other than 0000               |

| Status Out Only                                                      | 0010         | accept           | stall             | check            | For Control endpoints                                                           |

| Stall In/Out                                                         | 0011         | accept           | stall             | stall            | For Control endpoints                                                           |

| Ignore In/Out                                                        | 0100         | accept           | ignore            | ignore           | For Control endpoints                                                           |

| Isochronous Out                                                      | 0101         | ignore           | ignore            | always           | For Isochronous endpoints                                                       |

| Status In Only                                                       | 0110         | accept           | TX 0 Byte         | stall            | For Control Endpoints                                                           |

| Isochronous In                                                       | 0111         | ignore           | TX count          | ignore           | For Isochronous endpoints                                                       |

| Nak Out                                                              | 1000         | ignore           | ignore            | NAK              | Is set by SIE on an ACK from mode 1001 (Ack Out)                                |

| Ack Out(STALL <sup>[4]</sup> =0)<br>Ack Out(STALL <sup>[4]</sup> =1) | 1001<br>1001 | ignore<br>ignore | ignore<br>ignore  | ACK<br>stall     | On issuance of an ACK this mode is changed by SIE to 1000 (NAK Out)             |

| Nak Out-Status In                                                    | 1010         | accept           | TX 0 Byte         | NAK              | Is set by SIE on an ACK from mode 1011 (Ack Out-Status In)                      |

| Ack Out-Status In                                                    | 1011         | accept           | TX 0 Byte         | ACK              | On issuance of an ACK this mode is changed by SIE to 1010 (NAK Out – Status In) |

| Nak In                                                               | 1100         | ignore           | NAK               | ignore           | Is set by SIE on an ACK from mode 1101 (Ack In)                                 |

| Ack IN(STALL <sup>[4]</sup> =0)<br>Ack IN(STALL <sup>[4]</sup> =1)   | 1101<br>1101 | ignore<br>ignore | TX count<br>stall | ignore<br>ignore | On issuance of an ACK this mode is changed by SIE to 1100 (NAK In)              |

| Nak In – Status Out                                                  | 1110         | accept           | NAK               | check            | Is set by SIE on an ACK from mode 1111 (Ack In – Status Out)                    |

| Ack In – Status Out                                                  | 1111         | accept           | TX Count          | check            | On issuance of an ACK this mode is changed by SIE to 1110 (NAK In – Status Out) |

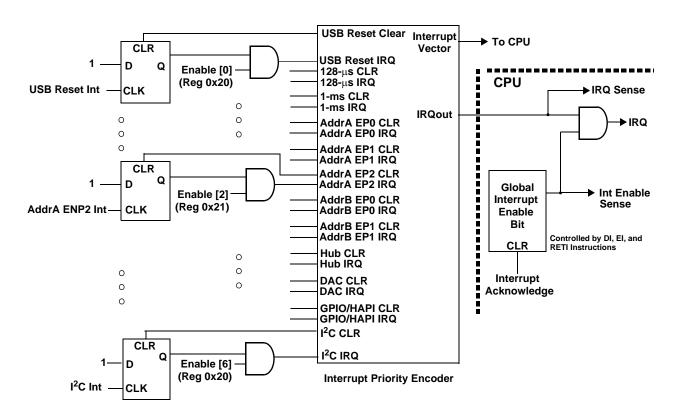

#### Mode

This lists the mnemonic given to the different modes that are set in the Endpoint Mode Register by writing to the lower nibble (bits 0..3). The bit settings for different modes are covered in the column marked "Mode Bits." The Status IN and Status OUT represent the Status stage in the IN or OUT transfer involving the control endpoint.

#### Mode Bits

These column lists the encoding for different modes by setting Bits[3..0] of the Endpoint Mode register. This modes represents how the SIE responds to different tokens sent by the host to an endpoint. For instance, if the mode bits are set to "0001" (NAK IN/OUT), the SIE responds with an

- ACK on receiving a SETUP token from the host

- NAK on receiving an OUT token from the host

- NAK on receiving an IN token from the host

Refer to  $I^2C$  Compatible Controller on page 22 for more information on SIE functioning.

#### SETUP, IN, and OUT

These columns shows the SIE's response to the host on receiving a SETUP, IN, and OUT token depending on the mode set in the Endpoint Mode Register.

A "Check" on the OUT token column, implies that on receiving an OUT token the SIE checks to see whether the OUT packet is of zero length and has a Data Toggle (DTOG) set to '1.' If the DTOG bit is set and the received OUT Packet has zero length, the OUT is ACKed to complete the transaction. If either of this condition is not met the SIE responds with a STALLL or just ignore the transaction.

A "TX Count" entry in the IN column implies that the SIE transmit the number of bytes specified in the Byte Count (bits 3..0 of the Endpoint Count Register) to the host in response to the IN token received.

A "TX0 Byte" entry in the IN column implies that the SIE transmit a zero length byte packet in response to the IN token received from the host.

An "Ignore" in any of the columns means that the device does not send any handshake tokens (no ACK) to the host.

An "Accept" in any of the columns means that the device responds with an ACK to a valid SETUP transaction to the host.

#### Comments

Some Mode Bits are automatically changed by the SIE in response to certain USB transactions. For example, if the Mode Bits [3:0] are set to '1111' which is ACK IN-Status OUT mode as shown in Table 14, the SIE changes the endpoint Mode Bits [3:0] to NAK IN-Status OUT mode (1110) after ACK'ing a valid status

#### Note

4. STALL bit is bit 7 of the USB Non Control Device Endpoint Mode registers. For more information, refer to USB Non Control Endpoint Mode Registers on page 40.

stage OUT token. The firmware needs to update the mode for the SIE to respond appropriately. See Table 12 for more details on what modes are changed by the SIE. A disabled endpoint remains disabled until changed by firmware, and all endpoints reset to the disabled mode (0000). Firmware normally enables the endpoint mode after a SetConfiguration request.

Any SETUP packet to an enabled endpoint with mode set to accept SETUPs are changed by the SIE to 0001 (NAKing INs and OUTs). Any mode set to accept a SETUP sends an ACK handshake to a valid SETUP token. The control endpoint has three status bits for identifying the token type received (SETUP, IN, or OUT), but the endpoint must be placed in the correct mode to function as such. Non control endpoints should not be placed into modes that accept SETUPs. Note that most modes that control transactions involving an ending ACK, are changed by the SIE to a corresponding mode which NAKs subsequent packets following the ACK. Exceptions are modes 1010 and 1110.

Table 16.

Decode Table for Table 17

The response of the SIE are summarized as follows:

- The SIE only responds to valid transactions, and ignores invalid ones.

- The SIE generates an interrupt when a valid transaction is completed or when the FIFO is corrupted. FIFO corruption occurs during an OUT or SETUP transaction to a valid internal address, that ends with a invalid CRC.

- An incoming Data packet is valid if the count is < Endpoint Size + 2 (includes CRC) and passes all error checking.</p>

- An IN is ignored by an OUT configured endpoint and visa versa.

- The IN and OUT PID status is updated at the end of a transaction.

- The SETUP PID status is updated at the beginning of the Data packet phase.

- The entire Endpoint 0 mode register and the Count register are locked to CPU writes at the end of any transaction to that endpoint in which an ACK is transferred. These registers are only unlocked by a CPU read of the register, which should be done by the firmware only after the transaction is complete. This represents about a 1  $\mu$ s window in which the CPU is locked from register writes to these USB registers. Normally the firmware should perform a register read at the beginning of the Endpoint ISRs to unlock and get the mode register information. The interlock on the Mode and Count registers ensures that the firmware recognizes the changes that the SIE might have made during the previous transaction. Note that the setup bit of the mode register is NOT locked. This means that before writing to the mode register, firmware must first read the register to make sure that the setup bit is not set (which indicates a setup was received, while processing the current USB request). This read unlocks the register. So care must be taken not to overwrite the register elsewhere.

| Table 17. Details of Modes for Differing | J Traffic Conditions (see | e Table 16 for the decode legend) | (continued) |

|------------------------------------------|---------------------------|-----------------------------------|-------------|

| Na  | < In/    | prei | mati  | ure stati | is Out             |          | •       |         | ,       |         |        |       |       | <b>o</b> , |          |          |      |                            |          |

|-----|----------|------|-------|-----------|--------------------|----------|---------|---------|---------|---------|--------|-------|-------|------------|----------|----------|------|----------------------------|----------|

| 1   | 1        | -    | 0     | Out       | 2                  | UC       | valid   | 1       | 1       | updates | UC     | UC    | 1     | 1          | No       | Ch       | ange | ACK                        | yes      |

| 1   | 1        |      | 0     | Out       | 2                  | UC       | valid   | 0       | 1       | updates |        | UC    | 1     | UC         |          |          | -    | Stall                      | yes      |

| 1   | 1        |      | 0     | Out       | _<br>!=2           | UC       | valid   | -       | 1       | updates |        | UC    | 1     | UC         |          |          |      | Stall                      | ves      |

| 1   | 1        |      | 0     | Out       | - <u>-</u><br>> 10 | UC       | X       | UC      | UC      |         | UC     | UC    | UC    | UC         |          |          |      | eignore                    | no       |

| 1   | 1        |      | 0     | Out       | x                  | UC       | invalid | UC      | UC      |         |        | UC    | UC    | UC         |          |          | -    | eignore                    | no       |

|     | 1        | -    | 0     | In        | x                  | UC       | x       | UC      | UC      |         | UC     | 1     |       | UC         |          |          |      | e NAK                      | yes      |

| Sta | tus      | -    |       | ra In     | ^                  | •••      | r -     |         |         |         |        | -     | ••    | ••         |          | •        | ag.  |                            | ,        |

| 0   | 0        | 1    | 0     | Out       | 2                  | UC       | valid   | 1       | 1       | updates | UC     | UC    | 1     | 1          | No       | Ch       | ande | ACK                        | yes      |

| 0   | 0        | 1    | 0     | Out       | 2                  | UC       |         | 0       | 1       | updates |        | UC    | 1     | UC         |          |          |      | Stall                      | yes      |

| 0   | 0        | 1    | 0     | Out       | !=2                | UC       | valid   | updates | 1       | updates |        | UC    | 1     | UC         |          |          | 1 1  |                            | yes      |

| 0   | 0        | 1    | 0     | Out       | > 10               | UC       | x       | UC      | UC      | -       | UC     | UC    | UC    |            |          |          |      | eignore                    | no       |

| 0   | 0        |      | 0     | Out       | X                  | UC       | invalid | UC      | UC      |         | UC     | 1     |       | UC         |          |          |      | eignore                    | no       |

| 0   | 0        | 1    | 0     | In        | х                  | UC       | x       | UC      | UC      |         | UC     | 1     | UC    | UC         |          |          | -    | Stall                      | yes      |

| -   | <u> </u> | I    | Ľ     |           |                    |          |         |         | OUT EN  |         |        | 1     | 1     | 1          | <u> </u> | -        |      |                            | P        |

|     |          | Pro  | per   | ties of   | Incomi             | ng Pack  | et      |         |         |         | by SIE | to In | terna | Regi       | stei     | 's a     | nd I | Node Bits                  |          |

| N   | lode     |      | -     |           |                    | buffer   |         | DTOG    | -       | COUNT   | -      |       |       | -          |          |          |      | Response                   | Intr     |

|     |          |      |       | roneous   |                    |          |         |         |         |         | •      |       |       |            |          |          |      | •                          |          |

| 1   | 0        | 0    | 1     | Out       | <= 10              | data     | valid   | updates | 1       | updates | UC     | UC    | 1     | 1          | 1        | 0        | 0 0  | ACK                        | yes      |

| 1   | 0        | 0    | 1     | Out       | > 10               | junk     | x       | updates | updates | updates | UC     | UC    | 1     | UC         | No       | Ch       | ange | eignore                    | yes      |

| 1   | 0        | 0    | 1     | Out       | х                  | junk     | invalid | updates | 0       | updates | UC     | UC    | 1     | UC         | No       | Ch       | ange | eignore                    | yes      |

| 1   | 0        | 0    | 1     | In        | х                  | UC       | x       | UC      | UC      | UC      | UC     | UC    | UC    | UC         |          |          |      | eignore                    | no       |

|     |          |      |       |           |                    |          |         |         |         |         |        |       |       |            |          |          |      | (STALL <sup>[4]</sup> = 0) |          |

| 1   | 0        | 0    | 1     | In        | х                  | UC       | x       | UC      | UC      | UC      | UC     | UC    | UC    | UC         | No       | Ch       | ange | e Stall                    | no       |

|     |          |      |       |           |                    |          |         |         |         |         |        |       |       |            |          |          |      | (STALL <sup>[4]</sup> = 1) |          |

| NA  | ко       | ut/e | rron  | ieous In  |                    |          |         |         |         |         |        |       |       |            |          |          |      | • /                        |          |

| 1   | 0        |      | 0     | Out       |                    | UC       | valid   | UC      | UC      | UC      | UC     | UC    | 1     | UC         | No       | Ch       | ande | NAK                        | yes      |

| 1   | 0        | 0    | 0     | Out       | > 10               | UC       | x       | UC      | UC      | UC      | UC     | UC    | UC    | UC         |          |          | -    | eignore                    | no       |

| 1   | 0        | 0    | 0     | Out       | х                  | UC       | invalid | UC      | UC      |         | UC     | UC    | UC    | UC         |          |          |      | eignore                    | no       |

| 1   | 0        | 0    | 0     | In        | х                  | UC       | x       | UC      | UC      | UC      | UC     | UC    | UC    | UC         |          |          |      | eignore                    | no       |

| lso | chro     | nou  | is ei | ndpoint   | (Out)              |          |         |         |         |         |        |       |       |            |          |          | Ū    | 0                          |          |

|     |          |      |       |           | • •                | updates  | updates | updates | updates | updates | UC     | UC    | 1     | 1          | No       | Ch       | ange | RX                         | yes      |

| 0   |          |      |       | In        |                    | UC       |         |         |         |         |        | UC    | UC    | UC         | No       | Ch       | ange | eignore                    | no       |

|     |          | -    | -     |           | 1                  |          |         | ı<br>   |         | POINT   |        |       |       |            |          |          | -    |                            | 1        |

|     |          | Pro  | pe    | ties of   | Incomi             | ing Pack | et      |         | Chang   | es made | by SIE | to In | terna | Regi       | stei     | 's a     | nd I | Node Bits                  |          |

| N   | lode     | e Bi | ts    | token     | count              | buffer   | dval    | DTOG    | DVAL    | COUNT   | Setup  | In    | Out   | ACK        | Mo       | ode      | Bits | Response                   | Intr     |

| No  | mal      | In/e | erro  | neous C   | Dut                |          |         |         |         |         |        |       |       |            |          |          |      |                            |          |

| 1   | 1        | 0    | 1     | Out       | х                  | UC       | х       | UC      | UC      | UC      | UC     | UC    | UC    | UC         | No       | Ch       | ange | elignore                   | no       |

|     |          |      |       |           |                    |          |         |         |         |         |        |       |       |            |          |          |      | (STALL <sup>[4]</sup> = 0) |          |

| 1   | 1        | 0    | 1     | Out       | х                  | UC       | x       | UC      | UC      | UC      | UC     | UC    | UC    | UC         | No       | Ch       | ange | estall                     | no       |

|     |          |      |       |           |                    |          |         |         |         |         |        |       |       |            |          |          |      | (STALL <sup>[4]</sup> = 1) |          |

| 1   | 1        | 0    | 1     | In        | х                  | UC       | x       | UC      | UC      | UC      | UC     | 1     | UC    | 1          | 1        | 1        | 0 0  | ACK (back)                 | yes      |

| NA  | K In     | /err |       | ous Out   | I                  | 1        | 1       | 1       | 1       | 1       | I      | I     | I     | I          | 1        | <b>I</b> |      | . ,                        | <u>r</u> |

| _   |          |      |       | Out       | х                  | UC       | х       | UC      | UC      | UC      | UC     | UC    | UC    | UC         | No       | Ch       | ange | ignore                     | no       |

| L   | L        | I    | I     | 1         | 1                  | 1        | 1       | 1       | I       | I       | 1      | 1     | 1     | 1          | I        |          | 0    | 1-                         |          |

Data 0/1

Toggle

Received

Data 0/1

Toggle

STALL

Data 0/1

Toggle

STALL

Size

Endpoint

Data

Valid

Received

Data Valid

Data Valid Byte

Endpoint Mode

Endpoint0 Endpoint0 SETUP IN

Byte

Count Bit 5

Endpoint0 OUT

Received

Byte

Bit 5

Count Bit 5

D+

Upstream

Count

|                                                        |    |      |      |                                     |              |                              |                                           |                                          |                              |                              |                              | -                             |                               |                                          |                       |

|--------------------------------------------------------|----|------|------|-------------------------------------|--------------|------------------------------|-------------------------------------------|------------------------------------------|------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|------------------------------------------|-----------------------|

| 1 ľ                                                    | 1  | 0    | 0    | In                                  | х            | UC >                         | c l                                       | JC                                       | UC U                         | IC UC                        | C 1                          | UC UC                         | No Char                       | nge NAK                                  | yes                   |

| lsoc                                                   | hr | onol | is e | endpoint                            | (In)         |                              |                                           | •                                        | •                            |                              |                              |                               |                               |                                          |                       |

| 0                                                      | 1  | 1    | 1    | Out                                 | х            | UC >                         | د ا                                       | UC                                       | UC U                         | IC UC                        | C UC                         | UC UC                         | No Char                       | nge ignore                               | no                    |

| 0                                                      | 1  | 1    | 1    | In                                  | х            | UC >                         | د ا                                       | UC                                       | UC U                         | IC UC                        | 2 1                          | UC UC                         | No Char                       | nge TX                                   | yes                   |

| Re                                                     | -  |      |      | Summ                                | -            |                              |                                           |                                          |                              |                              |                              |                               |                               | Read/W/rite/                             | Default               |

|                                                        | 1  | ١ddr |      | Register                            | Name         | Bit 7                        | Bit 6                                     | Bit 5                                    | Bit 4                        | Bit 3                        | Bit 2                        | Bit 1                         | Bit 0                         | Read/Write/<br>Both <sup>[5, 6, 7]</sup> | Default/<br>Reset [8] |

| m                                                      | 0> | (00  | Pc   | ort 0 Data                          |              | P0.7                         | P0.6                                      | P0.5                                     | P0.4                         | P0.3                         | P0.2                         | P0.1                          | P0.0                          | bbbbbbbb                                 | 11111111              |

| 2 AND                                                  | 0> | (01  | Pc   | ort 1 Data                          |              | P1.7                         | P1.6                                      | P1.5                                     | P1.4                         | P1.3                         | P1.2                         | P1.1                          | P1.0                          | bbbbbbbb                                 | 11111111              |

| Z                                                      | 0> | (02  | Pc   | ort 2 Data                          |              | P2.7                         | P2.6                                      | P2.5                                     | P2.4                         | P2.3                         | P2.2                         | P2.1                          | P2.0                          | bbbbbbbb                                 | 11111111              |

| °, 1, .                                                | 0> | (03  | Pc   | ort 3 Data                          |              |                              | P3.6<br>CY7C661130<br>only                | P3.5<br>CY7C6611:<br>only                | P3.4                         | P3.3                         | P3.2                         | P3.1                          | P3.0                          | bbbbbbbb                                 | -1111111              |

| OKIN                                                   | 0> | (04  |      | ort 0 Interi<br>able                | rupt         |                              | P0.6 Intr<br>Enable                       | P0.5 Intr<br>Enable                      | P0.4 Intr<br>Enable          | P0.3 Intr<br>Enable          | P0.2 Int<br>Enable           | Enable                        | P0.0 Intr<br>Enable           | wwwwwww                                  | 0000000               |

|                                                        | 0> | (05  | Er   | ort 1 Interi<br>able                | •            | Enable                       | P1.6 Intr<br>Enable                       | P1.5 Intr<br>Enable                      | Enable                       | P1.3 Intr<br>Enable          | P1.2 Int<br>Enable           | Enable                        | P1.0 Intr<br>Enable           | wwwwwww                                  | 0000000               |

| JRAT                                                   | 0> | (06  | Er   | ort 2 Interi<br>able                |              | Enable                       | P2.6 Intr<br>Enable                       | P2.5 Intr<br>Enable                      | Enable                       | P2.3 Intr<br>Enable          | P2.2 Int<br>Enable           | Enable                        | P2.0 Intr<br>Enable           | wwwwwww                                  | 0000000               |

| HAPIGPIO CONFIGURATION PORTS 0, 1,<br>1 <sup>2</sup> C | 0> | (07  |      | ort 3 Interi<br>able                | rupt         |                              | P3.6 Intr<br>Enable<br>CY7C661130<br>only | P3.5 Intr<br>Enable<br>CY7C6611:<br>only | E a a la la                  | P3.3 Intr<br>Enable          | P3.2 Int<br>Enable           | r P3.1 Intr<br>Enable         | P3.0 Intr<br>Enable           | wwwwwww                                  | 00000000              |

| GPIO C                                                 | 0> | (08  |      | PIO<br>onfiguratio                  | on           | Port 3<br>Config Bit<br>1    | Port 3<br>Config Bit<br>0                 | Port 2<br>Config B<br>1                  | Port 2<br>it Config B<br>0   | Port 1<br>it Config B<br>1   | Port 1<br>t Config E<br>0    | Port 0<br>Bit Config Bit<br>1 | Port 0<br>Config Bit<br>0     | bbbbbbbb                                 | 0000000               |

|                                                        | 0> | (09  |      | API/I <sup>2</sup> C<br>onfiguratio | on           | l <sup>2</sup> C<br>Position | Reserved                                  | LEMPTY<br>Polarity                       | DRDY<br>Polarity             | Latch<br>Empty               | Data<br>Ready                | Port Width<br>bit 1           | Port Width                    | b-bbrrbb                                 | 0000000               |

| Endpoint A0, AI<br>and A2 Configuration                | 0> | (10  |      | SB Device<br>Idress A               | <del>)</del> | Address A                    | Device<br>Address<br>A Bit 6              | Device<br>Address<br>A Bit 5             | Device<br>Address<br>A Bit 4 | Device<br>Address<br>A Bit 3 | Device<br>Address<br>A Bit 2 | Device Ad<br>dress<br>A Bit 1 | -Device<br>Address<br>A Bit 0 | bbbbbbbb                                 | 0000000               |

Byte Count Bit 4

ACK

Byte Count

Bit 4

ACK

Byte Count Bit 4

ACK

D-

Upstream

Byte Count Bit 3

Byte Count

Bit 3

Byte Count Bit 3

Bus Activity

Byte Count Bit 2

Byte Count

Bit 2

Byte

Count Bit 2

Mode Bit 3 Mode Bit 2 Mode Bit 1

Control

Bit 2

Byte CountByte Bit 1 Cour

Byte Count Byte

Byte Count Byte

Mode Bit 3 Mode Bit 2 Mode Bit 1 Mode Bit 0 bbbbbbbb

Mode Bit 3 Mode Bit 2 Mode Bit 1 Mode Bit 0 bbbbbbbb

Bit 1

Bit 1

Control Bit 1

Count

Bit 0

Count Bit 0

Count Bit 0

Control

Bit 0

#### Table 17. Details of Modes for Differing Traffic Conditions (see Table 16 for the decode legend) (continued)

Notes

USB-Endpoint A0, AI AND A2 Configuration CS

5. B: Read and Write.

6. W: Write.

7. R: Read.

8. X: Unknown

0x11

0x12

0x13

0x14

0x15

0x16

0x1F

EP A0 Counter

EP A0 Mode Register

EP A1 Counter Register

EP A1 Mode

EP A2 Mode

EP A2 Counter

Register

Register

Register USB Status and

Control

Register

00000000

00000000

0000000

00000000

00000000

00000000

-0xx0000

bbbbbbbb

bbbbbbbb

bbbbbbbb

bbrrbbbb

Mode Bit 0bbbbbbbb

## Register Summary (continued)

|                                                              | Addr | Register Name                          | Bit 7                      | Bit 6                      | Bit 5                        | Bit 4                        | Bit 3                          | Bit 2                        | Bit 1                          | Bit 0                                       | Read/Write/<br>Both <sup>[5, 6, 7]</sup> | Default/<br>Reset <sup>[8]</sup> |

|--------------------------------------------------------------|------|----------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--------------------------------|------------------------------|--------------------------------|---------------------------------------------|------------------------------------------|----------------------------------|

| RUPT                                                         |      | Global Interrupt<br>Enable             |                            | Enable                     | Interrupt<br>Enable          | Enable                       | Enable                         | Enable                       | 128 μs<br>Interrupt<br>Enable  | USB Bus<br>RESET In-<br>terrupt En-<br>able |                                          | -0000000                         |

| INTERRUPT                                                    |      | Endpoint Interrupt<br>Enable           | Reserved                   | Reserved                   |                              | EPB1<br>Interrupt<br>Enable  | EPB0<br>Interrupt<br>Enable    |                              | EPA1<br>Interrupt<br>Enable    | EPA0<br>Interrupt<br>Enable                 | bbbbb                                    | 00000                            |

| R                                                            | 0x24 | Timer (LSB)                            | Timer Bit 7                | Timer Bit 6                | Timer Bit 5                  | Timer Bit 4                  | Timer Bit 3                    | Timer Bit 2                  | Timer Bit 1                    | Timer Bit 0                                 | rrrrrrr                                  | 00000000                         |

| TIMER                                                        | 0x25 | Timer (MSB)                            | Reserved                   | Reserved                   | Reserved                     | Reserved                     | Timer Bit<br>11                | Timer Bit<br>10              | Time Bit 9                     | Timer Bit 8                                 | rrrr                                     | 0000                             |

|                                                              | 0x28 | I <sup>2</sup> C Control and<br>Status |                            | Busy                       | Xmit<br>Mode                 | ACK                          | Addr                           | ARB Lost/<br>Restart         | Stop                           | l <sup>2</sup> C<br>Enable                  | bbbbbbbb                                 | 00000000                         |

| ç                                                            | 0x29 | I <sup>2</sup> C Data                  | I <sup>2</sup> C Data 7    | I <sup>2</sup> C Data 6    | I <sup>2</sup> C Data 5      | I <sup>2</sup> C Data 4      | I <sup>2</sup> C Data 3        | I <sup>2</sup> C Data 2      | I <sup>2</sup> C Data 1        | I <sup>2</sup> C Data 0                     | bbbbbbbb                                 | XXXXXXXX                         |

| RATION                                                       | 0x40 | USB Device<br>Address B                |                            |                            |                              | Device<br>Address B<br>Bit 4 | Device<br>Address B<br>Bit 3   | Device<br>Address B<br>Bit 2 | Device<br>Address B<br>Bit 1   | Device<br>Address B<br>Bit 0                | bbbbbbbb                                 | 00000000                         |