Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-VQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega48v-10mmu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 22.11. Register Description                                         |     |

|---------------------------------------------------------------------|-----|

| 23. SPI – Serial Peripheral Interface                               | 222 |

| 23.1. Features                                                      |     |

| 23.1. Peatures                                                      |     |

| 23.2. Overview                                                      |     |

| 23.4. Data Modes                                                    |     |

| 23.5. Register Description                                          |     |

|                                                                     |     |

| 24. USART - Universal Synchronous Asynchronous Receiver Transceiver | 232 |

| 24.1. Features                                                      |     |

| 24.2. Overview                                                      | 232 |

| 24.3. Block Diagram                                                 |     |

| 24.4. Clock Generation                                              | 233 |

| 24.5. Frame Formats                                                 | 236 |

| 24.6. USART Initialization                                          | 237 |

| 24.7. Data Transmission – The USART Transmitter                     |     |

| 24.8. Data Reception – The USART Receiver                           |     |

| 24.9. Asynchronous Data Reception                                   | 244 |

| 24.10. Multi-Processor Communication Mode                           |     |

| 24.11. Examples of Baud Rate Setting                                | 247 |

| 24.12. Register Description                                         | 250 |

|                                                                     | 061 |

| 25. USARTSPI - USART in SPI Mode                                    |     |

| 25.1. Features                                                      |     |

| 25.2. Overview                                                      |     |

| 25.3. Clock Generation                                              |     |

| 25.4. SPI Data Modes and Timing                                     |     |

| 25.5. Frame Formats                                                 |     |

| 25.6. Data Transfer                                                 |     |

| 25.7. AVR USART MSPIM vs. AVR SPI                                   |     |

| 25.8. Register Description                                          |     |

| 26. TWI - 2-wire Serial Interface                                   |     |

| 26.1. Features                                                      | 267 |

| 26.2. Two-Wire Serial Interface Bus Definition                      |     |

| 26.3. Data Transfer and Frame Format                                |     |

| 26.4. Multi-master Bus Systems, Arbitration, and Synchronization    |     |

| 26.5. Overview of the TWI Module                                    |     |

| 26.6. Using the TWI                                                 |     |

| 26.7. Transmission Modes                                            |     |

| 26.8. Multi-master Systems and Arbitration                          |     |

| 26.9. Register Description                                          |     |

| 27 AC Apples Comparator                                             | 206 |

| 27. AC - Analog Comparator                                          |     |

| 27.1. Overview                                                      |     |

| 27.2. Analog Comparator Multiplexed Input                           |     |

| 27.3. Register Description                                          |     |

```

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR,r16

; Write logical one to EEMPE

sbi EECR,EEMPE

; Start eeprom write by setting EEPE

sbi EECR,EEPE

ret

```

#### C Code Example<sup>(1)</sup>

```

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EPE))

;

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR |= (1<<EEMPE);

/* Start eeprom write by setting EEPE */

EECR |= (1<<EEPE);

}</pre>

```

Note: (1) Please refer to About Code Examples

The next code examples show assembly and C functions for reading the EEPROM. The examples assume that interrupts are controlled so that no interrupts will occur during execution of these functions.

#### Assembly Code Example<sup>(1)</sup>

```

EEPROM_read:

; Wait for completion of previous write

sbic EECR,EEPE

rjmp EEPROM_read

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Start eeprom read by writing EERE

sbi EECR,EERE

; Read data from Data Register

in r16,EEDR

ret

```

C Code Example<sup>(1)</sup>

```

unsigned char EEPROM_read(unsigned int uiAddress)

{

/* Wait for completion of previous write */

while(EECR & (1<<EPE))

;

/* Set up address register */

EEAR = uiAddress;

/* Start eeprom read by writing EERE */

EECR |= (1<<EERE);

/* Return data from Data Register */

return EEDR;

}</pre>

```

1. Refer to About Code Examples.

#### Assembly Code Example

```

Move_interrupts:

; Get MCUCR

in r16, MCUCR

mov r17, r16

; Enable change of Interrupt Vectors

ori r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ori r17, (1<<IVSEL)

out MCUCR, r17

ret

```

### C Code Example

void Move\_interrupts(void)

{

uchar temp;

/\* GET MCUCR\*/

temp = MCUCR;

/\* Enable change of Interrupt Vectors \*/

MCUCR = temp|(1<<IVCE);

/\* Move interrupts to Boot Flash section \*/

MCUCR = temp|(1<<IVSEL);

}</pre>

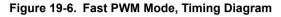

frequency of the Fast PWM mode can be twice as high as the phase correct PWM modes, which use dual-slope operation. This high frequency makes the Fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

In Fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the Fast PWM mode is shown below. The TCNT0 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal lines on the TCNT0 slopes mark compare matches between OCR0x and TCNT0.

The Timer/Counter Overflow Flag (TOV0) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In Fast PWM mode, the compare unit allows generation of PWM waveforms on the OC0x pins. Writing the TCCR0A.COM0x[1:0] bits to 0x2 will produce a non-inverted PWM; TCCR0A.COM0x[1:0]=0x3 will produce an inverted PWM output. Writing the TCCR0A.COM0A[1:0] bits to 0x1 allows the OC0A pin to toggle on Compare Matches if the TCCRnB.WGMn2 bit is set. This option is not available for the OC0B pin. The actual OC0x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC0x Register at the compare match between OCR0x and TCNT0, and clearing (or setting) the OC0x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{\text{OCnxPWM}} = \frac{f_{\text{clk}\_I/0}}{N \cdot 256}$$

N represents the prescale divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR0A register represents special cases for PWM waveform output in the Fast PWM mode: If OCR0A is written equal to BOTTOM, the output will be a narrow spike for each MAX +1 timer clock cycle. Writing OCR0A=MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM0A[1:0] bits.)

# **Atmel**

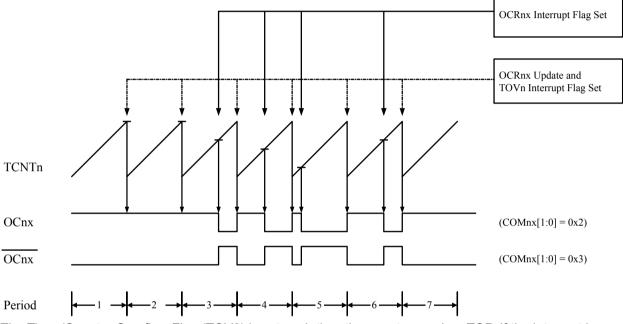

#### Figure 20-5. Compare Match Output Unit, Schematic

**Note:** The "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B).

The general I/O port function is overridden by the Output Compare (OC1x) from the Waveform Generator if either of the TCCR1A.COM1x[1:0] bits are set. However, the OC1x pin direction (input or output) is still controlled by the Data Direction Register (DDR) for the port pin. The Data Direction Register bit for the OC1x pin (DDR\_OC1x) must be set as output before the OC1x value is visible on the pin. The port override function is generally independent of the Waveform Generation mode, but there are some exceptions.

The design of the Output Compare pin logic allows initialization of the OC1x state before the output is enabled. Note that some TCCR1A.COM1x[1:0] bit settings are reserved for certain modes of operation.

The TCCR1A.COM1x[1:0] bits have no effect on the Input Capture unit.

#### 20.11.1. Compare Output Mode and Waveform Generation

The Waveform Generator uses the TCCR1A.COM1x[1:0] bits differently in normal, CTC, and PWM modes. For all modes, setting the TCCR1A.COM1x[1:0] = 0 tells the Waveform Generator that no action on the OC1x Register is to be performed on the next compare match. Refer also to the descriptions of the output modes.

A change of the TCCR1A.COM1x[1:0] bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the TCCR1C.FOC1x strobe bits.

## 20.12. Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the combination of the Waveform Generation mode (WGM1[3:0]) and Compare Output mode (TCCR1A.COM1x[1:0]) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The TCCR1A.COM1x[1:0] bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the TCCR1A.COM1x[1:0] bits control whether the output should be set, cleared, or toggle at a compare match.

In Fast PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Writing the COM1x[1:0] bits to 0x2 will produce an inverted PWM and a non-inverted PWM output can be generated by writing the COM1x[1:0] to 0x3. The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1, and clearing (or setting) the OC1x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{\text{OCnxPWM}} = \frac{f_{\text{clk}\_I/O}}{N \cdot (1 + \text{TOP})}$$

Note:

- The "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B).

- *N* represents the prescale divider (1, 8, 64, 256, or 1024).

The extreme values for the OCR1x registers represents special cases when generating a PWM waveform output in the Fast PWM mode. If the OCR1x is set equal to BOTTOM (0x0000) the output will be a narrow spike for each TOP+1 timer clock cycle. Setting the OCR1x equal to TOP will result in a constant high or low output (depending on the polarity of the output which is controlled by COM1x[1:0]).

A frequency waveform output with 50% duty cycle can be achieved in Fast PWM mode by selecting OC1A to toggle its logical level on each compare match (COM1A[1:0]=0x1). This applies only if OCR1A is used to define the TOP value (WGM1[3:0]=0xF). The waveform generated will have a maximum frequency of  $f_{OC1A} = f_{clk\_l/O}/2$  when OCR1A is set to zero (0x0000). This feature is similar to the OC1A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the Fast PWM mode.

## 20.12.4. Phase Correct PWM Mode

The Phase Correct Pulse Width Modulation or Phase Correct PWM modes (WGM1[3:0]= 0x1, 0x2, 0x3, 0xA, and 0xB) provide a high resolution, phase correct PWM waveform generation option. The Phase Correct PWM mode is, like the phase and frequency correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC1x) is cleared on the compare match between TCNT1 and OCR1x while up-counting, and set on the compare match while down-counting. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The PWM resolution for the Phase Correct PWM mode can be fixed to 8-, 9-, or 10-bit, or defined by either ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to 0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM resolution in bits can be calculated by using the following equation:

$R_{\rm PCPWM} = \frac{\log(\rm TOP+1)}{\log(2)}$

In Phase Correct PWM mode the counter is incremented until the counter value matches either one of the fixed values 0x00FF, 0x01FF, or 0x03FF (WGM1[3:0]= 0x1, 0x2, or 0x3), the value in ICR1 (WGM1[3:0]=0xA), or the value in OCR1A (WGM1[3:0]=0xB). The counter has then reached the TOP and changes the count direction. The TCNT1 value will be equal to TOP for one timer clock cycle. The timing diagram for the Phase Correct PWM mode is shown below, using OCR1A or ICR1 to define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The

#### 20.14.4. TC1 Counter Value Low byte

|        | Name:<br>Offset:<br>Reset:<br>Property | TCNT1L<br>0x84<br>0x00<br>: - |     |      |         |     |     |     |  |

|--------|----------------------------------------|-------------------------------|-----|------|---------|-----|-----|-----|--|

| Bit    | 7                                      | 6                             | 5   | 4    | 3       | 2   | 1   | 0   |  |

|        |                                        |                               |     | TCNT | 1L[7:0] |     |     |     |  |

| Access | R/W                                    | R/W                           | R/W | R/W  | R/W     | R/W | R/W | R/W |  |

| Reset  | 0                                      | 0                             | 0   | 0    | 0       | 0   | 0   | 0   |  |

#### Bits 7:0 – TCNT1L[7:0]: Timer/Counter 1 Counter Value Low byte

The two Timer/Counter I/O locations (TCNT1H and TCNT1L, combined TCNT1) give direct access, both for read and for write operations, to the Timer/Counter unit 16-bit counter. To ensure that both the high and low bytes are read and written simultaneously when the CPU accesses these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. Refer to Accessing 16-bit Registers for details.

Modifying the counter (TCNT1) while the counter is running introduces a risk of missing a compare match between TCNT1 and one of the OCR1x Registers.

Writing to the TCNT1 Register blocks (removes) the compare match on the following timer clock for all compare units.

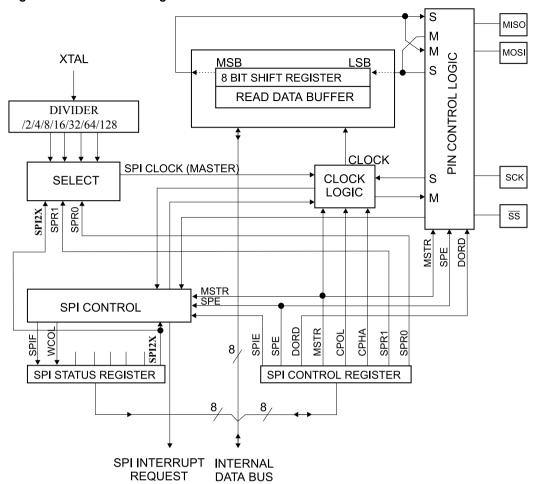

Figure 23-1. SPI Block Diagram

Note: Refer to the pin-out description and the IO Port description for SPI pin placement.

The interconnection between Master and Slave CPUs with SPI is shown in the figure below. The system consists of two shift registers, and a Master Clock generator. The SPI Master initiates the communication cycle when pulling low the Slave Select  $\overline{SS}$  pin of the desired Slave. Master and Slave prepare the data to be sent in their respective shift Registers, and the Master generates the required clock pulses on the SCK line to interchange data. Data is always shifted from Master to Slave on the Master Out – Slave In, MOSI, line, and from Slave to Master on the Master In – Slave Out, MISO, line. After each data packet, the Master will synchronize the Slave by pulling high the Slave Select,  $\overline{SS}$ , line.

When configured as a Master, the SPI interface has no automatic control of the  $\overline{SS}$  line. This must be handled by user software before communication can start. When this is done, writing a byte to the SPI Data Register starts the SPI clock generator, and the hardware shifts the eight bits into the Slave. After shifting one byte, the SPI clock generator stops, setting the end of Transmission Flag (SPIF). If the SPI Interrupt Enable bit (SPIE) in the SPCR Register is set, an interrupt is requested. The Master may continue to shift the next byte by writing it into SPDR, or signal the end of packet by pulling high the Slave Select,  $\overline{SS}$  line. The last incoming byte will be kept in the Buffer Register for later use.

When configured as a Slave, the SPI interface will remain sleeping with MISO tri-stated as long as the  $\overline{SS}$  pin is driven high. In this state, software may update the contents of the SPI Data Register, SPDR, but the data will not be shifted out by incoming clock pulses on the SCK pin until the  $\overline{SS}$  pin is driven low. As one byte has been completely shifted, the end of Transmission Flag, SPIF is set. If the SPI Interrupt Enable bit, SPIE, in the SPCR Register is set, an interrupt is requested. The Slave may continue to place new

# 25. USARTSPI - USART in SPI Mode

# 25.1. Features

- Full Duplex, Three-wire Synchronous Data Transfer

- Master Operation

- Supports all four SPI Modes of Operation (Mode 0, 1, 2, and 3)

- LSB First or MSB First Data Transfer (Configurable Data Order)

- Queued Operation (Double Buffered)

- High Resolution Baud Rate Generator

- High Speed Operation (f<sub>XCKmax</sub> = f<sub>CK</sub>/2)

- Flexible Interrupt Generation

## 25.2. Overview

The Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART) can be set to a master SPI compliant mode of operation.

Setting both UMSELn[1:0] bits to one enables the USART in MSPIM logic. In this mode of operation the SPI master control logic takes direct control over the USART resources. These resources include the transmitter and receiver shift register and buffers, and the baud rate generator. The parity generator and checker, the data and clock recovery logic, and the RX and TX control logic is disabled. The USART RX and TX control logic is replaced by a common SPI transfer control logic. However, the pin control logic and interrupt generation logic is identical in both modes of operation.

The I/O register locations are the same in both modes. However, some of the functionality of the control registers changes when using MSPIM.

## 25.3. Clock Generation

The Clock Generation logic generates the base clock for the Transmitter and Receiver. For USART MSPIM mode of operation only internal clock generation (i.e. master operation) is supported. The Data Direction Register for the XCKn pin (DDR\_XCKn) must therefore be set to one (i.e. as output) for the USART in MSPIM to operate correctly. Preferably the DDR\_XCKn should be set up before the USART in MSPIM is enabled (i.e. TXENn and RXENn bit set to one).

The internal clock generation used in MSPIM mode is identical to the USART synchronous master mode. The table below contains the equations for calculating the baud rate or UBRRn setting for Synchronous Master Mode.

| Operating Mode          | Equation for Calculating Baud<br>Rate <sup>(1)</sup> | Equation for Calculating UBRRn<br>Value                        |

|-------------------------|------------------------------------------------------|----------------------------------------------------------------|

| Synchronous Master mode | $BAUD = \frac{f_{OSC}}{2(UBRRn + 1)}$                | $\mathbf{UBRR}n = \frac{f_{\mathrm{OSC}}}{2\mathrm{BAUD}} - 1$ |

#### Table 25-1. Equations for Calculating Baud Rate Register Setting

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps)

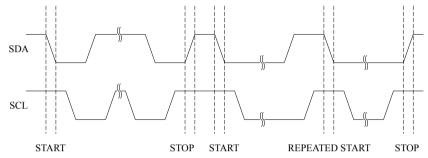

### 26.3.2. START and STOP Conditions

The Master initiates and terminates a data transmission. The transmission is initiated when the Master issues a START condition on the bus, and it is terminated when the Master issues a STOP condition. Between a START and a STOP condition, the bus is considered busy, and no other master should try to seize control of the bus. A special case occurs when a new START condition is issued between a START and STOP condition. This is referred to as a REPEATED START condition, and is used when the Master wishes to initiate a new transfer without relinquishing control of the bus. After a REPEATED START, the bus is considered busy until the next STOP. This is identical to the START behavior, and therefore START is used to describe both START and REPEATED START for the remainder of this datasheet, unless otherwise noted. As depicted below, START and STOP conditions are signaled by changing the level of the SDA line when the SCL line is high.

#### Figure 26-3. START, REPEATED START, and STOP conditions

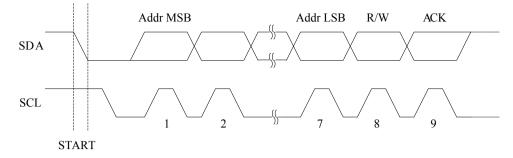

#### 26.3.3. Address Packet Format

All address packets transmitted on the TWI bus are nine bits long, consisting of seven address bits, one READ/WRITE control bit and an acknowledge bit. If the READ/WRITE bit is set, a read operation is to be performed, otherwise a write operation should be performed. When a Slave recognizes that it is being addressed, it should acknowledge by pulling SDA low in the ninth SCL (ACK) cycle. If the addressed Slave is busy, or for some other reason can not service the Master's request, the SDA line should be left high in the ACK clock cycle. The Master can then transmit a STOP condition, or a REPEATED START condition to initiate a new transmission. An address packet consisting of a slave address and a READ or a WRITE bit is called SLA+R or SLA+W, respectively.

The MSB of the address byte is transmitted first. Slave addresses can freely be allocated by the designer, but the address '0000 000' is reserved for a general call.

When a general call is issued, all slaves should respond by pulling the SDA line low in the ACK cycle. A general call is used when a Master wishes to transmit the same message to several slaves in the system. When the general call address followed by a Write bit is transmitted on the bus, all slaves set up to acknowledge the general call will pull the SDA line low in the ACK cycle. The following data packets will then be received by all the slaves that acknowledged the general call. Note that transmitting the general call address followed by a Read bit is meaningless, as this would cause contention if several slaves started transmitting different data.

All addresses of the format '1111 xxx' should be reserved for future purposes.

Figure 26-4. Address Packet Format

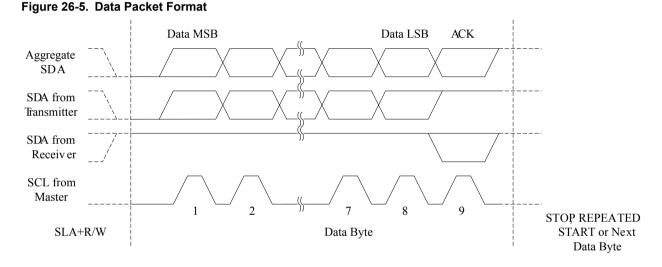

#### 26.3.4. Data Packet Format

All data packets transmitted on the TWI bus are nine bits long, consisting of one data byte and an acknowledge bit. During a data transfer, the Master generates the clock and the START and STOP conditions, while the Receiver is responsible for acknowledging the reception. An Acknowledge (ACK) is signalled by the Receiver pulling the SDA line low during the ninth SCL cycle. If the Receiver leaves the SDA line high, a NACK is signalled. When the Receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the Transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first.

#### 26.3.5. Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the "Wired-ANDing" of the SCL line can be used to implement handshaking between the Master and the Slave. The Slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the Master is too fast for the Slave, or the Slave needs extra time for processing between the data transmissions. The Slave extending the SCL low period will not affect the SCL high period, which is determined by the Master. As a consequence, the Slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

The following figure depicts a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control of the bus.

| Table 26-3. Status Codes for Master Transmitter Mode |

|------------------------------------------------------|

|------------------------------------------------------|

| Status Code             | Status of the 2-wire Serial                              | Application S        | oftwai        | re Res | Next Action Taken by TWI |   |                                                                                                        |  |

|-------------------------|----------------------------------------------------------|----------------------|---------------|--------|--------------------------|---|--------------------------------------------------------------------------------------------------------|--|

| (TWSR)                  | Bus and 2-wire Serial<br>Interface Hardware              | To/from              | To TWCRn      |        |                          |   | Hardware                                                                                               |  |

| Prescaler<br>Bits are 0 |                                                          | TWDR                 | STA STO TWINT |        | TWEA                     |   |                                                                                                        |  |

| 0x08                    | A START condition has been transmitted                   | Load SLA+W           | 0             | 0      | 1                        | х | SLA+W will be transmitted;<br>ACK or NOT ACK will be<br>received                                       |  |

| 0x10                    | A repeated START condition has been transmitted          | Load SLA+W<br>or     | 0             | 0      | 1                        | х | SLA+W will be transmitted;<br>ACK or NOT ACK will be<br>received                                       |  |

|                         |                                                          | Load SLA+R           | 0             | 0      | 1                        | х | SLA+R will be transmitted;<br>Logic will switch to Master<br>Receiver mode                             |  |

| 0x18                    | SLA+W has been transmitted;<br>ACK has been received     | Load data<br>byte or | 0             | 0      | 1                        | х | Data byte will be transmitted<br>and ACK or NOT ACK will be<br>received                                |  |

|                         |                                                          | No TWDR<br>action or | 1             | 0      | 1                        | Х | Repeated START will be transmitted                                                                     |  |

|                         |                                                          | No TWDR<br>action or | 0             | 1      | 1                        | Х | STOP condition will be<br>transmitted and TWSTO Flag<br>will be reset                                  |  |

|                         |                                                          | No TWDR<br>action    | 1             | 1      | 1                        | Х | STOP condition followed by a<br>START condition will be<br>transmitted and TWSTO Flag<br>will be reset |  |

| 0x20                    | SLA+W has been transmitted;<br>NOT ACK has been received | Load data<br>byte or | 0             | 0      | 1                        | х | Data byte will be transmitted<br>and ACK or NOT ACK will be<br>received                                |  |

|                         |                                                          | No TWDR<br>action or | 1             | 0      | 1                        | Х | Repeated START will be transmitted                                                                     |  |

|                         |                                                          | No TWDR<br>action or | 0             | 1      | 1                        | х | STOP condition will be<br>transmitted and TWSTO Flag<br>will be reset                                  |  |

|                         |                                                          | No TWDR<br>action    | 1             | 1      | 1                        | Х | STOP condition followed by a<br>START condition will be<br>transmitted and TWSTO Flag<br>will be reset |  |

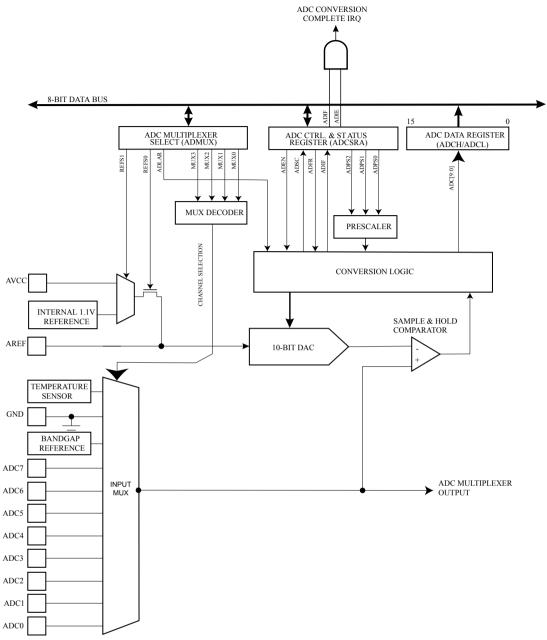

Figure 28-1. Analog to Digital Converter Block Schematic Operation

The analog input channel is selected by writing to the MUX bits in the ADC Multiplexer Selection register ADMUX.MUX[3:0]. Any of the ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected as single ended inputs to the ADC. The ADC is enabled by writing a '1' to the ADC Enable bit in the ADC Control and Status Register A (ADCSRA.ADEN). Voltage reference and input channel selections will not take effect until ADEN is set. The ADC does not consume power when ADEN is cleared, so it is recommended to switch off the ADC before entering power saving sleep modes.

The ADC generates a 10-bit result which is presented in the ADC Data Registers, ADCH and ADCL. By default, the result is presented right adjusted, but can optionally be presented left adjusted by setting the ADC Left Adjust Result bit ADMUX.ADLAR.

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data Registers belongs to the same conversion: Once ADCL is read, ADC access to Data Registers is blocked. This means that if

erased after a system reset. Note that it is not possible to write more than one time to each address without erasing the temporary buffer.

If the EEPROM is written in the middle of an SPM Page Load operation, all data loaded will be lost.

#### 30.1.3. Performing a Page Write

To execute Page Write, set up the address in the Z-pointer(R30 and R31), write "0x00000101" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored. The page address must be written to PCPAGE ([Z12:Z6]). Other bits in the Z-pointer must be written to zero during this operation.

• The CPU is halted during the Page Write operation

# 30.2. Addressing the Flash During Self-Programming

The Z-pointer (R30 and R31) is used to address the SPM commands.

| Bit      | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| ZH (R31) | Z15 | Z14 | Z13 | Z12 | Z11 | Z10 | Z9 | Z8 |

| ZL (R30) | Z7  | Z6  | Z5  | Z4  | Z3  | Z2  | Z1 | Z0 |

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

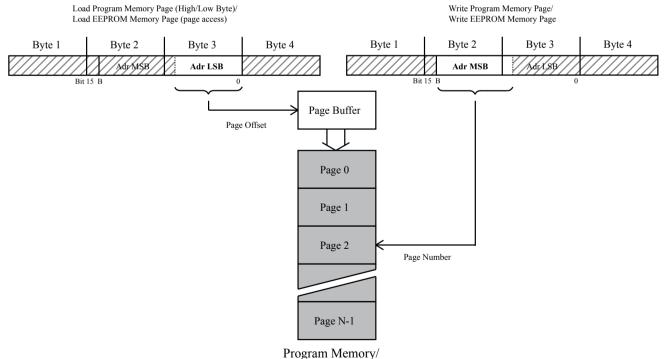

Since the Flash is organized in pages (Please refer to *Page Size* section in Memory Programming chapter), the Program Counter can be treated as having two different sections. One section, consisting of the least significant bits, is addressing the words within a page, while the most significant bits are addressing the pages. This is shown in the following figure. Note that the Page Erase and Page Write operations are addressed independently. Therefore it is of major importance that the software addresses the same page in both the Page Erase and Page Write operation.

The Load Program Memory (LPM) instruction uses the Z-pointer to store the address. Since this instruction addresses the Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used.

To program and verify the device in the serial programming mode, the following sequence is recommended (See Serial Programming Instruction set in Table 32-18:

1. Power-up sequence:

Apply power between  $V_{CC}$  and GND while RESET and SCK are set to "0". In some systems, the programmer can not guarantee that SCK is held low during power-up. In this case, RESET must be given a positive pulse of at least two CPU clock cycles duration after SCK has been set to "0".

- 2. Wait for at least 20ms and enable serial programming by sending the Programming Enable serial instruction to pin MOSI.

- 3. The serial programming instructions will not work if the communication is out of synchronization. When in sync. the second byte (0x53), will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all four bytes of the instruction must be transmitted. If the 0x53 did not echo back, give RESET a positive pulse and issue a new Programming Enable command.

- 4. The Flash is programmed one page at a time. The memory page is loaded one byte at a time by supplying the 6 LSB of the address and data together with the Load Program Memory Page instruction. To ensure correct loading of the page, the data low byte must be loaded before data high byte is applied for a given address. The Program Memory Page is stored by loading the Write Program Memory Page instruction with the 7 MSB of the address. If polling (RDY/BSY) is not used, the user must wait at least t<sub>WD\_FLASH</sub> before issuing the next page . Accessing the serial programming interface before the Flash write operation completes can result in incorrect programming.

- 5. A: The EEPROM array is programmed one byte at a time by supplying the address and data together with the appropriate Write instruction. An EEPROM memory location is first automatically erased before new data is written. If polling (RDY/BSY) is not used, the user must wait at least t<sub>WD\_EEPROM</sub> before issuing the next byte. In a chip erased device, no 0xFFs in the data file(s) need to be programmed.

B: The EEPROM array is programmed one page at a time. The Memory page is loaded one byte at a time by supplying the 6 LSB of the address and data together with the Load EEPROM Memory Page instruction. The EEPROM Memory Page is stored by loading the Write EEPROM Memory Page Instruction with the 7 MSB of the address. When using EEPROM page access only byte locations loaded with the Load EEPROM Memory Page instruction is altered. The remaining locations remain unchanged. If polling (RDY/ $\overline{BSY}$ ) is not used, the used must wait at least t<sub>WD\_EEPROM</sub> before issuing the next byte. In a chip erased device, no 0xFF in the data file(s) need to be programmed.

- 6. Any memory location can be verified by using the Read instruction which returns the content at the selected address at serial output MISO.

- 7. At the end of the programming session, RESET can be set high to commence normal operation.

- 8. Power-off sequence (if needed): Set RESET to "1".

Turn V<sub>CC</sub> power off.

#### Table 32-17. Typical Wait Delay Before Writing the Next Flash or EEPROM Location

| Symbol                 | Minimum Wait Delay |

|------------------------|--------------------|

| t <sub>WD_FLASH</sub>  | 2.6ms              |

| t <sub>WD_EEPROM</sub> | 3.6ms              |

| Instruction/Operation    |        | Instruction Format |        |              |  |  |  |

|--------------------------|--------|--------------------|--------|--------------|--|--|--|

|                          | Byte 1 | Byte 2             | Byte 3 | Byte 4       |  |  |  |

| Write Fuse High bits     | 0xAC   | 0xA8               | 0x00   | data byte in |  |  |  |

| Write Extended Fuse Bits | 0xAC   | 0xA4               | 0x00   | data byte in |  |  |  |

#### Note:

- 1. Not all instructions are applicable for all parts.

- 2. a = address.

- 3. Bits are programmed '0', unprogrammed '1'.

- 4. To ensure future compatibility, unused Fuses and Lock bits should be unprogrammed ('1').

- 5. Refer to the corresponding section for Fuse and Lock bits, Calibration and Signature bytes and Page size.

- 6. Instructions accessing program memory use a word address. This address may be random within the page range.

- 7. See http://www.atmel.com/avr for Application Notes regarding programming and programmers.

- 8. WORDS.

If the LSB in RDY/ $\overline{BSY}$  data byte out is '1', a programming operation is still pending. Wait until this bit returns '0' before the next instruction is carried out.

Within the same page, the low data byte must be loaded prior to the high data byte.

After data is loaded to the page buffer, program the EEPROM page, Please refer to the following figure.

#### Figure 32-7. Serial Programming Instruction example

#### Serial Programming Instruction

EEPROM Memory

# 33. Electrical Characteristics

# 33.1. Absolute Maximum Ratings

#### Table 33-1. Absolute Maximum Ratings

| Operating Temperature                                  | -55°C to +125°C         |

|--------------------------------------------------------|-------------------------|

| Storage Temperature                                    | -65°C to +150°C         |

| Voltage on any Pin except RESET with respect to Ground | -0.5V to $V_{CC}$ +0.5V |

| Voltage on RESET<br>with respect to Ground             | -0.5V to +13.0V         |

| Maximum Operating Voltage                              | 6.0V                    |

| DC Current per I/O Pin                                 | 40.0mA                  |

| DC Current V <sub>CC</sub> and GND Pins                | 200.0mA                 |

**Note:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 33.2. Common DC Characteristics

#### Table 33-2. Common DC characteristics T<sub>A</sub> = -40°C to 85°C, V<sub>CC</sub> = 1.8V to 5.5V (unless otherwise noted)

| Symbol           | Parameter                            | Condition                     | Min.                              | Тур. | Max.                              | Units |

|------------------|--------------------------------------|-------------------------------|-----------------------------------|------|-----------------------------------|-------|

| VIL              | Input Low Voltage, except XTAL1 and  | V <sub>CC</sub> = 1.8V - 2.4V | -0.5                              |      | 0.2V <sub>CC</sub> <sup>(1)</sup> | V     |

|                  | RESET pin                            | V <sub>CC</sub> = 2.4V - 5.5V | -0.5                              |      | 0.3V <sub>CC</sub> <sup>(1)</sup> |       |

| V <sub>IH</sub>  | Input High Voltage, except XTAL1 and | V <sub>CC</sub> = 1.8V - 2.4V | 0.7V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5             | V     |

|                  | RESET pins                           | V <sub>CC</sub> = 2.4V - 5.5V | 0.6V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5             |       |

| V <sub>IL1</sub> | Input Low Voltage,<br>XTAL1 pin      | V <sub>CC</sub> = 1.8V - 5.5V | -0.5                              |      | 0.1V <sub>CC</sub> <sup>(1)</sup> | V     |

| V <sub>IH1</sub> | Input High Voltage,                  | V <sub>CC</sub> = 1.8V - 2.4V | 0.8V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5             | V     |

|                  | XTAL1 pin                            | V <sub>CC</sub> = 2.4V - 5.5V | 0.7V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5             |       |

| V <sub>IL2</sub> | Input Low Voltage, RESET pin         | V <sub>CC</sub> = 1.8V - 5.5V | -0.5                              |      | $0.1 V_{CC}^{(1)}$                | V     |

| V <sub>IH2</sub> | Input High Voltage, RESET pin        | V <sub>CC</sub> = 1.8V - 5.5V | 0.9V <sub>CC</sub> <sup>(2)</sup> |      | V <sub>CC</sub> + 0.5             | V     |

| V <sub>IL3</sub> | Input Low Voltage,                   | V <sub>CC</sub> = 1.8V - 2.4V | -0.5                              |      | $0.2V_{CC}^{(1)}$                 | V     |

|                  | RESET pin as I/O                     | V <sub>CC</sub> = 2.4V - 5.5V | -0.5                              |      | $0.3V_{CC}^{(1)}$                 |       |

# 33.6. SPI Timing Characteristics

#### Table 33-8. SPI Timing Parameters

| Description                 | Mode   | Min.                | Тур                                                                                                  | Max  | Units |

|-----------------------------|--------|---------------------|------------------------------------------------------------------------------------------------------|------|-------|

| SCK period                  | Master | -                   | See Table. Relationship Between SCK and the Oscillator<br>Frequency in "SPCR – SPI Control Register" | -    | ns    |

| SCK high/low                | Master | -                   | 50% duty cycle                                                                                       | -    |       |

| Rise/Fall time              | Master | -                   | 3.6                                                                                                  | -    |       |

| Setup                       | Master | -                   | 10                                                                                                   | -    |       |

| Hold                        | Master | -                   | 10                                                                                                   | -    |       |

| Out to SCK                  | Master | -                   | 0.5 • t <sub>sck</sub>                                                                               | -    |       |

| SCK to out                  | Master | -                   | 10                                                                                                   | -    |       |

| SCK to out high             | Master | -                   | 10                                                                                                   | -    |       |

| SS low to out               | Slave  | -                   | 15                                                                                                   | -    |       |

| SCK period                  | Slave  | 4 • t <sub>ck</sub> | -                                                                                                    | -    |       |

| SCK high/low <sup>(1)</sup> | Slave  | 2 • t <sub>ck</sub> | -                                                                                                    | -    |       |

| Rise/Fall time              | Slave  | -                   | -                                                                                                    | 1600 |       |

| Setup                       | Slave  | 10                  | -                                                                                                    | -    |       |

| Hold                        | Slave  | t <sub>ck</sub>     | -                                                                                                    | -    |       |

| SCK to out                  | Slave  | -                   | 15                                                                                                   | -    |       |

| SCK to SS high              | Slave  | 20                  | -                                                                                                    | -    |       |

| SS high to tri-state        | Slave  |                     | 10                                                                                                   | -    |       |

| SS low to SCK               | Slave  | 2 • t <sub>ck</sub> | -                                                                                                    | -    |       |

Note: In SPI Programming mode the minimum SCK high/low period is:

- $2 \cdot t_{CLCLCL}$  for  $f_{CK} < 12MHz$

- $3 \cdot t_{CLCL}$  for  $f_{CK} > 12MHz$

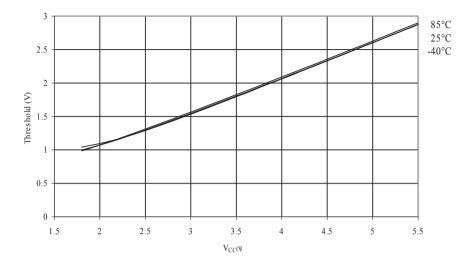

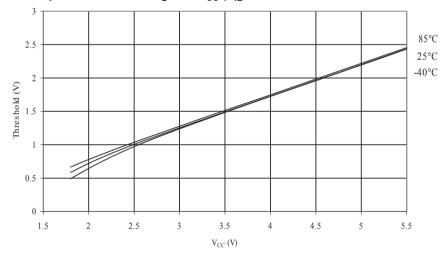

# 34.9. Pin Threshold and Hysteresis

Figure 34-28. I/O Pin Input Threshold Voltage vs.  $V_{CC}$  (V<sub>IH</sub>, I/O Pin read as '1')

Figure 34-29. I/O Pin Input Threshold Voltage vs.  $V_{CC}$  (V\_{IL}, I/O Pin read as '0'

# 38. Errata

# 38.1. Errata ATmega48/V

The revision letter in this section refers to the revision of the ATmega48/V device.

| 38.1.1. | Rev. D |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | <ul> <li>1 – Interrupts may be lost when writing the timer registers in the asynchronous timer</li> <li>The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.</li> <li>Fix/Workaround:</li> <li>Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).</li> </ul> |

| 38.1.2. | Rev. C |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |        | 1 – Reading EEPROM when system clock frequency is below 900kHz may not work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |        | Reading Data from the EEPROM at system clock frequency below 900kHz<br>may result in wrong data read.<br><b>Fix/Workaround:</b><br>Avoid using the EEPROM at clock frequency below 900kHz.                                                                                                                                                                                                                                                                                                                                                                                  |

|         |        | 2 – Interrupts may be lost when writing the timer registers in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         |        | asynchronous timer<br>The interrupt will be lost if a timer register that is synchronous timer clock is<br>written when the asynchronous Timer/Counter register (TCNTx) is 0x00.<br><b>Fix/Workaround:</b><br>Always check that the asynchronous Timer/Counter register neither have the<br>value 0xFF nor 0x00 before writing to the asynchronous Timer Control<br>Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or<br>asynchronous Output Compare Register (OCRx).                                                                                       |

| 38.1.3. | Rev. B |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |        | <ul> <li>1 – Interrupts may be lost when writing the timer registers in the asynchronous timer</li> <li>The interrupt will be lost if a timer register that is synchronous timer clock is written when the asynchronous Timer/Counter register (TCNTx) is 0x00.</li> <li>Fix/Workaround:</li> <li>Always check that the asynchronous Timer/Counter register neither have the value 0xFF nor 0x00 before writing to the asynchronous Timer Control Register (TCCRx), asynchronous Timer Counter Register (TCNTx), or asynchronous Output Compare Register (OCRx).</li> </ul> |

| 38.1.4. | Rev. A |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

1 – Part may hang in reset