#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 32-VQFN (5x5)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega88-20mu |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

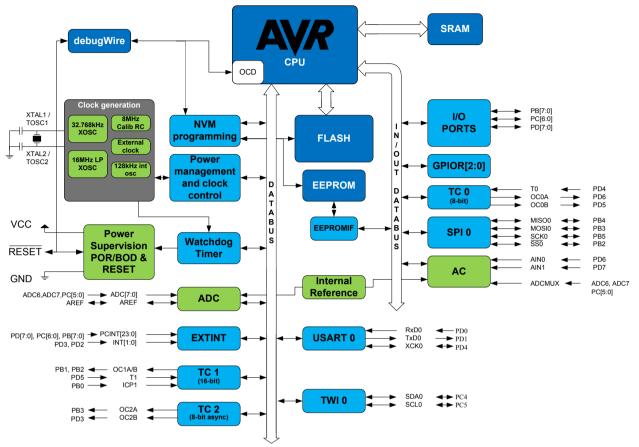

# 4. Block Diagram

Figure 4-1. Block Diagram

# 14. PM - Power Management and Sleep Modes

## 14.1. Overview

Sleep modes enable the application to shut down unused modules in the MCU, thereby saving power. The device provides various sleep modes allowing the user to tailor the power consumption to the application requirements.

## 14.2. Sleep Modes

The following Table shows the different sleep modes and their wake-up sources.

Table 14-1. Active Clock Domains and Wake-up Sources in the Different Sleep Modes.

| Sleep Mode             | eep Mode Active Clock Domains |          | Oscillators |                    | Wake-up Sources    |                                 |                             |                    |                      |                    |                     |     |     |           |

|------------------------|-------------------------------|----------|-------------|--------------------|--------------------|---------------------------------|-----------------------------|--------------------|----------------------|--------------------|---------------------|-----|-----|-----------|

|                        | clkCPU                        | CIKFLASH | clkIO       | clk <sub>ADC</sub> | clkasy             | Main Clock<br>Source<br>Enabled | Timer Oscillator<br>Enabled | INT and PCINT      | TWI Address<br>Match | Timer2             | SPM/EEPROM<br>Ready | ADC | WDT | Other I/O |

| Idle                   |                               |          | Yes         | Yes                | Yes                | Yes                             | Yes <sup>(2)</sup>          | Yes                | Yes                  | Yes                | Yes                 | Yes | Yes | Yes       |

| ADC Noise<br>Reduction |                               |          |             | Yes                | Yes                | Yes                             | Yes <sup>(2)</sup>          | Yes <sup>(3)</sup> | Yes                  | Yes <sup>(2)</sup> | Yes                 | Yes | Yes |           |

| Power-down             |                               |          |             |                    |                    |                                 |                             | Yes <sup>(3)</sup> | Yes                  |                    |                     |     | Yes |           |

| Power-save             |                               |          |             |                    | Yes                | Yes                             | Yes <sup>(2)</sup>          | Yes <sup>(3)</sup> | Yes                  | Yes                |                     |     | Yes |           |

| Standby <sup>(1)</sup> |                               |          |             |                    |                    | Yes                             |                             | Yes <sup>(3)</sup> | Yes                  |                    |                     |     | Yes |           |

| Extended Standby       |                               |          |             |                    | Yes <sup>(2)</sup> | Yes                             | Yes <sup>(2)</sup>          | Yes <sup>(3)</sup> | Yes                  | Yes                |                     |     | Yes |           |

#### Note:

- 1. Only recommended with external crystal or resonator selected as clock source.

- 2. If Timer/Counter2 is running in asynchronous mode.

- 3. For INT1 and INT0, only level interrupt.

To enter any of the six sleep modes, the Sleep Enable bit in the Sleep Mode Control Register (SMCR.SE) must be written to '1' and a SLEEP instruction must be executed. Sleep Mode Select bits (SMCR.SM[2:0]) select which sleep mode (Idle, ADC Noise Reduction, Power-down, Power-save, Standby, or Extended Standby) will be activated by the SLEEP instruction.

**Note:** The block diagram in the section *System Clock and Clock Options* provides an overview over the different clock systems in the device, and their distribution. This figure is helpful in selecting an appropriate sleep mode.

If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU is then halted for four cycles in addition to the start-up time, executes the interrupt routine, and resumes execution from the instruction following SLEEP. The contents of the Register File and SRAM are unaltered when the device wakes up from sleep. If a reset occurs during sleep mode, the MCU wakes up and executes from the Reset Vector.

#### **Related Links**

System Clock and Clock Options on page 51

## 14.3. Idle Mode

When the SM[2:0] bits are written to '000', the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing the SPI, USART, Analog Comparator, 2-wire Serial Interface, Timer/

#### Assembly Code Example

```

Move_interrupts:

; Get MCUCR

in r16, MCUCR

mov r17, r16

; Enable change of Interrupt Vectors

ori r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ori r17, (1<<IVSEL)

out MCUCR, r17

ret

```

## C Code Example

void Move\_interrupts(void)

{

uchar temp;

/\* GET MCUCR\*/

temp = MCUCR;

/\* Enable change of Interrupt Vectors \*/

MCUCR = temp|(1<<IVCE);

/\* Move interrupts to Boot Flash section \*/

MCUCR = temp|(1<<IVSEL);

}</pre>

| Name:            | PRR  |

|------------------|------|

| Offset:          | 0x64 |

| Reset:           | 0x00 |

| <b>Property:</b> | -    |

| Bit    | 7      | 6      | 5      | 4 | 3      | 2      | 1        | 0     |

|--------|--------|--------|--------|---|--------|--------|----------|-------|

| Γ      | PRTWI0 | PRTIM2 | PRTIM0 |   | PRTIM1 | PRSPI0 | PRUSART0 | PRADC |

| Access | R/W    | R/W    | R/W    |   | R/W    | R/W    | R/W      | R/W   |

| Reset  | 0      | 0      | 0      |   | 0      | 0      | 0        | 0     |

## Bit 7 – PRTWI0: Power Reduction TWI0

Writing a logic one to this bit shuts down the TWI 0 by stopping the clock to the module. When waking up the TWI again, the TWI should be re initialized to ensure proper operation.

## Bit 6 – PRTIM2: Power Reduction Timer/Counter2

Writing a logic one to this bit shuts down the Timer/Counter2 module in synchronous mode (AS2 is 0). When the Timer/Counter2 is enabled, operation will continue like before the shutdown.

## Bit 5 – PRTIM0: Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the Timer/Counter0 is enabled, operation will continue like before the shutdown.

## Bit 3 – PRTIM1: Power Reduction Timer/Counter1

Writing a logic one to this bit shuts down the Timer/Counter1 module. When the Timer/Counter1 is enabled, operation will continue like before the shutdown.

#### Bit 2 – PRSPI0: Power Reduction Serial Peripheral Interface 0

If using debugWIRE On-chip Debug System, this bit should not be written to one. Writing a logic one to this bit shuts down the Serial Peripheral Interface by stopping the clock to the module. When waking up the SPI again, the SPI should be re initialized to ensure proper operation.

#### Bit 1 – PRUSART0: Power Reduction USART0

Writing a logic one to this bit shuts down the USART by stopping the clock to the module. When waking up the USART again, the USART should be re initialized to ensure proper operation.

## Bit 0 – PRADC: Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. The ADC must be disabled before shut down. The analog comparator cannot use the ADC input MUX when the ADC is shut down.

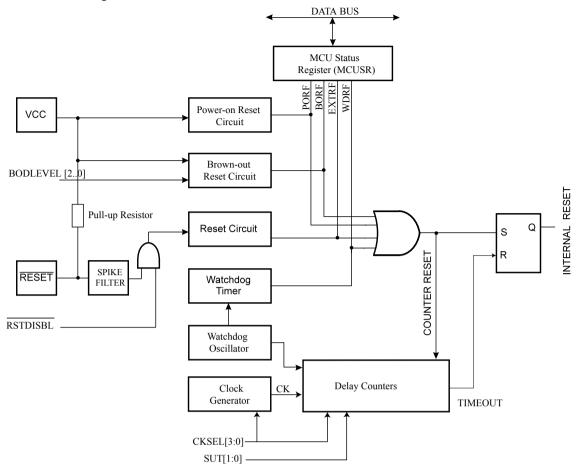

Figure 15-1. Reset Logic

## 15.3. Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in Reset after  $V_{CC}$  rise. The Reset signal is activated again, without any delay, when  $V_{CC}$  decreases below the detection level.

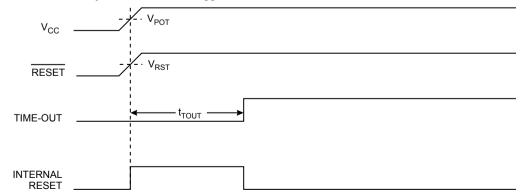

Figure 15-2. MCU Start-up, RESET Tied to V<sub>CC</sub>

| Vector No | Program Address | Source      | Interrupts definition                      |

|-----------|-----------------|-------------|--------------------------------------------|

| 24        | 0x0017          | ANALOG COMP | Analog Comparator                          |

| 25        | 0x0018          | TWI         | 2-wire Serial Interface (I <sup>2</sup> C) |

| 26        | 0x0019          | SPM READY   | Store Program Memory Ready                 |

The most typical and general program setup for the Reset and Interrupt Vector Addresses is:

| Address<br>0x0000<br>0x0001<br>0x0002<br>0x0003<br>0x0004<br>0x0005<br>0x0006<br>0x0007<br>0x0008<br>0x0009<br>0x000A<br>0x0009<br>0x000A<br>0x000B<br>0x000C<br>0x000C<br>0x000C<br>0x000C<br>0x000C<br>0x000F<br>0x0010<br>0x0011<br>0x0012<br>0x0013<br>0x0014<br>0x0015<br>0x0016<br>0x0017<br>0x0018<br>0x0019<br>; | Labels | Code<br>jmp<br>jmp<br>jmp<br>jmp<br>jmp<br>jmp<br>jmp<br>jmp<br>jmp<br>jmp | RESET<br>INTO<br>INT1<br>PCINT0<br>PCINT1<br>PCINT2<br>WDT<br>TIM2_COMPA<br>TIM2_COMPB<br>TIM2_OVF<br>TIM1_CAPT<br>TIM1_COMPB<br>TIM1_COMPB<br>TIM1_OVF<br>TIM0_COMPB<br>TIM0_OVF<br>SPI_STC<br>USART_UDRE<br>USART_UDRE<br>USART_TXC<br>ADC<br>EE_RDY<br>ANA_COMP<br>TWI<br>SPM_RDY | Comments<br>; Reset<br>; IRQ0<br>; IRQ1<br>; PCINT0<br>; PCINT1<br>; PCINT2<br>; Watchdog Timeout<br>; Timer2 CompareA<br>; Timer2 CompareA<br>; Timer1 Capture<br>; Timer1 CompareA<br>; Timer1 Overflow<br>; Timer0 CompareA<br>; Timer0 CompareA<br>; Timer0 CompareB<br>; Timer0 Overflow<br>; SPI Transfer Complete<br>; USART RX Complete<br>; USART TX Complete<br>; USART TX Complete<br>; ADC Conversion Complete<br>; EEPROM Ready<br>; Analog Comparator<br>; 2-wire Serial<br>; SPM Ready |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x001A<br>0x001B<br>0x001C<br>0x001D                                                                                                                                                                                                                                                                                     | RESET: | ldi<br>out<br>ldi<br>out                                                   | r16,high(RAMEND)<br>SPH,r16<br>r16,low(RAMEND)<br>SPL,r16                                                                                                                                                                                                                            | ; Main program start<br>; Set Stack Pointer to top of RAM                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x001E<br>0x001F                                                                                                                                                                                                                                                                                                         |        | sei                                                                        |                                                                                                                                                                                                                                                                                      | ; Enable interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0X001F                                                                                                                                                                                                                                                                                                                   |        | <instr></instr>                                                            | XXX                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                          |        |                                                                            |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# 16.2. Interrupt Vectors in ATmega88/V

Table 16-2. Reset and Interrupt Vectors in ATmega88/V

| Vector No | Program Address <sup>(2)</sup> | Source       | Interrupts definition                                                   |

|-----------|--------------------------------|--------------|-------------------------------------------------------------------------|

| 1         | 0x0000 <sup>(1)</sup>          | RESET        | External Pin, Power-on Reset, Brown-out Reset and Watchdog System Reset |

| 2         | 0x0001                         | INT0         | External Interrupt Request 0                                            |

| 3         | 0x0002                         | INT1         | External Interrupt Request 0                                            |

| 4         | 0x0003                         | PCINT0       | Pin Change Interrupt Request 0                                          |

| 5         | 0x0004                         | PCINT1       | Pin Change Interrupt Request 1                                          |

| 6         | 0x0005                         | PCINT2       | Pin Change Interrupt Request 2                                          |

| 7         | 0x0006                         | WDT          | Watchdog Time-out Interrupt                                             |

| 8         | 0x0007                         | TIMER2_COMPA | Timer/Counter2 Compare Match A                                          |

| 9         | 0x0008                         | TIMER2_COMPB | Timer/Coutner2 Compare Match B                                          |

# 18.2. Ports as General Digital I/O

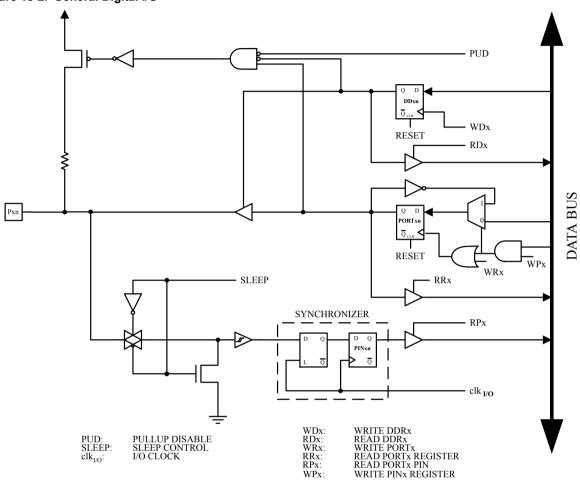

The ports are bi-directional I/O ports with optional internal pull-ups. The following figure shows the functional description of one I/O-port pin, here generically called Pxn.

Figure 18-2. General Digital I/O<sup>(1)</sup>

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port.  $clk_{I/O}$ , SLEEP, and PUD are common to all ports.

#### 18.2.1. Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in the Register Description, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written to '1', Pxn is configured as an output pin. If DDxn is written to '0', Pxn is configured as an input pin.

If PORTxn is written to '1' when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written to '0' or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

If PORTxn is written to '1' when the pin is configured as an output pin, the port pin is driven high. If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low.

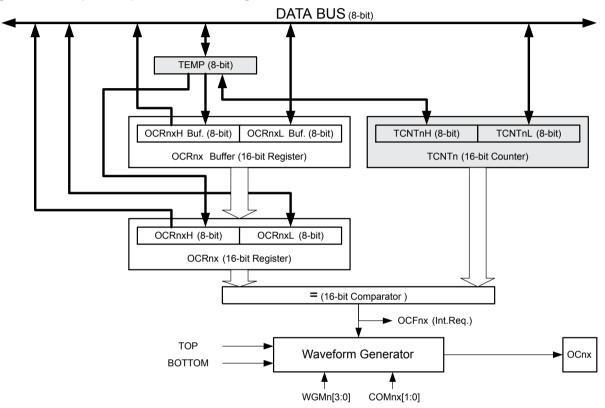

bits. The TOP and BOTTOM signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation, see Modes of Operation.

A special feature of Output Compare unit A allows it to define the Timer/Counter TOP value (i.e., counter resolution). In addition to the counter resolution, the TOP value defines the period time for waveforms generated by the Waveform Generator.

Below is a block diagram of the Output Compare unit. The elements of the block diagram that are not directly a part of the Output Compare unit are gray shaded.

**Note:** The "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B).

The OCR1x Register is double buffered when using any of the twelve Pulse Width Modulation (PWM) modes. For the Normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR1x Compare Register to either TOP or BOTTOM of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

When double buffering is enabled, the CPU has access to the OCR1x Buffer Register. When double buffering is disabled, the CPU will access the OCR1x directly.

The content of the OCR1x (Buffer or Compare) Register is only changed by a write operation (the Timer/ Counter does not update this register automatically as the TCNT1 and ICR1 Register). Therefore OCR1x is not read via the high byte temporary register (TEMP). However, it is good practice to read the low byte first as when accessing other 16-bit registers. Writing the OCR1x Registers must be done via the TEMP Register since the compare of all 16 bits is done continuously. The high byte (OCR1xH) has to be written first. When the high byte I/O location is written by the CPU, the TEMP Register will be updated by the value written. Then when the low byte (OCR1xL) is written to the lower eight bits, the high byte will be

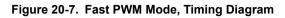

TCNT1 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal lines on the TCNT1 slopes mark compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

**Note:** The "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B).

The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches TOP. In addition, when either OCR1A or ICR1 is used for defining the TOP value, the OC1A or ICF1 Flag is set at the same timer clock cycle TOV1 is set. If one of the interrupts are enabled, the interrupt handler routine can be used for updating the TOP and compare values.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNT1 and the OCR1x. Note that when using fixed TOP values the unused bits are masked to zero when any of the OCR1x Registers are written.

The procedure for updating ICR1 differs from updating OCR1A when used for defining the TOP value. The ICR1 Register is not double buffered. This means that if ICR1 is changed to a low value when the counter is running with none or a low prescaler value, there is a risk that the new ICR1 value written is lower than the current value of TCNT1. As result, the counter will miss the compare match at the TOP value. The counter will then have to count to the MAX value (0xFFFF) and wrap around starting at 0x0000 before the compare match can occur. The OCR1A Register however, is double buffered. This feature allows the OCR1A I/O location to be written anytime. When the OCR1A I/O location is written the value written will be put into the OCR1A Buffer Register. The OCR1A Compare Register will then be updated with the value in the Buffer Register at the next timer clock cycle the TCNT1 matches TOP. The update is done at the same timer clock cycle as the TCNT1 is cleared and the TOV1 Flag is set.

Using the ICR1 Register for defining TOP works well when using fixed TOP values. By using ICR1, the OCR1A Register is free to be used for generating a PWM output on OC1A. However, if the base PWM frequency is actively changed (by changing the TOP value), using the OCR1A as TOP is clearly a better choice due to its double buffer feature.

## 20.14.8. Output Compare Register 1 A Low byte

|        | Name:    | OCR1AL |     |       |         |     |     |     |  |

|--------|----------|--------|-----|-------|---------|-----|-----|-----|--|

|        | Offset:  | 0x88   |     |       |         |     |     |     |  |

|        | Reset:   | 0x00   |     |       |         |     |     |     |  |

|        | Property | :-     |     |       |         |     |     |     |  |

|        |          |        |     |       |         |     |     |     |  |

|        |          |        |     |       |         |     |     |     |  |

| Bit    | 7        | 6      | 5   | 4     | 3       | 2   | 1   | 0   |  |

|        |          |        |     | OCR1/ | AL[7:0] |     |     |     |  |

| Access | R/W      | R/W    | R/W | R/W   | R/W     | R/W | R/W | R/W |  |

| Reset  | 0        | 0      | 0   | 0     | 0       | 0   | 0   | 0   |  |

## Bits 7:0 – OCR1AL[7:0]: Output Compare 1 A Low byte

The Output Compare Registers contain a 16-bit value that is continuously compared with the counter value (TCNT1). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC1x pin.

The Output Compare Registers are 16-bit in size. To ensure that both the high and low bytes are written simultaneously when the CPU writes to these registers, the access is performed using an 8-bit temporary High Byte Register (TEMP). This temporary register is shared by all the other 16-bit registers. Refer to Accessing 16-bit Registers for details.

| Name:    | TIMSK2 |  |

|----------|--------|--|

| Offset:  | 0x70   |  |

| Reset:   | 0x00   |  |

| Property | /: -   |  |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0    |

|--------|---|---|---|---|---|-------|-------|------|

|        |   |   |   |   |   | OCIEB | OCIEA | TOIE |

| Access |   |   |   |   |   | R/W   | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0     | 0     | 0    |

## Bit 2 – OCIEB: Timer/Counter2, Output Compare B Match Interrupt Enable

When the OCIEB bit is written to '1' and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match B interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, i.e., when the OCFB bit is set in TIFR2.

## Bit 1 – OCIEA: Timer/Counter2, Output Compare A Match Interrupt Enable

When the OCIEA bit is written to '1' and the I-bit in the Status Register is set (one), the Timer/Counter2 Compare Match A interrupt is enabled. The corresponding interrupt is executed if a compare match in Timer/Counter2 occurs, i.e., when the OCFA bit is set in TIFR2.

## Bit 0 – TOIE: Timer/Counter2, Overflow Interrupt Enable

When the TOIE bit is written to '1' and the I-bit in the Status Register is set (one), the Timer/Counter2 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter2 occurs, i.e., when the TOV bit is set in TIFR2.

| Name:     | ASSR |

|-----------|------|

| Offset:   | 0xB6 |

| Reset:    | 0x00 |

| Property: | -    |

| Bit    | 7 | 6     | 5   | 4      | 3       | 2       | 1       | 0       |

|--------|---|-------|-----|--------|---------|---------|---------|---------|

|        |   | EXCLK | AS2 | TCN2UB | OCR2AUB | OCR2BUB | TCR2AUB | TCR2BUB |

| Access |   | R     | R   | R      | R       | R       | R       | R       |

| Reset  |   | 0     | 0   | 0      | 0       | 0       | 0       | 0       |

## Bit 6 – EXCLK: Enable External Clock Input

When EXCLK is written to one, and asynchronous clock is selected, the external clock input buffer is enabled and an external clock can be input on Timer Oscillator 1 (TOSC1) pin instead of a 32kHz crystal. Writing to EXCLK should be done before asynchronous operation is selected. Note that the crystal Oscillator will only run when this bit is zero.

## Bit 5 – AS2: Asynchronous Timer/Counter2

When AS2 is written to zero, Timer/Counter2 is clocked from the I/O clock, clkI/O. When AS2 is written to one, Timer/Counter2 is clocked from a crystal Oscillator connected to the Timer Oscillator 1 (TOSC1) pin. When the value of AS2 is changed, the contents of TCNT2, OCR2A, OCR2B, TCCR2A and TCCR2B might be corrupted.

## Bit 4 – TCN2UB: Timer/Counter2 Update Busy

When Timer/Counter2 operates asynchronously and TCNT2 is written, this bit becomes set. When TCNT2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCNT2 is ready to be updated with a new value.

## Bit 3 – OCR2AUB: Enable External Clock Input

When Timer/Counter2 operates asynchronously and OCR2A is written, this bit becomes set. When OCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2A is ready to be updated with a new value.

## Bit 2 – OCR2BUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2B is written, this bit becomes set. When OCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2B is ready to be updated with a new value.

## Bit 1 – TCR2AUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2A is written, this bit becomes set. When TCCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2A is ready to be updated with a new value.

## Bit 0 – TCR2BUB: Timer/Counter Control Register2 Update Busy

When Timer/Counter2 operates asynchronously and TCCR2B is written, this bit becomes set. When TCCR2B has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCCR2B is ready to be updated with a new value.

If a write is performed to any of the five Timer/Counter2 Registers while its update busy flag is set, the updated value might get corrupted and cause an unintentional interrupt to occur.

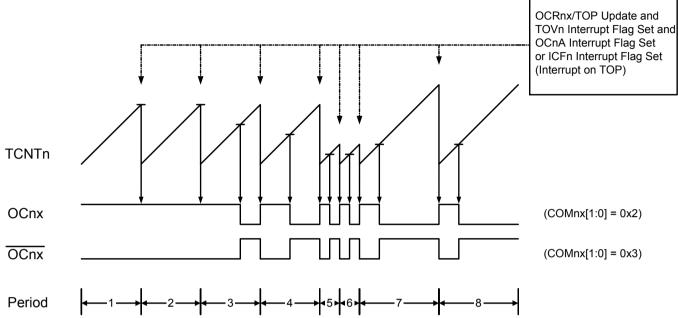

# 24.9. Asynchronous Data Reception

The USART includes a clock recovery and a data recovery unit for handling asynchronous data reception. The clock recovery logic is used for synchronizing the internally generated baud rate clock to the incoming asynchronous serial frames at the RxDn pin. The data recovery logic samples and low pass filters each incoming bit, thereby improving the noise immunity of the Receiver. The asynchronous reception operational range depends on the accuracy of the internal baud rate clock, the rate of the incoming frames, and the frame size in number of bits.

## 24.9.1. Asynchronous Clock Recovery

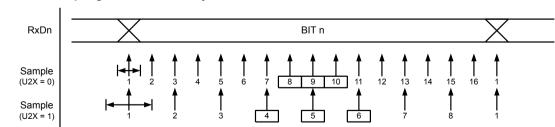

The clock recovery logic synchronizes internal clock to the incoming serial frames. The figure below illustrates the sampling process of the start bit of an incoming frame. The sample rate is 16-times the baud rate for Normal mode, and 8 times the baud rate for Double Speed mode. The horizontal arrows illustrate the synchronization variation due to the sampling process. Note the larger time variation when using the Double Speed mode (UCSRnA.U2Xn=1) of operation. Samples denoted '0' are samples taken while the RxDn line is idle (i.e., no communication activity).

## Figure 24-5. Start Bit Sampling

When the clock recovery logic detects a high (idle) to low (start) transition on the RxDn line, the start bit detection sequence is initiated. Let sample 1 denote the first zero-sample as shown in the figure. The clock recovery logic then uses samples 8, 9, and 10 for Normal mode, and samples 4, 5, and 6 for Double Speed mode (indicated with sample numbers inside boxes on the figure), to decide if a valid start bit is received. If two or more of these three samples have logical high levels (the majority wins), the start bit is rejected as a noise spike and the Receiver starts looking for the next high to low-transition on RxDn. If however, a valid start bit is detected, the clock recovery logic is synchronized and the data recovery can begin. The synchronization process is repeated for each start bit.

## 24.9.2. Asynchronous Data Recovery

When the receiver clock is synchronized to the start bit, the data recovery can begin. The data recovery unit uses a state machine that has 16 states for each bit in Normal mode and eight states for each bit in Double Speed mode. The figure below shows the sampling of the data bits and the parity bit. Each of the samples is given a number that is equal to the state of the recovery unit.

#### Figure 24-6. Sampling of Data and Parity Bit

The decision of the logic level of the received bit is taken by doing a majority voting of the logic value to the three samples in the center of the received bit: If two or all three center samples (those marked by

## 24.12.3. USART Control and Status Register 0 B

| Name:       | UCSR0B |  |  |  |  |

|-------------|--------|--|--|--|--|

| Offset:     | 0xC1   |  |  |  |  |

| Reset:      | 0x00   |  |  |  |  |

| Property: - |        |  |  |  |  |

| Bit    | 7      | 6      | 5      | 4     | 3     | 2      | 1     | 0     |

|--------|--------|--------|--------|-------|-------|--------|-------|-------|

| Γ      | RXCIE0 | TXCIE0 | UDRIE0 | RXEN0 | TXEN0 | UCSZ02 | RXB80 | TXB80 |

| Access | R/W    | R/W    | R/W    | R/W   | R/W   | R/W    | R     | R/W   |

| Reset  | 0      | 0      | 0      | 0     | 0     | 0      | 0     | 0     |

## Bit 7 – RXCIE0: RX Complete Interrupt Enable 0

Writing this bit to one enables interrupt on the RXC0 Flag. A USART Receive Complete interrupt will be generated only if the RXCIE0 bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXC0 bit in UCSR0A is set.

#### Bit 6 – TXCIE0: TX Complete Interrupt Enable 0

Writing this bit to one enables interrupt on the TXC0 Flag. A USART Transmit Complete interrupt will be generated only if the TXCIE0 bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXC0 bit in UCSR0A is set.

## Bit 5 – UDRIE0: USART Data Register Empty Interrupt Enable 0

Writing this bit to one enables interrupt on the UDRE0 Flag. A Data Register Empty interrupt will be generated only if the UDRIE0 bit is written to one, the Global Interrupt Flag in SREG is written to one and the UDRE0 bit in UCSR0A is set.

#### Bit 4 – RXEN0: Receiver Enable 0

Writing this bit to one enables the USART Receiver. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FE0, DOR0, and UPE0 Flags.

#### Bit 3 – TXEN0: Transmitter Enable 0

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxD0 pin when enabled. The disabling of the Transmitter (writing TXEN0 to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxD0 port.

#### Bit 2 – UCSZ02: Character Size 0

The UCSZ02 bits combined with the UCSZ0[1:0] bit in UCSR0C sets the number of data bits (Character Size) in a frame the Receiver and Transmitter use.

This bit is reserved in Master SPI Mode (MSPIM).

#### Bit 1 – RXB80: Receive Data Bit 8 0

RXB80 is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDR0.

This bit is reserved in Master SPI Mode (MSPIM).

## Bit 0 – TXB80: Transmit Data Bit 8 0

TXB80 is the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. Must be written before writing the low bits to UDR0.

This bit is reserved in Master SPI Mode (MSPIM).

ADCL has been read, and a second conversion completes before ADCH is read, neither register is updated and the result from the second conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

## **Related Links**

Power Management and Sleep Modes on page 65 Power Reduction Register on page 67

## 28.3. Starting a Conversion

A single conversion is started by writing a '0' to the Power Reduction ADC bit in the Power Reduction Register (PRR.PRADC), and writing a '1' to the ADC Start Conversion bit in the ADC Control and Status Register A (ADCSRA.ADSC). ADCS will stay high as long as the conversion is in progress, and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

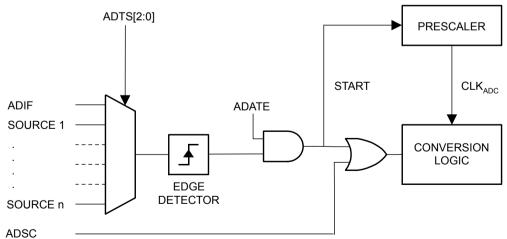

Alternatively, a conversion can be triggered automatically by various sources. Auto Triggering is enabled by setting the ADC Auto Trigger Enable bit (ADCSRA.ADATE). The trigger source is selected by setting the ADC Trigger Select bits in the ADC Control and Status Register B (ADCSRB.ADTS). See the description of the ADCSRB.ADTS for a list of available trigger sources.

When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an interrupt flag will be set even if the specific interrupt is disabled or the Global Interrupt Enable bit in the AVR Status REgister (SREG.I) is cleared. A conversion can thus be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to trigger a new conversion at the next interrupt event.

Using the ADC Interrupt Flag as a trigger source makes the ADC start a new conversion as soon as the ongoing conversion has finished. The ADC then operates in Free Running mode, constantly sampling and updating the ADC Data Register. The first conversion must be started by writing a '1' to

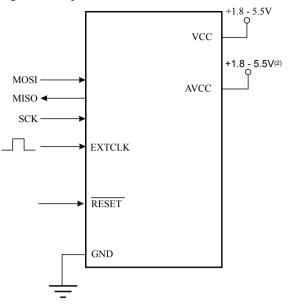

Figure 32-6. Serial Programming and Verify

#### Note:

- 1. If the device is clocked by the internal Oscillator, it is no need to connect a clock source to the XTAL1 pin.

- 2.  $V_{CC}$  0.3V < AVCC <  $V_{CC}$  + 0.3V, however, AVCC should always be within 1.8 5.5V

When programming the EEPROM, an auto-erase cycle is built into the self-timed programming operation (in the Serial mode ONLY) and there is no need to first execute the Chip Erase instruction. The Chip Erase operation turns the content of every memory location in both the Program and EEPROM arrays into 0xFF.

Depending on CKSEL Fuses, a valid clock must be present. The minimum low and high periods for the serial clock (SCK) input are defined as follows:

- Low: > 2 CPU clock cycles for  $f_{ck}$  < 12MHz, 3 CPU clock cycles for  $f_{ck} \ge$  12MHz

- High: > 2 CPU clock cycles for  $f_{ck}$  < 12MHz, 3 CPU clock cycles for  $f_{ck} \ge$  12MHz

## 32.8.1. Serial Programming Pin Mapping

Table 32-16. Pin Mapping Serial Programming

| Symbol | Pins | I/O | Description     |

|--------|------|-----|-----------------|

| MOSI   | PB3  | I   | Serial Data in  |

| MISO   | PB4  | 0   | Serial Data out |

| SCK    | PB5  | l   | Serial Clock    |

**Note:** The pin mapping for SPI programming is listed. Not all parts use the SPI pins dedicated for the internal SPI interface.

## 32.8.2. Serial Programming Algorithm

When writing serial data to the device, data is clocked on the rising edge of SCK.

When reading data from the device, data is clocked on the falling edge of SCK. Please refer to the figure, Serial Programming Waveforms in SPI Serial Programming Characteristics section for timing details.

| BRANCH INSTRUCTIONS |          |                                     |                                                      |            |         |

|---------------------|----------|-------------------------------------|------------------------------------------------------|------------|---------|

| Mnemonics           | Operands | Description                         | Operation                                            | Flags      | #Clocks |

| ICALL               |          | Indirect Call to (Z)                | PC ← Z                                               | None       | 3       |

| CALL(1)             | k        | Direct Subroutine Call              | PC ← k                                               | None       | 4       |

| RET                 |          | Subroutine Return                   | PC ← STACK                                           | None       | 4       |

| RETI                |          | Interrupt Return                    | PC ← STACK                                           | 1          | 4       |

| CPSE                | Rd,Rr    | Compare, Skip if Equal              | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3             | None       | 1/2/3   |

| CP                  | Rd,Rr    | Compare                             | Rd - Rr                                              | Z, N,V,C,H | 1       |

| CPC                 | Rd,Rr    | Compare with Carry                  | Rd - Rr - C                                          | Z, N,V,C,H | 1       |

| CPI                 | Rd,K     | Compare Register with Immediate     | Rd - K                                               | Z, N,V,C,H | 1       |

| SBRC                | Rr, b    | Skip if Bit in Register Cleared     | if (Rr(b)=0) PC $\leftarrow$ PC + 2 or 3             | None       | 1/2/3   |

| SBRS                | Rr, b    | Skip if Bit in Register is Set      | if (Rr(b)=1) PC $\leftarrow$ PC + 2 or 3             | None       | 1/2/3   |

| SBIC                | A, b     | Skip if Bit in I/O Register Cleared | if (I/O(A,b)=1) PC $\leftarrow$ PC + 2 or 3          | None       | 1/2/3   |

| SBIS                | A, b     | Skip if Bit in I/O Register is Set  | if (I/O(A,b)=1) PC $\leftarrow$ PC + 2 or 3          | None       | 1/2/3   |

| BRBS                | s, k     | Branch if Status Flag Set           | if (SREG(s) = 1) then $PC \leftarrow PC+k + 1$       | None       | 1/2     |

| BRBC                | s, k     | Branch if Status Flag Cleared       | if (SREG(s) = 0) then $PC \leftarrow PC+k + 1$       | None       | 1/2     |

| BREQ                | k        | Branch if Equal                     | if (Z = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRNE                | k        | Branch if Not Equal                 | if (Z = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRCS                | k        | Branch if Carry Set                 | if (C = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRCC                | k        | Branch if Carry Cleared             | if (C = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRSH                | k        | Branch if Same or Higher            | if (C = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRLO                | k        | Branch if Lower                     | if (C = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRMI                | k        | Branch if Minus                     | if (N = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRPL                | k        | Branch if Plus                      | if (N = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRGE                | k        | Branch if Greater or Equal, Signed  | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1 | None       | 1/2     |

| BRLT                | k        | Branch if Less Than Zero, Signed    | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1 | None       | 1/2     |

| BRHS                | k        | Branch if Half Carry Flag Set       | if (H = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRHC                | k        | Branch if Half Carry Flag Cleared   | if (H = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRTS                | k        | Branch if T Flag Set                | if (T = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRTC                | k        | Branch if T Flag Cleared            | if (T = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRVS                | k        | Branch if Overflow Flag is Set      | if (V = 1) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRVC                | k        | Branch if Overflow Flag is Cleared  | if (V = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BRIE                | k        | Branch if Interrupt Enabled         | if ( I = 1) then PC $\leftarrow$ PC + k + 1          | None       | 1/2     |

| BRID                | k        | Branch if Interrupt Disabled        | if (I = 0) then PC $\leftarrow$ PC + k + 1           | None       | 1/2     |

| BIT AND BIT-TEST INSTRUCTIONS |          |                           |              |       |         |

|-------------------------------|----------|---------------------------|--------------|-------|---------|

| Mnemonics                     | Operands | Description               | Operation    | Flags | #Clocks |

| SBI                           | P,b      | Set Bit in I/O Register   | I/O(P,b) ← 1 | None  | 2       |

| СВІ                           | P,b      | Clear Bit in I/O Register | I/O(P,b) ← 0 | None  | 2       |

Some parts may get stuck in a reset state when a reset signal is applied when the internal reset state-machine is in a specific state. The internal reset state-machine is in this state for approximately 10ns immediately before the part wakes up after a reset, and in a 10ns window when altering the system clock prescaler. The problem is most often seen during In-System Programming of the device. There are theoretical possibilities of this happening also in run-mode. The following three cases can trigger the device to get stuck in a reset-state:

- Two succeeding resets are applied where the second reset occurs in the 10ns window before the device is out of the reset-state caused by the first reset. - A reset is applied in a 10ns window while the system clock prescaler value is updated by software.

- Leaving SPI-programming mode generates an internal reset signal that can trigger this case.

The two first cases can occur during normal operating mode, while the last case occurs only during programming of the device.

#### Fix/Workaround:

The first case can be avoided during run-mode by ensuring that only one reset source is active. If an external reset push button is used, the reset start-up time should be selected such that the reset line is fully debouched during the start-up time.

The second case can be avoided by not using the system clock prescaler. The third case occurs during In-System programming only. It is most frequently seen when using the internal RC at maximum frequency. If the device gets stuck in the reset-state, turn power off, then on again to get the device out of this state.

## 2 – Wrong values read after erase only operation

At supply voltages below 2.7V, an EEPROM location that is erased by the Erase Only operation may read as programmed (0x00).

#### Problem fix/workaround

If it is necessary to read an EEPROM location after Erase Only, use an Atomic Write operation with 0xFF as data in order to erase a location. In any case, the Write Only operation can be used as intended. Thus no special considerations are needed as long as the erased location is not read before it is programmed.

#### 3 – Watchdog timer interrupt disabled

If the watchdog timer interrupt flag is not cleared before a new timeout occurs, the watchdog will be disabled, and the interrupt flag will automatically be cleared. This is only applicable in interrupt only mode. If the Watchdog is configured to reset the device in the watchdog time-out following an interrupt, the device works correctly.

#### Problem fix/workaround

Make sure there is enough time to always service the first timeout event before a new watchdog timeout occurs. This is done by selecting a long enough time-out period.

#### 4 - Start-up time with crystal oscillator is higher than expected

The clock counting part of the start-up time is about two times higher than expected for all start-up periods when running on an external Crystal. This applies only when waking up by reset. Wake-up from power down is not affected. For most settings, the clock counting parts is a small fraction of the