#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 6MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 80-BQFP                                                |

| Supplier Device Package         | 80-QFP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018006fsc |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ix

# List of Figures

| Z80180, Z8S180, Z8I | <b>.180 MPU Operation</b> 1                                                |

|---------------------|----------------------------------------------------------------------------|

| Figure 1.           | 64-Pin DIP                                                                 |

| Figure 2.           | 68-Pin PLCC                                                                |

| Figure 3.           | 80-Pin QFP                                                                 |

| Figure 4.           | Z80180/Z8S180/Z8L180 Block Diagram                                         |

| Figure 5.           | Operation Mode Control Register                                            |

| Figure 6.           | M1 Temporary Enable Timing16                                               |

| Figure 7.           | I/O Read and Write Cycles with IOC = 1<br>Timing Diagram                   |

| Figure 8.           | I/O Read and Write cycles with IOC = 0<br>Timing Diagram                   |

| Figure 9.           | Op Code Fetch (without Wait State) Timing Diagram19                        |

| Figure 10.          | Op Code Fetch (with Wait State) Timing Diagram20                           |

| Figure 11.          | Memory Read/Write (without Wait State)<br>Timing Diagram                   |

| Figure 12.          | Memory Read/Write (with Wait State)<br>Timing Diagram                      |

| Figure 13.          | I/O Read/Write Timing Diagram                                              |

| Figure 14.          | Instruction Timing Diagram                                                 |

| Figure 15.          | RESET Timing Diagram                                                       |

| Figure 16.          | Bus Exchange Timing During Memory Read                                     |

| Figure 17.          | Bus Exchange Timing During CPU Internal Operation27                        |

| Figure 18.          | WAIT Timing Diagram                                                        |

| Figure 19.          | Memory and I/O Wait State Insertion<br>(DCNTL – DMA/Wait Control Register) |

| Figure 20.          | HALT Timing Diagram                                                        |

UM005003-0703

Z8018x Family MPU User Manual

х

| Figure 21. | SLEEP Timing Diagram                              | . 35 |

|------------|---------------------------------------------------|------|

| Figure 22. | I/O Address Relocation                            | . 43 |

| Figure 23. | Logical Address Mapping Examples                  | . 55 |

| Figure 24. | Physical Address Transition                       | . 56 |

| Figure 25. | MMU Block Diagram                                 | . 56 |

| Figure 26. | I/O Address Translation                           | . 57 |

| Figure 27. | Logical Memory Organization                       | . 58 |

| Figure 28. | Logical Space Configuration                       | . 59 |

| Figure 29. | Physical Address Generation                       | . 64 |

| Figure 30. | Physical Address Generation 2                     | . 64 |

| Figure 31. | Interrupt Sources                                 | . 65 |

| Figure 32. | TRAP Timing Diagram -2nd Op Code Undefined        | . 71 |

| Figure 33. | TRAP Timing - 3rd Op Code Undefined               | . 72 |

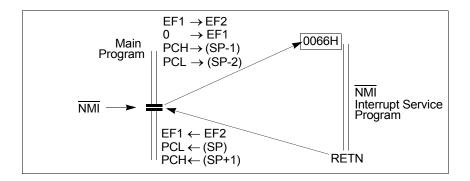

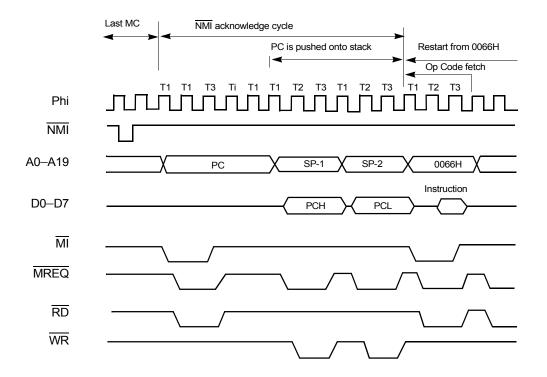

| Figure 34. | NMI Use                                           | . 74 |

| Figure 35. | NMI Timing                                        | . 75 |

| Figure 36. | INT0 Mode 0 Timing Diagram                        | . 76 |

| Figure 37. | INT0 Mode 1 Interrupt Sequence                    | . 77 |

| Figure 38. | INT0 Mode 1 Timing                                | . 78 |

| Figure 39. | INT0 Mode 2 Vector Acquisition                    | . 79 |

| Figure 40. | INT0 Interrupt Mode 2 Timing Diagram              | . 80 |

| Figure 41. | INT1, INT2 Vector Acquisition                     | . 81 |

| Figure 42. | RETI Instruction Sequence                         | . 84 |

| Figure 43. | INT1, INT2 and Internal Interrupts Timing Diagram | . 86 |

| Figure 44. | Refresh Cycle Timing Diagram                      | . 87 |

| Figure 45. | DMAC Block Diagram                                | . 93 |

| Figure 46. | DMA Timing Diagram-CYCLE STEAL Mode               | 106  |

| Figure 47. | CPU Operation and DMA Operation DREQ0             |      |

|            | is Programmed for Level-Sense                     | 107  |

| Figure 48. | CPU Operation and DMA Operation DREQ0             | 100  |

|            | is Programmed for Edge-Sense                      | 108  |

Z8018x Family MPU User Manual

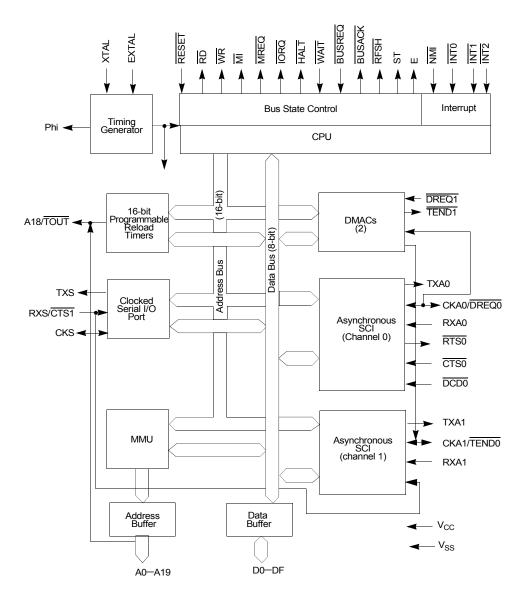

Figure 4. Z80180/Z8S180/Z8L180 Block Diagram

The external bus is IDLE while the CPU computes the effective address. Finally, the computed memory location is written with the contents of the CPU register (g).

#### **RESET Timing**

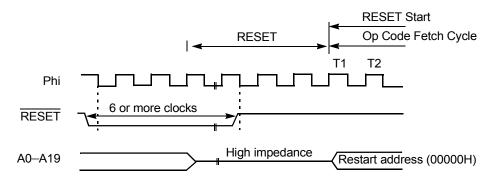

Figure 15 depicts the Z8X180 hardware RESET timing. If the  $\overline{\text{RESET}}$  pin is Low for six or more clock cycles, processing is terminated and the Z8X180 restarts execution from (logical and physical) address 00000H.

Figure 15. RESET Timing Diagram

### **BUSREQ/BUSACK Bus Exchange Timing**

The Z8X180 can coordinate the exchange of control, address and data bus ownership with another bus master. The alternate bus master can request the bus release by asserting the BUSREQ (Bus Request) input Low. After the Z8X180 releases the bus, it relinquishes control to the alternate bus master by asserting the BUSACK (Bus Acknowledge) output Low.

The bus may be released by the Z8X180 at the end of each machine cycle. In this context, a machine cycle consists of a minimum of three clock cycles (more if wait states are inserted) for Op Code fetch, memory read/ write, and I/O read/write cycles. Except for these cases, a machine cycle corresponds to one clock cycle.

• Data Bus, 3-state

SLEEP mode is exited in one of two ways as described below.

- RESET Exit from SLEEP mode. If the RESET input is held Low for at least six clock cycles, it exits SLEEP mode and begins the normal RESET sequence with execution starting at address (logical and physical) 00000H.

- Interrupt Exit from SLEEP mode. The SLEEP mode is exited by detection of an external (NMI, INT0, INT2) or internal (ASCI, CSI/O, PRT) interrupt.

In case of  $\overline{\text{NMI}}$ , SLEEP mode is exited and the CPU begins the normal  $\overline{\text{NMI}}$  interrupt response sequence.

In the case of all other interrupts, the interrupt response depends on the state of the global interrupt enable flag IEF1 and the individual interrupt source enable bit.

If the individual interrupt condition is disabled by the corresponding enable bit, occurrence of that interrupt is ignored and the CPU remains in the SLEEP mode.

Assuming the individual interrupt condition is enabled, the response to that interrupt depends on the global interrupt enable flag (IEF1). If interrupts are globally enabled (IEF1 is 1) and an individually enabled interrupt occurs, SLEEP mode is exited and the appropriate normal interrupt response sequence is executed.

If interrupts are globally disabled (IEF1 is 0) and an individually enabled interrupt occurs, SLEEP mode is exited and instruction execution begins with the instruction following the SLP instruction. This feature provides a technique for synchronization with high speed external events without incurring the latency imposed by an interrupt response sequence.

Figure 21 depicts SLEEP timing.

50

|     |                                           |          | A        | ldress |      |

|-----|-------------------------------------------|----------|----------|--------|------|

|     | Register                                  | Mnemonic | Binary   | Hex    | Page |

| DMA | DMA Source Address Register Ch 0L         | SAR0L    | XX100000 | 20H    | 93   |

|     | DMA Source Address Register Ch 0H         | SAR0H    | XX100001 | 21H    | 93   |

|     | DMA Source Address Register Ch 0B         | SAR0B    | XX100010 | 22H    | 93   |

|     | DMA Destination Address Register Ch<br>0L | DAR0L    | XX100011 | 23H    | 94   |

|     | DMA Destination Address Register Ch<br>0H | DAR0H    | XX100100 | 24H    | 94   |

|     | DMA Destination Address Register Ch<br>0B | DAR0B    | XX100101 | 25H    | 94   |

|     | DMA Byte Count Register Ch 0L             | BCR0L    | XX100110 | 26H    | 94   |

|     | DMA Byte Count Register Ch 0H             | BCR0H    | XX100111 | 27H    | 94   |

|     | DMA Memory Address Register Ch 1L         | MAR1L    | XX101000 | 28H    | 94   |

|     | DMA Memory Address Register Ch 1H         | MAR1H    | XX101001 | 29H    | 94   |

|     | DMA Memory Address Register Ch 1B         | MAR1B    | XX101010 | 2AH    | 94   |

|     | DMA I/O Address Register Ch 1L            | IAR1L    | XX101011 | 2BH    | 102  |

|     | DMA I/O Address Register Ch 1H            | IAR1H    | XX101100 | 2CH    | 102  |

|     | DMA I/O Address Register Ch 1             | IAR1B    | XX101101 | 2DH    | 94   |

|     | DMA Byte Count Register Ch 1L             | BCR1L    | XX101110 | 2EH    | 94   |

|     | DMA Byte Count Register Ch 1H             | BCR1H    | XX101111 | 2FH    | 94   |

|     | DMA Status Register                       | DSTAT    | XX110000 | 30H    | 95   |

|     | DMA Mode Register                         | DMODE    | XX110001 | 31H    | 97   |

|     | DMA/WAIT Control Register                 | DCNTL    | XX110010 | 32H    | 101  |

### Table 7. I/O Address Map (Z8S180/Z8L180-Class Processors Only) (Continued)

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|-----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | DME       | R   |       | DMA Main Enable — A DMA operation is only enabled<br>when its DE bit DE0 for channel 0, DE1 for channel 1)<br>and the DME bit are set to 1.<br>When NMI occurs, DME is reset to 0, thus disabling<br>DMA activity during the NMI interrupt service<br>routine. To restart DMA, DE0 and/or DE1 must be<br>written with 1 (even if the contents are already 1).<br>This action automatically sets DME to 1, allowing<br>DMA operations to continue. DME cannot be<br>directly written. It is cleared to 0 by NMI or<br>indirectly set to 1 by setting DE0 and/or DE1 to<br>1.DME is cleared to 0 during RESET. |

### **DMA Mode Register (DMODE)**

DMODE is used to set the addressing and transfer mode for channel 0. DMA Mode Register (DMODE: 31H)

| Bit                                                             | 7      | 6 | 5   | 4   | 3   | 2   | 1    | 0 |

|-----------------------------------------------------------------|--------|---|-----|-----|-----|-----|------|---|

| Bit/Field                                                       | ?      |   | DM1 | DM0 | SM1 | SM0 | MMOD | ? |

| R/W                                                             | ?      |   | R/W | R/W | R/W | R/W | R/W  | ? |

| Reset                                                           | eset ? |   | 0   | 0   | 0   | 0   | 0    | ? |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |        |   |     |     |     |     |      |   |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                   |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-4             | DM1:0     | R/W |       | <b>Destination Mode Channel 0</b> — Specifies whether the destination for channel 0 transfers is memory, I/O or memory mapped I/O and the corresponding address modifier. Reference Table 12. |

DREQ0 for ASCI transmission and reception respectively. To initiate memory to/from ASCI DMA transfer, perform the following operations:

- 1. Load the source and destination addresses into SAR0 and DAR0 Specify the I/O (ASCI) address as follows:

- a. Bits A0–A7 must contain the address of the ASCI channel transmitter or receiver (I/O addresses 6H-9H).

- b. Bits A8–A15 must equal 0.

- c. Bits SAR17–SAR16 must be set according to Table 16 to enable use of the appropriate ASCI status bit as an internal DMA request.

Table 16.DMA Transfer Request

| SAR18                | SAR17 | SAR16 | DMA Transfer Request  |  |  |

|----------------------|-------|-------|-----------------------|--|--|

| Х                    | 0     | 0     | DREQ0                 |  |  |

| Х                    | 0     | 1     | RDRF (ASCI channel 0) |  |  |

| Х                    | 1     | 0     | RDRF (ASCI channel 1) |  |  |

| Х                    | 1     | 1     | Reserved              |  |  |

| Note: X = Don't care |       |       |                       |  |  |

| DAR18                | DAR17 | DAR16 | DMA Transfer Request  |  |  |  |

|----------------------|-------|-------|-----------------------|--|--|--|

| X                    | 0     | 0     | DREQ0                 |  |  |  |

| Х                    | 0     | 1     | TDRE (ASCI channel O) |  |  |  |

| Х                    | 1     | 0     | TDRE (ASCI channel 1) |  |  |  |

| Х                    | 1     | 1     | Reserved              |  |  |  |

| Note: X = Don't care |       |       |                       |  |  |  |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5               | PE        | R   |       | <b>Parity Error</b> — PE is set to 1 when a parity error is detected on an incoming data byte and ASCI parity detection is enabled (the MOD1 bit of CNTLA is set to 1). PE is cleared to 0 when the EFR bit (Error Flag Reset) of CNTLA is written to 0, when DCD0 is High, in IOSTOP mode, and during RESET.                                                                                                                    |

| 4               | FE        | R   |       | <b>Framing Error</b> — If a receive data byte frame is delimited by an invalid stop bit (that is, 0, should be 1), FE is set to 1. FE is cleared to 0 when the EFR bit (Error Flag Reset) of CNTLA is written to 0, when DCD0 is High, in IOSTOP mode, and during RESET.                                                                                                                                                         |

| 3               | RIE       | R/W |       | <b>Receive Interrupt Enable</b> — RIE must be set to 1 to<br>enable ASCI receive interrupt requests. When RIE is 1, if<br>any of the flags RDRF, OVRN, PE, or FE become set to<br>1, an interrupt request is generated. For channel 0, an<br>interrupt is also generated by the transition of the external<br>DCD0 input from Low to High.                                                                                       |

| 2               | DCD0      | R   |       | <b>Data Carrier Detect</b> — Channel 0 has an external<br>$\overline{DCD0}$ input pin. The $\overline{DCD0}$ bit is set to 1 when the<br>$\overline{DCD0}$ input is HIGH. It is cleared to 0 on the first read of<br>(STAT0, following the $\overline{DCD0}$ input transition from<br>HIGH to LOW and during RESET. When $\overline{DCD0}$ is 1,<br>receiver unit is reset and receiver operation is inhibited.                  |

| 1               | TDRE      | R   |       | <b>Transmit Data Register Empty</b> — TDRE = 1 indicates<br>that the TDR is empty and the next transmit data byte is<br>written to TDR. After the byte is written to TDR, TDRE<br>is cleared to 0 until the ASCI transfers the byte from TDR<br>to the TSR and then TDRE is again set to 1. TDRE is set<br>to 1 in IOSTOP mode and during RESET. When the<br>external $\overline{\text{CTS}}$ input is High, TDRE is reset to 0. |

pins are initialized as ASCI data clock inputs. If SS2, SS1 and SS0 are reprogrammed (any other value than SS2, SS1, SS0 = 1) these pins become ASCI data clock inputs. However, if DMAC channel 0 is configured to perform memory to/from I/O (and memory mapped I/O) transfers the CKA0/ $\overline{\text{DREQ0}}$  pin reverts to DMA control signals regardless of SS2, SS1, SS0 programming.

Also, if the CKA1D bit in the CNTLA register is 1, then the CKA1/ TEND0 reverts to the DMA Control output function regardless of SS2, SS1 and SS0 programming. Final data clock rates are based on  $\overline{\text{CTS}}/\text{PS}$ (prescale), DR, SS2, SS1, SS0 and the Z8X180 system clock frequency (Reference Table 19).

| SS2 | SS1 | SS0 | Divide Ratio   |

|-----|-----|-----|----------------|

| 0   | 0   | 0   | ÷ 1            |

| 0   | 0   | 1   | ÷ 2            |

| 0   | 1   | 0   | ÷ 4            |

| 0   | 1   | 1   | ÷ 8            |

| 1   | 0   | 0   | ÷ 16           |

| 1   | 0   | 1   | ÷ 32           |

| 1   | 1   | 0   | ÷ 64           |

| 1   | 1   | 1   | external clock |

Each ASCI channel control register B configures multiprocessor mode, parity and baud rate selection.

186

### **Z80180 DC CHARACTERISTICS**

$V_{CC}$  = 5V ± 10%,  $V_{SS}$  = OV, Ta = 0° to +70°C, unless otherwise noted.)

Table 28. Z80180 DC Characteristics

| Symbol          | Item                                                      | Condition                                | Minimum                     | Typical        | Maximum                                | Unit           |

|-----------------|-----------------------------------------------------------|------------------------------------------|-----------------------------|----------------|----------------------------------------|----------------|

| VIH1            | Input High Voltage<br>RESET, EXTAL NMI                    |                                          | V <sub>CC</sub> –0.6        | _              | V <sub>CC</sub> +0.3                   | V              |

| VIH2            | Input High Voltage<br>except RESET, EXTAL<br>NMI          |                                          | 2.0                         |                | V <sub>CC</sub> +0.3                   | V              |

| VIL1            | Input Low Voltage<br>RESET, EXTAL NMI                     |                                          | -0.3                        |                | 0.6                                    | V              |

| VIL2            | Input Low Voltage<br>except RESET, EXTAL<br>NMI           |                                          | -0.3                        |                | 0.8<br>Standard<br>7 TL <sub>VIL</sub> | V              |

| VOH             | Output High Voltage<br>all outputs                        | $IOH = -200 \ \mu A$ $IOH = -20 \ \mu A$ | 2.4<br>V <sub>CC</sub> -1.2 | _              | _                                      | V<br>V         |

| VOL             | Output Low Voltage all outputs                            | IOL = 2.2  mA                            | _                           | _              | 0.45                                   | V              |

| I <sub>IL</sub> | Input Leakage Current<br>all inputs except XTAL,<br>EXTAL | $V_{IN} = 0.5 \sim V_{CC} - 0.5$         | -                           | _              | 1.0                                    | μΑ             |

| ITL             | Three-State Leakage<br>Current                            |                                          | _                           | _              | 1.0                                    | μA             |

| ICC             | Power Dissipation*<br>(Normal Operation)                  | f = 6 MHz<br>f = 8 MHz<br>f = 33 MHz     | _<br>_<br>_                 | 15<br>20<br>25 | 40<br>50<br>60                         | mA<br>mA<br>mA |

|                   |           |             |       |     |     |        |      |     |     |       |               |                                               |   |   | F | lags |   |   |

|-------------------|-----------|-------------|-------|-----|-----|--------|------|-----|-----|-------|---------------|-----------------------------------------------|---|---|---|------|---|---|

|                   |           |             |       |     | Add | Iressi | ng   |     |     |       |               |                                               | 7 | 6 | 4 | 2    | 1 | 0 |

| Operation<br>Name | Mnemonics | Op Code     | Immed | Ext | Ind | Reg    | Regl | Imp | Rel | Bytes | States        | Operation                                     | s | z | н | P/V  | N | с |

| Jump              | JR Zj     | 00 101 000  |       |     |     |        |      |     | D   | 2     | 6             | continue : Z = 0                              | • | • | • | •    | • | • |

|                   |           | <j-2></j-2> |       |     |     |        |      |     |     | 2     | 8             | PC <sub>R</sub> , + j→PC <sub>R</sub> : Z = 1 |   |   |   |      |   |   |

|                   | JR NZj    | 00 100 000  |       |     |     |        |      |     | D   | 2     | 6             | continue : Z = 1                              |   |   |   |      |   |   |

|                   |           | <j-2></j-2> |       |     |     |        |      |     |     | 2     | 8             | $PC_R + j \rightarrow PC_R : Z = 0$           |   |   |   |      |   |   |

| Return            | RET       | 11001001    |       |     |     |        |      | D   |     | 1     | 9             | (SP) <sub>M</sub> →PCLr                       | • | • | • | •    | • | • |

|                   |           |             |       |     |     |        |      |     |     |       |               | (SP + 1) <sub>M</sub> →PCHr                   |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | SP <sub>R</sub> + 2→SP <sub>R</sub>           |   |   |   |      |   |   |

|                   | RET f     | 11f 000     |       |     |     |        |      |     | D   | 1     | 5 (f : false) | continue : f is false                         | • | • | • | •    | • | • |

|                   |           |             |       |     |     |        |      |     |     | 1     | 10 (f : true) | RET : f is true                               |   |   |   |      |   |   |

|                   | RETI      | 11101101    |       |     |     |        |      | D   |     | 2     | 12 (R0,R1)    | (SP) <sub>M</sub> →PCLr                       | • | • | • | •    | • | • |

|                   |           | 01001101    |       |     |     |        |      |     |     |       | ZZ(z)         | (SP + 1) <sub>M</sub> →PCHr                   |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | SP <sub>R</sub> + 2→SP <sub>R</sub>           |   |   |   |      |   |   |

|                   | RETN      | 11101101    |       |     |     |        |      | D   |     | 2     | 12            | (SP) <sub>M</sub> →PCLr                       | • | • | • | •    | • | • |

|                   |           | 01000101    |       |     |     |        |      |     |     |       |               | (SP + 1) <sub>M</sub> →PCHr                   |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | SP <sub>R</sub> + 2→SP <sub>R</sub>           |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | IEF2→IEF1                                     |   |   |   |      |   |   |

| Restart           | RST v     | 11 v 111    |       |     |     |        |      | D   |     | 1     | 11            | PCHr→(SP-1) <sub>M</sub>                      | • | • | • | •    | • | • |

|                   |           |             |       |     |     |        |      |     |     |       |               | PCLr→(SP-2) <sub>M</sub>                      |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | 0→PCHr                                        |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | v→PCLr                                        |   |   |   |      |   |   |

|                   |           |             |       |     |     |        |      |     |     |       |               | SP <sub>R</sub> -2→SP <sub>R</sub>            |   |   |   |      |   |   |

### Table 45. Program Control Instructions (Continued)

257

| Instruction              | Machine<br>Cycle | States | Address                 | Data            | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|--------------------------|------------------|--------|-------------------------|-----------------|----|----|------|------|-----------|------|----|

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| EX (SP),IX<br>EX (SP),IY | MC2              | T1T2T3 | 2nd Op Code<br>Address  | 2nd Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                          | MC3              | T1T2T3 | SP                      | DATA            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                          | MC4              | T1T2T3 | SP+1                    | DATA            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                          | MC5              | Ti     | *                       | Z               | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                          | MC6              | T1T2T3 | SP+1                    | IXH<br>IYH      | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                          | MC7              | T1T2T3 | SP                      | IXL<br>IYL      | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| HALT                     | —                | _      | Next Op Code<br>Address | Next Op<br>Code | 0  | 1  | 0    | 1    | 0         | 0    | 0  |

| IM0<br>IM1               | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| IM2                      | MC2              | T1T2T3 | 2nd Op Code<br>Address  | 2nd Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| INC g                    | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| DEC g                    | MC2              | Ti     | *                       | Z               | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INC (HL)<br>DEC (HL)     | MC2              | T1T2T3 | HL                      | DATA            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                          | MC3              | Ti     | *                       | Z               | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                          | MC4              | T1T2T3 | HL                      | DATA            | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

UM005003-0703

| Instruction | Machine<br>Cycle | States | Address                        | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------|------------------|--------|--------------------------------|----------------|----|----|------|------|-----------|------|----|

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| OTIM**      | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| OTDM**      | MC3              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC4              | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|             | MC5              | T1T2T3 | C to A0~A7<br>00H to<br>A8~A15 | DATA           | 1  | 0  | 1    | 0    | 1         | 1    | 1  |

|             | MC6              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| OTIMR**     | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| OTDMR**     | MC3              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| (If Br≠0)   | MC4              | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|             | MC5              | T1T2T3 | C to A0~A7<br>00H to<br>A8~A15 | DATA           | 1  | 0  | 1    | 0    | 1         | 1    | 1  |

|             | MC6~M<br>C8      | TiTiTi | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

## 281

# **Operating Modes Summary**

Т

Г

### **REQUEST ACCEPTANCES IN EACH OPERATING MODE**

Т

| Current<br>Status<br>Request                                                  | Normal<br>Operation<br>(CPU mode<br>and IOSTOP<br>Mode)        | WAIT State                                                   | Refresh<br>Cycle                                                                           | Interrupt<br>Acknowledge<br>Cycle                      | DMA Cycle                                                     | BUS<br>RELEASE<br>Mode                                                                       | SLEEP<br>Mode                                                         | SYSTEM<br>STOP<br>Mode                                                     |

|-------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|

| WAIT                                                                          | Acceptable                                                     | Acceptable                                                   | Not<br>acceptable                                                                          | Acceptable                                             | Acceptable                                                    | Not<br>acceptable                                                                            | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| Refresh Request<br>Request of Refresh<br>by the on-chip<br>Refresh Controller | Refresh cycle<br>begins at the<br>end of Machine<br>Cycle (MC) | Not<br>acceptable                                            | Not<br>acceptable                                                                          | Refresh cycle<br>begins at the<br>end MC               | Refresh cycle<br>begins at the<br>end of MC                   | Not<br>acceptable                                                                            | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| DREQ0<br>DREQ1                                                                | DMA cycle<br>begins at the<br>end of MC                        | DMA cycle<br>begins at the<br>end of MC                      | Acceptable<br>Refresh cycle<br>precedes.<br>DMA cycle<br>begins at the<br>end of one<br>MC | Acceptable<br>DMA cycle<br>begins at the<br>end of MC. | Acceptable<br>Refer to<br>"DMA<br>Controller"<br>for details. | Acceptable<br>*After BUS<br>RELEASE<br>cycle, DMA<br>cycle begins<br>at the end of<br>one MC | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| BUSREQ                                                                        | Bus is released<br>at the end of<br>MC                         | Not<br>acceptable                                            | Not<br>acceptable                                                                          | Bus is released<br>at the end of<br>MC                 | Bus is<br>released at the<br>end of MC                        | Continue<br>BUS<br>RELEASE<br>mode                                                           | Acceptable                                                            | Acceptable                                                                 |

| Interrupt INTO,<br>INT1,<br>INT2                                              | Accepted after<br>executing the<br>current<br>instruction.     | Accepted<br>after<br>executing the<br>current<br>instruction | Not<br>acceptable                                                                          | Not<br>acceptable                                      | Not<br>acceptable                                             | Not<br>acceptable                                                                            | Acceptable<br>Return from<br>SLEEP<br>mode to<br>normal<br>operation. | Acceptable<br>Return from<br>SYSTEM<br>STOP mode<br>to normal<br>operation |

Table 53.

Request Acceptances in Each Operating Mode

T

1

т

Т

#### 293

# **I/O Registers**

### **INTERNAL I/O REGISTERS**

By programming IOA7 and IOA6 as the I/O control register, internal I/O register addresses are relocatable within ranges from 0000H to 00FFH in the I/O address space.

| Register                              | Mnemoni | cs Ad | dress |                                                                           |                                                              |                                                                                        | Re                                             | mark               | S                      |            |             |                     |

|---------------------------------------|---------|-------|-------|---------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------|--------------------|------------------------|------------|-------------|---------------------|

| ASCI Control Register A<br>Channel 0: | CNTLA0  | 0     | 0     | bit                                                                       | MPE                                                          | RE                                                                                     | TE                                             | RTS0               | MPBR/<br>EFR           | MOD2       | MOD1        | MOD0                |

|                                       |         |       |       | during RESET<br>R/W                                                       | 0<br>R/W                                                     | 0<br>R/W                                                                               | 0<br>R/W                                       | l<br>R/W           | invalid<br>R/W         | 0<br>R/W   | 0<br>R/W    | 0<br>R/W            |

|                                       |         |       |       |                                                                           |                                                              |                                                                                        | Tr<br>Receive En<br>cessor Ena                 | ansmit En<br>able  | Error<br>uest to Se    | r Flåg Re  | or Bit Rec  | ODE Select<br>eive/ |

| ASCI Control Register A<br>Channel 1: | CNTLA1  | 0     | 1     | bit<br>during RESET                                                       | MPE<br>0                                                     | RE<br>0                                                                                | TE<br>0                                        | CKA1E              | MPBR<br>EFR<br>invalid | / MOD      | 2 MODI<br>0 | MOD0                |

|                                       |         |       |       | R/W                                                                       | R/W                                                          |                                                                                        | R/W                                            | ransmit Er<br>able | En<br>KAl Disa         | ror Flag I | ssor Bit R  | R/W<br>MODE Seld    |

|                                       |         |       |       | 0 0 1 5<br>0 1 0 5<br>0 1 1 5<br>1 0 0 5<br>1 0 1 5<br>1 0 1 5<br>1 1 0 5 | Start + 7 bi<br>Start + 8 bi<br>Start + 8 bi<br>Start + 8 bi | it Data + 2<br>it Data + F<br>it Data + F<br>it Data + 1<br>it Data + 2<br>it Data + F | 2 Stop<br>Parity + 1 S<br>Parity + 2 S<br>Stop | Stop               |                        |            |             |                     |

#### Table 57. Internal I/O Registers

| Register                                  | Mnemoni | es Ad | ldress |              |            |          | Rer      | nark                           | s       |          |            |          |

|-------------------------------------------|---------|-------|--------|--------------|------------|----------|----------|--------------------------------|---------|----------|------------|----------|

| ASCI Transmit Data<br>Register Channel 0: | TDR0    | 0     | 6      |              |            |          |          |                                |         |          |            |          |

| ASCI Transmit Data<br>Register Channel 1: | TDR1    | 0     | 7      |              |            |          |          |                                |         |          |            |          |

| ASCI Receive Data<br>Register Channel 0:  | TSR0    | 0     | 8      |              |            |          |          |                                |         |          |            |          |

| ASCI Receive Data<br>Register Channel 1:  | TSR1    | 0     | 9      |              |            |          |          |                                |         |          |            |          |

| CSI/O Control Register:                   | CNTR    | 0     | А      | bit          | EF         | EIE      | RE       | TE                             | _       | SS2      | SS1        | SS0      |

|                                           |         |       |        | during RESET | 0          | 0        | 0        | 0                              | 1       | 1        | 1          | 1        |

|                                           |         |       |        | R/W          | R          | R/W      | R/W      | R/W                            |         | R/W      | R/W        | R/W      |

|                                           |         |       |        |              |            | End Flag |          | Ti<br>Receive Er<br>upt Enable |         | Enable   | Ľs         | peed Sel |

|                                           |         |       |        | SS           | 210        | Baud R   | ate      | SS2                            | 1 0     | Baud R   | ate        |          |

|                                           |         |       |        |              | 000        | Phi ÷    | 20       |                                | 0 0     |          | 320        |          |

|                                           |         |       |        |              | 001<br>010 | ÷        | 40<br>80 |                                | 0 1 1 0 |          | 640<br>280 |          |

|                                           |         |       |        |              | 011        | ÷        | 160      |                                | 11      | External |            | 20)      |

frequency < ÷ 20)

| Table 57. | Internal I/O Registers | (Continued) |

|-----------|------------------------|-------------|

|-----------|------------------------|-------------|

300

| Register                                                    | Mnemonics   | Addre      | <b>SS</b>                  |              |                     | Re                                  | marl                       | KS                         |         |           |                   |

|-------------------------------------------------------------|-------------|------------|----------------------------|--------------|---------------------|-------------------------------------|----------------------------|----------------------------|---------|-----------|-------------------|

| MMU Common Base                                             | CBR         | 3 8        |                            |              |                     |                                     |                            |                            | 1       | 1         | 1                 |

| Register:                                                   |             |            | bit                        | CB7          | CB6                 | CB5                                 | CB4                        | CB3                        | CB2     | CB1       | CB0               |

|                                                             |             |            | during RESET               | 0            | 0                   | 0                                   | 0                          | 0                          | 0       | 0         | 0                 |

|                                                             |             |            | R/W                        | R/W          | R/W                 | R/W                                 | R/W                        | R/W                        | R/W     | R/W       | R/W               |

|                                                             |             |            |                            |              |                     |                                     |                            | Y                          | MMU Co  | mmon Ba   | ise Regi          |

| MMU Bank Base Register                                      | BBR         | 3 9        |                            | BB7          | BB6                 | BB5                                 | BB4                        | BB3                        | BB2     | BB1       | BB0               |

|                                                             |             |            | bit<br>during RESET        | 0            | 0                   | 0                                   | 0                          | 0                          | 0       | 0         | 0                 |

|                                                             |             |            | R/W                        | R/W          | R/W                 | R/W                                 | R/W                        | R/W                        | R/W     | R/W       | R/W               |

|                                                             |             |            |                            |              |                     |                                     |                            | $\sim$                     |         | I         |                   |

|                                                             |             | 2          |                            |              |                     |                                     |                            |                            | MMU Bai | nk Base R | legister          |

| MMU Common/Bank<br>Register                                 | CBAR        | 3 A        | bit                        | CA3          | CA2                 | CA1                                 | CA0                        | BA3                        | BA2     | BA1       | BA0               |

|                                                             |             |            | during RESET               | 1            | 1                   | 1                                   | 1                          | 0                          | 0       | 0         | 0                 |

|                                                             |             |            | R/W                        | R/W          | R/W                 | R/W                                 | R/W                        | R/W                        | R/W     | R/W       | R/W               |

|                                                             |             |            |                            |              |                     |                                     | I Commo                    | n Area Re                  | gister  |           | U Bank<br>Registe |

|                                                             |             |            |                            |              |                     | MMU                                 | Commo                      |                            |         |           |                   |

|                                                             | OMCR        | 3 E        | bit                        | MIE          | MITE                |                                     | _                          |                            |         | _         | _                 |

|                                                             | OMCR        | 3 E        | bit<br>during RESET        | MIE          | MITE<br>1           |                                     | 1                          |                            | 1       | <br>1     | -<br>1            |

|                                                             | OMCR        | 3 E        |                            |              |                     | ĪOC                                 | _                          | _                          | _       |           |                   |

|                                                             | OMCR        | 3 E        | during RESET               | 1            | 1<br>W              | IOC<br>1<br>R/W                     | l<br>I/O Comp              | l                          | _       |           |                   |

|                                                             | OMCR        | 3 E        | during RESET               | l<br>R/W     | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l                          | _       |           |                   |

| Register                                                    |             |            | during RESET               | l<br>R/W     | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l                          | _       |           |                   |

| Register                                                    | OMCR<br>ICR | 3 E<br>3 F | during RESET<br>R/W        | l<br>R/W     | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l                          | _       |           |                   |

| Register                                                    |             |            | during RESET<br>R/W<br>bit | l<br>R/W     | 1<br>W<br>MI Enable | I<br>I<br>R/W<br>MI Temp            | 1<br>I/O Comp<br>orary Ena | l<br>patibility<br>ble     | 1       | 1         | 1                 |

| Operation Mode Control<br>Register<br>I/O Control Register: |             |            | during RESET<br>R/W        | 1<br>R/W<br> | 1<br>W<br>MI Enable | IOC<br>1<br>R/W<br>MT Temp<br>IOSTP | I/O Comp<br>orary Ena      | l<br>patibility<br>ble<br> |         | 1         | -                 |

### Table 57. Internal I/O Registers (Continued)

I/O Address