#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                 |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 6MHz                                                   |

| Co-Processors/DSP               |                                                        |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 80-BQFP                                                |

| Supplier Device Package         | 80-QFP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018006fsg |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 49.  | TEND0 Output Timing Diagram108                                                     |

|-------------|------------------------------------------------------------------------------------|

| Figure 50.  | DMA Interrupt Request Generation114                                                |

| Figure 51.  | NMI and DMA Operation Timing Diagram115                                            |

| Figure 52.  | ASCI Block Diagram117                                                              |

| Figure 53.  | DCD0 Timing Diagram139                                                             |

| Figure 54.  | RTS0 Timing Diagram140                                                             |

| Figure 55.  | ASCI Interrupt Request Circuit Diagram140                                          |

| Figure 56.  | ASCI Clock                                                                         |

| Figure 57.  | CSI/O Block Diagram147                                                             |

| Figure 58.  | CSI/O Interrupt Request Generation151                                              |

| Figure 59.  | Transmit Timing Diagram–Internal Clock153                                          |

| Figure 60.  | Transmit Timing–External Clock154                                                  |

| Figure 61.  | CSI/O Receive Timing–Internal Clock155                                             |

| Figure 62.  | CSI/O Receive Timing–External Clock156                                             |

| Figure 63.  | PRT Block Diagram157                                                               |

| Figure 64.  | Timer Initialization, Count Down, and Reload                                       |

|             | Timing Diagram163                                                                  |

| Figure 65.  | Timer Output Timing Diagram164                                                     |

| Figure 66.  | PRT Interrupt Request Generation164                                                |

| Figure 67.  | E Clock Timing Diagram (During Read/Write Cycle<br>and Interrupt Acknowledge Cycle |

| Figure 68.  | E Clock Timing in BUS RELEASE Mode                                                 |

| Figure 69.  | E Clock Timing in SLEEP Mode and                                                   |

| i iguie oy. | SYSTEM STOP Mode                                                                   |

| Figure 70.  | External Clock Interface                                                           |

| Figure 71.  | Clock Generator Circuit                                                            |

| Figure 72.  | Circuit Board Design Rules                                                         |

| Figure 73.  | Example of Board Design                                                            |

xvi

| Table 43.                 | Block Transfer                                            |

|---------------------------|-----------------------------------------------------------|

| Table 44.                 | Stock and Exchange                                        |

| Table 45.                 | Program Control Instructions                              |

| Table 46.                 | I/O Instructions                                          |

| Table 47.                 | Special Control Instructions                              |

| Op Code Map               |                                                           |

| Table 48.                 | 1st Op Code Map Instruction Format: XX                    |

| Table 49.                 | 2nd Op Code Map Instruction Format: CB XX 249             |

| Table 50.                 | 2nd Op Code Map Instruction Format: ED XX 250             |

| Bus Control Signal        | Conditions                                                |

| Table 51.                 | Bus and Control Signal Condition in Each<br>Machine Cycle |

| Table 52.                 | Interrupts                                                |

| <b>Operating Modes St</b> | ummary                                                    |

| Table 53.                 | Request Acceptances in Each Operating Mode                |

| Table 54.                 | The Z80180 Types of Requests 282                          |

| Status Signals 287        |                                                           |

| Table 55.                 | Pin Outputs in Each Operating Mode                        |

| Table 56.                 | Pin Status During RESET and<br>LOW POWER OPERATION Modes  |

| I/O Registers             |                                                           |

| Table 57.                 | Internal I/O Registers                                    |

Z8018x Family MPU User Manual

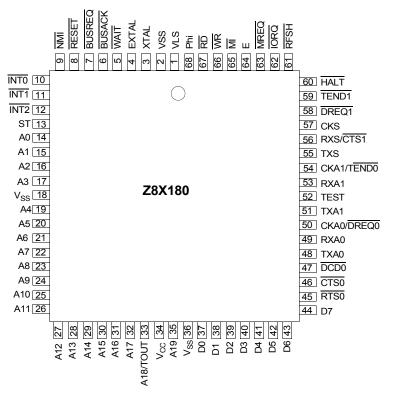

### **PIN DESCRIPTION**

**A0–A19.** Address Bus (Output, Active High, 3-state). A0–A19 form a 20bit address bus. The Address Bus provides the address for memory data bus exchanges, up to 1 MB, and I/O data bus exchanges, up to 64K. The address bus enters a high impedance state during RESET and external bus acknowledge cycles. Address line A18 is multiplexed with the output of PRT channel 1 (TOUT, selected as address output on RESET) and address line A19 is not available in DIP versions of the Z8X180.

**BUSACK.** *Bus Acknowledge (Output, Active Low).* **BUSACK** indicates that the requesting device, the MPU address and data bus, and some control signals, have entered their high impedance state.

**BUSREQ.** Bus Request (Input, Active Low). This input is used by external devices (such as DMA controllers) to request access to the system bus. This request has a higher priority than NMI and is always recognized at the end of the current machine cycle. This signal stops the CPU from executing further instructions and places the address and data buses, and other control signals, into the high impedance state.

**CKA0, CKA1.** *Asynchronous Clock 0 and 1 (Bidirectional, Active High).* These pins are the transmit and receive clocks for the ASCI channels. CKA0, is multiplexed with DREQ0 and CKA1 is multiplexed with TEND0.

**CKS.** *Serial Clock (Bidirectional, Active High).* This line is the clock for the CSIO channel.

**CLOCK (PHI).** *System Clock (Output, Active High).* The output is used as a reference clock for the MPU and the external system. The frequency of this output is equal to one-half that of the crystal or input clock frequency.

**CTS0**, **CTS1**. *Clear to Send 0 and 1 (Inputs, Active Low)*. These lines are modem control signals for the ASCI channels. **CTS1** is multiplexed with RXS.

36

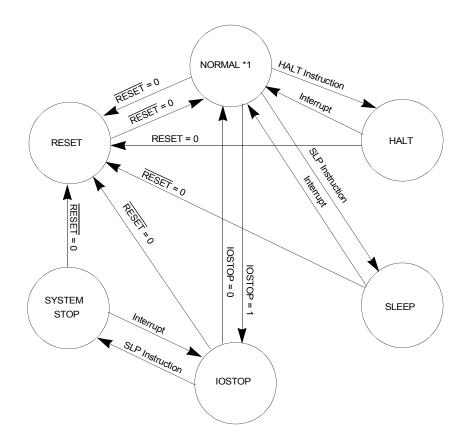

## Low Power Modes (Z8S180/Z8L180 only)

The following section is a detailed description of the enhancements to the Z8S180/L180 from the standard Z80180 in the areas of STANDBY, IDLE and STANDBY QUICK RECOVERY modes.

## **Add-On Features**

There are five different power-down modes. SLEEP and SYSTEM STOP are inherited from the Z80180. In SLEEP mode, the CPU is in a stopped state while the on-chip I/Os are still operating. In I/O STOP mode, the on-chip I/Os are in a stopped state while leaving the CPU running. In SYSTEM STOP mode, both the CPU and the on-chip I/Os are in the stopped state to reduce current consumption. The Z8S180 features two additional power-down modes, STANDBY and IDLE, to reduce current consumption even further. The differences in these power-down modes are summarized in Table 5.

85

Z8X180. Figure 43 illustrates the INT1, INT2 and internal interrupts timing.

| Machine |        |                |         |    |    |      | Γ    | MI    |       |      |    |

|---------|--------|----------------|---------|----|----|------|------|-------|-------|------|----|

| Cycle   | States | Address        | Data    | RD | WR | MREQ | IORQ | M1E=1 | M1E=0 | HALT | ST |

| 1       | T1-T3  | 1st<br>Op Code | EDH     | 0  | 1  | 0    | 1    | 0     | 1     | 1    | 0  |

| 2       | TI-T3  | 2nd<br>Op Code | 4DH     | 0  | 1  | 0    | 1    | 0     | 1     | 1    | 1  |

| 3       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 4       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 5       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 6       | T1-T3  | 1st<br>Op Code | EDH     | 0  | 1  | 0    | 1    | 0     | 0     | 1    | 1  |

| 7       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 8       | T1-T3  | 2nd<br>Op Code | 4DH     | 0  | 1  | 0    | 1    | 0     | 1     | 1    | 1  |

| 9       | T1-T3  | SP             | data    | 0  | 1  | 0    | 1    | 1     | 1     | 1    | 1  |

| 10      | T1-T3  | SP+1           | data    | 0  | 1  | 0    | 1    | 1     | 1     | 1    | 1  |

Table 10.

RETI Control Signal States

IOC affects the IORQ/RD signals. M1E affects the assertion of M1. One state also reflects a 1 while the other reflects a 0  $\,$

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                            |

|-----------------|-----------|-----|-------|--------------------------------------------------------------------------------------------------------|

| 2–0             | MOD2-0    | R/W |       | <b>ASCI Data Format Mode 2, 1, 0</b> — These bits program the ASCI data format as follows.             |

|                 |           |     |       | MOD2                                                                                                   |

|                 |           |     |       | 0: 7 bit data                                                                                          |

|                 |           |     |       | 1: 8 bit data                                                                                          |

|                 |           |     |       | MOD1                                                                                                   |

|                 |           |     |       | 0: No parity                                                                                           |

|                 |           |     |       | 1: Parity enabled                                                                                      |

|                 |           |     |       | MOD0                                                                                                   |

|                 |           |     |       | 0: 1 stop bit                                                                                          |

|                 |           |     |       | 1: 2 stop bits                                                                                         |

|                 |           |     |       | The data formats available based on all combinations of MOD2, MOD1 and MOD0 are described in Table 17. |

### ASCI to/from DMAC Operation

Operation of the ASCI with the on-chip DMAC channel 0 requires that the DMAC be correctly configured to use the ASCI flags as DMA request signals.

### **ASCI and RESET**

During RESET, the ASCI status and control registers are initialized as defined in the individual register descriptions.

Receive and Transmit operations are stopped during RESET. However, the contents of the transmit and receive data registers (TDR and RDR) are not changed by RESET.

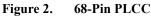

#### **ASCI Clock**

When in external clock input mode, the external clock is directly input to the sampling rate  $(\div 16/\div 64)$  as depicted in Figure 56.

Figure 56. ASCI Clock

| Pro | escaler         |    | npling<br>ate | g<br>Baud Rate     |            |             | e               | General         | Baud             | Rate (Exa<br>(BPS) | mple)            |     | СКА                |

|-----|-----------------|----|---------------|--------------------|------------|-------------|-----------------|-----------------|------------------|--------------------|------------------|-----|--------------------|

| PS  | Divide<br>Ratio | DR | Rate          | SS2                | <b>SS1</b> | <b>SS</b> 0 | Divide<br>Ratio | Divide<br>Ratio | φ = 6.144<br>MHz | φ = 4.608<br>MHz   | φ = 3.072<br>MHz | I/O | Clock<br>Frequency |

|     |                 |    |               | 0                  | 0          | 0           | ÷1              | φ ÷ 160         | 38400            |                    | 19200            |     | $\phi \div 10$     |

|     |                 |    |               | 0                  | 0          | 1           | 2               | 320             | 19200            |                    | 9600             |     | 20                 |

|     |                 | 0  | 16            | 0                  | 1          | 0           | 4               | 640             | 9600             |                    | 4800             |     | 40                 |

|     |                 | 0  | 10            | 0                  | 1          | 1           | 8               | 1280            | 4800             |                    | 2400             | 0   | 80                 |

|     |                 |    |               | 1                  | 0          | 0           | 16              | 2560            | 2400             |                    | 1200             |     | 160                |

|     |                 |    |               | 1                  | 0          | 1           | 32              | 5120            | 1200             |                    | 600              |     | 320                |

|     |                 |    |               | 1                  | 1          | 0           | 64              | 10240           | 600              |                    | 300              |     | 640                |

| 0   | φ ÷ 10          |    |               | 1                  | 1          | 1           | _               | fc ÷ 16         | _                | —                  | _                | Ι   | fc                 |

|     |                 |    |               | 0                  | 0          | 0           | ÷1              | 0÷640           | 9600             |                    | 4800             |     | φ ÷ 10             |

|     |                 |    |               | 0                  | 0          | 1           | 2               | 1280            | 4800             |                    | 2400             |     | 20                 |

|     |                 |    |               | 0                  | 1          | 0           | 4               | 2560            | 2400             |                    | 1200             |     | 40                 |

|     |                 | 1  | 64            | 0                  | 1          | 1           | 8               | 5120            | 1200             |                    | 600              | 0   | 80                 |

|     |                 |    |               | 1                  | 0          | 0           | 16              | 10240           | 600              |                    | 300              |     | 160                |

|     |                 |    |               | 1                  | 0          | 1           | 32              | 20480           | 300              |                    | 150              |     | 320                |

|     |                 |    |               | 1 1 0 64 40960 150 |            | 75          |                 | 640             |                  |                    |                  |     |                    |

|     |                 |    |               | 1                  | 1          | 1           | —               | fc ÷ 64         | _                | —                  | —                | Ι   | fc                 |

Table 19.

ASCI Baud Rate Selection

17

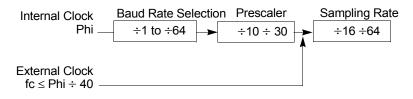

Figure 73. Example of Board Design

Circuit Board design should observe the following parameters.

- Locate the crystal and load capacitors as close to the IC as physically possible to reduce noise.

- Signal lines must not run parallel to the clock oscillator inputs. In particular, the clock input circuitry and the system clock output (pin 64) must be separated as much as possible.

- V<sub>CC</sub> power lines must be separated from the clock oscillator input circuitry.

- Resistivity between XTAL or EXTAL and the other pins must be greater than 10M ohms.

Signal line layout must avoid areas marked with the shaded area of Figure 73.

## . . . / .

# Software Architecture

## **INSTRUCTION SET**

The Z80180 is object code-compatible with the Z80 CPU. Refer to the Z80 CPU Technical Manual or the Z80 Assembly Language Programming Manual for further details.

| Table 26. | Instruction S | Set Summary |

|-----------|---------------|-------------|

|-----------|---------------|-------------|

| New Instructions | Operation                                            |

|------------------|------------------------------------------------------|

| SLP              | Enter SLEEP mode                                     |

| MLT              | 8-bit multiply with 16-bit result                    |

| INO g, (m)       | Input contents of immediate I/O address              |

| OUT0 (m), g      | Output register contents to immediate I/O address    |

| OTIM             | Block output - increment                             |

| OTIMR            | Block output - increment and repeat                  |

| OTDM             | Block output - decrement                             |

| OTDMR            | Block output - decrement and repeat                  |

| TSTIO m          | Non-destructive AND, I/O port, and accumulator       |

| TST g            | Non-destructive AND, register, and accumulator       |

| TST m            | Non-destructive AND, immediate data, and accumulator |

| TST (HL)         | Non-destructive AND, memory data, and accumulator    |

#### **SLP** - Sleep

The SLP instruction causes the Z80180 to enter the SLEEP low power consumption mode. See page 32 for a complete description of the SLEEP state.

# 207

# **Instruction Set**

This section explains the symbols in the instruction set.

### REGISTER

g, g', ww, xx, yy, and zz specify a register to be used. g and g' specify an 8-bit register. ww, xx, yy, and zz specify a pair of 8-bit registers. Table 32 describes the correspondence between symbols and registers.

Table 32.Register Values

111

А

| g,g' | Reg. | ww | Reg. | xx | Reg. | уу | Reg. | zz | Reg. |

|------|------|----|------|----|------|----|------|----|------|

| 000  | B    | 00 | BC   | 00 | BC   | 00 | BC   | 00 | BC   |

| 001  | С    | 01 | DE   | 01 | DE   | 01 | DE   | 01 | DE   |

| 010  | D    | 10 | HL   | 10 | IX   | 10 | IY   | 10 | HL   |

| 011  | Е    | 11 | SP   | 11 | SP   | 11 | SP   | 11 | AF   |

| 100  | Н    |    |      |    |      |    | •    |    |      |

| 101  | L    |    |      |    |      |    |      |    |      |

Note: Suffixed H and L to ww, xx, yy, zz (ex. wwH, IXL) indicate upper and lower 8-bit of the 16-bit register respectively.

### BIT

**b** specifies a bit to be manipulated in the bit manipulation instruction. Table 33 indicates the correspondence between **b** and bits.

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         |                                                                                                                                                                            |   |     | Fl | ags |   |   |

|-------------------|----------------------------------------------------|------------------|-------|-----|-----|-------|------|-----|-----|-------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----|-----|---|---|

|                   |                                                    |                  |       |     | Ad  | dress | ing  |     |     |       |                         |                                                                                                                                                                            | 7 | 6   | 4  | 2   | 1 | 0 |

| Operation<br>Name | Mnemonics                                          | Op Code          | Immed | Ext | Ind | Reg   | Regl | Imp | Rel | Bytes | States                  | Operation                                                                                                                                                                  | s | z   | н  | P/V | N | с |

|                   | CPI                                                | 11101101         |       |     |     |       | S    | s   |     | 2     | 12                      | Ar-(HL) <sub>M</sub>                                                                                                                                                       | ↑ | ↑   | ↑  | ↑   | s | • |

|                   |                                                    | 10100001         |       |     |     |       |      |     |     |       |                         | BC <sub>R</sub> -1→BC <sub>R</sub>                                                                                                                                         |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | HL <sub>R</sub> + 1→HL <sub>R</sub>                                                                                                                                        |   | (3) |    | (2) |   |   |

|                   | CPIR                                               | 11101101         |       |     |     |       | s    | s   |     | 2     | 14                      | BC <sub>R</sub> ≠0 Ar*(HL) <sub>M</sub>                                                                                                                                    | ↑ | ↑   | ↑  | ↑   | s | • |

|                   |                                                    | 10110001         |       |     |     |       |      |     |     |       | 12                      | $BC_R = 0 \text{ or } Ar = (HL)_M$                                                                                                                                         |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | $\begin{array}{c} & \text{Ar-(HL)}_M\\ \text{Q} & \text{BC}_{\text{R}}\text{-}1 {\rightarrow} \text{BC}_R\\ & \text{HL}_R \text{+}1 {\rightarrow} \text{HL}_R \end{array}$ |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | Repeat Q until                                                                                                                                                             |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | $Ar = (HL)_M \text{ or } BC_R = 0$                                                                                                                                         |   |     |    | (2) |   |   |

|                   | LDD                                                | 11 101 101       |       |     |     |       | S/D  |     |     | 2     | 12                      |                                                                                                                                                                            | • | •   | R  | ↑   | R | • |

|                   |                                                    | 10 101 000       |       |     |     |       |      |     |     |       |                         | BC <sub>R</sub> -1→BC <sub>R</sub>                                                                                                                                         |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | DE <sub>R</sub> -1→DE <sub>R</sub>                                                                                                                                         |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | HL <sub>R</sub> -1→HL <sub>R</sub>                                                                                                                                         |   |     |    |     |   |   |

|                   | LDDR                                               | 11 101 101       |       |     |     |       | S/D  |     |     | 2     | 14(BC <sub>R</sub> ≠ 0) | $(HL)_{M} \rightarrow (DE)_{M}$<br>BC <sub>R</sub> -1 $\rightarrow$ BC <sub>R</sub>                                                                                        | • | •   | R  | R   | R | • |

|                   |                                                    | 10 111 000       |       |     |     |       |      |     |     |       | 12(BC <sub>R</sub> = 0) | $\begin{array}{c} Q \qquad DE_{R}^{K} - 1 \rightarrow DE_{R}^{K} \\ HL_{R} - 1 \rightarrow HL_{R} \end{array}$                                                             |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | Repeat Q until                                                                                                                                                             |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | BC <sub>R</sub> = 0                                                                                                                                                        |   |     |    | (2) |   |   |

|                   | LDI                                                | 11 101 101       |       |     |     |       | S/D  |     |     | 2     | 12                      | (HL) <sub>M</sub> →DE) <sub>R</sub>                                                                                                                                        | • | •   | R  | ↑   | R | • |

|                   |                                                    | 10 100 000       |       |     |     |       |      |     |     |       |                         | BC <sub>R</sub> -1→BC <sub>R</sub>                                                                                                                                         |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | DE <sub>R</sub> + 1→DE <sub>R</sub>                                                                                                                                        |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | HL <sub>R</sub> + 1→HL <sub>R</sub>                                                                                                                                        |   |     |    |     |   |   |

|                   | LDIR                                               | 11 101 101       |       |     |     |       | S/D  |     |     | 2     | 14(BC <sub>R</sub> ≠0)  | $(HL)_{M} \rightarrow (DE)_{M}$<br>Q BC <sub>R</sub> -1 $\rightarrow$ BC <sub>R</sub>                                                                                      | • | •   | R  | R   | R | • |

|                   |                                                    | 10 110 000       |       |     |     |       |      |     |     |       | 12(BC <sub>R</sub> = 0) | $DE_{R} + 1 \rightarrow DE_{R}$ $HL_{R} + 1 \rightarrow HL_{R}$                                                                                                            |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | Repeat Q until                                                                                                                                                             |   |     |    |     |   |   |

|                   |                                                    |                  |       |     |     |       |      |     |     |       |                         | BC <sub>R</sub> = 0                                                                                                                                                        |   |     |    |     |   |   |

|                   | 0: BC <sub>R</sub> -1 = 0                          |                  |       |     |     |       |      |     |     |       |                         |                                                                                                                                                                            |   |     |    |     |   |   |

| (3) Z = 1:        | ⊃/V = 1: BC <sub>R</sub><br>Ar = (HL) <sub>M</sub> |                  |       |     |     |       |      |     |     |       |                         |                                                                                                                                                                            |   |     |    |     |   |   |

| Ž                 | Z = 0 :Ar ≠ (H                                     | IL) <sub>M</sub> |       |     |     |       |      |     |     |       |                         |                                                                                                                                                                            |   |     |    |     |   |   |

#### Table 43. Block Transfer (Continued)

|               |       | Machine |        |

|---------------|-------|---------|--------|

| MNEMONICS     | Bytes | Cycles  | States |

| RRC (IY+d)    | 4     | 7       | 19     |

| RRC g         | 2     | 3       | 7      |

| RRD           | 2     | 8       | 16     |

| RR (HL)       | 2     | 5       | 13     |

| RR (IX+d)     | 4     | 7       | 19     |

| RR (IY+d)     | 4     | 7       | 19     |

| RR g          | 2     | 3       | 7      |

| RST v         | 1     | 5       | 11     |

| SBC A,(HL)    | 1     | 2       | 6      |

| SBC A, (IX+d) | 3     | 6       | 14     |

| SBC A,(IY+d)  | 3     | 6       | 14     |

| SBC A,m       | 2     | 2       | 6      |

| SBC A,g       | 1     | 2       | 4      |

| SBC HL,ww     | 2     | 6       | 10     |

| SCF           | 1     | 1       | 3      |

| SET b,(HL)    | 2     | 5       | 13     |

| SET b,(IX+d)  | 4     | 7       | 19     |

| SET b,(IY+d)  | 4     | 7       | 19     |

| SET b,g       | 2     | 3       | 7      |

| SLA (HL)      | 2     | 5       | 13     |

| SLA (IX+d)    | 4     | 7       | 19     |

| SLA (IY+d)    | 4     | 7       | 19     |

| SLA g         | 2     | 3       | 7      |

| SLP**         | 2     | 2       | 8      |

| SRA (HL)      | 2     | 5       | 13     |

| SRA (IX+d)    | 4     | 7       | 19     |

| SRA (IY+d)    | 4     | 7       | 19     |

| SRA g         | 2     | 3       | 7      |

| SRL (HL)      | 2     | 5       | 13     |

| SRL (IX+d)    | 4     | 7       | 19     |

| Instruction | Machine<br>Cycle | States | Address                        | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------|------------------|--------|--------------------------------|----------------|----|----|------|------|-----------|------|----|

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| IN g,(C)    | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | BC                             | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INO g,(m)** | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | 1st operand<br>Address         | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|             | MC4              | T1T2T3 | m to A0~A7<br>00H to<br>A8~A15 | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INI<br>IND  | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | BC                             | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|             | MC4              | T1T2T3 | HL                             | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INIR        | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| INDR        | MC3              | T1T2T3 | BC                             | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

| (If Br≠0)   | MC4              | T1T2T3 | HL                             | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|             | MC5~M<br>C6      | TiTi   | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction | Machine<br>Cycle | States | Address                        | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------|------------------|--------|--------------------------------|----------------|----|----|------|------|-----------|------|----|

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| OTIM**      | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| OTDM**      | MC3              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC4              | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|             | MC5              | T1T2T3 | C to A0~A7<br>00H to<br>A8~A15 | DATA           | 1  | 0  | 1    | 0    | 1         | 1    | 1  |

|             | MC6              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| OTIMR**     | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| OTDMR**     | MC3              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| (If Br≠0)   | MC4              | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|             | MC5              | T1T2T3 | C to A0~A7<br>00H to<br>A8~A15 | DATA           | 1  | 0  | 1    | 0    | 1         | 1    | 1  |

|             | MC6~M<br>C8      | TiTiTi | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

### **INTERRUPTS**

|                | Machine     |                |                                 |                    |    |    |      |      |    |      |    |

|----------------|-------------|----------------|---------------------------------|--------------------|----|----|------|------|----|------|----|

| Instruction    | Cycle       | States         | Address                         | Data               | RD | WR | MREQ | IORQ | M1 | HALT | ST |

|                | MC1         | T1T2T3         | Next Op<br>Code<br>Address (PC) |                    | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| NMI            | MC2<br>~MC3 | T1T1           | *                               | Z                  | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                | MC4         | T1T2T3         | SP-1                            | РСН                | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                | MC5         | T1T2T3         | SP-2                            | PCL                | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

| INTO Mode 0    | MC1         | T1T2TW<br>TWT3 | Next Op<br>Code<br>Address      | 1st(PC)<br>Op Code | 1  | 1  | 1    | 0    | 0  | 1    | 0  |

| (RST Inserted) | MC2<br>~MC3 | T1T1           | *                               | Z                  | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                | MC4         | T1T2T3         | SP-1                            | РСН                | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                | MC5         | T1T2T3         | SP-2                            | PCL                | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                | MC1         | T1T2Tw<br>TWT3 | Next Op<br>Code<br>Address (PC) | 1st<br>Op Code     | 1  | 1  | 1    | 0    | 0  | 1    | 0  |

| INT0 Mode 0    | MC2         | T1T2T3         | PC                              | n                  | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| (Call          | MC3         | T1T2T3         | PC+1                            | m                  | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| Inserted)      | MC4         | Ti             | *                               | Z                  | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                | MC5         | T1T2T3         | SP-1                            | PC+2(H)            | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                | MC6         | T1T2T3         | SP-2                            | PC+2(L)            | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

| INT0 Mode 1    | MC1         | T1T2TW<br>TWT3 | Next<br>Op Code<br>Address (PC) |                    | 1  | 1  | 1    | 0    | 0  | 1    | 0  |

|                | MC2         | T1T2T3         | SP-1                            | РСН                | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                | MC3         | T1T2T3         | SP-2                            | PCL                | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

#### Table 52.Interrupts

UM005003-0703

Note: If Bus Request and Refresh Request occur simultaneously, Bus Request is accepted but Refresh Request is cleared.

# **OPERATION MODE TRANSITION**

298

| Register                                        | Mnemonics | Address | Remarks                                                                                                               |                                                 |  |  |  |

|-------------------------------------------------|-----------|---------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|

| Timer Data Register<br>Channel 1L:              | TMDR1L    | 1 4     |                                                                                                                       |                                                 |  |  |  |

| Timer Data Register<br>Channel 1H:              | TMDR1H    | 1 5     |                                                                                                                       |                                                 |  |  |  |

| Timer Reload Register<br>Channel 1L             | RLDR1L    | 1 6     |                                                                                                                       |                                                 |  |  |  |

| Timer Reload Register<br>Channel 1H:            | RLDR1H    | 1 7     |                                                                                                                       |                                                 |  |  |  |

| Free Running Counter:                           | FRC       | 1 8     | Read only                                                                                                             |                                                 |  |  |  |

| DMA Source Address<br>Register Channel 0L:      | SAR0L     | 2 0     |                                                                                                                       |                                                 |  |  |  |

| DMA Source Address<br>Register Channel 0H:      | SAR0H     | 2 1     |                                                                                                                       |                                                 |  |  |  |

| DMA Source Address<br>Register Channel 0B:      | SAR0B     | 2 2     | Bits 0-2 (3) are used for SAR0B DMA Transfe<br>A <sub>19</sub> *, A <sub>18</sub> , A <sub>17</sub> , A <sub>16</sub> |                                                 |  |  |  |

| DMA Destination Address<br>Register Channel 0L: | DAR0L     | 2 3     | X X 0 1 RDR0                                                                                                          | (ASCI0)<br>(ASCI1)                              |  |  |  |

| DMA Destination Address<br>Register Channel 0H: | DAR0H     | 2 4     | X X 1 1 Not us                                                                                                        | ed                                              |  |  |  |

| DMA Destination Address<br>Register Channel 0B: | DAR0B     | 2 5     | Bits 0-2 (3) are used for DAR0B DMA Transf<br>A <sub>19</sub> *, A <sub>18</sub> , A <sub>17</sub> , A <sub>16</sub>  |                                                 |  |  |  |

| DMA Byte Count Register<br>Channel 0L:          | BCROL     | 2 6     | X X 0 1 TDR0<br>X X 1 0 TDR1                                                                                          | Q <sub>0</sub> (external)<br>(ASCI0)<br>(ASCI1) |  |  |  |

| DMA Byte Count Register<br>Channel 0H:          | BCROH     | 2 7     | X X I I Not us                                                                                                        | sed                                             |  |  |  |

| DMA Memory Address<br>Register<br>Channel 11.:  | MAR1L     | 2 8     |                                                                                                                       |                                                 |  |  |  |

| DMA Memory Address<br>Register<br>Channel 1H:   | MAR1H     | 2 9     |                                                                                                                       |                                                 |  |  |  |

#### Table 57. Internal I/O Registers (Continued)

\* In the R1 and Z mask, these DMAC registers are expanded from 4 bits to 3 bits in the package version of CP-68.