Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 6MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 64-DIP (0.750", 19.05mm)                               |

| Supplier Device Package         | 64-DIP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018006psg |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

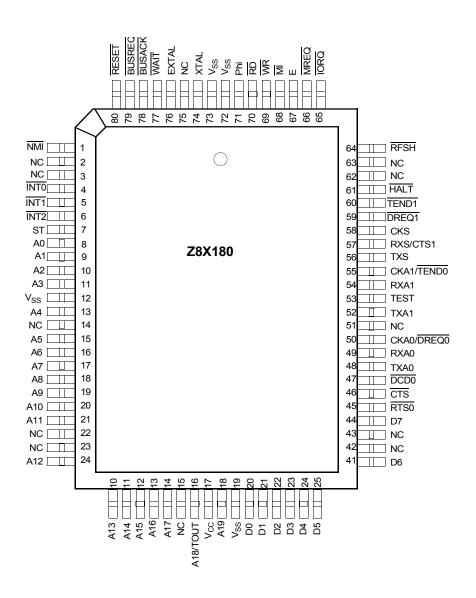

Figure 3. 80-Pin QFP

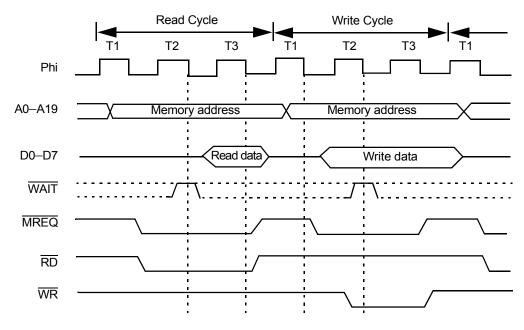

Wait States (TW) are inserted as previously described for Op Code fetch cycles. Figure 11 illustrates the read/write timing without Wait States (Tw), while Figure 12 illustrates read/write timing with Wait States (TW).

Figure 11. Memory Read/Write (without Wait State) Timing Diagram

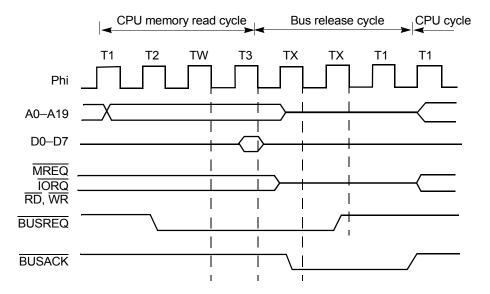

When the bus is released, the address (A0–A19), data (D0–D7), and control ( $\overline{MREQ}$ ,  $\overline{IORQ}$ ,  $\overline{RD}$ , and  $\overline{WR}$ ) signals are placed in the high impedance state.

Dynamic RAM refresh is not performed when the Z8X180 has released the bus. The alternate bus master must provide dynamic memory refreshing if the bus is released for long periods of time.

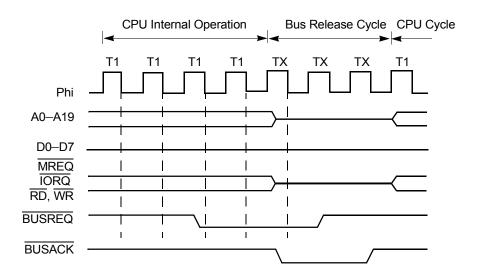

Figure 16 illustrates BUSREQ/BUSACK bus exchange during a memory read cycle. Figure 17 illustrates bus exchange when the bus release is requested during a Z8X180 CPU internal operation. BUSREQ is sampled at the falling edge of the system clock prior to T3, T1 and Tx (BUS RELEASE state). If BUSREQ is asserted Low at the falling edge of the clock state prior to Tx, another Tx is executed.

Figure 16. Bus Exchange Timing During Memory Read

Figure 17. Bus Exchange Timing During CPU Internal Operation

#### **Wait State Generator**

To ease interfacing with slow memory and I/O devices, the Z8X180 uses Wait States (TW) to extend bus cycle timing. A Wait State(s) is inserted based on the combined (logical OR) state of the external WAIT input and an internal programmable wait state (TW) generator. Wait States (TW) can be inserted in both CPU execution and DMA transfer cycles.

When the external WAIT input is asserted Low, Wait State(s) (TW) are inserted between T2 and T3 to extend the bus cycle duration. The WAIT input is sampled at the falling edge of the system clock in T2 or TW. If the WAIT input is asserted Low at the falling edge of the system clock in TW, another TW is inserted into the bus cycle.

Note: WAIT input transitions must meet specified setup and hold times. This specification can easily be accomplished by

- The HALT output pin is asserted Low

- The external bus activity consists of repeated dummy fetches of the Op Code following the HALT instruction.

Essentially, the Z80180 operates normally in HALT mode, except that instruction execution is stopped.

HALT mode can be exited in the following two ways:

- RESET Exit from HALT Mode

If the RESET input is asserted Low for at least six clock cycles, HALT mode is exited and the normal RESET sequence (restart at address 00000H) is initiated.

- Interrupt Exit from HALT mode

When an internal or external interrupt is generated, HALT mode is exited and the normal interrupt response sequence is initiated.

If the interrupt source is masked (individually by enable bit, or globally by IEF1 state), the Z80180 remains in HALT mode. However,  $\overline{NMI}$  interrupt initiates the normal  $\overline{NMI}$  interrupt response sequence independent of the state of IEF1.

HALT timing is illustrated in Figure 20.

## **MMU Register Description**

#### MMU Common/Bank Area Register (CBAR)

CBAR specifies boundaries within the Z8X180 64KB logical address space for up to three areas; Common Area 0, Bank Area and Common Area 1.

## MMU Common/Bank Area Register (CBAR: 3AH)

| Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit/Field | CA3 | CA2 | CA1 | CA0 | BA3 | BA2 | BA1 | BA0 |

| R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset     | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                             |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7–4             | CA7-4     | R/W |       | CA specifies the start (low) address (on 4KB boundaries) for the Common Area 1. This also determines the last address of the Bank Area. |

| 3–0             | BA3-0     | R/W |       | BA specifies the start (low) address (on 4KB boundaries) for the Bank Area. This also determines the last address of the Common Area 0. |

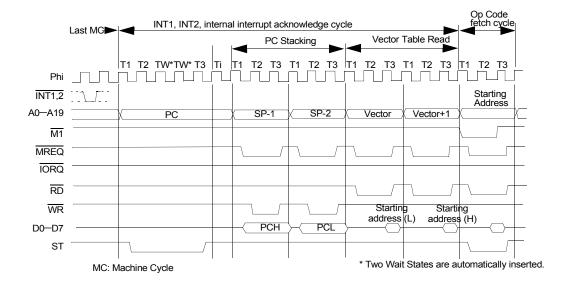

Figure 43. INT1, INT2 and Internal Interrupts Timing Diagram

## **Dynamic RAM Refresh Control**

The Z8X180 incorporates a dynamic RAM refresh control circuit including 8-bit refresh address generation and programmable refresh timing. This circuit generates asynchronous refresh cycles inserted at the programmable interval independent of CPU program execution. For systems which do not use dynamic RAM, the refresh function can be disabled.

When the internal refresh controller determines that a refresh cycle should occur, the current instruction is interrupted at the first breakpoint between machine cycles. The refresh cycle is inserted by placing the refresh address on A0–A7 and the  $\overline{RFSH}$  output is driven Low.

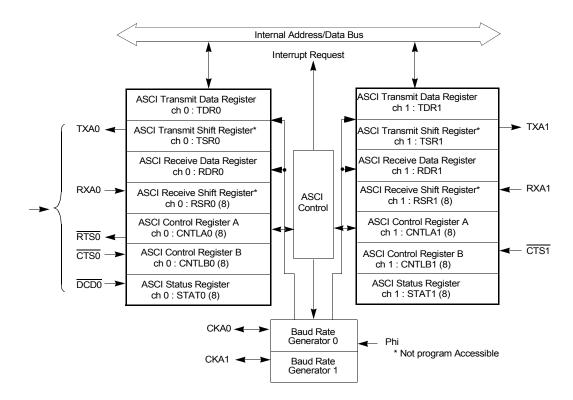

Figure 52. ASCI Block Diagram

## **ASCI Register Description**

The following subparagraphs explain the various functions of the ASCI registers.

## ASCI Transmit Shift Register 0, 1 (TSR0, 1)

When the ASCI Transmit Shift Register receives data from the ASCI Transmit Data Register (TDR), the data is shifted out to the TXA pin.

| Bit<br>Position | Bit/Field                  | R/W | Value  | Description                                         |

|-----------------|----------------------------|-----|--------|-----------------------------------------------------|

| 2               | Break<br>Feature<br>Enable | R/W | 0<br>1 | Break Feature Enable On<br>Break Feature Enable Off |

| 1               | Break<br>Detect<br>(RO)    | R/W | 0      | Break Detect On<br>Break Detect Off                 |

| 0               | Send<br>Break              | R/W | 0      | Normal Xmit<br>Drive TXA Low                        |

Each ASCI channel control register B configures multiprocessor mode, parity and baud rate selection.

## ASCI0 Time Constant Low Register (I/O Address: 1AH) (Z8S180/L180-Class Processors Only)

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

# ASCI0 Time Constant High Register (I/O Address: 1BH) (Z8S180/L180-Class Processors Only)

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

- c. Poll the RE bit in CNTR until RE = 0.

- d. Read the receive data from TRDR.

- e. Repeat steps 2 to 4 for each receive data byte.

- Receive–Interrupts

- a. Poll the RE bit in CNTR until RE is 0.

- b. Set the RE and EIE bits in CNTR to 1.

- c. When the receive interrupt occurs read the receive data from TRDR.

- d. Set the RE bit in CNTR to 1.

- e. Repeat steps 3 and 4 for each receive data byte.

#### **CSI/O Operation Timing Notes**

- Transmitter clocking and receiver sampling timings are different from internal and external clocking modes. Figure 59 to Figure 62 illustrate CSI/O Transmit/Receive Timing.

- The transmitter and receiver is disabled TE and RE = 0) when initializing or changing the baud rate.

#### **CSI/O Operation Notes**

- Disable the transmitter and receiver (TE and RE = 0) before initializing or changing the baud rate. When changing the baud rate after completion of transmission or reception, a delay of at least one bit time is required before baud rate modification.

- When RE or TE is cleared to 0 by software, a corresponding receive or transmit operation is immediately terminated. Normally, TE or RE is only cleared to 0 when EF is 1.

- Simultaneous transmission and reception is not possible. Thus, TE and RE are not both 1 at the same time

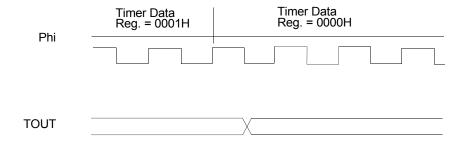

Figure 65. Timer Output Timing Diagram

## **PRT Interrupts**

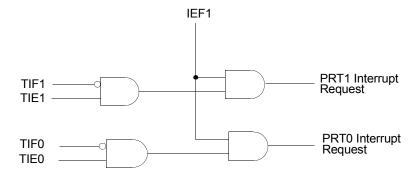

The PRT interrupt request circuit is illustrated in Figure 66.

Figure 66. PRT Interrupt Request Generation

#### PRT and RESET

During RESET, the bits in TCR are initialized as defined in the TCR register description. Down counting is stopped and the TMDR and RLDR registers are initialized to FFFFH. The A18/TOUT pin reverts to the address output function.

Figure 74 depicts CPU register configurations.

#### Register Set GR

| Accumulator A | Flag Register F |           |

|---------------|-----------------|-----------|

| B Register    | C Register      | General   |

| D Register    | E Register      | Purpose   |

| H Register    | L Register      | Registers |

#### Register Set GR'

| Accumulator A' | Flag Register F' |           |

|----------------|------------------|-----------|

| B' Register    | C' Register      | General   |

| D' Register    | E' Register      | >Purpose  |

| H' Register    | L' Register      | Registers |

#### Special Register

| Interrupt<br>Vector Register | R Counter |

|------------------------------|-----------|

| 1                            | R         |

| Index Register               | IX        |

| Index Register               | IY        |

| Stack Pointer                | SP        |

| Program Counter              | PC        |

Figure 74. CPU Register Configurations

## Accumulator (A, A')

The Accumulator (A) is the primary register used for many arithmetic, logical, and I/O instructions.

189

## **Z8L180 DC CHARACTERISTICS**

$V_{CC}$  = 3.3V  $\pm$  10%,  $V_{SS}$  = OV, Ta = 0° to +70°C, unless otherwise noted.)

Table 30. Z8L180 DC Characteristics

| Symbol | Item                                                | Condition                  | Minimum              | Typical | Maximum              | Unit |

|--------|-----------------------------------------------------|----------------------------|----------------------|---------|----------------------|------|

| VIH1   | Input High Voltage<br>RESET, EXTAL NMI              |                            | V <sub>CC</sub> -0.6 | _       | V <sub>CC</sub> +0.3 | V    |

| VIH2   | Input High Voltage except RESET, EXTAL NMI          |                            | 2.0                  |         | V <sub>CC</sub> +0.3 | V    |

| VIL1   | Input Low Voltage<br>RESET, EXTAL NMI               |                            | -0.3                 |         | 0.8                  | V    |

| VIL2   | Input Low Voltage<br>except RESET, EXTAL<br>NMI     |                            | -0.3                 |         | 0.8                  | V    |

| VOH1   | Output High Voltage all outputs                     | $IOH = -200 \mu A$         | 2.4                  |         |                      | V    |

| VOH2   | Output High Voltage<br>Output High Phi              | IOH = -200 μA              | V <sub>CC</sub> -0.6 |         |                      | V    |

| VOL    | Output Low Voltage all outputs                      | IOL = 4 mA                 | _                    | _       | 0.4                  | V    |

| VOL2   | Output Low Voltage<br>Output Low Phi                | IOL = 4 mA                 | _                    | _       | 0.4                  | V    |

| IIL    | Input Leakage Current all inputs except XTAL, EXTAL | $VIN = 0.5 \sim VCC - 0.5$ | _                    | _       | 1.0                  | μΑ   |

| ITL    | Three-State Leakage<br>Current                      | $VIN = 0.5 \sim VCC - 0.5$ | _                    | _       | 1.0                  | μΑ   |

207

## Instruction Set

This section explains the symbols in the instruction set.

#### **REGISTER**

g, g', ww, xx, yy, and zz specify a register to be used. g and g' specify an 8-bit register. ww, xx, yy, and zz specify a pair of 8-bit registers. Table 32 describes the correspondence between symbols and registers.

Table 32. Register Values

| g,g' | Reg. |

|------|------|

| 000  | В    |

| 001  | С    |

| 010  | D    |

| 011  | E    |

| 100  | Н    |

| 101  | L    |

| 111  | Α    |

| ww | Reg. | > |

|----|------|---|

| 00 | ВС   | ( |

| 01 | DE   | ( |

| 10 | HL   | ` |

| 11 | SP   | 1 |

| xx | Reg. |

|----|------|

| 00 | ВС   |

| 01 | DE   |

| 10 | IX   |

| 11 | SP   |

| уу | Reg. |

|----|------|

| 00 | ВС   |

| 01 | DE   |

| 10 | IY   |

| 11 | SP   |

| ZZ | Reg. |

|----|------|

| 00 | ВС   |

| 01 | DE   |

| 10 | HL   |

| 11 | AF   |

Note: Suffixed H and L to ww, xx, yy, zz (ex. wwH, IXL) indicate upper and lower 8-bit of the 16-bit register respectively.

### **BIT**

**b** specifies a bit to be manipulated in the bit manipulation instruction. Table 33 indicates the correspondence between **b** and bits.

Table 39. Rotate and Shift Instructions (Continued)

|                   |                |            |       |     |     |        |      |     |     |       |            |                                                   |   |          | F | lags |   |   |

|-------------------|----------------|------------|-------|-----|-----|--------|------|-----|-----|-------|------------|---------------------------------------------------|---|----------|---|------|---|---|

|                   |                |            |       |     | Add | Iressi | ing  |     |     |       |            |                                                   | 7 | 6        | 4 | 2    | 1 | 0 |

| Operation<br>Name |                | Op Code    | Immed | Ext | Ind | Reg    | Regi | lmp | Rel | Bytes | State<br>s | Operation                                         | s | z        | Н | P/V  | N | С |

| Bit Reset         | RES b,(IY + d) | 11 011 101 |       |     | S/D |        |      |     |     | 4     | 19         | $0\rightarrow b\bullet (IY + d)_M$                | • | •        | • | •    | • | • |

|                   |                | 11 001 011 |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   |                | 10 b 110   |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

| Bit Test          | BIT b, g       | 11 001 011 |       |     |     | S      |      |     |     | 2     | 6          | <del></del><br>b•gr→z                             | Х | 1        | S | X    | R | • |

|                   |                | 01bg       |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   | BIT b,(HL)     | 11 001 011 |       |     |     |        | S    |     |     | 2     | 9          | $\overline{b \bullet (HL)}_{M} \rightarrow Z$     | Х | <b>↑</b> | s | Х    | R | • |

|                   |                | 01 b 110   |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   | BIT b,(IX + d) | 11 011 101 |       |     | S   |        |      |     |     | 4     | 15         | $\overline{b \bullet (IX + d)}_{M} \rightarrow Z$ | Х | <b>↑</b> | s | X    | R | • |

|                   |                | 11 001 011 |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   |                | 01 b 110   |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   | BIT b,(IY + d) | 11 111 101 |       |     | s   |        |      |     |     | 4     | 15         | $b \bullet (IY + d)_M \rightarrow Z$              | Х | <b>↑</b> | s | Х    | R | • |

|                   |                | 11 001 011 |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      | 1 |   |

|                   |                | 01 b 110   |       |     |     |        |      |     |     |       |            |                                                   |   |          |   |      | ı |   |

|               |       | Machine |                     |

|---------------|-------|---------|---------------------|

| MNEMONICS     | Bytes | Cycles  | States              |

| LD g,g'       | 1     | 2       | 4                   |

| LD SP,HL      | 1     | 2       | 4                   |

| LD SP,IX      | 2     | 3       | 7                   |

| LD SP,IY      | 2     | 3       | 7                   |

| MLT ww"       | 2     | 13      | 17                  |

| NEG           | 2     | 2       | 6                   |

| NOP           | 1     | 1       | 3                   |

| OR (HL)       | 1     | 2       | 6                   |

| OR (IX+d)     | 3     | 6       | 14                  |

| OR (IY+d)     | 3     | 6       | 14                  |

| OR m          | 2     | 2       | 6                   |

| OR g          | 1     | 2       | 4                   |

| OTDM**        | 2     | 6       | 14                  |

| OTDMR**       | 2     | 8       | $16 (If Br \neq 0)$ |

|               | 2     | 6       | 14 (If $Br = 0$ )   |

| OTDR          | 2     | 6       | $14 (If Br \neq 0)$ |

|               | 2     | 4       | 12 (If $Br = 0$     |

| OTIM**        | 2     | 6       | 14                  |

| OTIMR**       | 2     | 8       | $16 (If Br \neq 0)$ |

|               | 2     | 6       | 14 (If $Br = 0$ )   |

| OTIR          | 2     | 6       | $14 (If Br \neq 0)$ |

|               | 2     | 4       | 12 (If $Br = 0$ )   |

| OUTD          | 2     | 4       | 12                  |

| OUTI          | 2     | 4       | 12                  |

| OUT (m),A     | 2     | 4       | 10                  |

| OUT (C),g     | 2     | 4       | 10                  |

| OUT0 (m),g ** | 3     | 5       | 13                  |

| POP IX        | 2     | 4       | 12                  |

| POP IY        | 2     | 4       | 12                  |

| POP zz        | 1     | 3       | 9                   |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction                                           | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT  | ST |

|-------------------------------------------------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|-------|----|

|                                                       | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1     | 0  |

| CPI<br>CPD                                            | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1     | 1  |

|                                                       | мс3              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1     | 1  |

|                                                       | MC1              | 1      | 1                      | 1              | 1  | 1  |      |      |           |       |    |

|                                                       | MC1              | T1T2T3 |                        |                | 0  | 1  | 0    | 1    | 0         | 1     | 0  |

| CPIR<br>CPDR<br>(If $BC_R \neq 0$ and $Ar = (HL)_M$ ) | MC2              | T1T2T3 |                        |                | 0  | 1  | 0    | 1    | 0         | 1     | 1  |

|                                                       | MC3              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1     | 1  |

|                                                       | _                |        | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1 1 1 | 1  |

|                                                       | MC1              | T1T2T3 |                        |                | 0  | 1  | 0    | 1    | 0         | 1     | 0  |

| CPIR<br>CPDR<br>(If BC <sub>R</sub> =0 or             | MC2              | T1T2T3 |                        |                | 0  | 1  | 0    | 1    | 0         | 1     | 1  |

| $Ar=(HL)_M$                                           | MC3              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1     | 1  |

|                                                       |                  | TiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1     | 1  |

| CPL                                                   | MC1              | T1T2T3 |                        |                | 0  | 1  | 0    | 1    | 0         | 1     | 0  |

| DAA                                                   | MC1              | T1T2T3 |                        |                | 0  | 1  | 0    | 1    | 0         | 1     | 0  |

|                                                       | MC2              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1     | 1  |

| DI*1                                                  | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1     | 0  |

UM005003-0703

Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction               | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | M1 | HALT | ST |

|---------------------------|------------------|--------|------------------------|----------------|----|----|------|------|----|------|----|

|                           | MC1              | TIT2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| INIR<br>INDR<br>(If Br=0) | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

| ,                         | мс3              | T1T2T3 | ВС                     | DATA           | 0  | 1  | 1    | 0    | 1  | 1    | 1  |

|                           | MC4              | T1T2T3 | HL                     | DATA           | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                           | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| JP mn                     | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                           | MC3              | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    |    | 1    |    |

| JP f,mn                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| (if is false)             | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                           | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| JP f,mn<br>(If f is true) | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                           | MC3              | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| JP (HL)                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| JP (IX)                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| JP (IY)                   | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction                                 | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | M1 | HALT | ST |

|---------------------------------------------|------------------|--------|------------------------|----------------|----|----|------|------|----|------|----|

|                                             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| JR j                                        | MC2              | T1T2T3 | 1st operand<br>Address | j-2            | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                                             | MC3~M<br>C4      | TiTi   | *                      | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

| JR C,j JR NC,j<br>JR Z,j JR NZ,j            | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| (if condition is false)                     | MC2              | T1T2T3 | 1st operand<br>Address | j-2            | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| JR C,j JR NC,j                              | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| JR Z,j JR NZ,j<br>(if condition<br>is true) | MC2              | T1T2T3 | 1st operand<br>Address | j-2            | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| ,                                           | MC3~M<br>C4      | TiTi   | *                      | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

| LD g,g'                                     | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                                             | MC2              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                                             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| LD g,m                                      | MC2              | T1T2T3 | 1st operand<br>Address | m              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| LD g, (HL)                                  | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                                             | MC2              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

287

## Status Signals

## PIN OUTPUTS IN EACH OPERATING MODE

Table 55 describes pin outputs in each operating mode.

Table 55. Pin Outputs in Each Operating Mode

|                        |                                           |           |      |      |    |    |      |      |        |    | Address | Data |

|------------------------|-------------------------------------------|-----------|------|------|----|----|------|------|--------|----|---------|------|

| Mode                   |                                           | <u>M1</u> | MREQ | IORQ | RD | WR | RFSH | HALT | BUSACK | ST | BUS     | BUS  |

| CPU<br>Operation       | Op Code Fetch<br>(1st Op Code)            | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 0  | A       | IN   |

|                        | Op Code Fetch<br>(except 1 st Op<br>Code) | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 1  | A       | IN   |

|                        | MemRead                                   | 1         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 1  | A       | IN   |

|                        | Memory Write                              | 1         | 0    | 1    | 1  | 0  | 1    | 1    | 1      | 1  | A       | OUT  |

|                        | I/O Read                                  | 1         | 1    | 0    | 0  | 1  | 1    | 1    | 1      | 1  | A       | IN   |

|                        | I/O Write                                 | 1         | 1    | 0    | 1  | 0  | 1    | 1    | 1      | 1  | A       | OUT  |

|                        | Internal<br>Operation                     | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 1  | A       | IN   |

| Refresh                |                                           | 1         | 0    | 1    | 1  | 1  | 0    | 1    | 1      | *  | A       | IN   |

| Interrupt              | NMI                                       | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 0  | A       | IN   |

| Acknowledge<br>Cycle   | ĪNT0                                      | 0         | 1    | 0    | 1  | 1  | 1    | 1    | 1      | 0  | A       | IN   |

| (1st Machine<br>Cycle) | INT1, INT2 &<br>Internal<br>Interrupts    | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 0  | A       | IN   |

| BUS RELEAS             | E                                         | 1         | Z    | Z    | Z  | Z  | 1    | 1    | 0      | *  | Z       | IN   |

| HALT                   |                                           | 0         | 0    | 1    | 0  | 1  | 1    | 0    | 1      | 0  | A       | IN   |

| SLEEP                  |                                           | 1         | 1    | 1    | 1  | 1  | 1    | 0    | 1      | 1  | 1       | IN   |