#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 6MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018006vsc |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MANUAL OBJECTIVES

This user manual describes the features of the Z8018x MPUs. This manual provides basic programming information for the Z80180/Z8S180/Z8L180. These cores and base peripheral sets are used in a large family of ZiLOG products. Below is a list of ZiLOG products that use this class of processor, along with the associated processor family. This document is also the core user manual for the following products:

| Part                  | Family          |

|-----------------------|-----------------|

| Z80180                | Z80180          |

| Z8S180                | Z8S180          |

| Z8L180                | Z8L180          |

| Z80181                | Z80180          |

| Z80182                | Z80180, Z8S180* |

| Z80S183               | Z8S180          |

| Z80185/195            | Z8S180          |

| Z80189                | Z8S180          |

| * Part number-dependa | nt              |

# **Intended Audience**

This manual is written for those who program the Z8018x.

# **Manual Organization**

The Z8018x User Manual is divided into five sections, seven appendices, and an index.

30

inserted depending on the programmed value in IWI1 and IWI0. Refer to Table 4.

#### Table 4.Wait State Insertion

|      |      | The Number of Wait States                 |                                              |                                                                  |                                                                                      |                                                                                |  |  |  |  |  |

|------|------|-------------------------------------------|----------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| IWI1 | IWIO | For external<br>I/O registers<br>accesses | For internal<br>I/O<br>registers<br>accesses | For INTO<br>interrupt<br>acknowledge<br>cycles when<br>M1 is Low | For INT1,<br>INT2 and<br>internal<br>interrupts<br>acknowledge<br>cycles<br>(Note 2) | For NMI<br>interrupt<br>acknowledge<br>cycles<br>when M1 is<br>Low<br>(Note 2) |  |  |  |  |  |

| 0    | 0    | 1                                         | 0                                            | 2                                                                | 2                                                                                    | 0                                                                              |  |  |  |  |  |

| 0    | 1    | 2                                         | (Note 1)                                     | 4                                                                |                                                                                      |                                                                                |  |  |  |  |  |

| 1    | 0    | 3                                         |                                              | 5                                                                |                                                                                      |                                                                                |  |  |  |  |  |

| 1    | 1    | 4                                         |                                              | 6                                                                |                                                                                      |                                                                                |  |  |  |  |  |

Note:

- For Z8X180 internal I/O register access (I/O addresses 0000H-003FH), IWI1 and IWI0 do not determine wait state (TW) timing. For ASCI, CSI/O and PRT Data Register accesses, 0 to 4 Wait States (TW) are generated. The number of Wait States inserted during access to these registers is a function of internal synchronization requirements and CPU state. All other on-chip I/O register accesses (that is, MMU, DMAC, ASCI Control Registers, for instance.) have no Wait States inserted and thus require only three clock cycles.

- 2. For interrupt acknowledge cycles in which  $\overline{M1}$  is High, such as interrupt vector table read and PC stacking cycle, memory access timing applies.

#### WAIT Input and RESET

During RESET, MWI1, MWI0 IWI1 and IWI0, are all 1, selecting the maximum number of Wait States (TW) (three for memory accesses, four for external I/O accesses).

42

To avoid address conflicts with external I/O, the Z8X180 internal I/O addresses can be relocated on 64-byte boundaries within the bottom 256 bytes of the 64KB I/O address space.

#### I/O Control Register (ICR)

ICR allows relocating of the internal I/O addresses. ICR also controls enabling/disabling of the IOSTOP mode.

I/O Control Register (ICR: 3FH)

| Bit        | 7         | 6          | 5          | 4          | 3        | 2 | 1 | 0 |

|------------|-----------|------------|------------|------------|----------|---|---|---|

| Bit/Field  | IOA7      | IOA6       | IOSTP      |            |          |   |   | — |

| R/W        | R/W       | R/W        | R/W        |            |          |   |   |   |

| Reset      | 0         | 0          | 0          |            |          |   |   |   |

| R = Read W | V = Write | X = Indete | erminate f | ? = Not Ap | plicable |   |   |   |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                            |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6             | IOA7:6    | R/W |       | IOA7 and IOA6 relocate internal I/O as depicted in<br>Figure . The high-order 8 bits of 16-bit internal I/O<br>addresses are always 0. IOA7 and IOA6 are cleared to 0<br>during RESET. |

| 5               | IOSTP     | R/W |       | IOSTOP mode is enabled when IOSTP is set to 1.<br>Normal. I/O operation resumes when IOSTP is reset to 0.                                                                              |

56

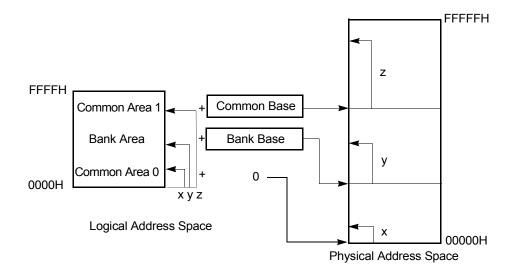

Figure 24. Physical Address Transition

#### **MMU Block Diagram**

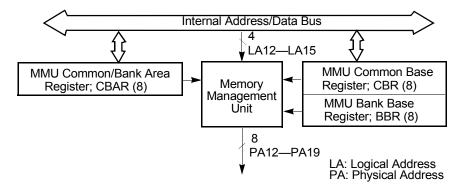

The MMU block diagram is depicted in Figure 25. The MMU translates internal 16-bit logical addresses to external 20-bit physical addresses.

Figure 25. MMU Block Diagram

#### **MMU and RESET**

During RESET, all bits of the CA field of CBAR are set to 1 while all bits of the BA field of CBAR, CBR and BBR are reset to 0. The logical 64KB address space corresponds directly with the first 64KB 0000H to FFFFH) of the 1024KB 0000H. to FFFFFH) physical address space. Thus, after RESET, the Z8X180 begins execution at logical and physical address 0.

#### **MMU Register Access Timing**

When data is written into CBAR, CBR or BBR, the value is effective from the cycle immediately following the I/O write cycle which updates these registers.

During MMU programming insure that CPU program execution is not disrupted. The next cycle following MMU register programming is normally an Op Code fetch from the newly translated address. One technique is to localize all MMU programming routines in a Common Area that is always enabled.

Z8018x Family MPU User Manual

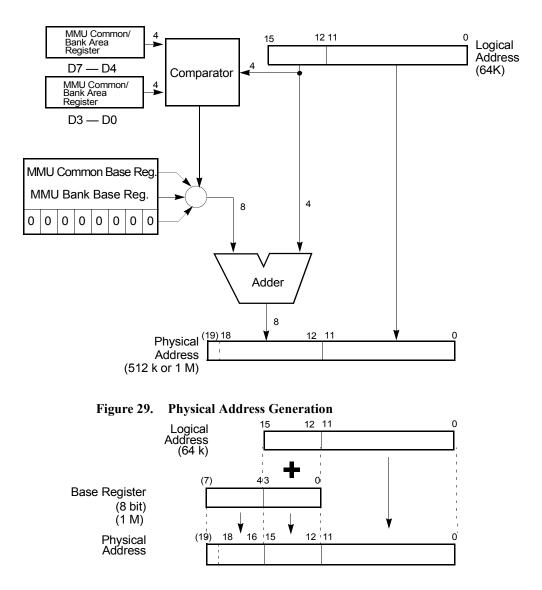

Figure 30. Physical Address Generation 2

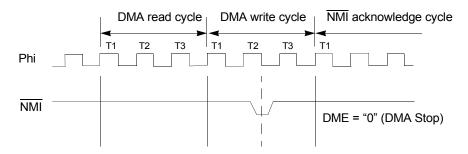

If the falling edge of  $\overline{\text{NMI}}$  occurs before the falling clock of the state prior to T3 (T2 or Tw) of the DMA write cycle, the DMAC is suspended and the CPU starts the  $\overline{\text{NMI}}$  response at the end of the current cycle. By setting a channel's DE bit to 1, the channel's operation is restarted and DMA correctly resumes from its suspended point by  $\overline{\text{NMI}}$ . (Reference Figure 51.)

Figure 51. NMI and DMA Operation Timing Diagram

#### **DMAC and RESET**

During RESET the bits in DSTAT, DMODE, and DCNTL are initialized as stated in their individual register descriptions. Any DMA operation in progress is stopped, allowing the CPU to use the bus to perform the RESET sequence. However, the address register (SAR0, DAR0 MAR1, IAR1) and byte count register (BCR0 BCR1) contents are not changed during RESET.

# Asynchronous Serial Communication Interface (ASCI)

The Z8X180 on-chip ASCI has two independent full-duplex channels. Based on full programmability of the following functions, the ASCI directly communicates with a wide variety of standard UARTs (Universal Asynchronous Receiver/Transmitter) including the Z8440 SIO and the Z85C30 SCC.

#### ASCI Receive Shift Register 0,1(RSR0, 1)

This register receives data shifted in on the RXA pin. When full, data is automatically transferred to the ASCI Receive Data Register (RDR) if it is empty. If RSR is not empty when the next incoming data byte is shifted in, an overrun error occurs. The RSR is not program-accessible.

#### ASCI Receive Data Register 0,1 (RDR0, 1: I/O Address = 08H, 09H)

When a complete incoming data byte is assembled in RSR, it is automatically transferred to the RDR if RDR is empty. The next incoming data byte can be shifted into RSR while RDR contains the previous received data byte. Thus, the ASCI receiver on Z80180 is doublebuffered.

#### ASCI Receive Data Register Ch. 0 (RDR0: 08H)

| Bit                                                                 | 7 | 6                      | 5 | 4 | 3   | 2 | 1 | 0 |  |

|---------------------------------------------------------------------|---|------------------------|---|---|-----|---|---|---|--|

| Bit/Field                                                           |   | ASCI Receive Channel 0 |   |   |     |   |   |   |  |

| R/W                                                                 |   |                        |   |   | R/W |   |   |   |  |

| Reset                                                               |   | 0                      |   |   |     |   |   |   |  |

| Note: $R = Read$ $W = Write$ $X = Indeterminate$ ? = Not Applicable |   |                        |   |   |     |   |   |   |  |

#### ASCI Receive Data Register Ch. 1 (RDR1: 09H)

١

| Bit                                                             | 7 | 6                      | 5 | 4 | 3   | 2 | 1 | 0 |  |

|-----------------------------------------------------------------|---|------------------------|---|---|-----|---|---|---|--|

| Bit/Field                                                       |   | ASCI Receive Channel 1 |   |   |     |   |   |   |  |

| R/W                                                             |   |                        |   |   | R/W |   |   |   |  |

| Reset                                                           | 0 |                        |   |   |     |   |   |   |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |                        |   |   |     |   |   |   |  |

On the Z8S180 and Z8L180-class processors are quadruple buffered. The ASCI Receive Data Register is a read-only register. However, if RDRF =

131

Table 17.Data Formats

| MOD2 | MOD1 | MOD0 | Data Format                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Start + 7 bit data + 1 stop          |

| 0    | 0    | 1    | Start + 7 bit date + 2 Stop          |

| 0    | 1    | 0    | Start + 7 bit data + parity + 1 stop |

| 0    | 1    | 1    | Start + 7 bit data + parity + 2 stop |

| 1    | 0    | 0    | Start + 8 bit data + 1 stop          |

| 1    | 0    | 1    | Start + 8 bit data + 2 stop          |

| 1    | 1    | 0    | Start + 8 bit data + parity + 1 stop |

| 1    | 1    | 1    | Start + 8 bit date + parity + 2 stop |

#### ASCI Control Register B0, 1 (CNTLB0, 1)

Each ASCI channel control register B configures multiprocessor mode, parity and baud rate selection.

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6             | TIF1–0    | R   |       | <b>TIF1: Timer Interrupt Flag</b> — When TMDR1<br>decrements to 0, TIF1 is set to 1. This generates an<br>interrupt request if enabled by TIE1 = 1. TIF1 is reset to 0<br>when TCR is read and the higher or lower byte of<br>TMDR1 is read. During RESET, TIF1 is cleared to 0.<br>When TMDR0 decrements to 0, TIF0 is set to 1. This<br>generates an interrupt request if enabled by TIE0 = 1.<br>TIF0 is reset to 0 when TCR is read and the higher or<br>lower byte of TMDR0 is read. During RESET, TIF0 is<br>cleared to 0. |

| 5-4             | TIE1–0    | R/W |       | <b>Timer Interrupt Enable</b> — When TIE1 is set to 1, TIF1<br>= 1 generates a CPU interrupt request. When TIE1 is reset<br>to 0, the interrupt request is inhibited. During RESET,<br>TIE1 is cleared to 0.<br>When TIE0 is set to 1, TIF0 = 1 generates a CPU interrupt<br>request. When TIE0 is reset to 0, the interrupt request is<br>inhibited. During RESET, TIE0 is cleared to 0.                                                                                                                                        |

| 3-2             | TOC1-0    | R/W |       | <b>Timer Output Control</b> — TOC1, and TOC0 control the output of PRT1 using the multiplexed A18/TOUT pin as shown in Table 23. During RESET, TOC1 and TOC0 are cleared to 0. This selects the address function for A18/TOUT. By programming TOC1 and TOC0 the A18/TOUT pin can be forced HIGH, LOW, or toggled when TMDR1 decrements to 0. Reference Table 23.                                                                                                                                                                 |

| 1-0             | TDE1–0    | R/W |       | <b>Timer Down Count Enable</b> — TDE1 and TDE0 enable<br>and disable down counting for TMDR1 and TMDR0<br>respectively. When TDEn ( $n = 0, 1$ ) is set to 1, down<br>counting is executed for TMDRn. When TDEn is reset to<br>0, down counting is stopped and TMDRn is freely read or<br>written. TDE1 and TDE0 are cleared to 0 during RESET<br>and TMDRn does not decrement until TDEn is set to 1.                                                                                                                           |

#### TST (HL) - Test Memory

The contents of memory pointed to by HL are ANDed with the accumulator (A) and the status flags are updated. The memory contents and accumulator are not changed (non-destructive AND).

#### INO g, (m) - Input, Immediate I/O address

The contents of immediately specified 8-bit I/O address are input into the specified register. When I/O is accessed, 00H is output in high-order bits of the address automatically.

#### OUTO (m), g - Output, Immediate I/O address

The contents of the specified register are output to the immediately specified 8-bit I/O address. When I/O is accessed, 00H is output in high-order bits of the address automatically.

## **CPU REGISTERS**

The Z80180 CPU registers consist of Register Set GR, Register Set GR' and Special Registers.

The Register Set GR consists of 8-bit Accumulator (A), 8-bit Flag Register (F), and three General Purpose Registers (BC, DE, and HL) which may be treated as 16-bit registers (BC, DE, and HL) or as individual 8-bit registers (B, C, D, E, H, and L) depending on the instruction to be executed. The Register Set GR' is alternate register set of Register Set GR and also contains Accumulator (A'), Flag Register (F') and three General Purpose Registers (BC', DE', and HL'). While the alternate Register Set GR' contents are not directly accessible, the contents can be programmably exchanged at high speed with those of Register Set GR.

The Special Registers consist of 8-bit Interrupt Vector Register (I), 8-bit R Counter (R), two 16-bit Index Registers (IX and IY), 16-bit Stack Pointer (SP), and 16-bit Program Counter (PC)

189

# **Z8L180 DC CHARACTERISTICS**

$V_{CC} = 3.3V \pm 10\%$ ,  $V_{SS} = OV$ , Ta = 0° to +70°C, unless otherwise noted.)

Table 30. Z8L180 DC Characteristics

| Symbol | Item                                                      | Condition            | Minimum              | Typical | Maximum              | Unit |

|--------|-----------------------------------------------------------|----------------------|----------------------|---------|----------------------|------|

| VIH1   | Input High Voltage<br>RESET, EXTAL NMI                    |                      | V <sub>CC</sub> -0.6 | _       | V <sub>CC</sub> +0.3 | v    |

| VIH2   | Input High Voltage<br>except RESET, EXTAL<br>NMI          |                      | 2.0                  |         | V <sub>CC</sub> +0.3 | V    |

| VIL1   | Input Low Voltage<br>RESET, EXTAL NMI                     |                      | -0.3                 |         | 0.8                  | V    |

| VIL2   | Input Low Voltage<br>except RESET, EXTAL<br>NMI           |                      | -0.3                 |         | 0.8                  | V    |

| VOH1   | Output High Voltage<br>all outputs                        | IOH = -200 μA        | 2.4                  |         |                      | V    |

| VOH2   | Output High Voltage<br>Output High Phi                    | $IOH = -200 \ \mu A$ | V <sub>CC</sub> -0.6 |         |                      | V    |

| VOL    | Output Low Voltage<br>all outputs                         | IOL = 4 mA           | _                    | _       | 0.4                  | V    |

| VOL2   | Output Low Voltage<br>Output Low Phi                      | IOL = 4 mA           | _                    | _       | 0.4                  | V    |

| IIL    | Input Leakage Current<br>all inputs except XTAL,<br>EXTAL | VIN = 0.5 ~ VCC -0.5 | -                    | _       | 1.0                  | μA   |

| ITL    | Three-State Leakage<br>Current                            | VIN = 0.5 ~ VCC -0.5 | -                    | —       | 1.0                  | μΑ   |

194

|     |                   | Operation                                                                      | <b>Z8S</b> 1 | 180—20 | Z8S |     |      |

|-----|-------------------|--------------------------------------------------------------------------------|--------------|--------|-----|-----|------|

|     |                   |                                                                                | Ν            | ЛНz    | I   |     |      |

| No. | Symbol            | Item                                                                           | Min          | Max    | Min | Max | Unit |

| 12  | t <sub>MED2</sub> | PHI Fall to MREQ Rise Delay                                                    |              | 25     | _   | 15  | ns   |

| 13  | t <sub>RDD2</sub> | PHI Fall to RD Rise Delay                                                      |              | 25     |     | 15  | ns   |

| 14  | t <sub>M1D2</sub> | PHI Rise to $\overline{M1}$ Rise Delay                                         |              | 40     |     | 15  | ns   |

| 15  | t <sub>DRS</sub>  | Data Read Set-up Time                                                          | 10           |        | 5   |     | ns   |

| 16  | t <sub>DRH</sub>  | Data Read Hold Time                                                            | 0            |        | 0   |     | ns   |

| 17  | t <sub>STD1</sub> | PHI Fall to ST Fall Delay                                                      |              | 30     |     | 15  | ns   |

| 18  | t <sub>STD2</sub> | PHI Fall to ST Rise Delay                                                      |              | 30     |     | 15  | ns   |

| 19  | t <sub>WS</sub>   | WAIT Set-up Time to PHI Fall                                                   | 15           |        | 10  |     | ns   |

| 20  | t <sub>WH</sub>   | WAIT Hold Time from PHI Fall                                                   | 10           |        | 5   |     | ns   |

| 21  | t <sub>WDZ</sub>  | PHI Rise to Data Float Delay                                                   |              | 35     |     | 20  | ns   |

| 22  | t <sub>WRD1</sub> | PHI Rise to WR Fall Delay                                                      |              | 25     |     | 15  | ns   |

| 23  | t <sub>WDD</sub>  | PHI Fall to Write Data Delay Time                                              |              | 25     |     | 15  | ns   |

| 24  | t <sub>WDS</sub>  | Write Data Set-up Time to WR Fall                                              | 10           |        | 10  |     | ns   |

| 25  | t <sub>WRD2</sub> | PHI Fall to WR Rise Delay                                                      |              | 25     |     | 15  | ns   |

| 26  | t <sub>WRP</sub>  | WR Pulse Width (Memory Write Cycle)                                            | 80           |        | 45  |     | ns   |

| 26a |                   | WR Pulse Width (I/O Write Cycle)                                               | 150          |        | 70  |     | ns   |

| 27  | t <sub>WDH</sub>  | Write Data Hold Time from $\overline{WR}$ Rise                                 | 10           |        | 5   |     | ns   |

| 28  | t <sub>IOD1</sub> | PHI Fall to $\overline{\text{IORQ}}$ Fall Delay $\overline{\text{IOC}}$<br>= 1 |              | 25     |     | 15  | ns   |

|     |                   | PHI Rise to $\overline{\text{IORQ}}$ Fall Delay $\overline{\text{IOC}} = 0$    | —            | 25     |     | 15  | -    |

| 29  | t <sub>IOD2</sub> | PHI Fall to IORQ Rise Delay                                                    |              | 25     |     | 15  | ns   |

| 30  | t <sub>IOD3</sub> | $\overline{\text{M1}}$ Fall to $\overline{\text{IORQ}}$ Fall Delay             | 125          |        | 80  | _   | ns   |

Table 31.Z8S180 AC Characteristics (Continued)  $V_{DD} = 5V \pm 10\%$  or $V_{DD} = 3.3V \pm 10\%$ ; 33-MHz Characteristics Apply Only to 5VOperation

196

|     |                   | Operation                                                    |     |                                 |     |                            |      |  |

|-----|-------------------|--------------------------------------------------------------|-----|---------------------------------|-----|----------------------------|------|--|

|     |                   |                                                              |     | Z8S180—20<br>MHz                |     | Z8S180—33<br>MHz           |      |  |

| No. | Symbol            | Item                                                         | Min | Max                             | Min | Max                        | Unit |  |

| 54  | t <sub>Ef</sub>   | Enable Fall Time                                             | _   | 10                              |     | 10                         | ns   |  |

| 55  | t <sub>TOD</sub>  | PHI Fall to Timer Output Delay                               |     | 75                              |     | 50                         | ns   |  |

| 56  | t <sub>STDI</sub> | CSI/O Transmit Data Delay Time<br>(Internal Clock Operation) | _   | 2                               |     | 2                          | tcyc |  |

| 57  | t <sub>STDE</sub> | CSI/O Transmit Data Delay Time<br>(External Clock Operation) |     | 7.5 t <sub>CY</sub><br>C<br>+75 |     | 75 t <sub>CYC</sub><br>+60 | ns   |  |

| 58  | t <sub>SRSI</sub> | CSI/O Receive Data Set-up Time<br>(Internal Clock Operation) | 1   | —                               | 1   |                            | tcyc |  |

| 59  | t <sub>SRHI</sub> | CSI/O Receive Data Hold Time<br>(Internal Clock Operation)   | 1   |                                 | 1   |                            | tcyc |  |

| 60  | t <sub>SRSE</sub> | CSI/O Receive Data Set-up Time<br>(External Clock Operation) | 1   |                                 | 1   |                            | tcyc |  |

| 61  | t <sub>SRHE</sub> | CSI/O Receive Data Hold Time<br>(External Clock Operation)   | 1   |                                 | 1   |                            | tcyc |  |

| 62  | t <sub>RES</sub>  | RESET Set-up Time to PHI Fall                                | 40  |                                 | 25  |                            | ns   |  |

| 63  | t <sub>REH</sub>  | RESET Hold Time from PHI Fall                                | 25  |                                 | 15  |                            | ns   |  |

| 64  | t <sub>OSC</sub>  | Oscillator Stabilization Time                                | —   | 20                              |     | 20                         | ns   |  |

| 65  | t <sub>EXR</sub>  | External Clock Rise Time (EXTAL)                             |     | 5                               |     | 5                          | ns   |  |

| 66  | t <sub>EXF</sub>  | External Clock Fall Time (EXTAL)                             | _   | 5                               |     | 5                          | ns   |  |

| 67  | t <sub>RR</sub>   | RESET Rise Time                                              |     | 50                              |     | 50                         | ms   |  |

| 68  | t <sub>RF</sub>   | RESET Fall Time                                              | _   | 50                              | _   | 50                         | ms   |  |

# Table 31.Z8S180 AC Characteristics (Continued) $V_{DD} = 5V \pm 10\%$ or $V_{DD} = 3.3V \pm 10\%$ ; 33-MHz Characteristics Apply Only to 5VOperation

# 207

# **Instruction Set**

This section explains the symbols in the instruction set.

## REGISTER

g, g', ww, xx, yy, and zz specify a register to be used. g and g' specify an 8-bit register. ww, xx, yy, and zz specify a pair of 8-bit registers. Table 32 describes the correspondence between symbols and registers.

Table 32.Register Values

111

А

| g,g' | Reg. | ww | Reg. | xx | Reg. | уу | Reg. | zz | Reg. |

|------|------|----|------|----|------|----|------|----|------|

| 000  | B    | 00 | BC   | 00 | BC   | 00 | BC   | 00 | BC   |

| 001  | С    | 01 | DE   | 01 | DE   | 01 | DE   | 01 | DE   |

| 010  | D    | 10 | HL   | 10 | IX   | 10 | IY   | 10 | HL   |

| 011  | Е    | 11 | SP   | 11 | SP   | 11 | SP   | 11 | AF   |

| 100  | Н    |    |      |    |      |    |      |    |      |

| 101  | L    |    |      |    |      |    |      |    |      |

Note: Suffixed H and L to ww, xx, yy, zz (ex. wwH, IXL) indicate upper and lower 8-bit of the 16-bit register respectively.

## BIT

**b** specifies a bit to be manipulated in the bit manipulation instruction. Table 33 indicates the correspondence between **b** and bits.

| Instruction | Machine<br>Cycle | States | Address                        | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------|------------------|--------|--------------------------------|----------------|----|----|------|------|-----------|------|----|

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| IN g,(C)    | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | BC                             | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INO g,(m)** | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | 1st operand<br>Address         | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|             | MC4              | T1T2T3 | m to A0~A7<br>00H to<br>A8~A15 | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INI<br>IND  | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | BC                             | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|             | MC4              | T1T2T3 | HL                             | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INIR        | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| INDR        | MC3              | T1T2T3 | BC                             | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

| (If Br≠0)   | MC4              | T1T2T3 | HL                             | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|             | MC5~M<br>C6      | TiTi   | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction                                                             | Machine<br>Cycle | States        | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------------------------------------------------------------------|------------------|---------------|------------------------|----------------|----|----|------|------|-----------|------|----|

| RLC (HL)                                                                | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RL (HL)<br>RRC (HL)<br>RR (HL)                                          | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| SLA (HL)<br>SRA (HL)                                                    | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| SRA (HL)<br>SRL (HL)                                                    | MC4              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC5              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

| $\frac{\text{RLC (IX + d)}}{\text{RLC (IY + d)}}$                       | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RL (IX + d) $RL (IY + d)$ $RRC (IX + d)$                                | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2ndOp<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| RRC (IY + d) $RR (IX + d)$ $RR (IY + d)$                                | MC3              | T1T2T3        | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| $\frac{RR(IY + d)}{SLA(IX + d)}$ $\frac{SLA(IY + d)}{SLA(IY + d)}$      | MC4              | T1T2T3        | 3rd Op Code<br>Address | 3rd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| $\frac{SRA (IX + d)}{SRA (IY + d)}$ $\frac{SRL (IX + d)}{SRL (IX + d)}$ | MC5              | T1T2T3        | IX+d<br>IY+d           | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| SRL (IY + d)<br>SRL (IY + d)                                            | MC6              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC7              | T1T2T3        | IX+d<br>IY+d           | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                                                                         | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RLD                                                                     | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| RRD                                                                     | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                                                                         | MC4~M<br>C7      | TiTiTiTi<br>* |                        | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC8              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

#### 287

# **Status Signals**

# **PIN OUTPUTS IN EACH OPERATING MODE**

Table 55 describes pin outputs in each operating mode.

| Mode                   |                                           | <u>M1</u> | MREQ | IORQ | RD | WR | RFSH | HALT | BUSACK | ST | Address<br>BUS | Data<br>BUS |

|------------------------|-------------------------------------------|-----------|------|------|----|----|------|------|--------|----|----------------|-------------|

| CPU<br>Operation       | Op Code Fetch<br>(1st Op Code)            | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

|                        | Op Code Fetch<br>(except 1 st Op<br>Code) | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

|                        | MemRead                                   | 1         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

|                        | Memory Write                              | 1         | 0    | 1    | 1  | 0  | 1    | 1    | 1      | 1  | А              | OUT         |

|                        | I/O Read                                  | 1         | 1    | 0    | 0  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

|                        | I/O Write                                 | 1         | 1    | 0    | 1  | 0  | 1    | 1    | 1      | 1  | А              | OUT         |

|                        | Internal<br>Operation                     | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

| Refresh                |                                           | 1         | 0    | 1    | 1  | 1  | 0    | 1    | 1      | *  | А              | IN          |

| Interrupt              | NMI                                       | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

| Acknowledge<br>Cycle   | <b>INTO</b>                               | 0         | 1    | 0    | 1  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

| (1st Machine<br>Cycle) | INT1, INT2 &<br>Internal<br>Interrupts    | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

| BUS RELEASE            |                                           | 1         | Z    | Z    | Z  | Z  | 1    | 1    | 0      | *  | Z              | IN          |

| HALT                   |                                           | 0         | 0    | 1    | 0  | 1  | 1    | 0    | 1      | 0  | А              | IN          |

| SLEEP                  |                                           | 1         | 1    | 1    | 1  | 1  | 1    | 0    | 1      | 1  | 1              | IN          |

#### Table 55. Pin Outputs in Each Operating Mode

|           |              | Pin Status in Each Operation Mode |                   |              |                |  |  |  |  |

|-----------|--------------|-----------------------------------|-------------------|--------------|----------------|--|--|--|--|

| Symbol    | Pin Function | RESET                             | SLEEP             | IOSTOP       | SYSTEM<br>STOP |  |  |  |  |

| MREQ      | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |  |

| Е         |              | 0                                 | E Clock<br>Output | <del>~</del> | ←              |  |  |  |  |

| <u>M1</u> | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |  |

| WR        | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |  |

| RD        | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |  |

| Phi       |              | Phi Clock<br>Output               | <del>~</del>      | <b>←</b>     | ←              |  |  |  |  |

Table 56.

Pin Status During RESET and LOW POWER OPERATION Modes (Continued)

- 1: HIGH 0: LOW A: Programmable Z: High Impedance

- IN (A): Input (Active) IN (N): Input (Not active) OUT: Output

- H: Holds the previous state

- $\leftarrow$ : same as the left

CSI/O control/status 147, 150, 159, 160, 161, 172 Direct bit field definitions 181 DMA mode (DMODE) 97 DMA status 95 DMA/WAIT control 100 Flag 178 I/O Control 42 I/O control (ICR) 42 Indirect addressing 181 INT/TRAP control (ITC) 67 Interrupt Vector (I) 66 MMU bank base (BBR) 62 MMU common bank area (CBAR) 60 MMU common base (CBR) 61 Operation mode control 15, 84 PRT timer control register 161 Refresh control 88 Relative addressing Addressing Relative 183 RETI control signal states 85 Instruction sequence 84 RTS0 timing diagram 140

# S

Secondary bus interface 165 SLEEP mode 33 SLP execution cycle timing diagram Timing diagram SLP execution cycle 203 Status summary table 10 SYSTEM STOP mode 35

# Т

Test conditions, standard 205 Timer initialization, count down and reload 163 Timer output timing diagram Timing diagram Timer output 202 Timing diagram 163 AC 197 Bus Exchange Timing During CPU Internal Operation 27 Bus Exchange Timing During Memory Read 26 CPU (I/O Read/Write cycles) 199 CSI/O external clock receive 156 CSI/O external clock transmit 154 CSI/O internal clock receive 155 CSI/O internal clock transmit 153 CSI/O receive/transmit 204 CSI/O timer output 164 DCD0 139 DMA control signals 200 DMA CYCLE STEAL mode 106 DMA edge-sense 108 DMA level-sense 107