#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 8MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | -40°C ~ 100°C (TA)                                     |

| Security Features               | -                                                      |

| Package / Case                  | 64-DIP (0.750", 19.05mm)                               |

| Supplier Device Package         | 64-DIP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018008peg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z8018x Family MPU User Manual

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

ZiLOG Worldwide Headquarters 532 Race Street San Jose, CA 95126-3432 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

© 2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

| r                  |            |      |   |    |                 |

|--------------------|------------|------|---|----|-----------------|

| V <sub>SS</sub> 1  | $\bigcirc$ |      | - | 64 | Phi             |

| XTAL 2             | $\bigcirc$ |      | _ | 63 | RD              |

| EXTAL 3            |            |      |   | 62 | WR              |

| WAIT 4             |            |      |   | 61 | MI              |

| BUSACK 5           |            |      |   | 60 | E               |

| BUSREQ 6           |            |      | - | 59 | MREQ            |

| RESET 7            |            |      | - | 58 | IORQ            |

| NMI 8              |            |      |   | 57 | RFSH            |

| INT0 9             |            |      | - | 56 | HALT            |

| INT1 10            |            |      | - | 55 | TEND1           |

| INT2 11            |            |      | _ | 54 | DREQ1           |

| ST 12              |            |      | - | 53 | CKS             |

| A0 13              |            |      | - | 52 | RXS/CTS1        |

| A1 14              |            |      |   | 51 | TXS             |

| A2 15              |            |      |   | 50 | CKA1/TEND0      |

| A3 16              | Z8         | X180 | - | 49 | RXA1            |

| A4 17              |            |      |   | 48 | TXA1            |

| A5 18              |            |      |   | 47 | CKA0/DREQ0      |

| A6 <u>19</u>       |            |      | - | 46 | RXA0            |

| A7 20              |            |      |   | 45 | TXA0            |

| A8 21              |            |      | - | 44 | DCO0            |

| A9 22              |            |      |   | 43 | CTS0            |

| A10 23             |            |      | - | 42 | RTS0            |

| A11 24             |            |      |   | 41 | D7              |

| A12 25             |            |      |   | 40 | D6              |

| A13 26             |            |      |   | 39 | D5              |

| A14 27             |            |      | - | 38 | D4              |

| A15 28             |            |      | - | 37 | D3              |

| A16 29             |            |      |   | 36 | D2              |

| A17 30             |            |      | - | 35 | D1              |

| A18/TOUT 31        |            |      | F | 34 | D0              |

| V <sub>CC</sub> 32 |            |      |   | 33 | V <sub>SS</sub> |

Figure 1. 64-Pin DIP

36

# Low Power Modes (Z8S180/Z8L180 only)

The following section is a detailed description of the enhancements to the Z8S180/L180 from the standard Z80180 in the areas of STANDBY, IDLE and STANDBY QUICK RECOVERY modes.

# **Add-On Features**

There are five different power-down modes. SLEEP and SYSTEM STOP are inherited from the Z80180. In SLEEP mode, the CPU is in a stopped state while the on-chip I/Os are still operating. In I/O STOP mode, the on-chip I/Os are in a stopped state while leaving the CPU running. In SYSTEM STOP mode, both the CPU and the on-chip I/Os are in the stopped state to reduce current consumption. The Z8S180 features two additional power-down modes, STANDBY and IDLE, to reduce current consumption even further. The differences in these power-down modes are summarized in Table 5.

If the BREXT bit of the CPU Control Register (CCR) is cleared, asserting the BUSREQ does not cause the Z8S180/Z8L180-class processors to exit STANDBY mode.

If STANDBY mode is exited because of a reset or an external interrupt, the Z8S180/Z8L180-class processors remains relinquished from the system bus as long as BUSREQ is active.

# **STANDBY Mode EXit with External Interrupts**

STANDBY mode can be exited by asserting input  $\overline{\text{NMI}}$ . The STANDBY mode may also exit by asserting  $\overline{\text{INT0}}$ .  $\overline{\text{INT1}}$  or  $\overline{\text{INT2}}$ , depending on the conditions specified in the following paragraphs.

$\overline{\text{INT0}}$  wake-up requires assertion throughout duration of clock stabilization time (2<sup>17</sup> clocks).

If exit conditions are met, the internal counter provides time for the crystal oscillator to stabilize, before the internal clocking and the system clock output within the Z8S180/Z8L180-class processors resume.

• Exit with Non-Maskable Interrupts

If  $\overline{\text{NMI}}$  is asserted, the CPU begins a normal NMI interrupt acknowledge sequence after clocking resumes.

• Exit with External Maskable Interrupts

If an External Maskable Interrupt input is asserted, the CPU responds according to the status of the Global Interrupt Enable Flag IEF1 (determined by the ITE1 bit) and the settings of the corresponding interrupt enable bit in the Interrupt/Trap Control Register (ITC: I/O Address = 34H).

If an interrupt source is disabled in the ITC, asserting the corresponding interrupt input does not cause the Z8S180/Z8L180-class processors to exit STANDBY mode. This condition is true regardless of the state of the Global Interrupt Enable Flag IEF1.

48

|      |                                     |          | A        | ldress |      |

|------|-------------------------------------|----------|----------|--------|------|

|      | Register                            | Mnemonic | Binary   | Hex    | Page |

| ASCI | ASCI Control Register A Ch 0        | CNTLA0   | XX000000 | 00H    | 125  |

|      | ASCI Control Register A Ch 1        | CNTLA1   | XX000001 | 01H    | 128  |

|      | ASCI Control Register B Ch 0        | CNTLB0   | XX000010 | 02H    | 132  |

|      | ASCI Control Register B Ch 1        | CNTLB1   | XX000011 | 03H    | 132  |

|      | ASCI Status Register Ch 0           | STAT0    | XX000100 | 04H    | 120  |

|      | ASCI Status Register Ch 1           | STAT1    | XX000101 | 05H    | 123  |

|      | ASCI Transmit Data Register Ch 0    | TDR0     | XX000110 | 06H    | 118  |

|      | ASCI Transmit Data Register Ch 1    | TDR1     | XX000111 | 07H    | 118  |

|      | ASCI Receive Data Register Ch 0     | RDR0     | XX001000 | 08H    | 119  |

|      | ASCI Receive Data Register Ch 1     | RDR1     | XX001001 | 09H    | 119  |

|      | ASCI0 Extension Control Register 0  | ASEXT0   | XX010010 | 12H    | 135  |

|      | ASCI1 Extension Control Register 1  | ASEXT1   | XX010011 | 13H    | 136  |

|      | ASCI0 Time Constant Low             | ASTCOL   | XX011010 | 1AH    | 137  |

|      | ASCI0 Time Constant High            | ASTC0H   | XX001011 | 1BH    | 137  |

|      | ASCI1 Time Constant Low             | ASCT1L   | XX001100 | 1CH    | 138  |

|      | ASCI1 Time Constant High            | ASCT1H   | XX001101 | 1DH    | 138  |

| CSI0 | CSI0 Control Register               | CNTR     | XX001010 | 0AH    | 147  |

|      | CSI0 Transmit/Receive Data Register | TRD      | XX1011   | 0BH    | 149  |

#### Table 7. I/O Address Map (Z8S180/Z8L180-Class Processors Only)

56

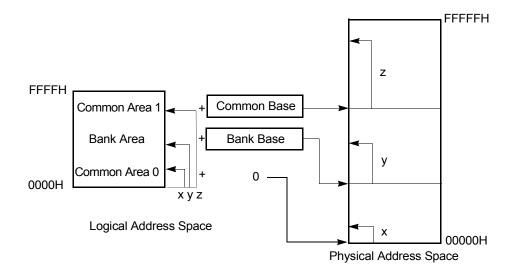

Figure 24. Physical Address Transition

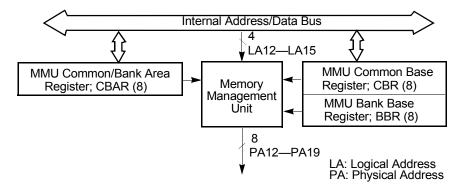

#### **MMU Block Diagram**

The MMU block diagram is depicted in Figure 25. The MMU translates internal 16-bit logical addresses to external 20-bit physical addresses.

Figure 25. MMU Block Diagram

Table 13.Channel 0 Source

| SM1 | SM0 | Memory/I/O | Address Increment/Decrement |

|-----|-----|------------|-----------------------------|

| 0   | 0   | Memory     | + 1                         |

| 0   | 1   | Memory     | -1                          |

| 1   | 0   | Memory     | fixed                       |

| 1   | 1   | I/O        | fixed                       |

Table 14 describes all DMA TRANSFER mode combinations of DM0 DM1, SM0 SM1. Because I/O to/from I/O transfers are not implemented, 12 combinations are available.

Table 14.

Transfer Mode Combinations

| DM1 | DM0 | SM1 | SM0 | Transfer Mode     | Increment/Decrement |

|-----|-----|-----|-----|-------------------|---------------------|

| 0   | 0   | 0   | 0   | Memory to Memory  | SAR0+1, DAR0+1      |

| 0   | 0   | 0   | 1   | Memory to Memory  | SAR0-1, DAR0+1      |

| 0   | 0   | 1   | 0   | Memory* to Memory | SAR0 fixed, DAR0+ 1 |

| 0   | 0   | 1   | 1   | I/O to Memory     | SAR0 fixed DAR0+1   |

| 0   | 1   | 0   | 0   | Memory to Memory  | SAR0+1, DAR0-1      |

| 0   | 1   | 0   | 1   | Memory to Memory  | SAR0-1,DAR0-1       |

| 0   | 1   | 1   | 0   | Memory to Memory  | SAR0 fixed, DAR0-1  |

| 0   | 1   | 1   | 1   | I/O to Memory     | SAR0 fixed. DAR0-1  |

| 1   | 0   | 0   | 0   | Memory to Memory* | SAR0+ 1, DAR0 fixed |

| 1   | 0   | 0   | 1   | Memory to Memory* | SAR0-1, DAR0 fixed  |

| 1   | 0   | 1   | 0   | Reserved          |                     |

| 1   | 0   | 1   | 1   | Reserved          |                     |

112

- 4. Specify whether  $\overline{\text{DREQ1}}$  is level- or edge- sense in the DMS1 bit in DCNTL.

- 5. Enable or disable DMA termination interrupt with the DIE1 bit in DSTAT.

- 6. Program DE1 = 1 (with  $\overline{DWE1} = 0$  in the same access) in DSTAT and the DMA operation with the external I/O device begins using the external  $\overline{DREQ1}$  input and  $\overline{TEND1}$  output.

#### **DMA Bus Timing**

When memory (and memory mapped I/O) is specified as a source or destination, MREQ goes Low during the memory access. When I/O is specified as a source or destination, IORQ goes Low during the I/O access.

When I/O (and memory mapped I/O) is specified as a source or destination, the DMA timing is controlled by the external  $\overline{\text{DREQ}}$  input and the  $\overline{\text{TEND}}$  output indicates DMA termination

For I/O accesses, one Wait State is automatically inserted. Additional Wait States can be inserted by programming the on-chip wait state generator or using the external WAIT input.

>

**Note:** For memory mapped I/O accesses, this automatic I/O Wait State is not inserted.

For memory to memory transfers (channel 0 only), the external  $\overline{DREQ0}$  input is ignored. Automatic DMA timing is programmed as either BURST or CYCLE STEAL.

When a DMA memory address carry/borrow between bits A15 and A16 of the address bus occurs (crossing 64KB boundaries), the minimum bus

123

#### ASCI Control Register A0, 1 (CNTLA0, 1)

Each ASCI channel Control Register A configures the major operating modes such as receiver/transmitter enable and disable, data format, and multiprocessor communication mode.

ASCI Status Register 1 (STAT1: 05H)

| Bit           | 7           | 6           | 5          | 4          | 3        | 2     | 1    | 0   |  |  |  |  |  |

|---------------|-------------|-------------|------------|------------|----------|-------|------|-----|--|--|--|--|--|

| Bit/Field     | RDRF        | OVRN        | PE         | FE         | RIE      | CTS1E | TDRE | TIE |  |  |  |  |  |

| R/W           | R           | R           | R          | R          | R/W      | R/W   | R    | R/W |  |  |  |  |  |

| Reset         |             |             |            |            |          |       |      |     |  |  |  |  |  |

| Note: R = Rea | ad $W = Wr$ | ite X = Ind | eterminate | ? = Not Ap | plicable |       |      |     |  |  |  |  |  |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7               | RDRF      | R   |       | <b>Receive Data Register Full</b> — RDRF is set to 1 when an incoming data byte is loaded into RDR. Note that if a framing or parity error occurs, RDRF is still set and the receive data (which generated the error) is still loaded into RDR. RDRF is cleared to 0 by reading RDR, when the DCD0 input is High, in IOSTOP mode, and during RESET. |

| 6               | OVRN      | R   |       | <b>Overrun Error</b> — OVRN is set to 1 when RDR is full<br>and RSR becomes full. OVRN is cleared to 0 when the<br>EFR bit (Error Flag Reset) of CNTLA is written to 0,<br>when DCD0 is High, in IOSTOP mode, and during<br>RESET.                                                                                                                  |

| 5               | PE        | R   |       | <b>Parity Error</b> — PE is set to 1 when a parity error is detected on an incoming data byte and ASCI parity detection is enabled (the MOD1 bit of CNTLA is set to 1). PE is cleared to 0 when the EFR bit (Error Flag Reset) of CNTLA is written to 0, when DCD0 is High, in IOSTOP mode, and during RESET.                                       |

157

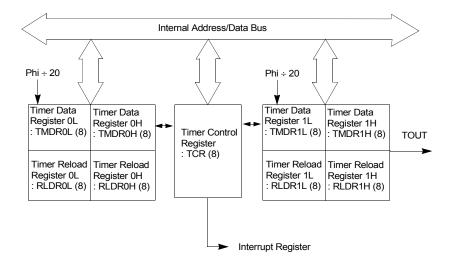

control register. The PRT input clock for both channels is equal to the system clock divided by 20.

Figure 63. PRT Block Diagram

# **PRT Register Description**

Timer Data Register (TMDR: I/O Address - CH0: 0CH, 0DH; CH1: 15H, 14H). PRT0 and PRT1 each contain 16-bit timer Data Registers (TMDR). TMDR0 and TMDR1 are each accessed as low and high byte registers (TMDR0H, TMDR0L and TMDR1H, TMDR1L). During RESET, TMDR0 and TMDR1 are set to FFFFH.

TMDR is decremented once every twenty clocks. When TMDR counts down to 0, it is automatically reloaded with the value contained in the Reload Register (RLDR).

TMDR is read and written by software using the following procedures. The read procedure uses a PRT internal temporary storage register to

178

# **Stack Pointer (SP)**

The Stack Pointer (SP) contains the memory address based LIFO stack. SP is cleared to 0000H during reset.

### **Program Counter (PC)**

The Program Counter (PC) contains the address of the instruction to be executed and is automatically updated after each instruction fetch. PC is cleared to 0000H during reset.

# Flag Register (F)

The Flag Register stores the logical state reflecting the results of instruction execution. The contents of the Flag Register are used to control program flow and instruction operation.

| Bit        | 7         | 6          | 5          | 4          | 3        | 2   | 1   | 0   |

|------------|-----------|------------|------------|------------|----------|-----|-----|-----|

| Bit/Field  | S         | Z          | Not Used   | Н          | Not Used | P/V | Ν   | С   |

| R/W        | R/W       | R/W        | ?          | R/W        | ?        | R/W | R/W | R/W |

| Reset      | 0         | 0          | ?          | 0          | ?        | 0   | 0   | 0   |

| R = Read V | W = Write | X = Indete | erminate ? | e = Not Ap | plicable |     |     |     |

Flag Register

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                        |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7               | S         | R/W | 0     | <b>Sign.</b> S stores the state of the most significant bit (bit 7) of the result. This is useful for operations with signed numbers in which values with bit $7 = 1$ are interpreted as negative. |

186

# **Z80180 DC CHARACTERISTICS**

$V_{CC}$  = 5V ± 10%,  $V_{SS}$  = OV, Ta = 0° to +70°C, unless otherwise noted.)

Table 28. Z80180 DC Characteristics

| Symbol          | Item                                                      | Condition                            | Minimum                     | Typical        | Maximum                                | Unit           |

|-----------------|-----------------------------------------------------------|--------------------------------------|-----------------------------|----------------|----------------------------------------|----------------|

| VIH1            | Input High Voltage<br>RESET, EXTAL NMI                    |                                      | V <sub>CC</sub> –0.6        | _              | V <sub>CC</sub> +0.3                   | V              |

| VIH2            | Input High Voltage<br>except RESET, EXTAL<br>NMI          |                                      | 2.0                         |                | V <sub>CC</sub> +0.3                   | V              |

| VIL1            | Input Low Voltage<br>RESET, EXTAL NMI                     |                                      | -0.3                        |                | 0.6                                    | V              |

| VIL2            | Input Low Voltage<br>except RESET, EXTAL<br>NMI           |                                      | -0.3                        |                | 0.8<br>Standard<br>7 TL <sub>VIL</sub> | V              |

| VOH             | Output High Voltage<br>all outputs                        | IOH = -200 μA<br>IOH = -20 μA        | 2.4<br>V <sub>CC</sub> –1.2 | _              | -<br>-                                 | V<br>V         |

| VOL             | Output Low Voltage<br>all outputs                         | IOL = 2.2  mA                        | _                           | _              | 0.45                                   | V              |

| I <sub>IL</sub> | Input Leakage Current<br>all inputs except XTAL,<br>EXTAL | $V_{IN} = 0.5 \sim V_{CC} - 0.5$     | -                           | _              | 1.0                                    | μA             |

| ITL             | Three-State Leakage<br>Current                            |                                      | _                           | _              | 1.0                                    | μA             |

| ICC             | Power Dissipation*<br>(Normal Operation)                  | f = 6 MHz<br>f = 8 MHz<br>f = 33 MHz | -<br>-<br>-                 | 15<br>20<br>25 | 40<br>50<br>60                         | mA<br>mA<br>mA |

| Symbol | Item                                                     | Condition                                    | Minimum                     | Typical        | Maximum        | Unit   |

|--------|----------------------------------------------------------|----------------------------------------------|-----------------------------|----------------|----------------|--------|

| VOH1   | Output High Voltage<br>All outputs                       | IOH = -200 μA<br>IOH = -20 μA                | 2.4<br>V <sub>CC</sub> -1.2 | _              | -              | V<br>V |

| VOH2   | Output High Voltage<br>Output High Phi                   | IOH = -200 μA                                | V <sub>CC</sub> -0.6        |                |                |        |

| VOL1   | Output Low Voltage<br>All outputs                        | IOL = 2.2  mA                                | _                           | _              | 0.45           | V      |

| VOL2   | Output Low Voltage<br>Output Low Phi                     | IOL = 2.2  mA                                | _                           | _              | 0.45           | V      |

| IIL    | Input Leakage Current<br>all inputs except XTAL,<br>ETAL | VIN = 0.5 ~ VCC -0.5                         | -                           | _              | 1.0            | μA     |

| ITL    | Three-State Leakage<br>Current                           | $VIN = 0.5 \sim VCC - 0.5$                   | _                           | _              | 1.0            | μA     |

| ICC    | Power Dissipation*<br>(Normal Operation)                 | f = 10  MHz<br>f = 20  MHz<br>f = 33  MHz    | -                           | 15<br>30<br>60 | -<br>50<br>100 | mA     |

|        | Power Dissipation*<br>(SYSTEM STOP<br>Mode)              | f = 10 MHz<br>f = 20 MHz<br>f = 33 MHz       | -                           | 1.5<br>3<br>5  | -<br>6<br>9    | mA     |

|        | Power Dissipation*<br>(IDLE Mode)                        | f = 20 MHz<br>f = 33 MHz                     | _                           | 4              | 10             | mA     |

|        | Power Dissipation*<br>(STANDBY Mode)                     | External Oscillator,<br>Internal Clock Stops | _                           | 5              | 10             | μA     |

| СР     | Pin Capacitance                                          | VIN = 0V,<br>f = 1MHz<br>TA = 25°C           | _                           | —              | 12             | pF     |

### Table 29. Z8S180 DC Characteristics (Continued)

UM005003-0703

194

|     |                   | Operation                                                                      | <b>Z8S</b> 1 | 180—20 | Z8S |     |      |  |

|-----|-------------------|--------------------------------------------------------------------------------|--------------|--------|-----|-----|------|--|

|     |                   |                                                                                | Ν            | ЛНz    | I   | MHz |      |  |

| No. | Symbol            | Item                                                                           | Min          | Max    | Min | Max | Unit |  |

| 12  | t <sub>MED2</sub> | PHI Fall to MREQ Rise Delay                                                    |              | 25     | _   | 15  | ns   |  |

| 13  | t <sub>RDD2</sub> | PHI Fall to RD Rise Delay                                                      |              | 25     |     | 15  | ns   |  |

| 14  | t <sub>M1D2</sub> | PHI Rise to $\overline{M1}$ Rise Delay                                         |              | 40     |     | 15  | ns   |  |

| 15  | t <sub>DRS</sub>  | Data Read Set-up Time                                                          | 10           |        | 5   |     | ns   |  |

| 16  | t <sub>DRH</sub>  | Data Read Hold Time                                                            | 0            |        | 0   |     | ns   |  |

| 17  | t <sub>STD1</sub> | PHI Fall to ST Fall Delay                                                      |              | 30     |     | 15  | ns   |  |

| 18  | t <sub>STD2</sub> | PHI Fall to ST Rise Delay                                                      |              | 30     |     | 15  | ns   |  |

| 19  | t <sub>WS</sub>   | WAIT Set-up Time to PHI Fall                                                   | 15           |        | 10  |     | ns   |  |

| 20  | t <sub>WH</sub>   | WAIT Hold Time from PHI Fall                                                   | 10           |        | 5   |     | ns   |  |

| 21  | t <sub>WDZ</sub>  | PHI Rise to Data Float Delay                                                   |              | 35     |     | 20  | ns   |  |

| 22  | t <sub>WRD1</sub> | PHI Rise to WR Fall Delay                                                      |              | 25     |     | 15  | ns   |  |

| 23  | t <sub>WDD</sub>  | PHI Fall to Write Data Delay Time                                              |              | 25     |     | 15  | ns   |  |

| 24  | t <sub>WDS</sub>  | Write Data Set-up Time to WR Fall                                              | 10           |        | 10  |     | ns   |  |

| 25  | t <sub>WRD2</sub> | PHI Fall to WR Rise Delay                                                      |              | 25     |     | 15  | ns   |  |

| 26  | t <sub>WRP</sub>  | WR Pulse Width (Memory Write Cycle)                                            | 80           |        | 45  |     | ns   |  |

| 26a |                   | WR Pulse Width (I/O Write Cycle)                                               | 150          |        | 70  |     | ns   |  |

| 27  | t <sub>WDH</sub>  | Write Data Hold Time from $\overline{WR}$ Rise                                 | 10           |        | 5   |     | ns   |  |

| 28  | t <sub>IOD1</sub> | PHI Fall to $\overline{\text{IORQ}}$ Fall Delay $\overline{\text{IOC}}$<br>= 1 |              | 25     |     | 15  | ns   |  |

|     |                   | PHI Rise to $\overline{\text{IORQ}}$ Fall Delay $\overline{\text{IOC}} = 0$    | —            | 25     |     | 15  | -    |  |

| 29  | t <sub>IOD2</sub> | PHI Fall to IORQ Rise Delay                                                    |              | 25     |     | 15  | ns   |  |

| 30  | t <sub>IOD3</sub> | $\overline{\text{M1}}$ Fall to $\overline{\text{IORQ}}$ Fall Delay             | 125          |        | 80  | _   | ns   |  |

Table 31.Z8S180 AC Characteristics (Continued)  $V_{DD} = 5V \pm 10\%$  or $V_{DD} = 3.3V \pm 10\%$ ; 33-MHz Characteristics Apply Only to 5VOperation

| Operation<br>Name | Mnemonics                                                    | Op Code    |            |     |     |     |      |     |     |       | Flags       |                                                                                                                         |   |             |   |     |                  |   |

|-------------------|--------------------------------------------------------------|------------|------------|-----|-----|-----|------|-----|-----|-------|-------------|-------------------------------------------------------------------------------------------------------------------------|---|-------------|---|-----|------------------|---|

|                   |                                                              |            | Addressing |     |     |     |      |     |     |       |             | 7                                                                                                                       | 6 | 4           | 2 | 1   | 0                |   |

|                   |                                                              |            | Immed      | Ext | Ind | Reg | Regl | Imp | Rel | Bytes | States      | Operation                                                                                                               |   | z           | н | P/V | N                | c |

|                   | OTIMR**                                                      | 11 101 101 |            |     |     |     | S    |     | D   | 2     | 16 (Br ≠ 0) |                                                                                                                         | R | s           | R | s   | ↑                | ł |

|                   |                                                              | 10 010 011 |            |     |     |     |      |     |     |       | 14 (Br = 0) | $\begin{array}{c} HL_{R} + 1 \rightarrow HL_{R} \\ Q \qquad Cr + 1 \rightarrow Cr \\ Br - 1 \rightarrow Br \end{array}$ |   |             |   |     |                  |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Repeat Q until<br>Br = 0                                                                                                |   |             |   |     |                  |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Br = 0<br>Cr→A0~A7                                                                                                      |   |             |   |     |                  |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | 00→A8~A16                                                                                                               |   | (5)         |   |     | (6)              |   |

|                   | OUTD                                                         | 11 101 101 |            |     |     |     |      | s   | D   | 2     | 12          | (HL) <sub>M</sub> →(BC) <sub>1</sub>                                                                                    | х | (- <i>)</i> | х | х   | (- <i>)</i><br>↑ | ; |

|                   |                                                              | 10 101 011 |            |     |     |     |      |     |     |       |             | HL <sub>R</sub> -1→HL <sub>R</sub>                                                                                      |   |             |   |     |                  |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Br-1→Br                                                                                                                 |   |             |   |     |                  |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Cr→A0~A7                                                                                                                |   |             |   |     |                  |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Br→A8~A16                                                                                                               |   |             |   |     |                  |   |

| (6) N = 1:        | : Br-1 = 0<br>: Br-1 ≠ 0<br>MSB of Data =<br>: MSB of Data = |            |            |     |     |     |      |     |     |       |             |                                                                                                                         |   |             |   |     |                  |   |

#### Table 46. I/O Instructions (Continued)

|            |       | Machine |                         |

|------------|-------|---------|-------------------------|

| MNEMONICS  | Bytes | Cycles  | States                  |

|            | 3     | 3       | 9                       |

|            |       |         | (If f is true)          |

| JP (HL)    | 1     | 1       | 3                       |

| JP (IX)    | 2     | 2       | 6                       |

| JP (IY)    | 2     | 2       | 6                       |

| JP mn      | 3     | 3       | 9                       |

| JR j       | 2     | 4       | 8                       |

| JR C,j     | 2     | 2       | 6                       |

|            |       |         | (If condition is false) |

|            | 2     | 4       | 8                       |

|            |       |         | (If condition is true)  |

| JR NC,j    | 2     | 2       | 6                       |

|            |       |         | (if condition is false) |

|            | 2     | 4       | 8                       |

|            |       |         | (If condition is true)  |

| JR Z,j     | 2     | 2       | 6                       |

|            |       |         | (If condition is false) |

|            | 2     | 4       | 8                       |

|            |       |         | If condition is true)   |

| JR NZ,j    | 2     | 2       | 6                       |

|            |       |         | (If condition is false) |

|            | 2     | 4       | 8                       |

|            |       |         | (If condition is true)  |

| LD A, (BC) | 1     | 2       | 6                       |

| LD A, (DE) | 1     | 2       | 6                       |

| LD A,I     | 2     | 2       | 6                       |

| LD A, (mn) | 3     | 4       | 12                      |

| LD A,R     | 2     | 2       | 6                       |

| LD (BC),A  | 1     | 3       | 7                       |

| LDD        | 2     | 4       | 12                      |

#### 293

# **I/O Registers**

# **INTERNAL I/O REGISTERS**

By programming IOA7 and IOA6 as the I/O control register, internal I/O register addresses are relocatable within ranges from 0000H to 00FFH in the I/O address space.

| Register                              | Mnemoni | Remarks |   |                                                                                                           |                                                                                                                                                                                     |          |                                |                   |                        |           |             |                  |

|---------------------------------------|---------|---------|---|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------|-------------------|------------------------|-----------|-------------|------------------|

| ASCI Control Register A<br>Channel 0: | CNTLA0  | 0       | 0 | bit                                                                                                       | MPE                                                                                                                                                                                 | RE       | TE                             | RTS0              | MPBR/<br>EFR           | MOD2      | MOD1        | MOD0             |

|                                       |         |         |   | during RESET<br>R/W                                                                                       | 0<br>R/W                                                                                                                                                                            | 0<br>R/W | 0<br>R/W                       | l<br>R/W          | invalid<br>R/W         | 0<br>R/W  | 0<br>R/W    | 0<br>R/W         |

|                                       |         |         |   |                                                                                                           |                                                                                                                                                                                     |          | Tr<br>Receive En<br>cessor Ena | ansmit En<br>able | Error<br>uest to Se    | r Flåg Re | or Bit Rec  | ODE Select       |

| ASCI Control Register A<br>Channel 1: | CNTLA1  | 0       | 1 | bit<br>during RESET                                                                                       | MPE<br>0                                                                                                                                                                            | RE<br>0  | TE<br>0                        | CKA1E             | MPBR<br>EFR<br>invalid | 0 MOD     | 2 MODI<br>0 | MOD0             |

|                                       |         |         |   | R/W R/W R/W R/W R/W R/W R/W R/W<br>Multi Proces<br>Error Flag R<br>CKA1 Disable<br>Multi Processor Enable |                                                                                                                                                                                     |          |                                |                   |                        |           | ssor Bit R  | R/W<br>MODE Seld |

|                                       |         |         |   | 0 0 1 5<br>0 1 0 5<br>0 1 1 5<br>1 0 0 5<br>1 0 1 5<br>1 0 1 5<br>1 1 0 5                                 | 0 Start + 7 bit Data + 1 Stop<br>1 Start + 7 bit Data + 2 Stop<br>0 Start + 7 bit Data + Parity + 1 Stop<br>1 Start + 7 bit Data + Parity + 2 Stop<br>0 Start + 8 bit Data + 1 Stop |          |                                |                   |                        |           |             |                  |

#### Table 57. Internal I/O Registers

295

| Register               | Mnemonics | Address |                           |                                                                                                                            |                   | Rer       | nark              | S         |            |                          |                                |                                                     |

|------------------------|-----------|---------|---------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|-------------------|-----------|------------|--------------------------|--------------------------------|-----------------------------------------------------|

| ASCI Status Channel 0: | STAT0     | 0 4     |                           |                                                                                                                            | 1                 |           | T                 | 1         | 1          |                          | T                              |                                                     |

|                        |           |         | bit                       | RDRF                                                                                                                       | OVRN              | PE        | FE                | RIE       | DCD0       | TDRE                     | TIE                            | _                                                   |

|                        |           |         | during RESET              | 0                                                                                                                          | 0                 | 0         | 0                 | invalid   | *          | **                       | 0                              |                                                     |

|                        |           |         | R/W                       | R                                                                                                                          | R                 | R         | R                 | R/W       | R          | R                        | R/W                            | ]                                                   |

|                        |           |         |                           |                                                                                                                            |                   | errun Err | arity Error<br>or | raming Er | teceive In | Data Carri<br>terrupt En | ransmit D<br>er Detect<br>able | nit Interrupt Enable<br>hata Register Empty<br>TDRE |

| ASCI Status Channel 1: | STAT1     | 0 5     | * DCD <sub>0</sub> : Depe | Receive Data Register Full $\frac{1}{L}$<br>* $\overline{DCD_0}$ : Depending on the condition of $\overline{DCD_0}$ Pin. H |                   |           |                   |           |            |                          |                                | 0                                                   |

|                        |           |         |                           | RDRF                                                                                                                       | OVRN              | PE        | FE                | RIE       | CTS1E      | TDRE                     | TIE                            | T                                                   |

|                        |           |         | bit<br>during RESET       | 0                                                                                                                          | 0                 | 0         | 0                 | 0         | 0          | 1                        | 0                              | 1                                                   |

|                        |           |         | R/W                       | R                                                                                                                          | R                 | R         | R                 | R/W       | R          | R                        | R/W                            |                                                     |

|                        |           |         |                           | R                                                                                                                          | -Ov<br>Leceive Da | errun Err | arity Error<br>or | raming Er | teceive In | TTSI Enal                | ransmit D<br>ble               | -<br>iit Interrupt Enable<br>ata Register Empty     |

Table 57.

Internal I/O Registers (Continued)

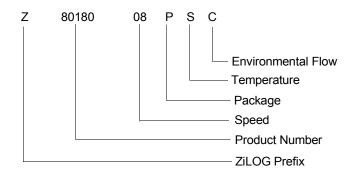

# **ORDERING INFORMATION**

# Codes

- Package

P = Plastic Dip

V = Plastic Chip Carrier

F = Quad Flat Pack

- Temperature  $S = 0^{\circ}C \text{ to } +70^{\circ}C$  $E = -40^{\circ}C \text{ to } 100^{\circ}C$

- Speed 06 = 6 MHz 08 = 8 MHz 10 = 10 MHz

•

- Environmental C = Plastic Standard

- Example Z8018008PSC is an 80180 8 MHz, Plastic DIP, 0°C to 70°C, Plastic Standard Flow.