Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 8MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 64-DIP (0.750", 19.05mm)                               |

| Supplier Device Package         | 64-DIP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018008psg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8018x Family MPU User Manual

viv

# List of Tables

| Z80180, Z8S180, Z8 | 8L180 MPU Operation                                   | 1   |

|--------------------|-------------------------------------------------------|-----|

| Table 1.           | Status Summary                                        | 10  |

| Table 2.           | Multiplexed Pin Descriptions                          | 12  |

| Table 3.           | Memory Wait States                                    | 29  |

| Table 4.           | Wait State Insertion                                  | 30  |

| Table 5.           | Power-Down Modes (Z8S180/Z8L180-Class Processor Only) | 37  |

| Table 6.           | I/O Address Map for Z80180-Class Processors Only.     | 44  |

| Table 7.           | I/O Address Map (Z8S180/Z8L180-Class Processors Only) | 48  |

| Table 8.           | State of IEF1 and IEF2                                | 69  |

| Table 9.           | Vector Table                                          | 82  |

| Table 10.          | RETI Control Signal States                            | 85  |

| Table 11.          | DRAM Refresh Intervals                                | 89  |

| Table 12.          | Channel 0 Destination                                 | 98  |

| Table 13.          | Channel 0 Source                                      | 99  |

| Table 14.          | Transfer Mode Combinations                            | 99  |

| Table 15.          | Channel 1 Transfer Mode                               | 102 |

| Table 16.          | DMA Transfer Request                                  | 110 |

| Table 17.          | Data Formats                                          | 131 |

| Table 18.          | Divide Ratio                                          | 134 |

| Table 19.          | ASCI Baud Rate Selection                              | 142 |

| Table 20.          | Clock Mode Bit Values                                 | 144 |

| Table 21.          | 2^ss Values                                           | 145 |

| Table 22           | CSI/O Baud Rate Selection                             | 150 |

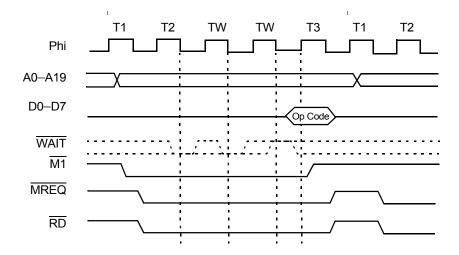

Figure 10. Op Code Fetch (with Wait State) Timing Diagram

#### **Operand and Data Read/Write Timing**

The instruction operand and data read/write timing differs from Op Code fetch timing in two ways:

- The  $\overline{M1}$  output is held inactive

- The read cycle timing is relaxed by one-half clock cycle because data is latched at the falling edge of T3

Instruction operands include immediate data, displacement, and extended addresses, and contain the same timing as memory data reads.

During memory write cycles the  $\overline{MREQ}$  signal goes active in the second half of T1. At the end of T1, the data bus is driven with the write data.

At the start of T2, the  $\overline{WR}$  signal is asserted Low enabling the memory.  $\overline{MREQ}$  and  $\overline{WR}$  go inactive in the second half of T3 followed by disabling of the write data on the data bus.

Table 6. I/O Address Map for Z80180-Class Processors Only (Continued)

|        |                        |          | Ac         | ddress    |      |

|--------|------------------------|----------|------------|-----------|------|

|        | Register               | Mnemonic | Binary     | Hex       | Page |

| Timer  | Data Register Ch 0 L   | TMDR0L   | XX001100   | 0СН       | 159  |

|        | Data Register Ch 0 H   | TMDR0H   | XX001101   | 0DH       | 159  |

|        | Reload Register Ch 0 L | RLDR0L   | XX001110   | 0EH       | 159  |

|        | Reload Register Ch 0 H | RLDR0H   | XX001111   | 0FH       | 159  |

|        | Timer Control Register | TCR      | XX010000   | 10H       | 161  |

|        | Reserved               |          | XX010001   | 11H       |      |

|        |                        |          | <b>\$</b>  | <b>\$</b> |      |

|        |                        |          | XX010011   | 13H       |      |

|        | Data Register Ch 1 L   | TMDR1L   | XX010100   | 14H       | 160  |

|        | Data Register Ch 1 H   | TMDR1H   | XX010101   | 15H       | 160  |

|        | Reload Register Ch 1 L | RLDR1L   | XX010110   | 16H       | 159  |

|        | Reload Register Ch 1 H | RLDR1H   | XX010111   | 17H       | 159  |

| Others | Free Running Counter   | FRC      | XX011000   | 18H       | 172  |

|        | Reserved               |          | XX011001   | 19H       |      |

|        |                        |          | $\uparrow$ | <b>\$</b> |      |

|        |                        |          | XX011111   | 1FH       |      |

# CPU Control Register (CCR: 1FH) (Z8S180/L180-Class Processors Only)

| Bit       | 7      | 6      | 5     | 4     | 3      | 2    | 1     | 0     |

|-----------|--------|--------|-------|-------|--------|------|-------|-------|

| Bit/Field | Clock  | STAND  | BREXT | LNPHI | STAND  | LNIO | LNCPU | LNAD/ |

|           | Divide | BY/    |       |       | BY/    |      | CTL   | DATA  |

|           |        | IDLE   |       |       | IDLE   |      |       |       |

|           |        | Enable |       |       | Enable |      |       |       |

| R/W       | R/W    | R/W    | R/W   | R/W   | R/W    | R/W  | R/W   | R/W   |

| Reset     | 0      | 0      | 0     | 0     | 0      | 0    | 0     | 0     |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

| Bit<br>Position | Bit/Field  | R/W | Value | Description                              |

|-----------------|------------|-----|-------|------------------------------------------|

| 7               | Clock      | R/W | 0     | XTAL/2                                   |

|                 | Divide     |     | 1     | XTAL/1                                   |

| 6               | STANDBY    | R/W |       | In conjunction with Bit 3                |

|                 | /IDLE Mode |     | 00    | No STANDBY                               |

|                 |            |     | 01    | IDLE after SLEEP                         |

|                 |            |     | 10    | STANDBY after SLEEP                      |

|                 |            |     | 11    | STANDBY after SLEEP 64 Cycle Exit (Quick |

|                 |            |     |       | Recovery)                                |

| 5               | BREXT      | R/W | 0     | Ignore BUSREQ in STANDBY/IDLE            |

|                 |            |     | 1     | STANDBY/IDLE exit on BUSREQ              |

| 4               | LNPHI      | R/W | 0     | Standard Drive                           |

|                 |            |     | 1     | 33% Drive on EXTPHI Clock                |

| 3               | STANDBY    | R/W |       | In conjunction with Bit 6                |

|                 | /IDLE Mode |     | 00    | No STANDBY                               |

|                 |            |     | 01    | IDLE after SLEEP                         |

|                 |            |     | 10    | STANDBY after SLEEP                      |

|                 |            |     | 11    | STANDBY after SLEEP 64 Cycle Exit (Quick |

|                 |            |     |       | Recovery)                                |

### Bits 5–3

Reserved. Must be 0.

### Bits 2-0

With DIM1, bit 1 of DCNTL, these bits control which request is presented to DMA channel 1, as described below:

| DIM1 | IAR18-16 | Request Routed to DMA Channel 1 |

|------|----------|---------------------------------|

| 0    | 000      | DREQ1                           |

| 0    | 001      | ASCI0 Tx                        |

| 0    | 010      | ASCI1 Tx                        |

| 0    | 011      | ext CKA0/DREQ0                  |

| 0    | 10X      | Reserved                        |

| 0    | 1X0      | Reserved                        |

| 0    | 111      | Reserved                        |

| 1    | 000      | ext DREQ1                       |

| 1    | 001      | ASCI0 Rx                        |

| 1    | 010      | ASCI1 Rx                        |

| 1    | 011      | ext CKA0/DREQ0                  |

| 1    | 10X      | Reserved                        |

| 1    | 1X0      | Reserved                        |

| 1    | 111      | Reserved                        |

# **DMA Operation**

This section discusses the three DMA operation modes for channel 0:

- Memory to/from memory

- Memory to/from I/O

- Memory to/from memory mapped I/O

112

cycle is extended to 4 clocks by automatic insertion of one internal Ti state.

#### **DMAC Channel Priority**

For simultaneous  $\overline{DREQ0}$  and  $\overline{DREQ1}$  requests, channel 0 has priority over channel 1. When channel 0 is performing a memory to/from memory transfer, channel 1 cannot operate until the channel 0 operation has terminated. If channel 1 is operating, channel 0 cannot operate until channel 1 releases control of the bus.

#### DMAC and BUSREQ, BUSACK

The BUSREQ and BUSACK inputs allow another bus master to take control of the Z8X180 bus. BUSREQ and BUSACK take priority over the on-chip DMAC and suspends DMAC operation. The DMAC releases the bus to the external bus master at the breakpoint of the DMAC memory or I/O access. Since a single byte DMAC transfer requires a read and a write cycle, it is possible for the DMAC to be suspended after the DMAC read, but before the DMAC write. Hence, when the external master releases the Z8X180 bus (BUSREQ High), the on-chip DMAC correctly continues the suspended DMA operation.

# Z8018x Family MPU User Manual

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                  |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | TIE       | R/W |       | <b>Transmit Interrupt Enable</b> — TIE must be set to 1 to enable ASCI transmit interrupt requests. If TIE is 1, an interrupt is requested when TDRE is 1. TIE is cleared to 0 during RESET. |

1 5 2

#### **CSI/O and RESET**

During RESET each bit in the CNTR is initialized as defined in the CNTR register description. CSI/O transmit and receive operations in progress are aborted during RESET. However, the contents of TRDR are not changed.

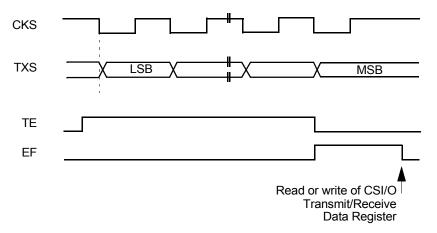

Figure 59. Transmit Timing Diagram-Internal Clock

**Table 23.** Timer Output Control

| TOC1 | TOC0 | OUTPUT    |                                                           |

|------|------|-----------|-----------------------------------------------------------|

| 0    | 0    | Inhibited | (A18/TOUT pin is selected as an address output function.) |

| 0    | 1    | Toggled   |                                                           |

| 1    | 0    | 0         | A18/TOUT pin is selected as a PRT1 output function!       |

| 1    | 1    | 1         |                                                           |

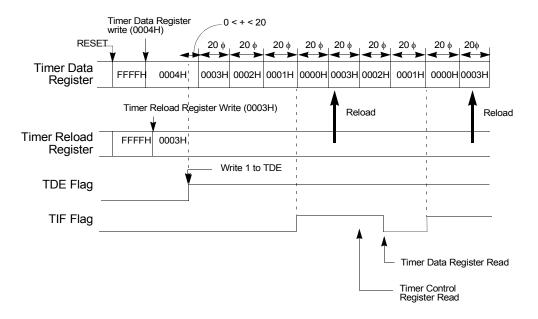

Figure 64 illustrates timer initialization, count down, and reload timing. Figure 65 depicts timer output (A18/TOUT) timing.

Figure 64. Timer Initialization, Count Down, and Reload Timing Diagram

122

# **Immediate (IMMED)**

The memory operands are contained within one or two bytes of the instruction, as depicted in Figure 79.

Figure 79. Immediate Addressing

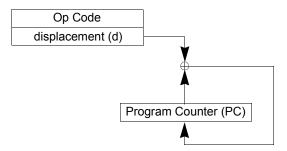

### Relative (REL)

Relative addressing mode is only used by the conditional and unconditional branch instructions (refer to Figure 80). The branch displacement (relative to the contents of the program counter) is contained in the instruction.

Figure 80. Relative Addressing

201

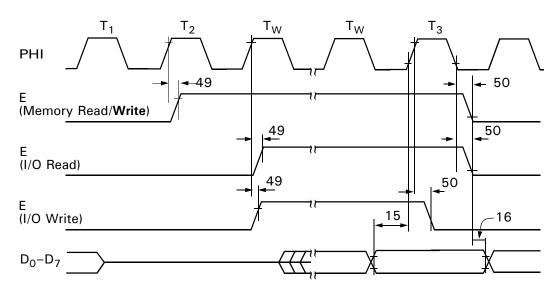

Figure 85. E Clock Timing (Memory R/W Cycle) (I/O R/W Cycle)

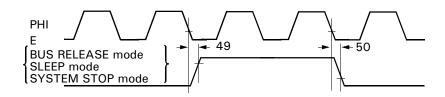

Figure 86. E Clock Timing (BUS RELEASE Mode, SLEEP Mode, and SYSTEM STOP Mode

Table 39. Rotate and Shift Instructions (Continued)

|                   |              |             |       |     |     |        |      |     |     |       |            |                   |            |            | F | lags |   |            |

|-------------------|--------------|-------------|-------|-----|-----|--------|------|-----|-----|-------|------------|-------------------|------------|------------|---|------|---|------------|

|                   |              |             |       |     | Add | Iressi | ng   |     |     |       |            |                   | 7          | 6          | 4 | 2    | 1 | 0          |

| Operation<br>Name | Mnemonics    | Op Code     | Immed | Ext | Ind | Reg    | Regi | lmp | Rel | Bytes | State<br>s | Operation         | s          | z          | н | P/V  | N | С          |

|                   |              | 11 001 011  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   |              | <d>&gt;</d> |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   | l          |

|                   |              | 00 001 110  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   | l          |

|                   | RRD          | 11 101 101  |       |     |     |        |      | S/D |     | 2     | 16         | <b>√</b>          | <b>↑</b>   | <b>↑</b>   | R | Р    | R | •          |

|                   |              | 01 100 111  |       |     |     |        |      |     |     |       |            | Ar                |            |            |   |      |   | l          |

|                   | SLA g        | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          | b7 b0             | <b>↑</b>   | $\uparrow$ | R | Р    | R | $\uparrow$ |

|                   |              | 00 100 g    |       |     |     |        |      |     |     |       |            | (HL) <sub>M</sub> |            |            |   |      |   |            |

|                   | SLA (HL)     | 11 001 011  |       |     |     |        | S/D  |     |     | 2     | 13         | b7 <b>b</b> 0     | <b>↑</b>   | $\uparrow$ | R | Р    | R | $\uparrow$ |

|                   |              | 00 100 110  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   | SLA (IX + d) | 11 011 101  |       |     | S/D |        |      |     |     | 4     | 19         |                   | <b>↑</b>   | $\uparrow$ | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011  |       |     |     |        |      |     |     |       |            | C b7 b0           |            |            |   |      |   |            |

|                   |              | <d></d>     |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   |              | 00 100 110  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   | SLA (IY + d) | 11 111 101  |       |     | S/D |        |      |     |     | 4     | 19         |                   | $\uparrow$ | <b>↑</b>   | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   |              | <d></d>     |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   |              | 00 100 110  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   | SRA g        | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          | _                 | <b>↑</b>   | $\uparrow$ | R | Р    | R | $\uparrow$ |

|                   |              | 00 101 g    |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   | SRA (HL)     | 11 001 011  |       |     |     |        | S/D  |     |     | 2     | 13         | b7 b0 C           | <b>↑</b>   | <b>↑</b>   | R | Р    | R | $\uparrow$ |

|                   |              | 00 101 110  |       |     |     |        |      |     |     |       |            | b/ b0 C           |            |            |   |      |   |            |

|                   | SRA (IX + d) | 11 011 101  |       |     | S/D |        |      |     |     | 4     | 19         |                   | <b>↑</b>   | <b>↑</b>   | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   |              | <d>&gt;</d> |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   |              | 00 101 110  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   |            |

|                   | SRA (IY + d) | 11 111 101  |       |     | S/D |        |      |     |     | 4     | 19         |                   | <b>↑</b>   | <b>↑</b>   | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011  |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   | H          |

|                   |              | <d>&gt;</d> |       |     |     |        |      |     |     |       |            |                   |            |            |   |      |   | H          |

|                   |              | 00 101 110  |       |     |     |        |      |     |     |       |            | <b>→</b>          |            |            |   |      |   |            |

|                   | SRL g        | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          | 0-                | <b>↑</b>   | <b>↑</b>   | R | Р    | R | $\uparrow$ |

|                   |              | 00 111 g    |       |     |     |        |      |     |     |       |            | b7 b0 C           |            |            |   |      |   |            |

# Z8018x Family MPU User Manual

245

| MATEMONICS | Destan | Machine | States |

|------------|--------|---------|--------|

| MNEMONICS  | Bytes  | Cycles  | States |

| SRL (IY+d) | 4      | 7       | 19     |

| SRL g      | 2      | 3       | 7      |

| SUB (HL)   | 1      | 2       | 6      |

| SUB (IX+d) | 3      | 6       | 14     |

| SUB (IY+d) | 3      | 6       | 14     |

| SUB m      | 2      | 2       | 6      |

| SUB g      | 1      | 2       | 4      |

| **TSTIO m  | 3      | 4       | 12     |

| **TST g    | 2      | 3       | 7      |

| TST m**    | 3      | 3       | 9      |

| TST (HL)** | 2      | 4       | 10     |

| XOR (HL)   | 1      | 2       | 6      |

| XOR (IX+d) | 3      | 6       | 14     |

| XOR (IY+d) | 3      | 6       | 14     |

| XOR m      | 2      | 2       | 6      |

| XOR g      | 1      | 2       | 4      |

# Op Code Map

Table 48. 1st Op Code Map Instruction Format: XX

|        |      |    | ww (L0 =     | ALL)  |                   |                  |         |        |        |         |       |       |       |       | L0 = 0~    | 7            |               |                 |    |

|--------|------|----|--------------|-------|-------------------|------------------|---------|--------|--------|---------|-------|-------|-------|-------|------------|--------------|---------------|-----------------|----|

|        |      |    | BC           | DE    | HL                | SP               |         |        |        |         |       |       |       |       | BC         | DE           | HL            | AF              | ZZ |

|        |      |    | g (LO = (    | )~7)  |                   |                  |         |        |        |         | 1     |       |       |       | NZ         | NC           | P0            | P               | f  |

|        |      |    | В            | D     | Н                 | (HL)             | В       | D      | Н      | (HL)    |       |       |       |       | 00H        | 10H          | 20H           | 30H             | v  |

|        | \    | НІ | 0000         | 0001  | 0010              | 0011             | 0100    | 0101   | 0110   | 0111    | 1000  | 1001  | 1010  | 1011  | 1100       | 1101         | 1110          | 1111            |    |

|        | LO   |    | 0            | 1     | 2                 | 3                | 4       | 5      | 6      | 7       | 8     | 9     | A     | В     | C          | D            | Е             | F               |    |

| В      | 0000 | 0  | N0P          | DJNZj | JR<br>NZ,j        | JR<br>NC,j       |         |        |        | note 1) |       |       |       |       | RET f      |              |               |                 | 0  |

| C      | 0001 | 1  | LD ww, t     | nn    |                   |                  | LD g, s | 3      |        |         | ADD   | SUB s | AND s | OR s  | POP zz     |              |               |                 | 1  |

| D      | 0010 | 2  | LD (ww)      | , A   | LD<br>(mn)<br>,HL | LD<br>(mn),<br>A |         |        |        |         | A,s   |       |       |       | JP f, mn   |              |               |                 | 2  |

| Е      | 0011 | 3  | INC ww       |       |                   | ı                |         |        |        |         |       |       |       |       | JP mn      | OUT<br>(m),A | EX(SP),<br>HL | DI              | 3  |

| Н      | 0100 | 4  | INC g        |       |                   | note1            |         |        |        |         |       |       |       |       | CALL f     | , mn         |               |                 | 4  |

| L      | 0101 | 5  | DEC g        |       |                   | note1            |         |        |        |         |       |       |       |       | PUSH z     | Z            |               |                 | 5  |

| (HL)   | 0110 | 6  | LD g,m       |       |                   | note1            | note2   |        |        | HALT    | note2 | note2 | note2 | note2 | ADD<br>A,m | SUB m        | AND m         | OR m            | 6  |

| A<br>B | 0111 | 7  | RLCA         | RLA   | DAA               | SCF              |         |        |        |         |       |       |       |       | RST v      |              |               |                 | 7  |

| ıl I   | 1000 | 8  | EXAF,A<br>F' | JR j  | JR Z,j            | JR C,j           |         |        |        |         |       |       |       |       | RET f      |              |               |                 | 8  |

| С      | 1001 | 9  | ADD HL       | , ww  |                   |                  | LD g, s | ;      |        |         | ADC   | SBC   | XOR s | CP s  | RET        | EXX          | JP(HL)        | LD<br>SP,<br>HL | 9  |

| D      | 1010 | A  | LD A,(w      | w)    | LD<br>HL,<br>(mn) | LD A,<br>(mn)    |         |        |        |         | A,s   | A,s   |       |       | JP f, mn   |              |               |                 | A  |

| Е      | 1011 | В  | DEC ww       |       |                   |                  |         |        |        |         |       |       |       |       | Table2     | IN A(m)      | EXDE,H<br>L   | EI              | В  |

| Н      | 1100 | С  | INC g        |       |                   |                  |         |        |        |         |       |       |       |       | CALL f     | , mn         | •             | •               | С  |

| L      | 1101 | D  | DEC g        |       |                   |                  |         |        |        |         |       |       |       |       | CALL<br>mn | note3        | Table3        | note3           | D  |

| (HL)   | 1110 | Е  | LD g,m       |       |                   |                  | note2   |        |        |         | note2 | note2 | note2 | note2 | ADC<br>A,m | SBC A,m      | XOR m         | CP m            | Е  |

|        |      | F  | RRCA         | RRA   | CPL               | CCF              |         |        |        |         |       |       |       |       | RST v      |              |               |                 |    |

| A      | 1111 | F  | KKCA         |       |                   |                  |         |        |        |         |       |       |       |       |            |              |               |                 |    |

| A      | 1111 | F  | 0            | 1     | 2                 | 3                | 4       | 5      | 6      | 7       | 8     | 9     | A     | В     | C          | D            | Е             | F               |    |

| A      | 1111 | F  |              |       | 2<br>L            | 3<br>A           | 4<br>C  | 5<br>E | 6<br>L | 7<br>A  | 8     | 9     | A     | В     | C<br>Z     | D<br>C       | E<br>PE       | F<br>M          | f  |

Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction               | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|---------------------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

|                           | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INIR<br>INDR<br>(If Br=0) | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| ,                         | мс3              | T1T2T3 | ВС                     | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

|                           | MC4              | T1T2T3 | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                           | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| JP mn                     | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                           | MC3              | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| JP f,mn                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| (if is false)             | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                           | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| JP f,mn<br>(If f is true) | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                           | MC3              | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| JP (HL)                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| JP (IX)                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| JP (IY)                   | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction               | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | M1 | HALT | ST |

|---------------------------|------------------|--------|------------------------|----------------|----|----|------|------|----|------|----|

| OTIR<br>OTDR<br>(if Br=0) | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                           | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|                           | MC3              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                           | MC4              | T1T2T3 | ВС                     | DATA           | 1  | 0  | 1    | 0    | 1  | 1    | 1  |

| POP zz                    | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                           | MC2              | T1T2T3 | SP                     | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                           | MC3              | T1T2T3 | SP+1                   | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| POP IX<br>POP IY          | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                           | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|                           | MC3              | T1T2T3 | SP                     | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                           | MC4              | T1T2T3 | SP+1                   | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

| PUSH zz                   | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                           | MC2<br>~MC3      | TiTi   | *                      | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                           | MC4              | T1T2T3 | SP-1                   | zzH            | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

|                           | MC5              | T1T2T3 | SP-2                   | zzL            | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction                              | Machine<br>Cycle | States   | Address                | Data                  | RD               | WD                           | MREQ                    | IORO                          | <u>M1</u> | HALT    | ST |

|------------------------------------------|------------------|----------|------------------------|-----------------------|------------------|------------------------------|-------------------------|-------------------------------|-----------|---------|----|

| Instruction                              |                  | States   | Address                | Data                  |                  |                              |                         | `                             |           |         |    |

| RETI (Z)                                 | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0*5<br>1  | 1       | 0  |

|                                          | MC2              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0*5<br>1  | 1       | 1  |

|                                          | MC3<br>~MC5      | TiTiTi   | *                      | Z                     | 1                | 1                            | 1                       | 1                             | 1*5<br>1  | 1       | 1  |

|                                          | MC6              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0*5<br>0  | 1       | 1  |

|                                          | MC7              | Ti       | *                      | Z                     | 1                | 1                            | 1                       | 1                             | 1*5<br>1  | 1       | 1  |

|                                          | MC8              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0*5<br>0  | 1       | 1  |

|                                          | МС9              | T1T2T3   | SP                     | data                  | 0                | 1                            | 0                       | 1                             | 1*5<br>1  | 1       | 1  |

|                                          | MC10             | T1T2T3   | SP+1                   | data                  | 0                | 1                            | 0                       | 1                             | 1*5<br>1  | 1       | 1  |

| RLCA<br>RLA<br>RRCA<br>RRA               | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0         | 1       | 0  |

| RLC g<br>RL g                            | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0         | 1       | 0  |

| RRC g<br>RR g<br>SLA g<br>SRA g<br>SRL g | MC2              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code        | 0                | 1                            | 0                       | 1                             | 0         | 1       | 1  |

|                                          | мс3              | Ti       | *                      | Z                     | 1                | 1                            | 1                       | 1                             | 1         | 1       | 1  |

| *5 The uppe                              | r and lower      | data sho | w the state of         | of $\overline{M1}$ wh | en <del>IO</del> | $\frac{1}{\overline{C}} = 1$ | and $\overline{\rm IO}$ | $\overline{C} = 0 \text{ re}$ | spect     | tively. |    |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction                                                                                                                                                                                                              | Machine<br>Cycle | States        | Address                | Data           | RD | WR | MREQ | IORQ | M1 | HALT | ST |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------------|----------------|----|----|------|------|----|------|----|

| RLC (HL)<br>RL (HL)<br>RRC (HL)<br>RR (HL)<br>SLA (HL)<br>SRA (HL)<br>SRL (HL)                                                                                                                                           | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                                                                                                                                                                                                                          | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|                                                                                                                                                                                                                          | мс3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC4              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC5              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

| RLC (IX + d) RLC (IY + d) RL (IY + d) RL (IY + d) RRC (IX + d) RRC (IY + d) RRC (IY + d) RR (IX + d) RR (IY + d) SLA (IX + d) SLA (IX + d) SRA (IX + d) SRA (IX + d) SRA (IY + d) SRL (IY + d) SRL (IY + d) SRL (IY + d) | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                                                                                                                                                                                                                          | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2ndOp<br>Code  | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|                                                                                                                                                                                                                          | мс3              | T1T2T3        | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC4              | T1T2T3        | 3rd Op Code<br>Address | 3rd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|                                                                                                                                                                                                                          | MC5              | T1T2T3        | IX+d<br>IY+d           | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC6              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC7              | T1T2T3        | IX+d<br>IY+d           | DATA           | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

| RLD<br>RRD                                                                                                                                                                                                               | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

|                                                                                                                                                                                                                          | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|                                                                                                                                                                                                                          | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC4~M<br>C7      | TiTiTiTi<br>* |                        | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|                                                                                                                                                                                                                          | MC8              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1  | 1    | 1  |

| Memory and I/O Wait state insertion 29                                                                                                                                                | Р                                                                                                                                                                                 |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory management unit (MMU) 13  Memory to ASCI 109  Memory to memory 105  MMU Register description 60  Mode  HALT 31  IOSTOP 35  SLEEP 33  SYSTEM STOP 35  Modem control signals 138 | Pin description  A0 through CTS1 7  BUSREQ through RFSH 9  D0 through INT2 8  RTS0 through TEND1 10  TEST through XTAL 10  Pin package  64-pin DIP 3  68-pin PLCC 4  80-pin QFP 5 |  |  |  |  |  |

| N                                                                                                                                                                                     | Programmable reload timer (PRT) 14  Programming  Level-sense 109                                                                                                                  |  |  |  |  |  |

| NMI and DMA operation timing diagram 115 Use 74  Non-maskable interrupt 72                                                                                                            | PRT  Block diagram 157  Bus release mode timing diagram 16'  Interrupt request generation 164  Timer control register 161                                                         |  |  |  |  |  |

| On-chip clock generator Circuit board design rules 170 External clock interface 169 Operating frequencies 168                                                                         | R Refresh 87 Control register 88                                                                                                                                                  |  |  |  |  |  |

| Operation modes Control register 84 CPU timing 18 IOC 16 M1 Enable 15 M1 temporary enable 16                                                                                          | Register ASCI Control A0 125 ASCI Control A1 128 ASCI Control B 131 ASCI Status 0 120 ASCI Status 1 123                                                                           |  |  |  |  |  |