#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 8MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | -40°C ~ 100°C (TA)                                     |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018008vec |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### MANUAL OBJECTIVES

This user manual describes the features of the Z8018x MPUs. This manual provides basic programming information for the Z80180/Z8S180/Z8L180. These cores and base peripheral sets are used in a large family of ZiLOG products. Below is a list of ZiLOG products that use this class of processor, along with the associated processor family. This document is also the core user manual for the following products:

| Part                  | Family          |

|-----------------------|-----------------|

| Z80180                | Z80180          |

| Z8S180                | Z8S180          |

| Z8L180                | Z8L180          |

| Z80181                | Z80180          |

| Z80182                | Z80180, Z8S180* |

| Z80S183               | Z8S180          |

| Z80185/195            | Z8S180          |

| Z80189                | Z8S180          |

| * Part number-dependa | nt              |

### **Intended Audience**

This manual is written for those who program the Z8018x.

### **Manual Organization**

The Z8018x User Manual is divided into five sections, seven appendices, and an index.

### xiv

# List of Tables

| Z80180, Z8S180, Z81 | L180 MPU Operation1                                        |

|---------------------|------------------------------------------------------------|

| Table 1.            | Status Summary                                             |

| Table 2.            | Multiplexed Pin Descriptions                               |

| Table 3.            | Memory Wait States                                         |

| Table 4.            | Wait State Insertion                                       |

| Table 5.            | Power-Down Modes<br>(Z8S180/Z8L180-Class Processor Only)   |

| Table 6.            | I/O Address Map for Z80180-Class Processors Only44         |

| Table 7.            | I/O Address Map<br>(Z8S180/Z8L180-Class Processors Only)48 |

| Table 8.            | State of IEF1 and IEF269                                   |

| Table 9.            | Vector Table                                               |

| Table 10.           | RETI Control Signal States                                 |

| Table 11.           | DRAM Refresh Intervals                                     |

| Table 12.           | Channel 0 Destination                                      |

| Table 13.           | Channel 0 Source                                           |

| Table 14.           | Transfer Mode Combinations                                 |

| Table 15.           | Channel 1 Transfer Mode102                                 |

| Table 16.           | DMA Transfer Request110                                    |

| Table 17.           | Data Formats                                               |

| Table 18.           | Divide Ratio                                               |

| Table 19.           | ASCI Baud Rate Selection                                   |

| Table 20.           | Clock Mode Bit Values                                      |

| Table 21.           | 2^ss Values                                                |

| Table 22.           | CSI/O Baud Rate Selection                                  |

2

on-chip memory management unit (MMU) with the capability of addressing up to 1 MB of memory.

Reduced system costs are obtained by incorporating several key system functions on-chip with the CPU. These key functions include I/O devices such as DMA, UART, and timer channels. Also included on-chip are several *glue* functions such as dynamic RAM refresh control, wait state generators, clock oscillator, and interrupt controller.

Not only does the Z8X180 consume a low amount of power during normal operation, but processors with Z8S180 and Z8L180 class processors also provides two operating modes that are designed to drastically reduce the power consumption even further. The SLEEP mode reduces power by placing the CPU into a *stopped* state, thereby consuming less current, while the on-chip I/O device is still operating. The SYSTEM STOP mode places both the CPU and the on-chip peripherals into a *stopped* state, thereby reducing power consumption even further.

When combined with other CMOS VLSI devices and memories, the Z8X180 provides an excellent solution to system applications requiring high performance, and low power operation.

Figures 1 through 3 illustrate the three pin packages in the Z8X180 MPU family:

- 64-Pin Dual In-line Package (DIP), Figure 1

- 68-Pin Plastic Leaded Chip Carrier (PLCC), Figure 2

- 80-Pin Quad Flat Pack (QFP), Figure 3

Pin out package descriptions for other Z8X180-based products are covered in their respective product specifications.

Figure 4 depicts the block diagram that is shared throughout all configurations of the Z8X180.

23

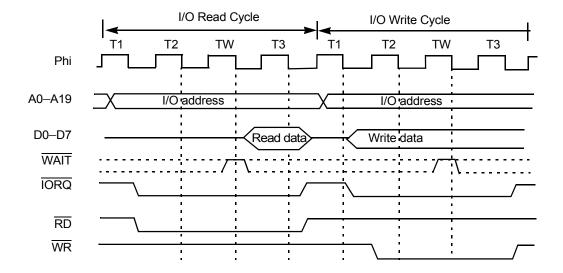

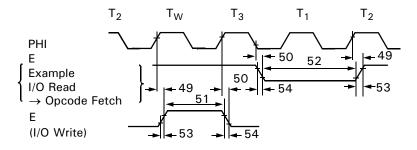

Figure 13. I/O Read/Write Timing Diagram

#### **Basic Instruction Timing**

An instruction may consist of a number of machine cycles including Op Code fetch, operand fetch, and data read/write cycles. An instruction may also include cycles for internal processes which make the bus IDLE. The example in Figure 14 illustrates the bus timing for the data transfer instruction LD (IX+d),g.

UM005003-0703

Z8018x Family MPU User Manual

86

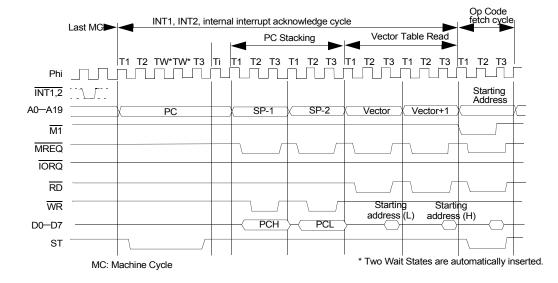

Figure 43. INT1, INT2 and Internal Interrupts Timing Diagram

### **Dynamic RAM Refresh Control**

The Z8X180 incorporates a dynamic RAM refresh control circuit including 8-bit refresh address generation and programmable refresh timing. This circuit generates asynchronous refresh cycles inserted at the programmable interval independent of CPU program execution. For systems which do not use dynamic RAM, the refresh function can be disabled.

When the internal refresh controller determines that a refresh cycle should occur, the current instruction is interrupted at the first breakpoint between machine cycles. The refresh cycle is inserted by placing the refresh address on A0–A7 and the  $\overline{\text{RFSH}}$  output is driven Low.

DREQ Input

Level- and edge-sense DREQ input detection are selectable.

TEND Output Used to indicate DMA completion to external devices.

• Transfer Rate

Each byte transfer occurs every 6 clock cycles. Wait States can be inserted in DMA cycles for slow memory or I/O devices. At the system clock ( $\phi$ ) = 6 MHz, the DMA transfer rate is as high as 1.0 megabytes/second (no Wait States).

There is an additional feature disc for DMA interrupt request by DMA END. Each channel has the following additional specific capabilities:

### Channel 0

- Memory to memory

- Memory to I/O

- Memory to memory mapped I/O transfers.

- Memory address increment, decrement, no-change

- Burst or cycle steal memory to/from memory transfers

- DMA to/from both ASCI channels

- Higher priority than DMAC channel 1

### Channel 1

- Memory to/from I/O transfer

- Memory address increment, decrement

### **DMAC Registers**

Each channel of the DMAC (channel 0, 1) contains three registers specifically associated with that channel.

Table 13.Channel 0 Source

| SM1 | SM0 | Memory/I/O | Address Increment/Decrement |

|-----|-----|------------|-----------------------------|

| 0   | 0   | Memory     | + 1                         |

| 0   | 1   | Memory     | -1                          |

| 1   | 0   | Memory     | fixed                       |

| 1   | 1   | I/O        | fixed                       |

Table 14 describes all DMA TRANSFER mode combinations of DM0 DM1, SM0 SM1. Because I/O to/from I/O transfers are not implemented, 12 combinations are available.

Table 14.

Transfer Mode Combinations

| DM1 | DM0 | SM1 | SM0 | Transfer Mode     | Increment/Decrement |

|-----|-----|-----|-----|-------------------|---------------------|

| 0   | 0   | 0   | 0   | Memory to Memory  | SAR0+1, DAR0+1      |

| 0   | 0   | 0   | 1   | Memory to Memory  | SAR0-1, DAR0+1      |

| 0   | 0   | 1   | 0   | Memory* to Memory | SAR0 fixed, DAR0+ 1 |

| 0   | 0   | 1   | 1   | I/O to Memory     | SAR0 fixed DAR0+1   |

| 0   | 1   | 0   | 0   | Memory to Memory  | SAR0+1, DAR0-1      |

| 0   | 1   | 0   | 1   | Memory to Memory  | SAR0-1,DAR0-1       |

| 0   | 1   | 1   | 0   | Memory to Memory  | SAR0 fixed, DAR0-1  |

| 0   | 1   | 1   | 1   | I/O to Memory     | SAR0 fixed. DAR0-1  |

| 1   | 0   | 0   | 0   | Memory to Memory* | SAR0+ 1, DAR0 fixed |

| 1   | 0   | 0   | 1   | Memory to Memory* | SAR0-1, DAR0 fixed  |

| 1   | 0   | 1   | 0   | Reserved          |                     |

| 1   | 0   | 1   | 1   | Reserved          |                     |

In addition, the operation of channel 0 DMA with the on-chip ASCI (Asynchronous Serial Communication Interface) as well as Channel 1 DMA are described.

### Memory to Memory—Channel 0

For memory to/from memory transfers, the external  $\overline{\text{DREQ0}}$  input is not used for DMA transfer timing. Rather, the DMA operation is timed in one of two programmable modes – BURST or CYCLE STEAL. In both modes, the DMA operation automatically proceeds until termination (shown by byte count-BCR0) = 0.

In BURST mode, the DMA operation proceeds until termination. In this case, the CPU cannot perform any program execution until the DMA operation is completed. In CYCLE STEAL mode, the DMA and CPU operation are alternated after each DMA byte transfer until the DMA is completed. The sequence:

- 1 CPU Machine Cycle

- DMA Byte Transfer

is repeated until DMA is completed. Figure 46 describes CYCLE STEAL mode DMA timing.

112

- 4. Specify whether  $\overline{\text{DREQ1}}$  is level- or edge- sense in the DMS1 bit in DCNTL.

- 5. Enable or disable DMA termination interrupt with the DIE1 bit in DSTAT.

- 6. Program DE1 = 1 (with  $\overline{DWE1} = 0$  in the same access) in DSTAT and the DMA operation with the external I/O device begins using the external  $\overline{DREQ1}$  input and  $\overline{TEND1}$  output.

### **DMA Bus Timing**

When memory (and memory mapped I/O) is specified as a source or destination, MREQ goes Low during the memory access. When I/O is specified as a source or destination, IORQ goes Low during the I/O access.

When I/O (and memory mapped I/O) is specified as a source or destination, the DMA timing is controlled by the external  $\overline{\text{DREQ}}$  input and the  $\overline{\text{TEND}}$  output indicates DMA termination

For I/O accesses, one Wait State is automatically inserted. Additional Wait States can be inserted by programming the on-chip wait state generator or using the external WAIT input.

>

**Note:** For memory mapped I/O accesses, this automatic I/O Wait State is not inserted.

For memory to memory transfers (channel 0 only), the external  $\overline{DREQ0}$  input is ignored. Automatic DMA timing is programmed as either BURST or CYCLE STEAL.

When a DMA memory address carry/borrow between bits A15 and A16 of the address bus occurs (crossing 64KB boundaries), the minimum bus

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|-----------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4               | FE        | R   |       | <b>Framing Error</b> — If a receive data byte frame is delimited by an invalid stop bit (that is, 0, should be 1), FE is set to 1. FE is cleared to 0 when the EFR bit (Error Flag Reset) of CNTLA is written to 0, when DCD0 is High, in IOSTOP mode, and during RESET.                                                                                                                                     |

| 3               | RIE       | R/W |       | <b>Receive Interrupt Enable</b> — RIE must be set to 1 to<br>enable ASCI receive interrupt requests. When RIE is 1, if<br>any of the flags RDRF, OVRN, PE, or FE become set to<br>1, an interrupt request is generated. For channel 0, an<br>interrupt is also generated by the transition of the external<br>DCD0 input from Low to High.                                                                   |

| 2               | CTS1E     | R/W |       | Channel 1 CTS Enable — Channel 1 has an external<br>CTS1 input which is multiplexed with the receive data<br>pin (RXS) for the CSI/O (Clocked Serial I/O Port).<br>Setting CTS1E to 1 selects the CTS1 function and<br>clearing CTS1E to 0 selects the RXS function.                                                                                                                                         |

| 1               | TDRE      | R   |       | <b>Transmit Data Register Empty</b> — TDRE = 1 indicates<br>that the TDR is empty and the next transmit data byte is<br>written to TDR. After the byte is written to TDR, TDRE<br>is cleared to 0 until the ASCI transfers the byte from TDR<br>to the TSR and then TDRE is again set to 1. TDRE is set<br>to 1 in IOSTOP mode and during RESET. When the<br>external CTS input is High, TDRE is reset to 0. |

| 0               | TIE       | R/W |       | <b>Transmit Interrupt Enable</b> — TIE must be set to 1 to<br>enable ASCI transmit interrupt requests. If TIE is 1, an<br>interrupt is requested when TDRE is 1. TIE is cleared to 0<br>during RESET.                                                                                                                                                                                                        |

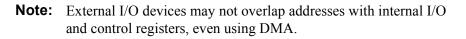

Figure 57. CSI/O Block Diagram

### **CSI/O Registers Description**

### CSI/O Control/Status Register (CNTR: I/O Address 0AH)

CNTR is used to monitor CSI/O status, enable and disable the CSI/O, enable and disable interrupt generation, and select the data clock speed and source.

| Bit                                                             | 7  | 6   | 5   | 4   | 3 | 2   | 1   | 0   |  |  |  |  |

|-----------------------------------------------------------------|----|-----|-----|-----|---|-----|-----|-----|--|--|--|--|

| Bit/Field                                                       | EF | EIE | RE  | TE  | — | SS2 | SS1 | SS0 |  |  |  |  |

| R/W                                                             | R  | R/W | R/W | R/W |   | R/W | R/W | R/W |  |  |  |  |

| Reset                                                           | 0  | 0   | 0   | 0   |   | 1   | 1   | 1   |  |  |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |    |     |     |     |   |     |     |     |  |  |  |  |

CSI/O Control/Status Register (CNTR: 0AH)

### **PRT Operation Notes**

• TMDR data is accurately read without stopping down counting by reading the lower (TMDRnL\*) and higher (TMDRnH\*) bytes in that order. Also, TMDR is read or written by stopping the down counting.<sup>1</sup>

Take care to ensure that a timer reload does not occur during or between lower (RLDRnL\*) and higher (RLDRnH\*) byte writes. This may be guaranteed by system design/timing or by stopping down counting (with TMDR containing a non-zero value) during the RLDR updating. Similarly, in applications where TMDR is written at each TMDR overflow, the system/software design must guarantee that RLDR can be updated before the next overflow occurs. Otherwise, time base inaccuracy occurs.

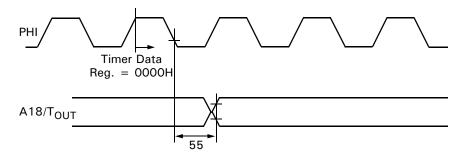

• During RESET, the multiplexed A18/TOUT pin reverts to the address output. By reprogramming the TOC1 and TOC0 bits, the timer output function for PRT channel 1 is selected. The following paragraph describes the initial state of the TOUT pin after TOC1 and TOC0 are programmed to select the PRT channel 1 timer output function.

PRT (channel 1) has not counted down to 0.

If the PRT has not counted down to 0 (timed out), the initial state of TOUT depends on the programmed value in TOC1 and TOC0.

### **Secondary Bus Interface**

### **E clock Output Timing**

The Z8X180 also has a secondary bus interface that allows it to easily interface with other peripheral families.

202

Figure 87. E Clock Timing (Minimum Timing Example of PWEL and PWEH)

Figure 88. Timer Output Timing

### Table 38. Arithmetic and Logical Instructions (8-bit) (Continued)

|                   |              |            |       |     |     |        |      |     |     |       |        |                                  | Flags |   |   |     |   |   |

|-------------------|--------------|------------|-------|-----|-----|--------|------|-----|-----|-------|--------|----------------------------------|-------|---|---|-----|---|---|

|                   |              |            |       |     | Add | ressin | g    |     |     |       |        |                                  | 7     | 6 | 4 | 2   | 1 | 0 |

| Operation<br>Name | Mnemonics    | Op Code    | Immed | Ext | Ind | Reg    | Regl | Imp | Rel | Bytes | States | Operation                        | s     | z | н | P/V | N | с |

|                   | XOR (IY + d) | 11 111 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar⊕ + (IY + d)) <sub>M</sub> →Ar | ↑     | ↑ | R | Ρ   | R | R |

|                   |              | 10 101 110 |       |     |     |        |      |     |     |       |        |                                  |       |   |   |     |   |   |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |        |                                  |       |   |   |     |   |   |

Table 39.

Rotate and Shift Instructions

|                   |             |             |       |     |     |        |      |     |     |       |            |                   |   |   | F | lags |   |   |

|-------------------|-------------|-------------|-------|-----|-----|--------|------|-----|-----|-------|------------|-------------------|---|---|---|------|---|---|

|                   |             |             |       |     | Add | Iressi | ing  |     |     |       |            |                   | 7 | 6 | 4 | 2    | 1 | 0 |

| Operation<br>Name | Mnemonics   | Op Code     | Immed | Ext | Ind | Reg    | Regi | Imp | Rel | Bytes | State<br>s | Operation         | s | z | н | P/V  | N | с |

| Rotate            | RL A        | 00 010 1111 |       |     |     |        |      | S/D |     | 1     | 3          |                   | • | • | R | •    | R | ↑ |

| and<br>Shift      | RL g        | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          |                   | ↑ | ↑ | R | Р    | R | ↑ |

| Data              |             | 00 010 g    |       |     |     |        |      |     |     |       |            | C b7 b0           |   |   |   |      |   |   |

|                   | RL (HL)     | 11 001 011  |       |     |     |        | S/D  |     |     | 2     | 13         | 0 0/              | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 00 010 110  |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   | RL (IX + d) | 11 011 101  |       |     | S/D |        |      |     |     | 4     | 19         |                   | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 11 001 011  |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   |             | <d></d>     |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   |             | 00 010 110  |       |     |     |        |      |     |     |       |            | Ţ,                |   |   |   |      |   |   |

|                   | RL (IY + d) | 11 111 101  |       |     | S/D |        |      |     |     | 4     | 19         | Ar                | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 11 001 011  |       |     |     |        |      |     |     |       |            | b7 b0             |   |   |   |      |   |   |

|                   |             | <d></d>     |       |     |     |        |      |     |     |       |            | Ĭ <u></u>         |   |   |   |      |   |   |

|                   |             | 00 010 110  |       |     |     |        |      |     |     |       |            | (HL) <sub>M</sub> | 1 |   |   |      |   |   |

|                   | RLC A       | 00 000 111  |       |     |     |        |      | S/D |     | 1     | 3          | b7 b0             | • | • | R |      | R | ↑ |

|                   | RLC g       | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          |                   | ↑ | ↑ | R | Ρ    | R | ↑ |

|                   |             | 00 000 g    |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   | RLC (HL)    | 11 001 011  |       |     |     |        | S/D  |     |     | 2     | 13         | b7 🗲 b0 C         | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 00 000 110  |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             |                                                                                                                         | Flags |                  |   |     |                  |   |  |  |

|-------------------|--------------------------------------------------------------|------------|------------|-----|-----|-----|------|-----|-----|-------|-------------|-------------------------------------------------------------------------------------------------------------------------|-------|------------------|---|-----|------------------|---|--|--|

|                   |                                                              |            | Addressing |     |     |     |      | 7   | 6   | 4     | 2           | 1                                                                                                                       | C     |                  |   |     |                  |   |  |  |

| Operation<br>Name | Mnemonics                                                    | Op Code    | Immed      | Ext | Ind | Reg | Regl | Imp | Rel | Bytes | States      | Operation                                                                                                               |       | z                | н | P/V | N                | c |  |  |

|                   | OTIMR**                                                      | 11 101 101 |            |     |     |     | S    |     | D   | 2     | 16 (Br ≠ 0) |                                                                                                                         | R     | s                | R | s   | ↑                | ł |  |  |

|                   |                                                              | 10 010 011 |            |     |     |     |      |     |     |       | 14 (Br = 0) | $\begin{array}{c} HL_{R} + 1 \rightarrow HL_{R} \\ Q \qquad Cr + 1 \rightarrow Cr \\ Br - 1 \rightarrow Br \end{array}$ |       |                  |   |     |                  |   |  |  |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Repeat Q until<br>Br = 0                                                                                                |       |                  |   |     |                  |   |  |  |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Br = 0<br>Cr→A0~A7                                                                                                      |       |                  |   |     |                  |   |  |  |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | 00→A8~A16                                                                                                               |       | (5)              |   |     | (6)              |   |  |  |

|                   | OUTD                                                         | 11 101 101 |            |     |     |     |      | s   | D   | 2     | 12          | (HL) <sub>M</sub> →(BC) <sub>1</sub>                                                                                    | х     | (= <i>)</i><br>↑ | х | х   | (- <i>)</i><br>↑ | ; |  |  |

|                   |                                                              | 10 101 011 |            |     |     |     |      |     |     |       |             | HL <sub>R</sub> -1→HL <sub>R</sub>                                                                                      |       |                  |   |     |                  |   |  |  |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Br-1→Br                                                                                                                 |       |                  |   |     |                  |   |  |  |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Cr→A0~A7                                                                                                                |       |                  |   |     |                  |   |  |  |

|                   |                                                              |            |            |     |     |     |      |     |     |       |             | Br→A8~A16                                                                                                               |       |                  |   |     |                  |   |  |  |

| (6) N = 1:        | : Br-1 = 0<br>: Br-1 ≠ 0<br>MSB of Data =<br>: MSB of Data = |            |            |     |     |     |      |     |     |       |             |                                                                                                                         |       |                  |   |     |                  |   |  |  |

### Table 46. I/O Instructions (Continued)

250

#### ww (L0 = ALL) BC DE HL SP $G(L0 = 0 \sim 7)$ В D Н В D Н HI 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 LO 0 2 4 5 7 8 9 А в С D Е F 1 3 6 0000 IN0 g, (m) IN g, (C) LDI LDIR 0 0 0001 OUT0 (m),g OUT (C),g CPI CPIR 1 1 SBC HL, ww INIR INI 2 0010 2 OTIM OTIM 0011 3 LD (mn), ww OUTI OTIR 3 R 0100 4 TST g TST NEG TST m TSTIO 4 (HL) m 0101 5 RETN 5 0110 6 IM 0 IM 1 SLP 6 LD I,A LD A,I RRD 7 0111 7 1000 IN0 g, (m) IN g, (C) LDD LDDR 8 8 9 1001 OUT0 (m), g OUT (C), g CPD CPDR 9 A ADC HL,ww IND INDR 1010 А OTD в 1011 В LD ww, (mn) OTD OUTD OTDR М MR 1100 С TST g MLT ww С 1101 D RETI D 1110 Е IM 2 Е 1111 LDR, LD A,R RLD F F А 4 5 9 В С D Е F 0 2 3 6 7 8 Α С Е L А С Е L А $g(L0 = 8 \sim F)$

#### Table 50. 2nd Op Code Map Instruction Format: ED XX

252

| Instruction                                                                 | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-----------------------------------------------------------------------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

| ADD A,g<br>ADC A,g                                                          | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SUB g<br>SBC A,g<br>AND g<br>OR g<br>XOR g<br>CP g                          | MC2              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| ADD A,m<br>ADC A,m                                                          | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SUB m<br>SBC A,m<br>AND m<br>OR m<br>XOR m<br>CP m                          | MC2              | T1T2T3 | 1st operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| ADD A, (HL)<br>ADC A, (HL)                                                  | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SUB (HL)<br>SBC A, (HL)<br>AND HU<br>OR (HL)<br>XOR (HL)<br>CP (HL)         | MC2              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| ADD A, (IX+ d)<br>ADD A, (IY+d)                                             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| ADC A, (IX+d)<br>ADC A, (IY+d)<br>SUB (IX+d)<br>SUB (IY+d)<br>SBC A, (IX+d) | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| SBC A, (IY+ d)<br>AND (IX+d)                                                | MC3              | T1T2T3 | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction      | Machine<br>Cycle | States            | Address                         | Data   | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|------------------|------------------|-------------------|---------------------------------|--------|----|----|------|------|-----------|------|----|

|                  | MC1              | T1T2TW<br>TWT3    | Next<br>Op Code<br>Address (PC) | Vector | 1  | 1  | 1    | 0    | 0         | 1    | 0  |

| INTO Mode 2      | MC2              | Ti                | *                               | Z      | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                  | MC3              | T1T2T3            | SP-1                            | РСН    | 1  | 0  | 0    | 1    | 1         |      | 1  |

|                  | MC4              | T1T2T3            | SP-2                            | PCL    | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                  | MC5              | T1T2T3            | I, Vector                       | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                  | MC6              | T1T2T3<br>T1T2,TW | I, Vector+1                     | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| INTI             | MC1              | T1T2,TW<br>TWT3   | Next<br>Op Code<br>Address (PC) |        | 1  | 1  | 1    | 1    | 1         | 1    | 0  |

| INT2<br>Internal | MC2              | Ti                | *                               | Z      | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| Interrupts       | MC3              | T1T2T3            | SP-1                            | РСН    | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                  | MC4              | T1T2T3            | SP-2                            | PCL    | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                  | MC5              | T1T2T3            | I, Vector                       | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                  | MC6              | T1T2T3            | I, Vector+1                     | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

### Table 52. Interrupts (Continued)

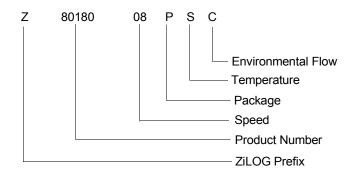

### **ORDERING INFORMATION**

### Codes

- Package

P = Plastic Dip

V = Plastic Chip Carrier

F = Quad Flat Pack

- Temperature  $S = 0^{\circ}C \text{ to } +70^{\circ}C$  $E = -40^{\circ}C \text{ to } 100^{\circ}C$

- Speed 06 = 6 MHz 08 = 8 MHz 10 = 10 MHz

•

- Environmental C = Plastic Standard

- Example Z8018008PSC is an 80180 8 MHz, Plastic DIP, 0°C to 70°C, Plastic Standard Flow.

305

### Α

(ASCI) 14

AC characteristics 197 Address generation, physical 64 Address map I/O 44 I/O address translation 57 Logical examples 55 Logical memory organization 58 Logical space configuration 59 Physical address transition 56 Addressing Extended 182 I/O 184 Indexed 182 Indirect 181 Architecture 12 ASCI Baud rate selection 142 Block diagram 117 Clock diagram 141 Control register A0 125 Control register A1 128 Control register B 131 Functions 116 Interrupt request circuit diagram 140 Register descriptions 117 Status register 0 120 Status register 1 123 Asynchronous serial communications interface

### В

Baud rate selection ASCI 142 CSI/O 150 Block diagram 6 ASCI 117 CSI/O 146 DMAC 92 MMU 56 PRT 157

Bus state controller 13

### С

Central processing unit (CPU) 14 Circuit diagram, ASCI interrupt request 140 Clock generator 13 Clocked serial I/O (CSI/O) 14 CPU register configurations 176 CPU timing Basic instruction 23 **BUSREQ/BUSACK Bus Exchange 25** HALT and Low Power modes 31 I/O data read/write 22 Internal I/O registers 41 MMU register description 60 Op Code fetch timing 18 Operand and data read/write 20 RESET 25 Wait state generator 27