# E·XFL

#### Zilog - Z8018008VSC00TR Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Obsolete                                                   |

| Core Processor                  | Z80180                                                     |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                              |

| Speed                           | 8MHz                                                       |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | DRAM                                                       |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | -                                                          |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | 5.0V                                                       |

| Operating Temperature           | 0°C ~ 70°C (TA)                                            |

| Security Features               | -                                                          |

| Package / Case                  | 68-LCC (J-Lead)                                            |

| Supplier Device Package         | 68-PLCC                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018008vsc00tr |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z8018x Family MPU User Manual

6

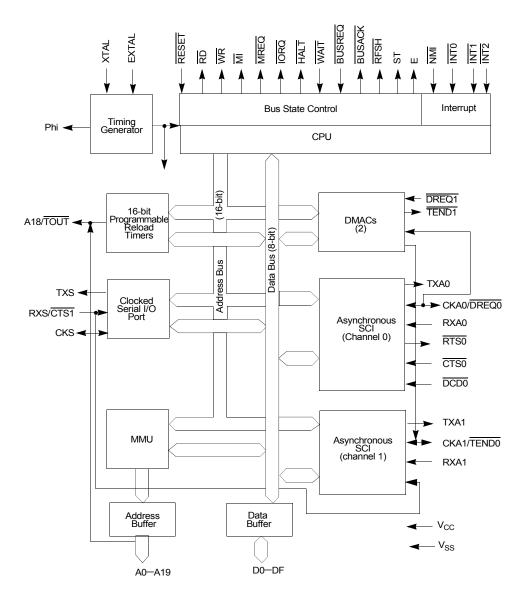

Figure 4. Z80180/Z8S180/Z8L180 Block Diagram

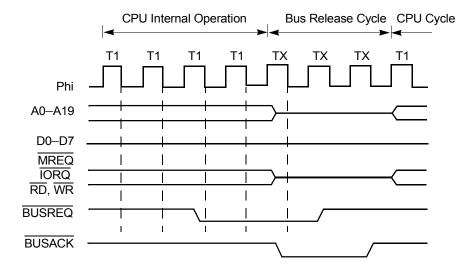

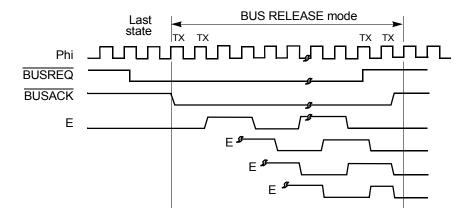

Figure 17. Bus Exchange Timing During CPU Internal Operation

## Wait State Generator

To ease interfacing with slow memory and I/O devices, the Z8X180 uses Wait States (TW) to extend bus cycle timing. A Wait State(s) is inserted based on the combined (logical OR) state of the external  $\overline{WAIT}$  input and an internal programmable wait state (TW) generator. Wait States (TW) can be inserted in both CPU execution and DMA transfer cycles.

When the external  $\overline{\text{WAIT}}$  input is asserted Low, Wait State(s) (TW) are inserted between T2 and T3 to extend the bus cycle duration. The  $\overline{\text{WAIT}}$ input is sampled at the falling edge of the system clock in T2 or TW. If the  $\overline{\text{WAIT}}$  input is asserted Low at the falling edge of the system clock in TW, another TW is inserted into the bus cycle.

**Note:** WAIT input transitions must meet specified setup and hold times. This specification can easily be accomplished by

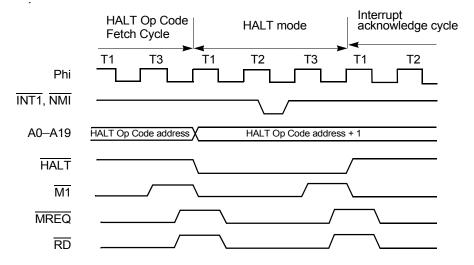

Figure 20. HALT Timing Diagram

#### **SLEEP Mode**

SLEEP mode is entered by execution of the 2-byte SLP instruction. SLEEP mode contains the following characteristics:

- The internal CPU clock stops, reducing power consumption

- The internal crystal oscillator does not stop

- Internal and external interrupt inputs can be received

- DRAM refresh cycles stop

- I/O operations using on-chip peripherals continue

- The internal DMAC stop

- BUSREQ can be received and acknowledged

- Address outputs go High and all other control signal outputs become inactive High

84

# **Return from Subroutine (RETI) Instruction Sequence**

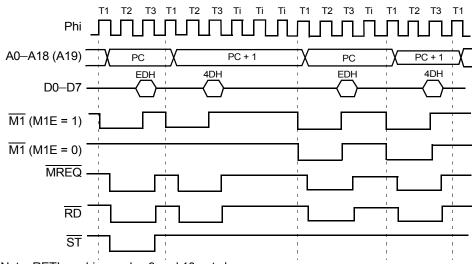

When the EDH/4DH sequence is fetched by the Z8X180, it is recognized as the RETI instruction sequence. The Z8X180 then refetches the RETI instruction with four T-states in the EDH cycle allowing the Z80 peripherals time to decode that cycle (See Figure 42). This procedure allows the internal interrupt structure of the peripheral to properly decode the instruction and behave accordingly.

The M1E bit of the Operation Mode Control Register (OMCR) must be set to 0 so that  $\overline{M1}$  signal is active only during the refetch of the RETI instruction sequence. This condition is the desired operation when Z80 peripherals are connected to the Z8018X.

Note: RETI machine cycles 9 and 10 not shown.

Figure 42. RETI Instruction Sequence

The RETI instruction takes 22 T-states and 10 machine cycles. Table 10 lists the conditions of all the control signals during this sequence for the

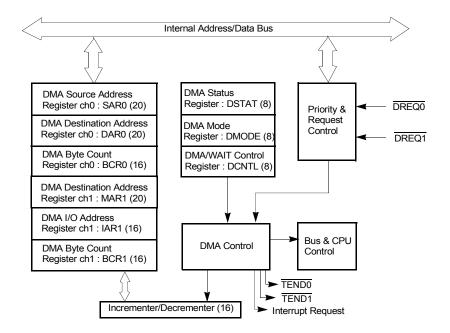

Figure 45. DMAC Block Diagram

#### **DMAC Register Description**

# DMA Source Address Register Channel 0 (SAR0 I/O Address = 20H to 22H)

Specifies the physical source address for channel 0 transfers. The register contains 20 bits and can specify up to 1024KB memory addresses or up to 64KB I/O addresses. Channel 0 source can be memory, I/O, or memory mapped I/O.

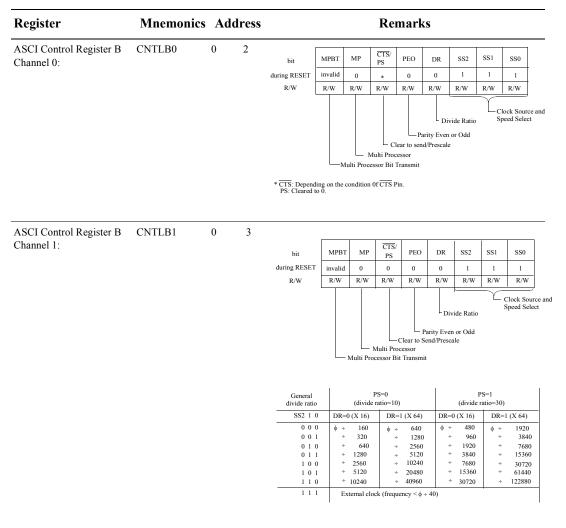

2<sup>ss</sup> depends on the three least significant bits of the CNTLB register, as described in Table 21.

| ss2 | ss1 | ss0 | 2^ss                     |

|-----|-----|-----|--------------------------|

| 0   | 0   | 0   | 1                        |

| 0   | 0   | 1   | 2                        |

| 0   | 1   | 0   | 4                        |

| 0   | 1   | 1   | 8                        |

| 1   | 0   | 0   | 16                       |

| 1   | 0   | 1   | 32                       |

| 1   | 1   | 0   | 64                       |

| 1   | 1   | 1   | External Clock from CKA0 |

Table 21. 2<sup>^</sup>ss Values

The ASCIs require a 50% duty cycle when CKA is used as an input. Minimum High and Low times on CKA0 are typical of most CMOS devices.

RDRF is set, and if enabled, an Rx Interrupt or DMA REquest is generated when the receiver transfers a character from the Rx Shift Register to the RX FIFO. The FIFO provides a margin against overruns. When the is more than one character in the FIFO, and software or a DMA channel reads a character, RDRF either remains set or is cleared and then immediately set again. For example, if a receive interrupt service routine does not real all the characters in the RxFIFO, RDRF and the interrupt request remain asserted.

The Rx DMA request is disabled when any of the error flags PE or FE or OVRN are set, so that software can identify with which character the problem is associated.

If Bit 7, RDRF Interrupt Inhibit, is set to 1, the ASCI does not request a Receive interrupt when its RDRF flag is 1. Set this bit when programming a DMA channel to handle the receive data from an ASCI. The other

157

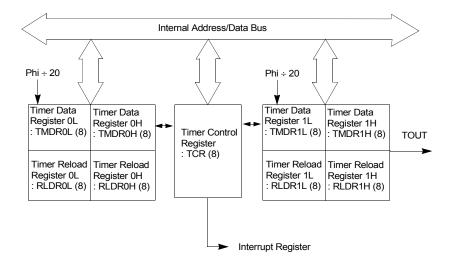

control register. The PRT input clock for both channels is equal to the system clock divided by 20.

Figure 63. PRT Block Diagram

# **PRT Register Description**

Timer Data Register (TMDR: I/O Address - CH0: 0CH, 0DH; CH1: 15H, 14H). PRT0 and PRT1 each contain 16-bit timer Data Registers (TMDR). TMDR0 and TMDR1 are each accessed as low and high byte registers (TMDR0H, TMDR0L and TMDR1H, TMDR1L). During RESET, TMDR0 and TMDR1 are set to FFFFH.

TMDR is decremented once every twenty clocks. When TMDR counts down to 0, it is automatically reloaded with the value contained in the Reload Register (RLDR).

TMDR is read and written by software using the following procedures. The read procedure uses a PRT internal temporary storage register to

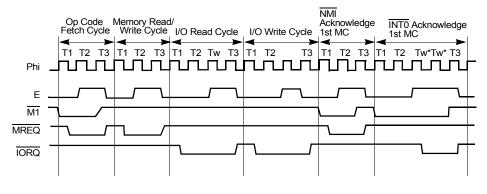

NOTE : MC = Machine Cycle

\* Two wait states are automatically inserted

Figure 68. E Clock Timing in BUS RELEASE Mode

198

Memory Read/Write Cycle timing is the sam as I/O Read/Write Cycle except there are no automatica Wait States (TW), and MREQ is active instead of IORQ.

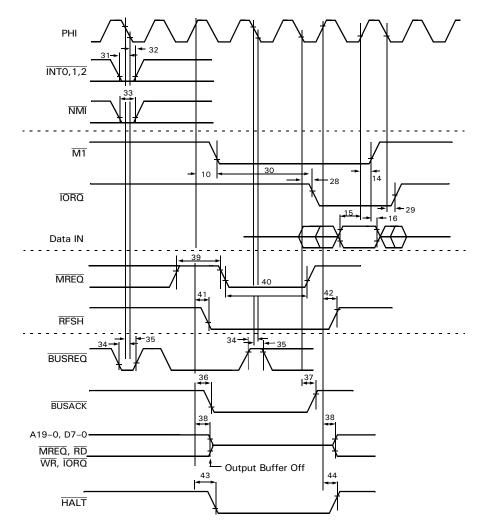

Figure 82. AC Timing Diagram 2

UM005003-0703

205

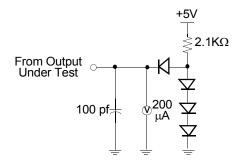

# STANDARD TEST CONDITIONS

The previous DC Characteristics and Capacitance sections apply to the following standard test conditions, unless otherwise noted. All voltages are referenced to GND (0V). Positive current flows in to the referenced pin.

All AC parameters assume a load capacitance of 100 pF. Add 10 ns delay for each 50 pF increase in load up to a maximum of 200 pF for the data bus and 100 pF for the address and control lines. AC timing measurements are referenced to 1.5 volts (except for CLOCK, which is referenced to the 10% and 90% points).

The Ordering Information section lists temperature ranges and product numbers. Package drawings are in the Package Information section. Refer to the Literature List for additional documentation.

Figure 93. Test Setup

# 213

#### Table 38. Arithmetic and Logical Instructions (8-bit) (Continued)

|                   |              |               |       |     |     |        |      |     |     |       |        |                                         |   |   | FI | ags |   |   |

|-------------------|--------------|---------------|-------|-----|-----|--------|------|-----|-----|-------|--------|-----------------------------------------|---|---|----|-----|---|---|

|                   |              |               |       |     | Add | ressir | g    |     |     |       |        |                                         | 7 | 6 | 4  | 2   | 1 | 0 |

| Operation<br>Name | Mnemonics    | Op Code       | Immed | Ext | Ind | Reg    | Regi | Imp | Rel | Bytes | States | Operation                               | s | z | н  | P/V | N | с |

| DEC               | DEC g        | 00 g 101      |       |     |     | S/D    |      |     |     | 1     | 4      | gr-1→gr                                 | ↑ | ↑ | ↑  | V   | S | • |

|                   | DEC (HL)     | 00 110 101    |       |     |     |        | S/D  |     |     | 1     | 10     | (HL) <sub>M</sub> -1→(HL) <sub>M</sub>  | ↑ | ↑ | ↑  | v   | s | • |

|                   | DEC (IX + d) | 11 011 101    |       |     | S/D |        |      |     |     | 3     | 18     | (IX + d)) <sub>M</sub> -I→              | ↑ | ↑ | ↑  | v   | s | • |

|                   |              | 00 110 101    |       |     |     |        |      |     |     |       |        | (IX + d)) <sub>M</sub>                  |   |   |    |     |   |   |

|                   |              | <d></d>       |       |     |     |        |      |     |     |       |        |                                         |   |   |    |     |   |   |

|                   | DEC (IY + d) | 11 111 101    |       |     | S/D |        |      |     |     | 3     | 18     | $(IY + d)_M - 1 \rightarrow$            | ↑ | ↑ | ↑  | v   | s | • |

|                   |              | 00 1101 01    |       |     |     |        |      |     |     |       |        | (IY + d) <sub>M</sub>                   |   |   |    |     |   |   |

|                   |              | <d></d>       |       |     |     |        |      |     |     |       |        |                                         |   |   |    |     |   |   |

| INC               | INC g        | 00 g 100      |       |     |     | S/D    |      |     |     | 1     | 4      | gr + l→gr                               | ↑ | ↑ | ↑  | V   | R | • |

|                   | INC (HL)     | 00 110 100    |       |     |     |        | S/D  |     |     | 1     | 10     | (HL) <sub>M</sub> + I→(HL) <sub>M</sub> | ↑ | ↑ | ↑  | v   | R | • |

|                   | INC (IX + d) | 11 011 101    |       |     | S/D |        |      |     |     | 3     | 18     | $(IX + d))_M + 1 \rightarrow$           | ↑ | ↑ | ↑  | v   | R | • |

|                   |              | 00 110 100    |       |     |     |        |      |     |     |       |        | (1X + d)) <sub>M</sub>                  |   |   |    |     |   |   |

|                   |              | <d></d>       |       |     |     |        |      |     |     |       |        |                                         |   |   |    |     |   |   |

|                   | INC (IY + d) | 11 111 101    |       |     | S/D |        |      |     |     | 3     | 18     | $(IY + d)v + 1 \rightarrow$             | ↑ | ↑ | ↑  | v   | R | • |

|                   |              | 00 110 100    |       |     |     |        |      |     |     |       |        | (IY + d)v                               |   |   |    |     |   |   |

|                   |              | <d></d>       |       |     |     |        |      |     |     |       |        |                                         |   |   |    |     |   |   |

| MULT              | MLT ww**     | 11 101 101    |       |     |     | S/D    |      |     |     | 2     | 17     | wwHr→wwLr→wwI                           | • | • | •  | •   | • | • |

|                   |              | 01 WWI<br>100 |       |     |     |        |      |     |     |       |        |                                         |   |   |    |     |   |   |

| NEGATE            | NEG          | 11 101 101    |       |     |     |        |      | S/D |     | 2     | 6      | 0-Ar→Ar                                 | ↑ | ↑ | ↑  | Y   | s | ↑ |

|                   |              | 01 000 100    |       |     |     |        |      |     |     |       |        |                                         |   |   |    |     |   |   |

|                   |               |            |       |     |     |        |      |     |     |       |        |                          |   |   |   | Flags |   |   |

|-------------------|---------------|------------|-------|-----|-----|--------|------|-----|-----|-------|--------|--------------------------|---|---|---|-------|---|---|

|                   |               |            |       |     | Ad  | dressi | ng   |     |     |       |        |                          | 7 | 6 | 4 | 2     | 1 | C |

| Operation<br>Name | Mnemonics     | Op Code    | Immed | Ext | Ind | Reg    | Regl | Imp | Rel | Bytes | States | Operation                | s | z | н | P/V   | N | ¢ |

| oad               | LD (IX + d),m | 11 011 101 | S     |     | D   |        |      |     |     | 4     | 15     | m→(IX + d) <sub>M</sub>  | • | • | • | •     | • | • |

| 8-Bit<br>Data     |               | 00 110 110 |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

| Jata              |               | <d></d>    |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   | LD (IY + d),m | 11 111 101 | S     |     | D   |        |      |     |     | 4     | 15     | m→(IY + d) <sub>M</sub>  | • | • | • | •     | • | • |

|                   |               | 01 110 g   |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   |               | <d></d>    |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   |               | <m></m>    |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   | LD (HL),g     | 01 110 g   |       |     |     | s      | D    |     |     | 1     | 7      | gr→(HL) <sub>M</sub>     | • | • | • | •     | • | • |

|                   | LD (IX + d),g | 11 011 101 |       |     | D   | s      |      |     |     | 3     | 15     | gr→(IX+d) <sub>M</sub>   | • | • | • | •     | • | ٠ |

|                   |               | 01 110 g   |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   |               | <d></d>    |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   | LD (IY + d),g | 11 111 101 |       |     | D   | s      |      |     |     | 3     | 15     | gr→(IY + d) <sub>M</sub> | • | • | • | •     | • | • |

|                   |               | 01 110 g   |       |     |     |        |      |     |     |       |        |                          |   |   |   |       |   |   |

|                   |               | <d></d>    |       |     |     |        |      |     |     |       |        |                          |   |   |   |       | 1 |   |

#### Table 41.8-Bit Load (Continued)

Table 42.16-Bit Load

|                   |           |            |       |     |     |         |      |     |     |       |        |                    |   |   | F | lags |   |   |

|-------------------|-----------|------------|-------|-----|-----|---------|------|-----|-----|-------|--------|--------------------|---|---|---|------|---|---|

|                   |           |            |       |     | Add | lressir | ng   |     |     |       |        |                    | 7 | 6 | 4 | 2    | 1 | 0 |

| Operation<br>Name | Mnemonics | Op Code    | Immed | Ext | Ind | Reg     | Regl | Imp | Rel | Bytes | States | Operation          | s | z | н | P/V  | N | с |

| Load              | LD ww,mn  | 00 ww0 001 | S     |     |     | D       |      |     |     | 3     | 9      | mn→ww <sub>R</sub> | • | • | • | •    | • | • |

| 16-Bit<br>Data    |           | <n></n>    |       |     |     |         |      |     |     |       |        |                    |   |   |   |      |   | ĺ |

|                   |           | <m></m>    |       |     |     |         |      |     |     |       |        |                    |   |   |   |      |   | Í |

|                   | LD IX,mn  | 11 011 101 | S     |     |     |         |      | D   |     | 4     | 12     | mn→IX <sub>R</sub> | • | • | • | •    | • | • |

|                   |           | 00 100 001 |       |     |     |         |      |     |     |       |        |                    |   |   |   |      |   | ĺ |

|                   |           | <n></n>    |       |     |     |         |      |     |     |       |        |                    |   |   |   |      |   | Í |

|                   |           | <m></m>    |       |     |     |         |      |     |     |       |        |                    |   |   |   |      |   |   |

|                   |            |              |       |     |     |         |      |     |     |       |        |                            |   |   | F | lags |   |   |

|-------------------|------------|--------------|-------|-----|-----|---------|------|-----|-----|-------|--------|----------------------------|---|---|---|------|---|---|

|                   |            |              |       |     | Add | Iressii | ng   |     |     |       |        |                            | 7 | 6 | 4 | 2    | 1 | 0 |

| Operation<br>Name | Mnemonics  | Op Code      | Immed | Ext | Ind | Reg     | Regl | Imp | Rel | Bytes | States | Operation                  | s | z | н | P/V  | N | с |

| Load              | LD (mn),HL | 00 100 010   |       | D   |     |         |      | S   |     | 3     | 16     | Hr→(mn + 1) <sub>M</sub>   | • | • | • | •    | • | • |

| 16-bit<br>Data    |            | <n></n>      |       |     |     |         |      |     |     |       |        | Lr→(mn) <sub>M</sub>       |   |   |   |      |   |   |

|                   |            | < <b>m</b> > |       |     |     |         |      |     |     |       |        |                            |   |   |   |      |   |   |

|                   | LD (mn),IX | 11 011 101   |       | D   |     |         |      | s   |     | 4     | 19     | IXHr-(mn + 1) <sub>M</sub> | • | • | • | •    | • | • |

|                   |            | 00 100 010   |       |     |     |         |      |     |     |       |        | IXLr→(mn) <sub>M</sub>     |   |   |   |      |   |   |

|                   |            | <n></n>      |       |     |     |         |      |     |     |       |        |                            |   |   |   |      |   |   |

|                   |            | <m></m>      |       |     |     |         |      |     |     |       |        |                            |   |   |   |      |   |   |

|                   | LD (mn),IY | 11 111 101   |       | D   |     |         |      | s   |     | 4     | 19     | IYHr→(mn + 1) <sub>M</sub> | • | • | • | •    | • | • |

|                   |            | 00 100 010   |       |     |     |         |      |     |     |       |        | IYLr→(mn) <sub>M</sub>     |   |   |   |      |   |   |

|                   |            | <n></n>      |       |     |     |         |      |     |     |       |        |                            |   |   |   |      |   |   |

|                   |            | <m></m>      |       |     |     |         |      |     |     |       |        |                            |   |   |   |      |   |   |

Table 42.

16-Bit Load (Continued)

г—— т

Table 43.Block Transfer

|                             |           |            |       |     |     |       |      |     |     |       |        |                                                                                                                                                              |   |          | Fla | ags      |   |   |

|-----------------------------|-----------|------------|-------|-----|-----|-------|------|-----|-----|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|-----|----------|---|---|

|                             |           |            |       |     | Ad  | dress | ing  |     |     |       |        |                                                                                                                                                              | 7 | 6        | 4   | 2        | 1 | 0 |

| Operation<br>Name           | Mnemonics | Op Code    | Immed | Ext | Ind | Reg   | Regl | Imp | Rel | Bytes | States | Operation                                                                                                                                                    | s | z        | н   | P/V      | N | с |

| Block<br>Transfer<br>Search | CPD       | 11 101 101 |       |     |     |       | s    | s   |     | 2     | 12     | Ar = (HL) <sub>M</sub>                                                                                                                                       | ↑ | (3)<br>↑ | ↑   | (2)<br>↑ | s | • |

| Data                        |           | 10 101 001 |       |     |     |       |      |     |     |       |        | BC <sub>R</sub> -1→BC <sub>R</sub>                                                                                                                           |   |          |     |          |   |   |

|                             |           |            |       |     |     |       |      |     |     |       |        | HL <sub>R</sub> -1→HL <sub>R</sub>                                                                                                                           |   | (3)      |     | (2)      |   |   |

|                             | CPDR      | 11 101 101 |       |     |     |       | s    | s   |     | 2     | 14     | BC <sub>R</sub> ≠0 Ar≠(HL) <sub>M</sub>                                                                                                                      | ↑ | ↑        | ↑   | ↑        | s | • |

|                             |           | 10 111 001 |       |     |     |       |      |     |     |       | 12     | $BC_R = 0 \text{ or } Ar = (HL)_M$                                                                                                                           |   |          |     |          |   |   |

|                             |           |            |       |     |     |       |      |     |     |       |        | $\begin{array}{c} & \text{Ar-(HL)}_{R} \\ \text{Q} & \text{BC}_{R}\text{-1-BC}_{R} \\ & \text{HL}_{R}\text{-1} \text{\rightarrow} \text{HL}_{R} \end{array}$ |   |          |     |          |   |   |

|                             |           |            |       |     |     |       |      |     |     |       |        | Repeat Q until                                                                                                                                               |   |          |     |          |   |   |

|                             |           |            |       |     |     |       |      |     |     |       |        | Ar = $(HL)_{M}$ or $BC_{R} = 0$                                                                                                                              |   | (3)      |     | (2)      |   |   |

250

#### ww (L0 = ALL) BC DE HL SP $G(L0 = 0 \sim 7)$ В D Н В D Н HI 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 LO 0 2 4 5 7 8 9 А в С D Е F 1 3 6 0000 IN0 g, (m) IN g, (C) LDI LDIR 0 0 0001 OUT0 (m),g OUT (C),g CPI CPIR 1 1 SBC HL, ww INIR INI 2 0010 2 OTIM OTIM 0011 3 LD (mn), ww OUTI OTIR 3 R 0100 4 TST g TST NEG TST m TSTIO 4 (HL) m 0101 5 RETN 5 0110 6 IM 0 IM 1 SLP 6 LD I,A LD A,I RRD 7 0111 7 1000 IN0 g, (m) IN g, (C) LDD LDDR 8 8 9 1001 OUT0 (m), g OUT (C), g CPD CPDR 9 A ADC HL,ww IND INDR 1010 А OTD в 1011 В LD ww, (mn) OTD OUTD OTDR М MR 1100 С TST g MLT ww С 1101 D RETI D 1110 Е IM 2 Е 1111 LDR, LD A,R RLD F F А 4 5 9 В С D Е F 0 2 3 6 7 8 А С Е L А С Е L А $g(L0 = 8 \sim F)$

#### Table 50. 2nd Op Code Map Instruction Format: ED XX

258

| Instruction                | Machine<br>Cycle | States | Address                   | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|----------------------------|------------------|--------|---------------------------|----------------|----|----|------|------|-----------|------|----|

|                            | MC1              | T1T2T3 | 1st Op Code<br>Address    | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INC (IX+ d)<br>INC (IY+d)  | MC2              | T1T2T3 | 2nd Op Code<br>Address    | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                            | MC3              | T1T2T3 | 1st operand<br>Address    | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| DEC (IX+d)<br>DEC (IY+d)   | MC4~M<br>C5      | TiTi   | *                         | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                            | MC6              | T1T2T3 | X+ d<br>IY+ d             | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                            | MC7              | T1     | *                         | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                            | MC8              | T1T2T3 | IX+ d<br>IY+d             | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

| INC ww                     | MC1              | T1T2T3 | 1st Op Code<br>Address    | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| DEC ww                     | MC2              | Ti     | *                         | Z              | 1  | 1  | t    | 1    | 1         | 1    | 1  |

| INC IX                     | MC1              | T1T2T3 | 1st Op Code<br>Address    | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| INC IY<br>DEC IX<br>DEC IY | MC2              | T1T2T3 | 2nd Op Code<br>Address    | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                            | MC3              | Ti     | *                         | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                            | MC1              | T1T2T3 | 1st Op Code<br>Address    | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| IN A,(m)                   | MC2              | T1T2T3 | 1st operand<br>Address    | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                            | MC3              | T1T2T3 | m to A0~A7<br>A to A8~A15 | DATA           | 0  | 1  | 1    | 0    | 1         | 1    | 1  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

| Instruction      | Machine<br>Cycle | States            | Address                         | Data   | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|------------------|------------------|-------------------|---------------------------------|--------|----|----|------|------|-----------|------|----|

|                  | MC1              | T1T2TW<br>TWT3    | Next<br>Op Code<br>Address (PC) | Vector | 1  | 1  | 1    | 0    | 0         | 1    | 0  |

| INTO Mode 2      | MC2              | Ti                | *                               | Z      | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                  | MC3              | T1T2T3            | SP-1                            | РСН    | 1  | 0  | 0    | 1    | 1         |      | 1  |

|                  | MC4              | T1T2T3            | SP-2                            | PCL    | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                  | MC5              | T1T2T3            | I, Vector                       | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                  | MC6              | T1T2T3<br>T1T2,TW | I, Vector+1                     | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| INTI             | MC1              | T1T2,TW<br>TWT3   | Next<br>Op Code<br>Address (PC) |        | 1  | 1  | 1    | 1    | 1         | 1    | 0  |

| INT2<br>Internal | MC2              | Ti                | *                               | Z      | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| Interrupts       | MC3              | T1T2T3            | SP-1                            | РСН    | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                  | MC4              | T1T2T3            | SP-2                            | PCL    | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                  | MC5              | T1T2T3            | I, Vector                       | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                  | MC6              | T1T2T3            | I, Vector+1                     | DATA   | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

#### Table 52. Interrupts (Continued)

Note: If Bus Request and Refresh Request occur simultaneously, Bus Request is accepted but Refresh Request is cleared.

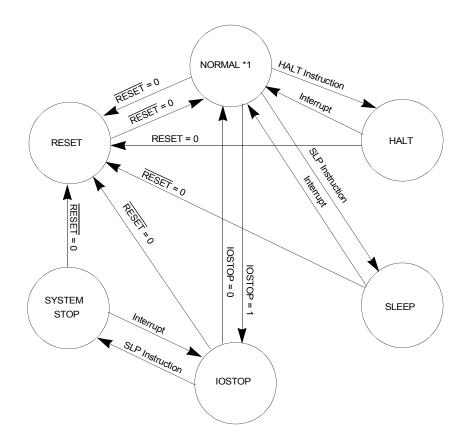

# **OPERATION MODE TRANSITION**

288

| Mode            |              | <u>M1</u> | MREQ | IORQ | RD | WR | RFSH | HALT | BUSACK | ST | Address<br>BUS | Data<br>BUS |

|-----------------|--------------|-----------|------|------|----|----|------|------|--------|----|----------------|-------------|

|                 | Memory Read  | 1         | 0    | 1    | 0  | 1  | 1    | *    | 1      | 0  | А              | IN          |

| Internal<br>DMA | Memory Write | 1         | 0    | 1    | 1  | 0  | 1    | *    | 1      | 0  | А              | OUT         |

|                 | I/O Read     | 1         | 1    | 0    | 0  | 1  | 1    | *    | 1      | 0  | А              | IN          |

|                 | I/O Write    | 1         | 1    | 0    | 1  | 0  | 1    | *    | 1      | 0  | А              | OUT         |

| RESET           |              | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 1  | Ζ              | IN          |

#### Table 55. Pin Outputs in Each Operating Mode (Continued)

- 1 : High

- 0 : Low

- A : Programmable

- Z : High Impedance

- IN : Input

- OUT : Output

- \* : Invalid

# **PIN STATUS**

Tables 56 describes the status of each ping during RESET and LOW POWER OPERATION modes.

294

#### Table 57. Internal I/O Registers (Continued)

305

# Α

(ASCI) 14

AC characteristics 197 Address generation, physical 64 Address map I/O 44 I/O address translation 57 Logical examples 55 Logical memory organization 58 Logical space configuration 59 Physical address transition 56 Addressing Extended 182 I/O 184 Indexed 182 Indirect 181 Architecture 12 ASCI Baud rate selection 142 Block diagram 117 Clock diagram 141 Control register A0 125 Control register A1 128 Control register B 131 Functions 116 Interrupt request circuit diagram 140 Register descriptions 117 Status register 0 120 Status register 1 123 Asynchronous serial communications interface

# В

Baud rate selection ASCI 142 CSI/O 150 Block diagram 6 ASCI 117 CSI/O 146 DMAC 92 MMU 56 PRT 157

Bus state controller 13

# С

Central processing unit (CPU) 14 Circuit diagram, ASCI interrupt request 140 Clock generator 13 Clocked serial I/O (CSI/O) 14 CPU register configurations 176 CPU timing Basic instruction 23 **BUSREQ/BUSACK Bus Exchange 25** HALT and Low Power modes 31 I/O data read/write 22 Internal I/O registers 41 MMU register description 60 Op Code fetch timing 18 Operand and data read/write 20 RESET 25 Wait state generator 27