#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 8MHz                                                   |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018008vsg |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents

| Z80180, Z8S180, Z8L180 MPU Operation                 | 1   |

|------------------------------------------------------|-----|

| Features                                             | .1  |

| General Description                                  | .1  |

| Pin Description                                      | .7  |

| Architecture                                         | 2   |

| Operation Modes1<br>CPU Timing1                      |     |

| Wait State Generator                                 | 27  |

| (Z80180-Class Processors Only)                       |     |

| (Z8S180/Z8L180 only)                                 |     |

| STANDBY Mode                                         |     |

| STANDBY Mode Exit wiht BUS REQUEST                   | 8   |

| STANDBY Mode EXit with External Interrupts           | ;9  |

| IDLE Mode 4                                          |     |

| STANDBY-QUICK RECOVERY Mode                          |     |

| Internal I/O Registers4                              | 1   |

| MMU Register Description                             | 50  |

| Interrupts                                           | 5   |

| Interrupt Acknowledge Cycle Timings                  | 32  |

| Interrupt Sources During RESET                       | 33  |

| Dynamic RAM Refresh Control                          | 36  |

| DMA Controller (DMAC)                                | )() |

| Asynchronous Serial Communication Interface (ASCI)11 | 5   |

|                  | Flag                                                          |     |

|------------------|---------------------------------------------------------------|-----|

|                  | Miscellaneous                                                 |     |

|                  | Data Manipulation Instructions                                |     |

|                  | Data Transfer Instructions                                    |     |

|                  | Program and Control Instructions Special Control Instructions |     |

| Instructio       | n Summary                                                     | 237 |

| <b>Op Code</b> N | Мар                                                           | 247 |

| Bus Contr        | rol Signal Conditions                                         | 251 |

|                  | Bus and Control Signal Condition in each Machine Cycle        |     |

|                  | Interrupts                                                    |     |

| Operating        | g Modes Summary                                               | 281 |

|                  | Request Acceptances in Each Operating Mode                    |     |

|                  | Request Priority                                              |     |

|                  | Operation Mode Transition                                     |     |

|                  | Other Operation Mode Transitions                              |     |

| Status Sig       | nals                                                          | 287 |

|                  | Pin Outputs in Each Operating Mode                            |     |

|                  | Pin Status                                                    |     |

| I/O Regist       | ters                                                          | 293 |

|                  | Internal I/O Registers                                        |     |

|                  | Ordering Information                                          |     |

$\overline{\text{BUSREQ}}$ , and  $\overline{\text{INT0}}$  signals are inactive. The CPU acknowledges these interrupt requests with an interrupt acknowledge cycle. Unlike the acknowledgment for  $\overline{\text{INT0}}$ , during this cycle neither the  $\overline{\text{M1}}$  or  $\overline{\text{IORQ}}$  signals become Active.

**IORQ.** *I/O Request (Output, Active Low, 3-state).* IORQ indicates that the address bus contains a valid I/O address for an I/O read or I/O write operation. IORQ is also generated, along with M1, during the acknowledgment of the INTO input signal to indicate that an interrupt response vector can be placed onto the data bus. This signal is analogous to the IOE signal of the Z64180.

**M1.** *Machine Cycle 1 (Output, Active Low).* Together with  $\overline{\text{MREQ}}$ ,  $\overline{\text{M1}}$  indicates that the current cycle is the Op Code fetch cycle of an instruction execution. Together with  $\overline{\text{IORQ}}$ ,  $\overline{\text{M1}}$  indicates that the current cycle is for an interrupt acknowledge. It is also used with the  $\overline{\text{HALT}}$  and ST signal to decode status of the CPU machine cycle. This signal is analogous to the  $\overline{\text{LIR}}$  signal of the Z64180.

**MREQ.** *Memory Request (Output, Active Low, 3-state).* MREQ indicates that the address bus holds a valid address for a memory read or memory write operation. This signal is analogous to the ME signal of the Z64180.

**NMI.** *Non-maskable Interrupt (Input, negative edge triggered).* **NMI** has a higher priority than **INT** and is always recognized at the end of an instruction, regardless of the state of the interrupt enable flip-flops. This signal forces CPU execution to continue at location 0066H.

**RD.** *Read (Output active Low, 3-state).* **RD** indicates that the CPU wants to read data from memory or an I/O device. The addressed I/O or memory device must use this signal to gate data onto the CPU data bus.

**RFSH.** *Refresh (Output, Active Low).* Together with  $\overline{\text{MREQ}}$ ,  $\overline{\text{RFSH}}$  indicates that the current CPU machine cycle and the contents of the address bus must be used for refresh of dynamic memories. The low order 8 bits of the address bus (A7–A0) contain the refresh address.

This signal is analogous to the  $\overline{\text{REF}}$  signal of the Z64180.

17

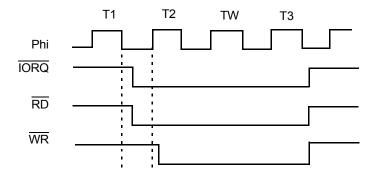

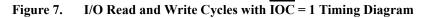

When  $\overline{IOC}$  is 0, the timing of the  $\overline{IORQ}$  and  $\overline{RD}$  signals match the timing required by the Z80 family of peripherals. The  $\overline{IORQ}$  and  $\overline{RD}$  signals go active as a result of the rising edge of T2. This timing allows the Z8X180 to satisfy the setup times required by the Z80 peripherals on those two signals (Figure ).

Figure 8. I/O Read and Write cycles with IOC = 0 Timing Diagram

For the remainder of this document, assume that M1E is 0 and  $\overline{IOC}$  is 0.

UM005003-0703

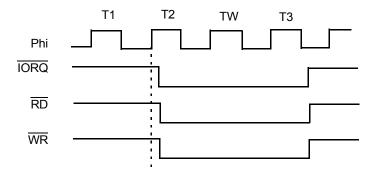

Figure 22. I/O Address Relocation

## Internal I/O Registers Address Map

The internal I/O register addresses are described in Table 6 and Table 7. These addresses are relative to the 64-byte boundary base address specified in ICR.

#### I/O Addressing Notes

The internal I/O register addresses are located in the I/O address space from 0000H to 00FFH (16-bit I/O addresses). Thus, to access the internal I/O registers (using I/O instructions), the high-order 8 bits of the 16-bit I/O address must be 0.

The conventional I/O instructions (OUT (m), A/IN A, (m) / OUTI/INI, for example) place the contents of a CPU register on the high-order 8 bits of the address bus, and thus may be difficult to use for accessing internal I/O registers.

For efficient internal I/O register access, a number of new instructions have been added, which force the high-order 8 bits of the 16-bit I/O

50

|     |                                           |          | A        | ldress |      |

|-----|-------------------------------------------|----------|----------|--------|------|

|     | Register                                  | Mnemonic | Binary   | Hex    | Page |

| DMA | DMA Source Address Register Ch 0L         | SAR0L    | XX100000 | 20H    | 93   |

|     | DMA Source Address Register Ch 0H         | SAR0H    | XX100001 | 21H    | 93   |

|     | DMA Source Address Register Ch 0B         | SAR0B    | XX100010 | 22H    | 93   |

|     | DMA Destination Address Register Ch<br>0L | DAR0L    | XX100011 | 23H    | 94   |

|     | DMA Destination Address Register Ch<br>0H | DAR0H    | XX100100 | 24H    | 94   |

|     | DMA Destination Address Register Ch<br>0B | DAR0B    | XX100101 | 25H    | 94   |

|     | DMA Byte Count Register Ch 0L             | BCR0L    | XX100110 | 26H    | 94   |

|     | DMA Byte Count Register Ch 0H             | BCR0H    | XX100111 | 27H    | 94   |

|     | DMA Memory Address Register Ch 1L         | MAR1L    | XX101000 | 28H    | 94   |

|     | DMA Memory Address Register Ch 1H         | MAR1H    | XX101001 | 29H    | 94   |

|     | DMA Memory Address Register Ch 1B         | MAR1B    | XX101010 | 2AH    | 94   |

|     | DMA I/O Address Register Ch 1L            | IAR1L    | XX101011 | 2BH    | 102  |

|     | DMA I/O Address Register Ch 1H            | IAR1H    | XX101100 | 2CH    | 102  |

|     | DMA I/O Address Register Ch 1             | IAR1B    | XX101101 | 2DH    | 94   |

|     | DMA Byte Count Register Ch 1L             | BCR1L    | XX101110 | 2EH    | 94   |

|     | DMA Byte Count Register Ch 1H             | BCR1H    | XX101111 | 2FH    | 94   |

|     | DMA Status Register                       | DSTAT    | XX110000 | 30H    | 95   |

|     | DMA Mode Register                         | DMODE    | XX110001 | 31H    | 97   |

|     | DMA/WAIT Control Register                 | DCNTL    | XX110010 | 32H    | 101  |

#### Table 7. I/O Address Map (Z8S180/Z8L180-Class Processors Only) (Continued)

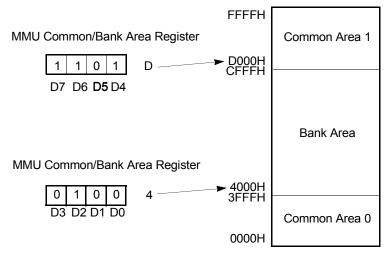

Figure 28. Logical Space Configuration (Example)

59

UM005003-0703

87

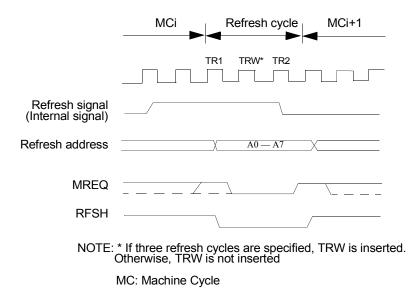

Refresh cycles may be programmed to be either two or three clock cycles in duration by programming the REFW (Refresh Wait) bit in the Refresh Control Register (RCR). The external  $\overline{WAIT}$  input and the internal Wait State generator are not effective during refresh.

Figure 44 depicts the timing of a refresh cycle with a refresh wait (TRW) cycle.

Figure 44. Refresh Cycle Timing Diagram

100

| DM1                                  | DM0 | SM1 | SM0 | Transfer Mode | Increment/Decrement |  |  |

|--------------------------------------|-----|-----|-----|---------------|---------------------|--|--|

| 1                                    | 1   | 0   | 0   | Memory to I/O | SAR0+1, DAR0 fixed  |  |  |

| 1                                    | 1   | 0   | 1   | Memory to I/O | SAR0-1, DAR0 fixed  |  |  |

| 1                                    | 1   | 1   | 0   | Reserved      |                     |  |  |

| 1                                    | 1   | 1   | 1   | Reserved      |                     |  |  |

| Note: *: includes memory mapped I/O. |     |     |     |               |                     |  |  |

Table 14.

Transfer Mode Combinations

### **DMA/WAIT Control Register (DCNTL)**

DCNTL controls the insertion of Wait States into DMAC (and CPU) accesses of memory or I/O Also, the DMA request mode for each DREQ  $\overline{\text{DREQ0}}$  and  $\overline{\text{DREQ1}}$ ) input is defined as level or edge sense. DCNTL also sets the DMA transfer mode for channel 1, which is limited to memory to/from I/O transfers.

133

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

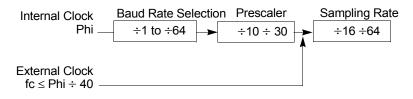

| 5               | CTS/PS    | R/W |       | <b>Clear to Send/Prescale</b> — When read, $\overline{\text{CTS}/\text{PS}}$ reflects<br>the state of the external $\overline{\text{CTS}}$ input. If the $\overline{\text{CTS}}$ input pin<br>is High, $\overline{\text{CTS}/\text{PS}}$ is read as 1. When the $\overline{\text{CTS}}$ input pin is<br>High, the TDRE bit is inhibited (that is, held at 0). For<br>channel 1, the $\overline{\text{CTS}1}$ input is multiplexed with RXS pin<br>(Clocked Serial Receive Data). Thus, $\overline{\text{CTS}/\text{PS}}$ is only<br>valid when read if the channel 1 CTS1E bit is 1 and the<br>$\overline{\text{CST1}}$ input pin function is selected. The read data of<br>$\overline{\text{CTS}/\text{PS}}$ is not affected by RESET.<br>When written, $\overline{\text{CT}/\text{PS}}$ specifies the baud rate generator<br>prescale factor. If $\overline{\text{CTS}/\text{PS}}$ is set to 1, the system clock is<br>prescaled by 30 while if $\overline{\text{CTS}/\text{PS}}$ is cleared to 0, the<br>system clock is prescaled by 10.CTS/PS is cleared to 0<br>during RESET. |

| 4               | PEO       | R/W |       | <b>Parity Even Odd</b> — PE0 selects even or odd parity. PE0 does not affect the enabling/disabling of parity (MOD1 bit of CNTLA). If PE0 is cleared to 0, even parity is selected. If PE0 is set to 1, odd parity is selected.PE0 is cleared to 0 during RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3               | DR        | R/W |       | <b>Divide Ratio</b> — DR specifies the divider used to obtain<br>baud rate from the data sampling clock If DR is reset to 0,<br>divide by 16 is used, while if DR is set to 1, divide by 64<br>is used. DR is cleared to 0 during RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2–0             | SS2-0     | R/W |       | <b>Source/Speed Select</b> — Specifies the data clock source (internal or external) and baud rate prescale factor. SS2, SS1, and SS0 are all set to 1 during RESET. Table 18 describes the divide ratio corresponding to SS2, SS1 and SS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

The external ASCI channel 0 data clock pins are multiplexed with DMA control lines (CKA0/ $\overline{\text{DREQ}}$  and CKA1/ $\overline{\text{TEND0}}$ ). During RESET, these

#### ASCI to/from DMAC Operation

Operation of the ASCI with the on-chip DMAC channel 0 requires that the DMAC be correctly configured to use the ASCI flags as DMA request signals.

#### **ASCI and RESET**

During RESET, the ASCI status and control registers are initialized as defined in the individual register descriptions.

Receive and Transmit operations are stopped during RESET. However, the contents of the transmit and receive data registers (TDR and RDR) are not changed by RESET.

#### **ASCI Clock**

When in external clock input mode, the external clock is directly input to the sampling rate  $(\div 16/\div 64)$  as depicted in Figure 56.

Figure 56. ASCI Clock

160

#### Timer Reload Register Channel 0L (RLDR0L: 0EH)

| Bit                                                             | 7 | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------------------------------|---|-------------------|---|---|---|---|---|---|--|--|

| Bit/Field                                                       |   | Timer Reload Data |   |   |   |   |   |   |  |  |

| R/W                                                             |   | R/W               |   |   |   |   |   |   |  |  |

| Reset                                                           |   | 0                 |   |   |   |   |   |   |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |                   |   |   |   |   |   |   |  |  |

#### Timer Reload Register Channel 0H (RLDR0L: 0FH)

| Bit                                                           | 7 | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------------------------------------------------------------|---|-------------------|---|---|---|---|---|---|--|--|

| Bit/Field                                                     |   | Timer Reload Data |   |   |   |   |   |   |  |  |

| R/W                                                           |   | R/W               |   |   |   |   |   |   |  |  |

| Reset                                                         |   | 0                 |   |   |   |   |   |   |  |  |

| Note: R = Read W = Write X = Indeterminate ? = Not Applicable |   |                   |   |   |   |   |   |   |  |  |

## Timer Data Register 1L (TMDR1L: 14H)

| Bit                                                             | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------------------------------|---|------------|---|---|---|---|---|---|--|--|

| Bit/Field                                                       |   | Timer Data |   |   |   |   |   |   |  |  |

| R/W                                                             |   | R/W        |   |   |   |   |   |   |  |  |

| Reset                                                           |   | 0          |   |   |   |   |   |   |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |            |   |   |   |   |   |   |  |  |

#### Timer Data Register 1H (TMDR1H: 15H)

| Bit                                                             | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------------------------------|---|------------|---|---|---|---|---|---|--|--|

| Bit/Field                                                       |   | Timer Data |   |   |   |   |   |   |  |  |

| R/W                                                             |   | R/W        |   |   |   |   |   |   |  |  |

| Reset                                                           |   | 0          |   |   |   |   |   |   |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |            |   |   |   |   |   |   |  |  |

These devices require connection with the Z8X180 synchronous E clock output. The speed (access time) required for the peripheral devices are determined by the Z8X180 clock rate. Table 24, and Figure 67 through Figure 70 define E clock output timing.

Wait States are inserted in Op Code fetch, memory read/write, and I/O read/write cycles which extend the duration of E clock output High. During I/O read/write cycles with no Wait States (only occurs during on-chip I/O register accesses), E does not go High.

| Condition                                               | ondition Duration of E Clock Output High |                        |  |  |  |  |

|---------------------------------------------------------|------------------------------------------|------------------------|--|--|--|--|

| Op Code Fetch Cycle<br>Memory Read/Write Cycle          | T2 rise - T3 fall                        | (1.5 Phi + nw x Phi)   |  |  |  |  |

| I/O read Cycle                                          | 1st Tw rise - T3 fall                    | (0.5Phi + nw x Phi)    |  |  |  |  |

| I/O Write Cycle                                         | 1st Tw rise - T3 rise                    | In <sub>w</sub> x Phi) |  |  |  |  |

| NMI Acknowledge 1st MC                                  | T2 rise - T3 fall                        | (1.5 Phi)              |  |  |  |  |

| INT0 Acknowledge 1st MC                                 | 1st Tw rise - T3 fall                    | (0.50 + nw x Phi)      |  |  |  |  |

| BUS RELEASE mode<br>SLEEP mode<br>SYSTEM STOP mode      | Phi fall - Phi fall                      | (2 Phi or 1 Phi)       |  |  |  |  |

| Note: nw = the number of Wait States; MC: Machine Cycle |                                          |                        |  |  |  |  |

| Table 24. | E Clock | Timing in | Each | Condition |

|-----------|---------|-----------|------|-----------|

|-----------|---------|-----------|------|-----------|

166

#### **MLT- Multiply**

The MLT performs unsigned multiplication on two 8-bit numbers yielding a 16-bit result. MLT may specify BC, DE, HL, or SP registers. The 8-bit operands are loaded into each half of the 16-bit register and the 16-bit result is returned in that register.

#### OTIM, OTIMR, OTDM, OTDMR - Block I/O

The contents of memory pointed to by HL is output to the I/O address in (C). The memory address (HL) and I/O address (C) are incremented in OTIM and OTIMR and decremented in OTDM and OTDMR, respectively. The B register is decremented. The OTIMR and OTDMR variants repeat the above sequence until register B is decremented to 0. Since the I/O address (C) is automatically incremented or decremented, these instructions are useful for block I/O (such as Z80180 on-chip I/O) initialization. When I/O is accessed, 00H is output in high-order bits of address automatically.

#### TSTIO m - Test I/O Port

The contents of the I/O port addressed by C are ANDed with immediately specified 8-bit data and the status flags are updated. The I/O port contents are not written (non-destructive AND). When I/O is accessed, 00H is output in higher bits of address automatically.

#### TST g - Test Register

Perform an AND instruction on the contents of the specified register with the accumulator (A) and the status flags are updated. The accumulator and specified register are not changed (non-destructive AND).

#### TST m - Test Immediate

Perform an AND instruction on the contents of the immediately specified 8-bit data with the accumulator (A) and the status flags are updated. The accumulator is not changed (non-destructive AND).

211

## DATA MANIPULATION INSTRUCTIONS

#### Table 38. Arithmetic and Logical Instructions (8-bit)

|                   |                |            |       |     |     |        |      |     |     |       |        |                                       |   |   | FI | ags |   | Π |

|-------------------|----------------|------------|-------|-----|-----|--------|------|-----|-----|-------|--------|---------------------------------------|---|---|----|-----|---|---|

|                   |                |            |       |     | Add | ressin | g    |     |     |       |        |                                       | 7 | 6 | 4  | 2   | 1 | 0 |

| Operation<br>Name | Mnemonics      | Op Code    | Immed | Ext | Ind | Reg    | Regi | Imp | Rel | Bytes | States | Operation                             | s | z | н  | P/V | N | с |

| ADD               | ADD A,g        | 10 000 g   |       |     |     | S      |      | D   |     | 1     | 4      | Ar + gr→Ar                            | ↑ | ↑ | ↑  | V   | R | 1 |

|                   | ADD A, (HL)    | 10 000 110 |       |     |     |        | s    | D   |     | 1     | 6      | Ar + (HL) <sub>M</sub> →Ar            | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   | ADD A, m       | 11 000 110 | s     |     |     |        |      | D   |     | 2     | 6      | Ar + m→Ar                             | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   |                | <m></m>    |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   | ADD A,(IX + d) | 11 011 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar + (IX + d) <sub>M</sub> →Ar        | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   |                | 10 000 110 |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   | ADD A,(IY + d) | 11 111 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar + (IY + d)) <sub>M</sub> →Ar       | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   |                | 10 000 110 |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

| ADC               | ADC A,g        | 10 001 g   |       |     |     | s      |      | D   |     | 1     | 4      | Ar + gr + c→Ar                        | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   | ADC A,(HL)     | 10 001 110 |       |     |     |        | S    | D   |     | 1     | 6      | Ar + (HL) <sub>M</sub> + c→Ar         | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   | ADC A,m        | 11 001 110 | S     |     |     |        |      | D   |     | 2     | 6      | Ar + m + c→Ar                         | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   |                | <m></m>    |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   | ADC A,(IX + d) | 11 011 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar + (IX + d)) <sub>M</sub> +<br>c→Ar | ↑ | ↑ | ↑  | V   | R | ↑ |

|                   |                | 10 001 110 |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   | ADC A,(IY + d) | 11 111 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar + (IY + d)) <sub>M</sub> +<br>c→Ar | ↑ | 1 | ↑  | v   | R | ¢ |

|                   |                | 10 001 110 |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

|                   |                | <d></d>    |       |     |     |        |      |     |     |       |        |                                       |   |   |    |     |   |   |

UM005003-0703

235

## **Special Control Instructions**

|                     |           |            |       |     |     |        |      |     |     |       |        |                                  |   |   | F | lags |   |   |

|---------------------|-----------|------------|-------|-----|-----|--------|------|-----|-----|-------|--------|----------------------------------|---|---|---|------|---|---|

|                     |           |            |       |     | A   | ddress | ing  |     |     |       |        |                                  | 7 | 6 | 4 | 2    | 1 | 0 |

| Operation<br>Name   | Mnemonics | Op Code    | Immed | Ext | Ind | Reg    | Regi | Imp | Rel | Bytes | States | Operation                        | s | z | н | P/V  | N | с |

| Special<br>Function | DAA       | 00 100 111 |       |     |     |        |      | S/D |     | 1     | 4      | Decimal<br>Adjust<br>Accumulator | 1 | ↑ | ↑ | Р    | • | ↑ |

| Carry<br>Control    | CCF       | 00 111 111 |       |     |     |        |      |     |     | 1     | 3      | C→C                              | • | • | R | •    | R | ↑ |

|                     | SCF       | 00 110 111 |       |     |     |        |      |     |     | 1     | 3      | 1→C                              | • | • | R | •    | R | s |

| CPU<br>Control      | DI        | 11 110 011 |       |     |     |        |      |     |     | 1     | 3      | 0→IEF1,0→IEF2 (7)                | • | • | • | •    | • | • |

|                     | EI        | 11 111 011 |       |     |     |        |      |     |     | 1     | 3      | 1→IEF1,1→IEF2 (7)                | • | • | • | •    | • | • |

|                     | HALT      | 01 110 110 |       |     |     |        |      |     |     | 1     | 3      | CPU halted                       | • | • | • | •    | • | • |

|                     | IMO       | 11 101 101 |       |     |     |        |      |     |     | 2     | 6      | Interrupt                        | • | • | • | •    | • | • |

|                     |           | 01 000 110 |       |     |     |        |      |     |     |       |        | Mode 0                           |   |   |   |      |   |   |

|                     | IM1       | 11 101 101 |       |     |     |        |      |     |     | 2     | 6      | Interrupt                        | • | • | • | •    | • | • |

|                     |           | 01 010 110 |       |     |     |        |      |     |     |       |        | Mode 1                           |   |   |   |      |   |   |

|                     | IM2       | 11 101 101 |       |     |     |        |      |     |     | 2     | 6      | Interrupt                        | • | • | • | •    | • | • |

|                     |           | 01 011 110 |       |     |     |        |      |     |     |       |        | Mode 2                           |   |   |   |      |   |   |

|                     | NOP       | 00 000 000 |       |     |     |        |      |     |     | 1     | 3      | No operation                     | • | • | • | •    | • | • |

|                     | SLP**     | 11 101 101 |       |     |     |        |      |     |     | 2     | 8      | Sleep                            | • | • | • | •    | • | • |

|                     |           | 01 110 110 |       |     |     |        |      |     |     |       |        |                                  |   |   |   |      |   |   |

#### Table 47. Special Control Instructions

#### 251

## **Bus Control Signal Conditions**

# BUS AND CONTROL SIGNAL CONDITION IN EACH MACHINE CYCLE

\* (ADDRESS) invalid

Z (DATA) high impedance.

\*\* added new instructions to Z80

| Table 51.         Bus and Control Signal Condition in Each Machine Cycle |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

| Instruction            | Machine<br>Cycle | States   | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|------------------------|------------------|----------|------------------------|----------------|----|----|------|------|-----------|------|----|

|                        | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| ADD HL,ww              | MC2<br>~MC5      | TiTiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                        | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| ADD IX,xx<br>ADD IY,yy | MC2              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                        | MC3<br>~MC6      | TiTiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| ADC HL,ww              | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SBC HL,ww              | MC2              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                        | MC3<br>~MC6      | TiTiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

278

| Instruction | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

|             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| TST g**     | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| TST m**     | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | 1st operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| TST (HL)**  | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 2  | 0    | 2    | 0         | 2    | 0  |

|             | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC4              | T1T23  | HL                     | Data           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

290

|                      |                               | Pi     | n Status in Ea | ach Operation | Mode           |

|----------------------|-------------------------------|--------|----------------|---------------|----------------|

| Symbol               | Pin Function                  | RESET  | SLEEP          | ΙΟՏΤΟΡ        | SYSTEM<br>STOP |

|                      | CKA0<br>(External Clock Mode) | Z      | IN (A)         | IN (N)        | IN (N)         |

|                      | DREQ0                         | Ζ      | IN (N)         | IN (A)        | IN (N)         |

| TXA1                 | —                             | 1      | OUT            | Н             | Н              |

| RXA1                 | —                             | IN (N) | IN (A)         | IN (N)        | IN (N)         |

| CKA1/TEND0           | CKA1<br>(Internal Clock Mode) | Z      | OUT            | Z             | Z              |

|                      | CKA1<br>(External Clock Mode) | Z      | IN (A)         | IN (N)        | IN (N)         |

|                      | TEND0                         | Ζ      | 1              | OUT           | 1              |

| TXS                  | —                             | 1      | OUT            | Н             | Н              |

| RXS/CTS <sub>1</sub> | RXS                           | IN (N) | IN (A)         | IN (N)        | IN (N)         |

|                      | CTS1                          | IN (N) | IN (A)         | IN (N)        | IN (N)         |

| CKS                  | CKS<br>(Internal Clock Mode)  | Z      | OUT            | 1             | 1              |

|                      | CKS<br>(External Clock Mode)  | Z      | IN (A)         | Z             | Z              |

| DREQ <sub>1</sub>    | <b>—</b>                      | IN (N) | IN (N)         | IN (A)        | IN (N)         |

| TEND <sub>1</sub>    | <b> </b>                      | 1      | 1              | OUT           | 1              |

| HALT                 | <b> </b>                      | 1      | 0              | OUT           | 0              |

| RFSH                 | —                             | 1      | 1              | OUT           | 1              |

| IORQ                 | —                             | 1      | 1              | OUT           | 1              |

#### Table 56. Pin Status During RESET and LOW POWER OPERATION Modes (Continued)

UM005003-0703

300

| Register                                                    | Mnemonics   | Addre      | SS                  |                  |                     | Re                                  | marl                       | KS .      |         |           |                     |

|-------------------------------------------------------------|-------------|------------|---------------------|------------------|---------------------|-------------------------------------|----------------------------|-----------|---------|-----------|---------------------|

| MMU Common Base                                             | CBR         | 3 8        |                     |                  |                     |                                     |                            | 1         | T       | 1         | 1                   |

| Register:                                                   |             |            | bit                 | CB7              | CB6                 | CB5                                 | CB4                        | CB3       | CB2     | CB1       | CB0                 |

|                                                             |             |            | during RESET        | 0                | 0                   | 0                                   | 0                          | 0         | 0       | 0         | 0                   |

|                                                             |             |            | R/W                 | R/W              | R/W                 | R/W                                 | R/W                        | R/W       | R/W     | R/W       | R/W                 |

|                                                             |             |            |                     |                  |                     |                                     |                            | Y         | MMU Co  | mmon Ba   | ise Regis           |

| MMU Bank Base Register                                      | BBR         | 3 9        |                     | BB7              | BB6                 | BB5                                 | BB4                        | BB3       | BB2     | BB1       | BB0                 |

|                                                             |             |            | bit<br>during RESET | 0                | 0                   | 0                                   | 0                          | 0         | 0       | 0         | 0                   |

|                                                             |             |            | R/W                 | R/W              | R/W                 | R/W                                 | R/W                        | R/W       | R/W     | R/W       | R/W                 |

|                                                             |             |            |                     |                  |                     |                                     |                            |           |         | I         |                     |

|                                                             |             |            |                     |                  |                     |                                     |                            |           | MMU Ba  | nk Base R | legister            |

| MMU Common/Bank<br>Register                                 | CBAR        | 3 A        | bit                 | CA3              | CA2                 | CA1                                 | CA0                        | BA3       | BA2     | BA1       | BA0                 |

|                                                             |             |            | during RESET        | 1                | 1                   | 1                                   | 1                          | 0         | 0       | 0         | 0                   |

|                                                             |             |            | R/W                 | R/W              | R/W                 | R/W                                 | R/W                        | R/W       | R/W     | R/W       | R/W                 |

|                                                             |             |            |                     |                  |                     |                                     |                            |           |         |           |                     |

|                                                             |             |            |                     |                  |                     | ммц                                 | J Commo                    | n Area Re | egister |           | U Bank<br>1 Registe |

|                                                             | OMCR        | 3 E        | bit                 | MIE              | MITE                |                                     | J Commo                    | n Area Re | egister |           | U Bank<br>1 Registe |

|                                                             | OMCR        | 3 E        | bit<br>during RESET | MIE              | MITE<br>1           |                                     | 1                          |           | -       | Area      | 1 Registe           |

|                                                             | OMCR        | 3 E        |                     |                  |                     | IOC                                 | _                          | _         | _       | Area      | Registe             |

|                                                             | OMCR        | 3 E        | during RESET        | 1                | 1<br>W              | IOC<br>1<br>R/W                     | l<br>I/O Comp              | l         | _       | Area      | Registe             |

|                                                             | OMCR        | 3 E        | during RESET        | l<br>R/W         | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l         | _       | Area      | Registe             |

| Register                                                    |             |            | during RESET        | l<br>R/W         | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l         | _       | Area      | Registe             |

| Register                                                    | OMCR<br>ICR | 3 E<br>3 F | during RESET<br>R/W | l<br>R/W         | 1<br>W<br>MI Enable | I<br>I<br>R/W<br>MI Temp            | 1<br>I/O Comp<br>orary Ena | l         | _       | Area      | I Registe           |

| Register                                                    |             |            | during RESET<br>R/W | l<br>R/W         | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              |           | 1       | Area      | Registe             |

| Operation Mode Control<br>Register<br>I/O Control Register: |             |            | during RESET<br>R/W | I<br>R/W<br>IOA7 | 1<br>W<br>MI Enable | IOC<br>1<br>R/W<br>MT Temp<br>IOSTP | I/O Comp<br>orary Ena      |           |         | Area      | 1 Registe           |

#### Table 57. Internal I/O Registers (Continued)

I/O Address