# E·XF

#### Zilog - Z8018010FSC00TR Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of Embedded - Microprocessors

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Obsolete                                                   |

| Core Processor                  | Z80180                                                     |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                              |

| Speed                           | 10MHz                                                      |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | DRAM                                                       |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | -                                                          |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | 5.0V                                                       |

| Operating Temperature           | 0°C ~ 70°C (TA)                                            |

| Security Features               | -                                                          |

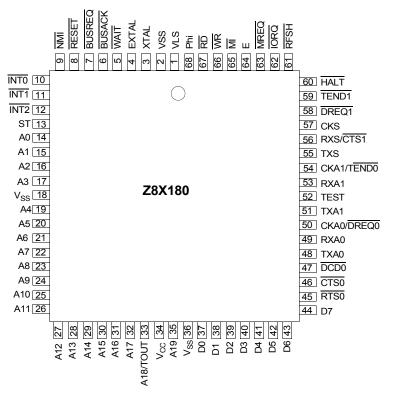

| Package / Case                  | 80-BQFP                                                    |

| Supplier Device Package         | 80-QFP                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018010fsc00tr |

|                                 |                                                            |

Email: info@E-XFL.COM

Details

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | Flag                                                          |     |

|------------------|---------------------------------------------------------------|-----|

|                  | Miscellaneous                                                 |     |

|                  | Data Manipulation Instructions                                |     |

|                  | Data Transfer Instructions                                    |     |

|                  | Program and Control Instructions Special Control Instructions |     |

| Instructio       | n Summary                                                     | 237 |

| <b>Op Code</b> N | Мар                                                           | 247 |

| Bus Contr        | rol Signal Conditions                                         | 251 |

|                  | Bus and Control Signal Condition in each Machine Cycle        |     |

|                  | Interrupts                                                    |     |

| Operating        | g Modes Summary                                               | 281 |

|                  | Request Acceptances in Each Operating Mode                    |     |

|                  | Request Priority                                              |     |

|                  | Operation Mode Transition                                     |     |

|                  | Other Operation Mode Transitions                              |     |

| Status Sig       | nals                                                          | 287 |

|                  | Pin Outputs in Each Operating Mode                            |     |

|                  | Pin Status                                                    |     |

| I/O Regist       | ters                                                          | 293 |

|                  | Internal I/O Registers                                        |     |

|                  | Ordering Information                                          |     |

| r                  |            |      |   |    |                 |

|--------------------|------------|------|---|----|-----------------|

| V <sub>SS</sub> 1  | $\bigcirc$ |      | - | 64 | Phi             |

| XTAL 2             | $\bigcirc$ |      | _ | 63 | RD              |

| EXTAL 3            |            |      |   | 62 | WR              |

| WAIT 4             |            |      |   | 61 | MI              |

| BUSACK 5           |            |      |   | 60 | E               |

| BUSREQ 6           |            |      | - | 59 | MREQ            |

| RESET 7            |            |      | - | 58 | IORQ            |

| NMI 8              |            |      |   | 57 | RFSH            |

| INT0 9             |            |      | - | 56 | HALT            |

| INT1 10            |            |      | - | 55 | TEND1           |

| INT2 11            |            |      | _ | 54 | DREQ1           |

| ST 12              |            |      | - | 53 | CKS             |

| A0 13              |            |      | - | 52 | RXS/CTS1        |

| A1 14              |            |      |   | 51 | TXS             |

| A2 15              |            |      |   | 50 | CKA1/TEND0      |

| A3 16              | Z8         | X180 | - | 49 | RXA1            |

| A4 17              |            |      |   | 48 | TXA1            |

| A5 18              |            |      |   | 47 | CKA0/DREQ0      |

| A6 <u>19</u>       |            |      | - | 46 | RXA0            |

| A7 20              |            |      |   | 45 | TXA0            |

| A8 21              |            |      | - | 44 | DCO0            |

| A9 22              |            |      |   | 43 | CTS0            |

| A10 23             |            |      | - | 42 | RTS0            |

| A11 24             |            |      |   | 41 | D7              |

| A12 25             |            |      |   | 40 | D6              |

| A13 26             |            |      |   | 39 | D5              |

| A14 27             |            |      | - | 38 | D4              |

| A15 28             |            |      | - | 37 | D3              |

| A16 29             |            |      |   | 36 | D2              |

| A17 30             |            |      | - | 35 | D1              |

| A18/TOUT 31        |            |      | F | 34 | D0              |

| V <sub>CC</sub> 32 |            |      |   | 33 | V <sub>SS</sub> |

Figure 1. 64-Pin DIP

Z8018x Family MPU User Manual

4

address to 0. These instructions are IN0, OUT0, OTIM, OTIMR, OTDM, OTDMR and TSTIO (see Instruction Set).

When writing to an internal I/O register, the same I/O write occurs on the external bus. However, the duplicate external I/O write cycle exhibits internal I/O write cycle timing. For example, the WAIT input and programmable Wait State generator are ignored. Similarly, internal I/O read cycles also cause a duplicate external I/O read cycle. However, the external read data is ignored by the Z8X180.

Normally, external I/O addresses should be chosen to avoid overlap with internal I/O addresses and duplicate I/O accesses.

|       |                                      |          | A        | ldress |      |

|-------|--------------------------------------|----------|----------|--------|------|

|       | Register                             | Mnemonic | Binary   | Hex    | Page |

| ASCI  | ASCI Control Register A Ch 0         | CNTLA0   | XX000000 | 00H    | 125  |

|       | ASCI Control Register A Ch 1         | CNTLA1   | XX000001 | 01H    | 128  |

|       | ASCI Control Register B Ch 0         | CNTLB0   | XX000010 | 02H    | 132  |

|       | ASCI Control Register B Ch 1         | CNTLB1   | XX000011 | 03H    | 132  |

|       | ASCI Status Register Ch 0            | STAT0    | XX000100 | 04H    | 120  |

|       | ASCI Status Register Ch 1            | STAT1    | XX000101 | 05H    | 123  |

|       | ASCI Transmit Data Register Ch 0     | TDR0     | XX000110 | 06H    | 118  |

|       | ASCI Transmit Data Register Ch 1     | TDR1     | XX000111 | 07H    | 118  |

|       | ASCI Receive Data Register Ch 0      | RDR0     | XX001000 | 08H    | 119  |

|       | ASCI Receive Data Register Ch 1      | RDR1     | XX001001 | 09H    | 119  |

| CSI/O | CSI/O Control Register               | CNTR     | XX001010 | 0AH    | 147  |

|       | CSI/O Transmit/Receive Data Register | TRD      | XX1011   | 0BH    | 149  |

#### Table 6. I/O Address Map for Z80180-Class Processors Only

60

# **MMU Register Description**

#### MMU Common/Bank Area Register (CBAR)

CBAR specifies boundaries within the Z8X180 64KB logical address space for up to three areas; Common Area 0, Bank Area and Common Area 1.

MMU Common/Bank Area Register (CBAR: 3AH)

| Bit       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit/Field | CA3 | CA2 | CA1 | CA0 | BA3 | BA2 | BA1 | BA0 |

| R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset     | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                             |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 7–4             | CA7-4     | R/W |       | CA specifies the start (low) address (on 4KB boundaries) for the Common Area 1. This also determines the last address of the Bank Area. |

| 3-0             | BA3-0     | R/W |       | BA specifies the start (low) address (on 4KB boundaries) for the Bank Area. This also determines the last address of the Common Area 0. |

-

77

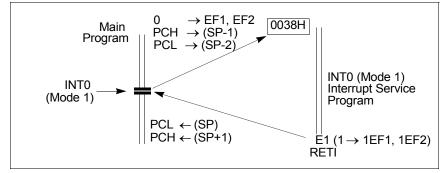

disabling all maskable interrupts. The interrupt service routine normally terminates with the EI (Enable Interrupts) instruction followed by the RETI (Return from Interrupt) instruction, to reenable the interrupts. Figure 37 depicts the use of INTO (Mode 1) and RETI for the Mode 1 interrupt sequence.

Figure 38 illustrates INTO Mode 1 Timing.

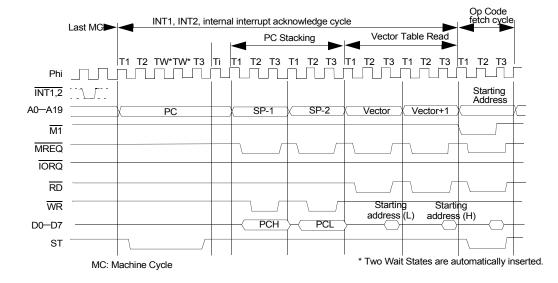

also the interrupt response sequence used for all internal interrupts (except TRAP).

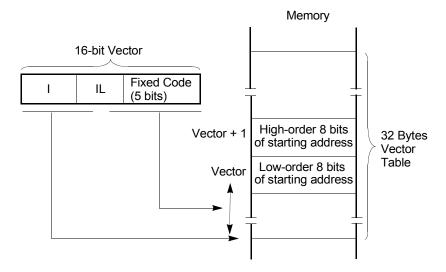

As depicted in Figure 41, the low-order byte of the vector table address has the most significant three bits of the software programmable IL register while the least significant five bits are a unique fixed value for each interrupt ( $\overline{INT1}$ ,  $\overline{INT2}$  and internal) source:

Figure 41. INT1, INT2 Vector Acquisition

INT1 and INT2 are globally masked by IEF1 is 0. Each is also individually maskable by respectively clearing the ITE1 and ITE2 (bits 1,2) of the INT/TRAP control register to 0.

During RESET, IEF1, ITE1 and ITE2 bits are reset to 0.

#### **Internal Interrupts**

Internal interrupts (except TRAP) use the same vectored response mode as INT1 and INT2. Internal interrupts are globally masked by IEF1 is 0. Individual internal interrupts are enabled/disabled by programming each UM005003-0703 81

Z8018x Family MPU User Manual

86

Figure 43. INT1, INT2 and Internal Interrupts Timing Diagram

# **Dynamic RAM Refresh Control**

The Z8X180 incorporates a dynamic RAM refresh control circuit including 8-bit refresh address generation and programmable refresh timing. This circuit generates asynchronous refresh cycles inserted at the programmable interval independent of CPU program execution. For systems which do not use dynamic RAM, the refresh function can be disabled.

When the internal refresh controller determines that a refresh cycle should occur, the current instruction is interrupted at the first breakpoint between machine cycles. The refresh cycle is inserted by placing the refresh address on A0–A7 and the  $\overline{\text{RFSH}}$  output is driven Low.

#### ASCI Receive Shift Register 0,1(RSR0, 1)

This register receives data shifted in on the RXA pin. When full, data is automatically transferred to the ASCI Receive Data Register (RDR) if it is empty. If RSR is not empty when the next incoming data byte is shifted in, an overrun error occurs. The RSR is not program-accessible.

#### ASCI Receive Data Register 0,1 (RDR0, 1: I/O Address = 08H, 09H)

When a complete incoming data byte is assembled in RSR, it is automatically transferred to the RDR if RDR is empty. The next incoming data byte can be shifted into RSR while RDR contains the previous received data byte. Thus, the ASCI receiver on Z80180 is doublebuffered.

#### ASCI Receive Data Register Ch. 0 (RDR0: 08H)

| Bit                                                             | 7 | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------------------------------------------------------|---|------------------------|---|---|---|---|---|---|--|--|--|

| Bit/Field                                                       |   | ASCI Receive Channel 0 |   |   |   |   |   |   |  |  |  |

| R/W                                                             |   | R/W                    |   |   |   |   |   |   |  |  |  |

| Reset                                                           |   | 0                      |   |   |   |   |   |   |  |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |                        |   |   |   |   |   |   |  |  |  |

#### ASCI Receive Data Register Ch. 1 (RDR1: 09H)

١

| Bit                                                             | 7 | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------------------------------------------------------|---|------------------------|---|---|---|---|---|---|--|--|--|

| Bit/Field                                                       |   | ASCI Receive Channel 1 |   |   |   |   |   |   |  |  |  |

| R/W                                                             |   | R/W                    |   |   |   |   |   |   |  |  |  |

| Reset                                                           |   | 0                      |   |   |   |   |   |   |  |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |                        |   |   |   |   |   |   |  |  |  |

On the Z8S180 and Z8L180-class processors are quadruple buffered. The ASCI Receive Data Register is a read-only register. However, if RDRF =

## ASCI to/from DMAC Operation

Operation of the ASCI with the on-chip DMAC channel 0 requires that the DMAC be correctly configured to use the ASCI flags as DMA request signals.

## **ASCI and RESET**

During RESET, the ASCI status and control registers are initialized as defined in the individual register descriptions.

Receive and Transmit operations are stopped during RESET. However, the contents of the transmit and receive data registers (TDR and RDR) are not changed by RESET.

#### **ASCI Clock**

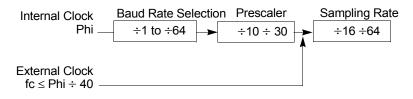

When in external clock input mode, the external clock is directly input to the sampling rate  $(\div 16/\div 64)$  as depicted in Figure 56.

Figure 56. ASCI Clock

153

#### **CSI/O and RESET**

During RESET each bit in the CNTR is initialized as defined in the CNTR register description. CSI/O transmit and receive operations in progress are aborted during RESET. However, the contents of TRDR are not changed.

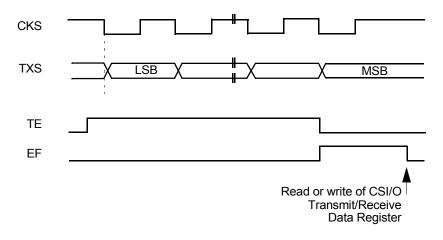

Figure 59. Transmit Timing Diagram–Internal Clock

158

return accurate data without requiring the timer to be stopped. The write procedure requires the PRT to be stopped.

For reading (without stopping the timer), TMDR is read in the order of lower byte - higher byte (TMDRnL, TMDRnH). The lower byte read (TMDRnL) stores the higher byte value in an internal register. The following higher byte read (TMDRnH) accesses this internal register. This procedure insures timer data validity by eliminating the problem of potential 16-bit timer updating between each 8-bit read. Specifically, reading TMDR in higher byte–lower byte order may result in invalid data. Note the implications of TMDR higher byte internal storage for applications which may read only the lower and/or higher bytes. In normal operation all TMDR read routines must access both the lower and higher bytes, in that order. For writing, the TMDR down counting must be inhibited using the TDE (Timer Down Count Enable) bits in the TCR (Timer Control Register). Then, any or both higher and lower bytes of TMDR can be freely written (and read) in any order.

## CSI/O Transmit/Receive Data Register (TRDR: I/O Address = 0BH).

TRDR is used for both CSI/O transmission and reception. Thus, the system design must insure that the constraints of half-duplex operation are met (Transmit and receive operation cannot occur simultaneously). For example, if a CSI/O transmission is attempted while the CSI/O is receiving data, the CSI/O does not work.

TRDR is not buffered. Attempting to perform a CSI/O transmit while the previous transmit data is still being shifted out causes the shift data to be immediately updated, thereby corrupting the transmit operation in progress. Similarly, reading TRDR during a transmit or receive must be avoided.

161

## Timer Reload Register Channel 1L (RLDR1L: 16H)

| Bit              | 7                                                                   | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------------|---------------------------------------------------------------------|-------------------|---|---|---|---|---|---|--|--|--|

| Bit/Field        |                                                                     | Timer Reload Data |   |   |   |   |   |   |  |  |  |

| R/W              |                                                                     | R/W               |   |   |   |   |   |   |  |  |  |

| Reset            |                                                                     | 0                 |   |   |   |   |   |   |  |  |  |

| Note: $R = Real$ | Note: $R = Read$ $W = Write$ $X = Indeterminate$ ? = Not Applicable |                   |   |   |   |   |   |   |  |  |  |

## Timer Reload Register Channel 1H (RLDR1H: 17H)

| Bit                                                             | 7 | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------------------------------------------------------|---|-------------------|---|---|---|---|---|---|--|--|--|

| Bit/Field                                                       |   | Timer Reload Data |   |   |   |   |   |   |  |  |  |

| R/W                                                             |   | R/W               |   |   |   |   |   |   |  |  |  |

| Reset                                                           |   | 0                 |   |   |   |   |   |   |  |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |                   |   |   |   |   |   |   |  |  |  |

# **Timer Control Register (TCR)**

TCR monitors both channels (PRT0, PRT1) TMDR status. It also controls enabling and disabling of down counting and interrupts along with controlling output pin A18/TOUT for PRT1.

#### Timer Control Register (TCR: 10H)

| Bit            | 7                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|----------------|---------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Bit/Field      | TIF1                                                          | TIF0 | TIE1 | TIE0 | TOC1 | TOC0 | TDE1 | TDE0 |  |  |

| R/W            | R                                                             | R    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| Reset          | 0                                                             | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| Note: $R = Re$ | Note: R = Read W = Write X = Indeterminate ? = Not Applicable |      |      |      |      |      |      |      |  |  |

## **Addressing Modes**

The Z80180 instruction set includes eight addressing modes.

- Implied Register

- Register Direct

- Register Indirect

- Indexed

- Extended

- Immediate

- Relative

- IO

# **Implied Register (IMP)**

Certain Op Codes automatically imply register usage, such as the arithmetic operations that inherently reference the Accumulator, Index Registers, Stack Pointer, and General Purpose Registers.

# **Register Direct (REG)**

Many Op Codes contain bit fields specifying registers used for operation. The exact bit field definitions vary depending on instruction depicted in Figure 75.

186

# **Z80180 DC CHARACTERISTICS**

$V_{CC}$  = 5V ± 10%,  $V_{SS}$  = OV, Ta = 0° to +70°C, unless otherwise noted.)

Table 28. Z80180 DC Characteristics

| Symbol          | Item                                                      | Condition                             | Minimum                     | Typical        | Maximum                                | Unit           |

|-----------------|-----------------------------------------------------------|---------------------------------------|-----------------------------|----------------|----------------------------------------|----------------|

| VIH1            | Input High Voltage<br>RESET, EXTAL NMI                    |                                       | V <sub>CC</sub> –0.6        | _              | V <sub>CC</sub> +0.3                   | V              |

| VIH2            | Input High Voltage<br>except RESET, EXTAL<br>NMI          |                                       | 2.0                         |                | V <sub>CC</sub> +0.3                   | V              |

| VIL1            | Input Low Voltage<br>RESET, EXTAL NMI                     |                                       | -0.3                        |                | 0.6                                    | V              |

| VIL2            | Input Low Voltage<br>except RESET, EXTAL<br>NMI           |                                       | -0.3                        |                | 0.8<br>Standard<br>7 TL <sub>VIL</sub> | V              |

| VOH             | Output High Voltage<br>all outputs                        | IOH = -200 μA<br>IOH = -20 μA         | 2.4<br>V <sub>CC</sub> –1.2 | _              | -                                      | V<br>V         |

| VOL             | Output Low Voltage<br>all outputs                         | IOL = 2.2  mA                         | _                           | _              | 0.45                                   | V              |

| I <sub>IL</sub> | Input Leakage Current<br>all inputs except XTAL,<br>EXTAL | $V_{IN} = 0.5 \sim$<br>$V_{CC} - 0.5$ | -                           | _              | 1.0                                    | μA             |

| ITL             | Three-State Leakage<br>Current                            |                                       | _                           | _              | 1.0                                    | μΑ             |

| ICC             | Power Dissipation*<br>(Normal Operation)                  | f = 6 MHz<br>f = 8 MHz<br>f = 33 MHz  | -                           | 15<br>20<br>25 | 40<br>50<br>60                         | mA<br>mA<br>mA |

206

#### Table 38. Arithmetic and Logical Instructions (8-bit) (Continued)

|                   |              |            |       |            |     |     |      |     |     |       | Flag   |                                  |   | ags | ls |     |   |   |

|-------------------|--------------|------------|-------|------------|-----|-----|------|-----|-----|-------|--------|----------------------------------|---|-----|----|-----|---|---|

|                   |              |            |       | Addressing |     |     |      |     |     | 7     | 6      | 4                                | 2 | 1   | 0  |     |   |   |

| Operation<br>Name | Mnemonics    | Op Code    | Immed | Ext        | Ind | Reg | Regi | Imp | Rel | Bytes | States | Operation                        | s | z   | н  | P/V | N | с |

|                   | XOR (IY + d) | 11 111 101 |       |            | s   |     |      | D   |     | 3     | 14     | Ar⊕ + (IY + d)) <sub>M</sub> →Ar | ↑ | ↑   | R  | Ρ   | R | R |

|                   |              | 10 101 110 |       |            |     |     |      |     |     |       |        |                                  |   |     |    |     |   |   |

|                   |              | <d></d>    |       |            |     |     |      |     |     |       |        |                                  |   |     |    |     |   |   |

Table 39.

Rotate and Shift Instructions

|                   |             |             |       |     |     |        |      |     |     |       |            |                   |   |   | F | lags |   |   |

|-------------------|-------------|-------------|-------|-----|-----|--------|------|-----|-----|-------|------------|-------------------|---|---|---|------|---|---|

|                   |             |             |       |     | Add | Iressi | ing  |     |     |       |            |                   | 7 | 6 | 4 | 2    | 1 | 0 |

| Operation<br>Name | Mnemonics   | Op Code     | Immed | Ext | Ind | Reg    | Regi | Imp | Rel | Bytes | State<br>s | Operation         | s | z | н | P/V  | N | с |

| Rotate            | RL A        | 00 010 1111 |       |     |     |        |      | S/D |     | 1     | 3          |                   | • | • | R | •    | R | ↑ |

| and<br>Shift      | RL g        | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          |                   | ↑ | ↑ | R | Р    | R | ↑ |

| Data              |             | 00 010 g    |       |     |     |        |      |     |     |       |            | C b7 b0           |   |   |   |      |   |   |

|                   | RL (HL)     | 11 001 011  |       |     |     |        | S/D  |     |     | 2     | 13         | 0 0/              | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 00 010 110  |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   | RL (IX + d) | 11 011 101  |       |     | S/D |        |      |     |     | 4     | 19         |                   | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 11 001 011  |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   |             | <d></d>     |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   |             | 00 010 110  |       |     |     |        |      |     |     |       |            | Ţ,                |   |   |   |      |   |   |

|                   | RL (IY + d) | 11 111 101  |       |     | S/D |        |      |     |     | 4     | 19         | Ar                | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 11 001 011  |       |     |     |        |      |     |     |       |            | b7 b0             |   |   |   |      |   |   |

|                   |             | <d></d>     |       |     |     |        |      |     |     |       |            | Ĭ <u></u>         |   |   |   |      |   |   |

|                   |             | 00 010 110  |       |     |     |        |      |     |     |       |            | (HL) <sub>M</sub> | 1 |   |   |      |   |   |

|                   | RLC A       | 00 000 111  |       |     |     |        |      | S/D |     | 1     | 3          | b7 b0             | • | • | R |      | R | ↑ |

|                   | RLC g       | 11 001 011  |       |     |     | S/D    |      |     |     | 2     | 7          |                   | ↑ | ↑ | R | Ρ    | R | ↑ |

|                   |             | 00 000 g    |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

|                   | RLC (HL)    | 11 001 011  |       |     |     |        | S/D  |     |     | 2     | 13         | b7 🗲 b0 C         | ↑ | ↑ | R | Р    | R | ↑ |

|                   |             | 00 000 110  |       |     |     |        |      |     |     |       |            |                   |   |   |   |      |   |   |

271

| Instruction             | Machine<br>Cycle                                                                                                                                                                                                             | States | Address                        | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT                                                                                                                                                                                                              | ST |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|----------------|----|----|------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                         | MC1                                                                                                                                                                                                                          | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                 | 0  |

| OTIMR**                 | MC2                                                                                                                                                                                                                          | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                 | 1  |

| OTDMR**                 | MC3                                                                                                                                                                                                                          | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1                                                                                                                                                                                                                 | 1  |

| (if Br= 0)              | MC4                                                                                                                                                                                                                          | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1                                                                                                                                                                                                                 | 1  |

|                         | MC5                                                                                                                                                                                                                          | T1T2T3 | C to A0~A7<br>00H to<br>A8~A15 | DATA           | 1  | 0  | 1    | 0    | 1         | 1                                                                                                                                                                                                                 | 1  |

|                         | MC6                                                                                                                                                                                                                          | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1                                                                                                                                                                                                                 | 1  |

|                         | MC1                                                                                                                                                                                                                          | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                 | 0  |

| OUTI<br>OUTD            | MC0     II     II     II     II     II       MC1     T1T2T3     1st Op Code<br>Address     1st Op<br>Code     0     1     0     1       MC2     T1T2T3     2nd Op Code<br>Address     2nd Op<br>Code     0     1     0     1 | 1      | 0                              | 1              | 1  |    |      |      |           |                                                                                                                                                                                                                   |    |

|                         | MC3                                                                                                                                                                                                                          | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1                 | 1  |

|                         | MC4                                                                                                                                                                                                                          | T1T2T3 | BC                             | DATA           | 1  | 0  | 1    | 0    | 1         | 1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 | 1  |

|                         | MC1                                                                                                                                                                                                                          | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                 | 0  |

| OTIR<br>OTDR            | MC2                                                                                                                                                                                                                          | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                 | 1  |

| $(\text{If Br} \neq 0)$ | MC3                                                                                                                                                                                                                          | T1T2T3 | HL                             | DATA           | 0  | 1  | 0    | 1    | 1         | 1                                                                                                                                                                                                                 | 1  |

|                         | MC4                                                                                                                                                                                                                          | T1T2T3 | BC                             | DATA           | 1  | 0  | 1    | 0    | 1         | 1                                                                                                                                                                                                                 | 1  |

|                         | MC5~M<br>C6                                                                                                                                                                                                                  | TiTi   | *                              | Z              | 1  | 1  | 1    | 1    | 1         | 1                                                                                                                                                                                                                 | 1  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

275

| Instruction                                                             | Machine<br>Cycle | States        | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------------------------------------------------------------------|------------------|---------------|------------------------|----------------|----|----|------|------|-----------|------|----|

| RLC (HL)                                                                | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RL (HL)<br>RRC (HL)<br>RR (HL)                                          | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| SLA (HL)<br>SRA (HL)                                                    | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| SRA (HL)<br>SRL (HL)                                                    | MC4              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC5              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

| $\frac{\text{RLC (IX + d)}}{\text{RLC (IY + d)}}$                       | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RL (IX + d) $RL (IY + d)$ $RRC (IX + d)$                                | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2ndOp<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| RRC (IY + d) $RR (IX + d)$ $RR (IY + d)$                                | MC3              | T1T2T3        | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| $\frac{RR(IY + d)}{SLA(IX + d)}$ $\frac{SLA(IY + d)}{SLA(IY + d)}$      | MC4              | T1T2T3        | 3rd Op Code<br>Address | 3rd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| $\frac{SRA (IX + d)}{SRA (IY + d)}$ $\frac{SRL (IX + d)}{SRL (IX + d)}$ | MC5              | T1T2T3        | IX+d<br>IY+d           | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| SRL (IY + d)<br>SRL (IY + d)                                            | MC6              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC7              | T1T2T3        | IX+d<br>IY+d           | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                                                                         | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RLD                                                                     | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| RRD                                                                     | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                                                                         | MC4~M<br>C7      | TiTiTiTi<br>* |                        | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC8              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

# 281

# **Operating Modes Summary**

Т

Г

# **REQUEST ACCEPTANCES IN EACH OPERATING MODE**

Т

| Current<br>Status<br>Request                                                  | Normal<br>Operation<br>(CPU mode<br>and IOSTOP<br>Mode)    | WAIT State                                                   | Refresh<br>Cycle                                                                           | Interrupt<br>Acknowledge<br>Cycle                      | DMA Cycle                                                     | BUS<br>RELEASE<br>Mode                                                                       | SLEEP<br>Mode                                                         | SYSTEM<br>STOP<br>Mode                                                     |

|-------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|

| WAIT                                                                          | Acceptable                                                 | Acceptable                                                   | Not<br>acceptable                                                                          | Acceptable                                             | Acceptable                                                    | Not<br>acceptable                                                                            | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| Refresh Request<br>Request of Refresh<br>by the on-chip<br>Refresh Controller | end of Machine                                             |                                                              | Not<br>acceptable                                                                          | Refresh cycle<br>begins at the<br>end MC               | Refresh cycle<br>begins at the<br>end of MC                   | Not<br>acceptable                                                                            | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| DREQ0<br>DREQ1                                                                | DMA cycle<br>begins at the<br>end of MC                    | DMA cycle<br>begins at the<br>end of MC                      | Acceptable<br>Refresh cycle<br>precedes.<br>DMA cycle<br>begins at the<br>end of one<br>MC | Acceptable<br>DMA cycle<br>begins at the<br>end of MC. | Acceptable<br>Refer to<br>"DMA<br>Controller"<br>for details. | Acceptable<br>*After BUS<br>RELEASE<br>cycle, DMA<br>cycle begins<br>at the end of<br>one MC | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| BUSREQ                                                                        | Bus is released<br>at the end of<br>MC                     | Not<br>acceptable                                            | Not<br>acceptable                                                                          | Bus is released<br>at the end of<br>MC                 | Bus is<br>released at the<br>end of MC                        | Continue<br>BUS<br>RELEASE<br>mode                                                           | Acceptable                                                            | Acceptable                                                                 |

| Interrupt INTO,<br>INT1,<br>INT2                                              | Accepted after<br>executing the<br>current<br>instruction. | Accepted<br>after<br>executing the<br>current<br>instruction | Not<br>acceptable                                                                          | Not<br>acceptable                                      | Not<br>acceptable                                             | Not<br>acceptable                                                                            | Acceptable<br>Return from<br>SLEEP<br>mode to<br>normal<br>operation. | Acceptable<br>Return from<br>SYSTEM<br>STOP mode<br>to normal<br>operation |

Table 53.

Request Acceptances in Each Operating Mode

T

1

т

Т