#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Active                                                 |

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 10MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 80-BQFP                                                |

| Supplier Device Package         | 80-QFP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018010fsg |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

5

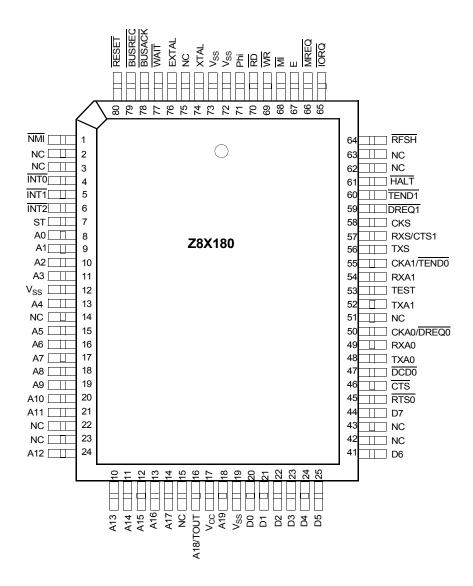

Figure 3. 80-Pin QFP

• Data Bus, 3-state

SLEEP mode is exited in one of two ways as described below.

- RESET Exit from SLEEP mode. If the RESET input is held Low for at least six clock cycles, it exits SLEEP mode and begins the normal RESET sequence with execution starting at address (logical and physical) 00000H.

- Interrupt Exit from SLEEP mode. The SLEEP mode is exited by detection of an external (NMI, INT0, INT2) or internal (ASCI, CSI/O, PRT) interrupt.

In case of  $\overline{\text{NMI}}$ , SLEEP mode is exited and the CPU begins the normal  $\overline{\text{NMI}}$  interrupt response sequence.

In the case of all other interrupts, the interrupt response depends on the state of the global interrupt enable flag IEF1 and the individual interrupt source enable bit.

If the individual interrupt condition is disabled by the corresponding enable bit, occurrence of that interrupt is ignored and the CPU remains in the SLEEP mode.

Assuming the individual interrupt condition is enabled, the response to that interrupt depends on the global interrupt enable flag (IEF1). If interrupts are globally enabled (IEF1 is 1) and an individually enabled interrupt occurs, SLEEP mode is exited and the appropriate normal interrupt response sequence is executed.

If interrupts are globally disabled (IEF1 is 0) and an individually enabled interrupt occurs, SLEEP mode is exited and instruction execution begins with the instruction following the SLP instruction. This feature provides a technique for synchronization with high speed external events without incurring the latency imposed by an interrupt response sequence.

Figure 21 depicts SLEEP timing.

42

To avoid address conflicts with external I/O, the Z8X180 internal I/O addresses can be relocated on 64-byte boundaries within the bottom 256 bytes of the 64KB I/O address space.

## I/O Control Register (ICR)

ICR allows relocating of the internal I/O addresses. ICR also controls enabling/disabling of the IOSTOP mode.

I/O Control Register (ICR: 3FH)

| Bit                                                         | 7    | 6    | 5     | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------------------------------------------------------------|------|------|-------|---|---|---|---|---|--|--|--|

| Bit/Field                                                   | IOA7 | IOA6 | IOSTP |   |   |   |   | — |  |  |  |

| R/W                                                         | R/W  | R/W  | R/W   |   |   |   |   |   |  |  |  |

| Reset                                                       | 0    | 0    | 0     |   |   |   |   |   |  |  |  |

| R = Read $W = Write$ $X = Indeterminate$ ? = Not Applicable |      |      |       |   |   |   |   |   |  |  |  |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                            |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6             | IOA7:6    | R/W |       | IOA7 and IOA6 relocate internal I/O as depicted in<br>Figure . The high-order 8 bits of 16-bit internal I/O<br>addresses are always 0. IOA7 and IOA6 are cleared to 0<br>during RESET. |

| 5               | IOSTP     | R/W |       | IOSTOP mode is enabled when IOSTP is set to 1.<br>Normal. I/O operation resumes when IOSTP is reset to 0.                                                                              |

|        |                        |          | A          | ldress     |      |

|--------|------------------------|----------|------------|------------|------|

|        | Register               | Mnemonic | Binary     | Hex        | Page |

| Timer  | Data Register Ch 0 L   | TMDR0L   | XX001100   | 0CH        | 159  |

|        | Data Register Ch 0 H   | TMDR0H   | XX001101   | 0DH        | 159  |

|        | Reload Register Ch 0 L | RLDR0L   | XX001110   | 0EH        | 159  |

|        | Reload Register Ch 0 H | RLDR0H   | XX001111   | 0FH        | 159  |

|        | Timer Control Register | TCR      | XX010000   | 10H        | 161  |

|        | Reserved               |          | XX010001   | 11H        |      |

|        |                        |          | $\uparrow$ | $\uparrow$ |      |

|        |                        |          | XX010011   | 13H        |      |

|        | Data Register Ch 1 L   | TMDR1L   | XX010100   | 14H        | 160  |

|        | Data Register Ch 1 H   | TMDR1H   | XX010101   | 15H        | 160  |

|        | Reload Register Ch 1 L | RLDR1L   | XX010110   | 16H        | 159  |

|        | Reload Register Ch 1 H | RLDR1H   | XX010111   | 17H        | 159  |

| Others | Free Running Counter   | FRC      | XX011000   | 18H        | 172  |

|        | Reserved               |          | XX011001   | 19H        |      |

|        |                        |          | $\uparrow$ | $\uparrow$ |      |

|        |                        |          | XX011111   | 1FH        |      |

#### Table 6. I/O Address Map for Z80180-Class Processors Only (Continued)

57

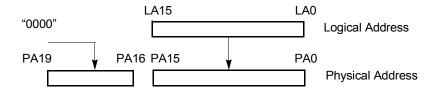

Whether address translation (Figure 26) takes place depends on the type of CPU cycle as follows.

Memory Cycles

Address Translation occurs for all memory access cycles including instruction and operand fetches, memory data reads and writes, hardware interrupt vector fetch, and software interrupt restarts.

• I/O Cycles

The MMU is logically bypassed for I/O cycles. The 16-bit logical I/O address space corresponds directly with the 16-bit physical I/O address space. The four high-order bits (A16–A19) of the physical address are always 0 during I/O cycles.

Figure 26. I/O Address Translation

• DMA Cycles

When the Z8X180 on-chip DMAC is using the external bus, the MMU is physically bypassed. The 20-bit source and destination registers in the DMAC are directly output on the physical address bus (A0–A19).

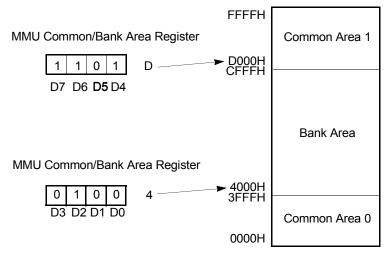

## **MMU Registers**

Three MMU registers are used to program a specific configuration of logical and physical memory.

Figure 28. Logical Space Configuration (Example)

59

UM005003-0703

85

Z8X180. Figure 43 illustrates the INT1, INT2 and internal interrupts timing.

| Machine |        |                |         |    |    |      | Γ    | MI    |       |      |    |

|---------|--------|----------------|---------|----|----|------|------|-------|-------|------|----|

| Cycle   | States | Address        | Data    | RD | WR | MREQ | IORQ | M1E=1 | M1E=0 | HALT | ST |

| 1       | T1-T3  | 1st<br>Op Code | EDH     | 0  | 1  | 0    | 1    | 0     | 1     | 1    | 0  |

| 2       | TI-T3  | 2nd<br>Op Code | 4DH     | 0  | 1  | 0    | 1    | 0     | 1     | 1    | 1  |

| 3       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 4       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 5       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 6       | T1-T3  | 1st<br>Op Code | EDH     | 0  | 1  | 0    | 1    | 0     | 0     | 1    | 1  |

| 7       | T1     | Don't<br>Care  | 3-state | 1  | 1  | 1    | 1    | 1     | 1     | 1    | 1  |

| 8       | T1-T3  | 2nd<br>Op Code | 4DH     | 0  | 1  | 0    | 1    | 0     | 1     | 1    | 1  |

| 9       | T1-T3  | SP             | data    | 0  | 1  | 0    | 1    | 1     | 1     | 1    | 1  |

| 10      | T1-T3  | SP+1           | data    | 0  | 1  | 0    | 1    | 1     | 1     | 1    | 1  |

Table 10.

RETI Control Signal States

IOC affects the IORQ/RD signals. M1E affects the assertion of M1. One state also reflects a 1 while the other reflects a 0  $\,$

DREQ Input

Level- and edge-sense DREQ input detection are selectable.

TEND Output Used to indicate DMA completion to external devices.

• Transfer Rate

Each byte transfer occurs every 6 clock cycles. Wait States can be inserted in DMA cycles for slow memory or I/O devices. At the system clock ( $\phi$ ) = 6 MHz, the DMA transfer rate is as high as 1.0 megabytes/second (no Wait States).

There is an additional feature disc for DMA interrupt request by DMA END. Each channel has the following additional specific capabilities:

## Channel 0

- Memory to memory

- Memory to I/O

- Memory to memory mapped I/O transfers.

- Memory address increment, decrement, no-change

- Burst or cycle steal memory to/from memory transfers

- DMA to/from both ASCI channels

- Higher priority than DMAC channel 1

## Channel 1

- Memory to/from I/O transfer

- Memory address increment, decrement

## **DMAC Registers**

Each channel of the DMAC (channel 0, 1) contains three registers specifically associated with that channel.

| Bit           | 7                                                             | 6   | 5      | 4   | 3   | 2   | 1   | 0   |  |  |  |  |  |

|---------------|---------------------------------------------------------------|-----|--------|-----|-----|-----|-----|-----|--|--|--|--|--|

| Bit/Field     | MPBT                                                          | MP  | CTS/PS | PE0 | DR  | SS2 | SS1 | SS0 |  |  |  |  |  |

| R/W           | R/W                                                           | R/W | R/W    | R/W | R/W | R/W | R/W | R/W |  |  |  |  |  |

| Reset         | Х                                                             | 0   | 0      | 0   | 0   | 1   | 1   | 1   |  |  |  |  |  |

| Note: R = Rea | Note: R = Read W = Write X = Indeterminate ? = Not Applicable |     |        |     |     |     |     |     |  |  |  |  |  |

## ASCI Control Register B 0 (CNTLB0: 02H) ASCI Control Register B 1 (CNTLB1: 03H)

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7               | MPBT      | R/W |       | <b>Multiprocessor Bit Transmit</b> — When multiprocessor<br>communication format is selected (MP bit is 1), MPBT is<br>used to specify the MPB data bit for transmission. If<br>MPBT is 1, then MPB = 1 is transmitted. If MPBT is 0,<br>then MPBT = 0 is transmitted. MPBT state is undefined<br>during and after RESET.                                                                                                                                                                       |

| 6               | MP        | R/W |       | <b>Multiprocessor Mode</b> — When MP is set to 1, the data<br>format is configured for multiprocessor mode based on<br>the MOD2 (number of data bits) and MOD0 (number of<br>stop bits) bits in CNTLA. The format is as follows.<br>Start bit + 7 or 8 data bits + MPB bit + 1 or 2 stop bits<br>Multiprocessor (MP = 1) format has no provision for<br>parity. If MP is 0, the data format is based on MOD0<br>MOD1, MOD2, and may include parity. The MP bit is<br>cleared to 0 during RESET. |

172

## Miscellaneous

## **Free Running Counter (I/O Address = 18H)**

If data is written into the free running counter, the interval of DRAM refresh cycle and baud rates for the ASCI and CSI/O are not guaranteed.

In IOSTOP mode, the free running counter continues counting down. It is initialized to FFH during RESET.

Free Running counter (FRC: 18H)

| Bit                                                             | 7 | 6 5           |  | 4 | 3 | 2 | 1 | 0 |  |  |  |  |  |  |

|-----------------------------------------------------------------|---|---------------|--|---|---|---|---|---|--|--|--|--|--|--|

| Bit/Field                                                       |   | Counting Data |  |   |   |   |   |   |  |  |  |  |  |  |

| R/W                                                             |   | R             |  |   |   |   |   |   |  |  |  |  |  |  |

| Reset                                                           | ? |               |  |   |   |   |   |   |  |  |  |  |  |  |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |   |               |  |   |   |   |   |   |  |  |  |  |  |  |

187

Table 28.

Z80180 DC Characteristics (Continued)

| Symbol                                                                                                                          | Item                                     | Condition                               | Minimum     | Typical         | Maximum              | Unit           |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|-------------|-----------------|----------------------|----------------|--|--|--|

|                                                                                                                                 | Power Dissipation*<br>(SYSTEM STOP mode) | f = 6 MHz<br>f = 8 MHz<br>f = 33 MHz    | _<br>_<br>_ | 3.8<br>5<br>6.3 | 12.5<br>15.0<br>17.5 | mA<br>mA<br>mA |  |  |  |

| СР                                                                                                                              | Pin Capacitance                          | $VIN = 0V, f = 1MHz$ $TA = 25^{\circ}C$ | _           | _               | 12                   | pF             |  |  |  |

| $TA = 25^{\circ}C$ Notes: * VIN min = V <sub>CC</sub> -1.0V. VIL max = 0.8V (All output terminals are a no load.)<br>VCC = 5.0V |                                          |                                         |             |                 |                      |                |  |  |  |

# **Z8S180 DC CHARACTERISTICS**

$V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = OV$ ,  $Ta = 0^{\circ}$  to  $+70^{\circ}C$ , unless otherwise noted.

Table 29. Z8S180 DC Characteristics

| Symbol | Item                                             | Condition | Minimum              | Typical | Maximum               | Unit |

|--------|--------------------------------------------------|-----------|----------------------|---------|-----------------------|------|

| VIH1   | Input High Voltage<br>RESET, EXTAL NMI           |           | V <sub>CC</sub> –0.6 | _       | V <sub>CC</sub> +0.3  | V    |

| VIH2   | Input High Voltage<br>except RESET, EXTAL<br>NMI |           | 2.0                  |         | V <sub>CC</sub> +0.3  | V    |

| VIH3   | Input High Voltage<br>CKS, CKA0, CKA1            |           | 2.4                  |         | V <sub>DD</sub> + 0.3 | V    |

| VIL1   | Input Low Voltage<br>RESET, EXTAL NMI            |           | -0.3                 |         | 0.6                   | V    |

| VIL2   | Input Low Voltage<br>except RESET, EXTAL<br>NMI  |           | -0.3                 |         | 0.8                   | V    |

193

# AC Characteristics

This section describes the AC characteristics of the Z8X180 family and absolute maximum rating for these products.

# AC CHARACTERISTICS—Z8S180

|     |                   |                                                                           |     | 180—20<br>/IHz |     | 180—33<br>MHz |      |

|-----|-------------------|---------------------------------------------------------------------------|-----|----------------|-----|---------------|------|

| No. | Symbol            | Item                                                                      | Min | Max            | Min | Max           | Unit |

| 1   | t <sub>CYC</sub>  | Clock Cycle Time                                                          | 50  | DC             | 30  | DC            | ns   |

| 2   | t <sub>CHW</sub>  | Clock "H" Pulse Width                                                     | 15  |                | 10  |               | ns   |

| 3   | t <sub>CLW</sub>  | Clock "L" Pulse Width                                                     | 15  |                | 10  |               | ns   |

| 4   | t <sub>CF</sub>   | Clock Fall Time                                                           |     | 10             |     | 5             | ns   |

| 5   | t <sub>CR</sub>   | Clock Rise Time                                                           |     | 10             |     | 5             | ns   |

| 6   | t <sub>AD</sub>   | PHI Rise to Address Valid Delay                                           |     | 30             |     | 15            | ns   |

| 7   | t <sub>AS</sub>   | Address Valid to MREQ Fall or IORQ Fall)                                  | 5   |                | 5   | —             | ns   |

| 8   | t <sub>MED1</sub> | PHI Fall to MREQ Fall Delay                                               |     | 25             |     | 15            | ns   |

| 9   | t <sub>RDD1</sub> | PHI Fall to $\overline{RD}$ Fall Delay $\overline{IOC} = 1$               | l — | 25             |     | 15            | ns   |

|     |                   | PHI Rise to $\overline{\text{RD}}$ Rise Delay $\overline{\text{IOC}} = 0$ | —   | 25             | _   | 15            | _    |

| 10  | t <sub>M1D1</sub> | PHI Rise to $\overline{M1}$ Fall Delay                                    |     | 35             |     | 15            | ns   |

| 11  | t <sub>AH</sub>   | Address Hold Time from<br>MREQ, IOREQ, RD, WR High                        | 5   |                | 5   |               | ns   |

Table 31.Z8S180 AC Characteristics $V_{DD} = 5V \pm 10\%$  or  $V_{DD} = 3.3V \pm 10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

#### I/O Write Cycle\* I/O Read Cycle\* Opcode Fetch Cycle $T_2$ T<sub>3</sub> $T_1$ $T_2$ T<sub>3</sub> $T_1$ Τ<sub>1</sub> Τw Tw 2 3 PHI ADDRESS М 20 20 19 19 WAIT MREQ 8 29 IORQ 11 28 13 RD 9 9 25-22 WR 26 14 M1 18 10 ST 16 15 Data IN 24 23 Data OUT 62 62-63 - 63 RESET 68 - 67 67 **⊢** 68

# **Timing Diagrams**

Figure 81. AC Timing Diagram 1

206

218

|                   |              |            |       |     |     |       |      |     |     |       |            | Γ         |            | F | lags |     |   |            |

|-------------------|--------------|------------|-------|-----|-----|-------|------|-----|-----|-------|------------|-----------|------------|---|------|-----|---|------------|

|                   |              |            |       |     | Add | ressi | ing  |     |     |       |            |           | 7          | 6 | 4    | 2   | 1 | 0          |

| Operation<br>Name | Mnemonics    | Op Code    | Immed | Ext | Ind | Reg   | Regi | Imp | Rel | Bytes | State<br>s | Operation | s          | z | н    | P/V | N | с          |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           | Γ          |   |      |     |   |            |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   |              | 00 001 110 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   | RRD          | 11 101 101 |       |     |     |       |      | S/D |     | 2     | 16         | <b>↓</b>  | $\uparrow$ | ↑ | R    | Р   | R | •          |

|                   |              | 01 100 111 |       |     |     |       |      |     |     |       |            | Ar        |            |   |      |     |   | Í          |

|                   | SLA g        | 11 001 011 |       |     |     | S/D   |      |     |     | 2     | 7          | b7 b0     | $\uparrow$ | ↑ | R    | Р   | R | $\uparrow$ |

|                   |              | 00 100 g   |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   | SLA (HL)     | 11 001 011 |       |     |     |       | S/D  |     |     | 2     | 13         | b7 b0     | ↑          | ↑ | R    | Р   | R | ↑          |

|                   |              | 00 100 110 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   | SLA (IX + d) | 11 011 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | ↑          | ↑ | R    | Р   | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            | C b7 b0   |            |   |      |     |   | Í          |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   |              | 00 100 110 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   | SLA (IY + d) | 11 111 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | ↑          | ↑ | R    | Р   | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   |              | 00 100 110 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   | SRA g        | 11 001 011 |       |     |     | S/D   |      |     |     | 2     | 7          | _         | $\uparrow$ | ↑ | R    | Р   | R | $\uparrow$ |

|                   |              | 00 101 g   |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   | Í          |

|                   | SRA (HL)     | 11 001 011 |       |     |     |       | S/D  |     |     | 2     | 13         | b7 b0 C   | $\uparrow$ | ↑ | R    | Р   | R | $\uparrow$ |

|                   |              | 00 101 110 |       |     |     |       |      |     |     |       |            | b7 b0 C   |            |   |      |     |   |            |

|                   | SRA (IX + d) | 11 011 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | $\uparrow$ | ↑ | R    | Р   | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   |              | 00 101 110 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   | SRA (IY + d) | 11 111 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | ↑          | ↑ | R    | Р   | R | ↑          |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   |              | 00 101 110 |       |     |     |       |      |     |     |       |            |           |            |   |      |     |   |            |

|                   | SRL g        | 11 001 011 |       |     |     | S/D   |      |     |     | 2     | 7          |           | ↑          | ↑ | R    | Р   | R | ↑          |

|                   |              | 00 111 g   |       |     |     |       |      |     |     |       |            | b7 b0 C   |            |   |      |     |   |            |

## Table 39. Rotate and Shift Instructions (Continued)

263

| Instruction            | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|------------------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

|                        | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| LD (IX+d),m            | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| LD (IY+d),m            | MC3              | T1T2T3 | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                        | MC4              | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                        | MC5              | T1T2T3 | IX+ d<br>IY+d          | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

| LD A, (BC)             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| LD A, (DE)             | MC2              | T1T2T3 | BC<br>DE               | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                        | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| LD A,(mn)              | MC2              | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                        | MC3              | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                        | MC4              | T1T2T3 | mn                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                        | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| LD (BC),A<br>LD (DE),A | MC2              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| X 12                   | MC3              | T1T2T3 | BC<br>DE               | А              | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

265

|             | Machine |        | 1                      |                | 1  |    |      | 1    | 1         | 1    | 1  |  |

|-------------|---------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|--|

| Instruction | Cycle   | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |  |

|             | MC1     | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |  |

| LD HL, (mn) | MC2     | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC3     | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC4     | T1T2T3 | mn                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC5     | T1T2T3 | mn+1                   | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC1     | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |  |

| LD ww,(mn)  | MC2     | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |  |

|             | MC3     | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC4     | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC5     | T1T2T3 | mn                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC6     | T1T2T3 | mn+ 1                  | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC1     | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |  |

| LD IX,(mn)  | MC2     | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |  |

| LD IY,(mn)  | MC3     | T1T2T3 | 1st operand<br>Address | n              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC4     | T1T2T3 | 2nd operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC5     | T1T2T3 | mn                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

|             | MC6     | T1T2T3 | mn+1                   | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

275

| Instruction                                                             | Machine<br>Cycle | States        | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------------------------------------------------------------------|------------------|---------------|------------------------|----------------|----|----|------|------|-----------|------|----|

| RLC (HL)                                                                | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RL (HL)<br>RRC (HL)<br>RR (HL)                                          | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| SLA (HL)<br>SRA (HL)                                                    | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| SRA (HL)<br>SRL (HL)                                                    | MC4              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC5              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

| $\frac{\text{RLC (IX + d)}}{\text{RLC (IY + d)}}$                       | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RL (IX + d) $RL (IY + d)$ $RRC (IX + d)$                                | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2ndOp<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| RRC (IX + d) $RRC (IY + d)$ $RR (IX + d)$ $RR (IY + d)$                 | MC3              | T1T2T3        | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| $\frac{RR(IY + d)}{SLA(IX + d)}$ $\frac{SLA(IY + d)}{SLA(IY + d)}$      | MC4              | T1T2T3        | 3rd Op Code<br>Address | 3rd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| $\frac{SRA (IX + d)}{SRA (IY + d)}$ $\frac{SRL (IX + d)}{SRL (IX + d)}$ | MC5              | T1T2T3        | IX+d<br>IY+d           | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| SRL (IY + d)<br>SRL (IY + d)                                            | MC6              | Ti            | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC7              | T1T2T3        | IX+d<br>IY+d           | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                                                                         | MC1              | T1T2T3        | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| RLD                                                                     | MC2              | T1T2T3        | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| RRD                                                                     | MC3              | T1T2T3        | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                                                                         | MC4~M<br>C7      | TiTiTiTi<br>* |                        | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                                                                         | MC8              | T1T2T3        | HL                     | DATA           | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

300

| Register                                                    | Mnemonics   | Addre      | Remarks             |                  |                     |                                     |                            |           |         |           |                     |

|-------------------------------------------------------------|-------------|------------|---------------------|------------------|---------------------|-------------------------------------|----------------------------|-----------|---------|-----------|---------------------|

| MMU Common Base                                             | CBR         | 3 8        |                     |                  |                     |                                     |                            | 1         | T       | 1         |                     |

| Register:                                                   |             |            | bit                 | CB7              | CB6                 | CB5                                 | CB4                        | CB3       | CB2     | CB1       | CB0                 |

|                                                             |             |            | during RESET        | 0                | 0                   | 0                                   | 0                          | 0         | 0       | 0         | 0                   |

|                                                             |             |            | R/W                 | R/W              | R/W                 | R/W                                 | R/W                        | R/W       | R/W     | R/W       | R/W                 |

|                                                             |             |            |                     |                  |                     |                                     |                            | Y         | MMU Co  | mmon Ba   | ise Regis           |

| MMU Bank Base Register                                      | BBR         | 3 9        |                     | BB7              | BB6                 | BB5                                 | BB4                        | BB3       | BB2     | BB1       | BB0                 |

|                                                             |             |            | bit<br>during RESET | 0                | 0                   | 0                                   | 0                          | 0         | 0       | 0         | 0                   |

|                                                             |             |            | R/W                 | R/W              | R/W                 | R/W                                 | R/W                        | R/W       | R/W     | R/W       | R/W                 |

|                                                             |             |            |                     |                  |                     |                                     |                            |           |         | I         |                     |

|                                                             |             |            |                     |                  |                     |                                     |                            |           | MMU Ba  | nk Base R | legister            |

| MMU Common/Bank<br>Register                                 | CBAR        | 3 A        | bit                 | CA3              | CA2                 | CA1                                 | CA0                        | BA3       | BA2     | BA1       | BA0                 |

|                                                             |             |            | during RESET        | 1                | 1                   | 1                                   | 1                          | 0         | 0       | 0         | 0                   |

|                                                             |             |            | R/W                 | R/W              | R/W                 | R/W                                 | R/W                        | R/W       | R/W     | R/W       | R/W                 |

|                                                             |             |            |                     |                  |                     |                                     |                            |           |         |           |                     |

|                                                             |             |            |                     |                  |                     | ммц                                 | J Commo                    | n Area Re | egister |           | U Bank<br>1 Registe |

|                                                             | OMCR        | 3 E        | bit                 | MIE              | MITE                |                                     | J Commo                    | n Area Re | egister |           | U Bank<br>1 Registe |

|                                                             | OMCR        | 3 E        | bit<br>during RESET | MIE              | MITE<br>1           |                                     | 1                          |           | -       | Area      | 1 Registe           |

|                                                             | OMCR        | 3 E        |                     |                  |                     | IOC                                 | _                          | _         | _       | Area      | Registe             |

|                                                             | OMCR        | 3 E        | during RESET        | 1                | 1<br>W              | IOC<br>1<br>R/W                     | l<br>I/O Comp              | l         | _       | Area      | Registe             |

|                                                             | OMCR        | 3 E        | during RESET        | l<br>R/W         | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l         | _       | Area      | Registe             |

| Register                                                    |             |            | during RESET        | l<br>R/W         | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              | l         | _       | Area      | Registe             |

| Register                                                    | OMCR<br>ICR | 3 E<br>3 F | during RESET<br>R/W | l<br>R/W         | 1<br>W<br>MI Enable | I<br>I<br>R/W<br>MI Temp            | 1<br>I/O Comp<br>orary Ena | l         | _       | Area      | I Registe           |

| Register                                                    |             |            | during RESET<br>R/W | l<br>R/W         | 1<br>W              | IOC<br>1<br>R/W<br>MI Temp          | l<br>I/O Comp              |           | 1       | Area      | Registe             |

| Operation Mode Control<br>Register<br>I/O Control Register: |             |            | during RESET<br>R/W | I<br>R/W<br>IOA7 | 1<br>W<br>MI Enable | IOC<br>1<br>R/W<br>MT Temp<br>IOSTP | I/O Comp<br>orary Ena      |           |         | Area      | 1 Registe           |

## Table 57. Internal I/O Registers (Continued)

I/O Address

| Register                  | Mnemonics | Ad | ldress |              |                 |           | Rei                | mark        | s      |          |       |            |

|---------------------------|-----------|----|--------|--------------|-----------------|-----------|--------------------|-------------|--------|----------|-------|------------|

| Interrupt Vector Low      | IL        | 3  | 3      |              |                 |           |                    |             |        |          |       |            |

| Register                  |           |    |        | bit          | IL7             | IL6       | IL5                | —           | —      | —        | —     | —          |

|                           |           |    |        | during RESET | 0               | 0         | 0                  | 0           | 0      | 0        | 0     | 0          |

|                           |           |    |        | R/W          | R/W             | R/W       | R/W                |             |        |          |       |            |

|                           |           |    |        |              |                 | Inter     | rupt Vecto         | or Low      |        |          |       |            |

| INT/TRAP Control          | ITC       | 3  | 4      | bit          | TRAP            | UF0       | _                  | —           | —      | ITE2     | ITE1  | ITE0       |

| Register                  |           |    |        | during RESET | 0               | 0         | 1                  | 1           | 1      | 0        | 0     | 0          |

|                           |           |    |        | R/W          | R/W             | R         |                    |             |        | R/W      | R/W   | R/W        |

|                           |           |    |        |              |                 | TRAP      | Unidentifi         | ied Fetch ( | Object | <u> </u> |       | INT Enable |

| Refresh Control Register: | RCR       | 3  | 6      | bit          | REFE            | REFW      | —                  | —           | —      | —        | CYC1  | CYC0       |

|                           |           | -  |        | during RESET | 1               | 1         | 1                  | 1           | 1      | 1        | 0     | 0          |

|                           |           |    |        | R/W          | R/W             | R/W       | r                  |             |        |          | R/W   | R/W        |

|                           |           |    |        |              |                 | Refresh E | Refresh W<br>nable | /ait State  |        |          | Cycle | select     |

|                           |           |    |        |              | Interval of     |           | lycle              |             |        |          |       |            |

|                           |           |    |        | 00001        | 10 states<br>20 |           |                    |             |        |          |       |            |

|                           |           |    |        | 10           | 40              |           |                    |             |        |          |       |            |

|                           |           |    |        | 11           | 80              |           |                    |             |        |          |       |            |

## Table 57. Internal I/O Registers (Continued)