#### Zilog - Z8018010PEC Datasheet

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                        |

|---------------------------------|--------------------------------------------------------|

| Product Status                  | Obsolete                                               |

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 10MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | -40°C ~ 100°C (TA)                                     |

| Security Features               | -                                                      |

| Package / Case                  | 64-DIP (0.750", 19.05mm)                               |

| Supplier Device Package         | 64-DIP                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018010pec |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z8018x Family MPU User Manual

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

ZiLOG Worldwide Headquarters 532 Race Street San Jose, CA 95126-3432 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

© 2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

|             | Table 23.  | Timer Output Control                        | 163 |

|-------------|------------|---------------------------------------------|-----|

|             | Table 24.  | E Clock Timing in Each Condition            | 166 |

|             | Table 25.  | Z8X180 Operating Frequencies                | 169 |

| Software A  | rchitectur | e                                           |     |

|             | Table 26.  | Instruction Set Summary                     |     |

| DC Charac   | eteristics |                                             |     |

|             | Table 27.  | Absolute Maximum Rating                     |     |

|             | Table 28.  | Z80180 DC Characteristics                   |     |

|             | Table 29.  | Z8S180 DC Characteristics                   |     |

|             | Table 30.  | Z8L180 DC Characteristics                   |     |

| AC Charac   | teristics  |                                             |     |

|             | Table 31.  | Z8S180 AC Characteristics                   | 193 |

| Instruction | Set        |                                             |     |

|             | Table 32.  | Register Values                             |     |

|             | Table 33.  | Bit Values                                  |     |

|             | Table 34.  | Instruction Values                          |     |

|             | Table 35.  | Address Values                              |     |

|             | Table 36.  | Flag Conditions                             |     |

|             | Table 37.  | Operations Mnemonics                        |     |

|             | Table 38.  | Arithmetic and Logical Instructions (8-bit) |     |

|             | Table 39.  | Rotate and Shift Instructions               |     |

|             | Table 40.  | Arithmetic Instructions (16-bit)            |     |

|             | Table 41.  | 8-Bit Load                                  |     |

|             | Table 42.  | 16-Bit Load                                 |     |

xvi

| Table 43.                 | Block Transfer                                            |

|---------------------------|-----------------------------------------------------------|

| Table 44.                 | Stock and Exchange                                        |

| Table 45.                 | Program Control Instructions                              |

| Table 46.                 | I/O Instructions                                          |

| Table 47.                 | Special Control Instructions                              |

| Op Code Map               |                                                           |

| Table 48.                 | 1st Op Code Map Instruction Format: XX                    |

| Table 49.                 | 2nd Op Code Map Instruction Format: CB XX 249             |

| Table 50.                 | 2nd Op Code Map Instruction Format: ED XX 250             |

| Bus Control Signal        | Conditions                                                |

| Table 51.                 | Bus and Control Signal Condition in Each<br>Machine Cycle |

| Table 52.                 | Interrupts                                                |

| <b>Operating Modes St</b> | ummary                                                    |

| Table 53.                 | Request Acceptances in Each Operating Mode                |

| Table 54.                 | The Z80180 Types of Requests 282                          |

| Status Signals 287        |                                                           |

| Table 55.                 | Pin Outputs in Each Operating Mode                        |

| Table 56.                 | Pin Status During RESET and<br>LOW POWER OPERATION Modes  |

| I/O Registers             |                                                           |

| Table 57.                 | Internal I/O Registers                                    |

- 3. Refresh cycles are suppressed during SLEEP mode. If a refresh cycle is requested during SLEEP mode, the refresh cycle request is internally *latched* (until replaced with the next refresh request). The latched refresh cycle is inserted at the end of the first machine cycle after SLEEP mode is exited. After this initial cycle, the time at which the next refresh cycle occurs depends on the refresh time and has no timing relationship with the exit from SLEEP mode.

- 4. Regarding (2) and (3), the refresh address is incremented by one for each successful refresh cycle, not for each refresh request. Thus, independent of the number of *missed* refresh requests, each refresh bus cycle uses a refresh address incremented by one from that of the previous refresh bus cycles.

# **DMA Controller (DMAC)**

The Z8X180 contains a two-channel DMA (Direct Memory Access) controller which supports high speed data transfer. Both channels (channel 0 and channel 1) feature the following capabilities:

Memory Address Space

Memory source and destination addresses can be directly specified anywhere within the 1024KB physical address space using 20-bit source and destination memory addresses. In addition, memory transfers can arbitrarily cross 64KB physical address boundaries without CPU intervention.

• I/O Address Space

I/O source and destination addresses can be directly specified anywhere within the 64KB I/O address space (16-bit source and destination I/O addresses).

• Transfer Length

Up to 64KB are transferred based on a 16- bit byte count register.

DREQ0 for ASCI transmission and reception respectively. To initiate memory to/from ASCI DMA transfer, perform the following operations:

- 1. Load the source and destination addresses into SAR0 and DAR0 Specify the I/O (ASCI) address as follows:

- a. Bits A0–A7 must contain the address of the ASCI channel transmitter or receiver (I/O addresses 6H-9H).

- b. Bits A8–A15 must equal 0.

- c. Bits SAR17–SAR16 must be set according to Table 16 to enable use of the appropriate ASCI status bit as an internal DMA request.

Table 16.DMA Transfer Request

| SAR18         | SAR17      | SAR16 | DMA Transfer Request  |

|---------------|------------|-------|-----------------------|

| Х             | 0          | 0     | DREQ0                 |

| Х             | 0          | 1     | RDRF (ASCI channel 0) |

| Х             | 1          | 0     | RDRF (ASCI channel 1) |

| Х             | 1          | 1     | Reserved              |

| Note: $X = I$ | Don't care | 1     | 1                     |

| DAR18         | DAR17      | DAR16 | DMA Transfer Request  |

|---------------|------------|-------|-----------------------|

| X             | 0          | 0     | DREQ0                 |

| Х             | 0          | 1     | TDRE (ASCI channel O) |

| Х             | 1          | 0     | TDRE (ASCI channel 1) |

| Х             | 1          | 1     | Reserved              |

| Note: $X = I$ | Don't care |       |                       |

## 110

117

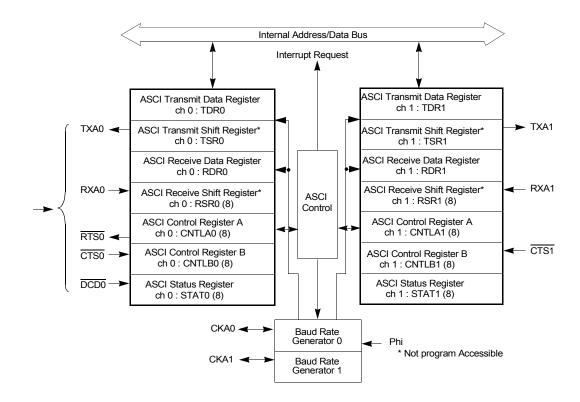

Figure 52. ASCI Block Diagram

### **ASCI Register Description**

The following subparagraphs explain the various functions of the ASCI registers.

#### ASCI Transmit Shift Register 0, 1 (TSR0, 1)

When the ASCI Transmit Shift Register receives data from the ASCI Transmit Data Register (TDR), the data is shifted out to the TXA pin.

123

#### ASCI Control Register A0, 1 (CNTLA0, 1)

Each ASCI channel Control Register A configures the major operating modes such as receiver/transmitter enable and disable, data format, and multiprocessor communication mode.

ASCI Status Register 1 (STAT1: 05H)

| Bit           | 7           | 6           | 5          | 4          | 3        | 2     | 1    | 0   |

|---------------|-------------|-------------|------------|------------|----------|-------|------|-----|

| Bit/Field     | RDRF        | OVRN        | PE         | FE         | RIE      | CTS1E | TDRE | TIE |

| R/W           | R           | R           | R          | R          | R/W      | R/W   | R    | R/W |

| Reset         | 0           | 0           | 0          | 0          | 0        | 0     | 0    | 0   |

| Note: R = Rea | ad $W = Wr$ | ite X = Ind | eterminate | ? = Not Ap | plicable |       |      |     |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7               | RDRF      | R   |       | <b>Receive Data Register Full</b> — RDRF is set to 1 when an incoming data byte is loaded into RDR. Note that if a framing or parity error occurs, RDRF is still set and the receive data (which generated the error) is still loaded into RDR. RDRF is cleared to 0 by reading RDR, when the DCD0 input is High, in IOSTOP mode, and during RESET. |

| 6               | OVRN      | R   |       | <b>Overrun Error</b> — OVRN is set to 1 when RDR is full<br>and RSR becomes full. OVRN is cleared to 0 when the<br>EFR bit (Error Flag Reset) of CNTLA is written to 0,<br>when DCD0 is High, in IOSTOP mode, and during<br>RESET.                                                                                                                  |

| 5               | PE        | R   |       | <b>Parity Error</b> — PE is set to 1 when a parity error is detected on an incoming data byte and ASCI parity detection is enabled (the MOD1 bit of CNTLA is set to 1). PE is cleared to 0 when the EFR bit (Error Flag Reset) of CNTLA is written to 0, when DCD0 is High, in IOSTOP mode, and during RESET.                                       |

133

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5               | CTS/PS    | R/W |       | Clear to Send/Prescale — When read, $\overline{\text{CTS}}/\text{PS}$ reflects<br>the state of the external $\overline{\text{CTS}}$ input. If the $\overline{\text{CTS}}$ input pin<br>is High, $\overline{\text{CTS}}/\text{PS}$ is read as 1. When the $\overline{\text{CTS}}$ input pin is<br>High, the TDRE bit is inhibited (that is, held at 0). For<br>channel 1, the $\overline{\text{CTS}}$ input is multiplexed with RXS pin<br>(Clocked Serial Receive Data). Thus, $\overline{\text{CTS}}/\text{PS}$ is only<br>valid when read if the channel 1 CTS1E bit is 1 and the<br>$\overline{\text{CST1}}$ input pin function is selected. The read data of<br>$\overline{\text{CTS}}/\text{PS}$ is not affected by RESET.<br>When written, $\overline{\text{CT}}/\text{PS}$ specifies the baud rate generator<br>prescale factor. If $\overline{\text{CTS}}/\text{PS}$ is set to 1, the system clock is<br>prescaled by 30 while if $\overline{\text{CTS}}/\text{PS}$ is cleared to 0, the<br>system clock is prescaled by 10.CTS/PS is cleared to 0<br>during RESET. |

| 4               | PEO       | R/W |       | <b>Parity Even Odd</b> — PE0 selects even or odd parity. PE0 does not affect the enabling/disabling of parity (MOD1 bit of CNTLA). If PE0 is cleared to 0, even parity is selected. If PE0 is set to 1, odd parity is selected.PE0 is cleared to 0 during RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3               | DR        | R/W |       | <b>Divide Ratio</b> — DR specifies the divider used to obtain<br>baud rate from the data sampling clock If DR is reset to 0,<br>divide by 16 is used, while if DR is set to 1, divide by 64<br>is used. DR is cleared to 0 during RESET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2–0             | SS2-0     | R/W |       | <b>Source/Speed Select</b> — Specifies the data clock source (internal or external) and baud rate prescale factor. SS2, SS1, and SS0 are all set to 1 during RESET. Table 18 describes the divide ratio corresponding to SS2, SS1 and SS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

The external ASCI channel 0 data clock pins are multiplexed with DMA control lines (CKA0/ $\overline{\text{DREQ}}$  and CKA1/ $\overline{\text{TEND0}}$ ). During RESET, these

| Pro | escaler         |    | npling<br>ate |     | Bau | d Rat | e               | General         | Baud             | Rate (Exa<br>(BPS) | mple)            | СКА  |                    |  |    |

|-----|-----------------|----|---------------|-----|-----|-------|-----------------|-----------------|------------------|--------------------|------------------|------|--------------------|--|----|

| PS  | Divide<br>Ratio | DR | Rate          | SS2 | SS1 | SS0   | Divide<br>Ratio | Divide<br>Ratio | φ = 6.144<br>MHz | φ = 4.608<br>MHz   | φ = 3.072<br>MHz | I/O  | Clock<br>Frequency |  |    |

|     |                 |    |               | 0   | 0   | 0     | ÷1              | φ ÷ 480         |                  | 9600               |                  |      | φ ÷ 30             |  |    |

|     |                 |    |               | 0   | 0   | 1     | 2               | 960             |                  | 4800               |                  |      | 60                 |  |    |

|     |                 |    |               | 0   | 1   | 0     | 4               | 1920            |                  | 2400               |                  |      | 120                |  |    |

|     |                 | 0  | 16            | 0   | 1   | 1     | 8               | 3840            |                  | 1200               |                  | 0    | 240                |  |    |

|     |                 |    |               | 1   | 0   | 0     | 16              | 7680            |                  | 600                |                  |      | 480                |  |    |

|     |                 |    |               | 1   | 0   | 1     | 32              | 15360           |                  | 300                |                  |      | 960                |  |    |

| 1   | φ ÷ 30          |    |               | 1   | 1   | 0     | 64              | 30720           |                  | 150                |                  |      | 1920               |  |    |

|     |                 |    |               | 1   | 1   | 1     | _               | fc ÷ 16         |                  | —                  | _                | Ι    | fc                 |  |    |

|     |                 |    |               | 0   | 0   | 0     | ÷1              | φ ÷ 1920        |                  | 2400               |                  |      | φ ÷ 30             |  |    |

|     |                 |    |               |     |     | 0     | 0               | 1               | 2                | 3840               |                  | 1200 |                    |  | 60 |

|     |                 |    |               | 0   | 1   | 0     | 4               | 7680            |                  | 600                |                  |      | 120                |  |    |

|     |                 | 1  | 64            | 0   | 1   | 1     | 8               | 15360           |                  | 300                |                  | 0    | 240                |  |    |

|     |                 |    |               | 1   | 0   | 0     | 16              | 30720           |                  | 150                |                  |      | 480                |  |    |

|     |                 |    |               | 1   | 0   | 1     | 32              | 61440           |                  | 75                 |                  |      | 960                |  |    |

|     |                 |    |               | 1   | 1   | 0     | 64              | 122880          |                  | 37.5               |                  |      | 1920               |  |    |

|     |                 |    |               | 1   | 1   | 1     | _               | fc ÷ 64         | _                |                    | _                | Ι    | fc                 |  |    |

Table 19.

ASCI Baud Rate Selection (Continued)

#### Baud Rate Generator (Z8S180/Z8L180-Class Processors Only)

The Z8S180/Z8L180 Baud Rate Generator (BRG) features two modes. The first is the same as in the Z80180. The second is a 16-bit down counter that divides the processor clock by the value in a 16-bit time constant register, and is identical to the DMSCC BRG. This feature allows

UM005003-0703

160

#### Timer Reload Register Channel 0L (RLDR0L: 0EH)

| Bit             | 7                                                                   | 7 6 5 4 3 2 1 0   |  |    |   |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------|-------------------|--|----|---|--|--|--|--|--|--|--|

| Bit/Field       |                                                                     | Timer Reload Data |  |    |   |  |  |  |  |  |  |  |

| R/W             |                                                                     |                   |  | R/ | W |  |  |  |  |  |  |  |

| Reset           |                                                                     | 0                 |  |    |   |  |  |  |  |  |  |  |

| Note: $R = Rea$ | Note: $R = Read$ $W = Write$ $X = Indeterminate$ ? = Not Applicable |                   |  |    |   |  |  |  |  |  |  |  |

#### Timer Reload Register Channel 0H (RLDR0L: 0FH)

| Bit           | 7         | 7 6 5 4 3 2 1 0 |            |             |           |  |  |  |  |  |  |  |

|---------------|-----------|-----------------|------------|-------------|-----------|--|--|--|--|--|--|--|

| Bit/Field     |           |                 |            | Timer Re    | load Data |  |  |  |  |  |  |  |

| R/W           |           |                 |            | R/          | W         |  |  |  |  |  |  |  |

| Reset         |           | 0               |            |             |           |  |  |  |  |  |  |  |

| Note: R = Rea | ad W = Wr | ite X = Ind     | eterminate | ? = Not App | plicable  |  |  |  |  |  |  |  |

## Timer Data Register 1L (TMDR1L: 14H)

| Bit             | 7           | 6           | 5          | 4          | 3        | 2 | 1 | 0 |  |  |  |  |

|-----------------|-------------|-------------|------------|------------|----------|---|---|---|--|--|--|--|

| Bit/Field       |             | Timer Data  |            |            |          |   |   |   |  |  |  |  |

| R/W             |             |             |            | R/         | W        |   |   |   |  |  |  |  |

| Reset           |             | 0           |            |            |          |   |   |   |  |  |  |  |

| Note: $R = Rea$ | ad $W = Wr$ | ite X = Ind | eterminate | ? = Not Ap | plicable |   |   |   |  |  |  |  |

#### Timer Data Register 1H (TMDR1H: 15H)

| Bit           | 7         | 6                                                | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |  |

|---------------|-----------|--------------------------------------------------|---|-------|------|---|---|---|--|--|--|--|

| Bit/Field     |           |                                                  |   | Timer | Data |   |   |   |  |  |  |  |

| R/W           |           | R/W                                              |   |       |      |   |   |   |  |  |  |  |

| Reset         |           |                                                  |   | (     | )    |   |   |   |  |  |  |  |

| Note: R = Rea | ad W = Wr | W = Write  X = Indeterminate  ? = Not Applicable |   |       |      |   |   |   |  |  |  |  |

187

Table 28.

Z80180 DC Characteristics (Continued)

| Symbol | Item                                     | Condition                               | Minimum      | Typical         | Maximum              | Unit           |

|--------|------------------------------------------|-----------------------------------------|--------------|-----------------|----------------------|----------------|

|        | Power Dissipation*<br>(SYSTEM STOP mode) | f = 6 MHz<br>f = 8 MHz<br>f = 33 MHz    | _<br>_<br>_  | 3.8<br>5<br>6.3 | 12.5<br>15.0<br>17.5 | mA<br>mA<br>mA |

| СР     | Pin Capacitance                          | $VIN = 0V, f = 1MHz$ $TA = 25^{\circ}C$ | _            | _               | 12                   | pF             |

|        | $VIN min = V_{CC} - 1.0V. V_{CC} = 5.0V$ | VIL max = 0.8V (All outp                | ut terminals | are a no        | load.)               |                |

## **Z8S180 DC CHARACTERISTICS**

$V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = OV$ ,  $Ta = 0^{\circ}$  to  $+70^{\circ}C$ , unless otherwise noted.

Table 29. Z8S180 DC Characteristics

| Symbol | Item                                             | Condition | Minimum              | Typical | Maximum               | Unit |

|--------|--------------------------------------------------|-----------|----------------------|---------|-----------------------|------|

| VIH1   | Input High Voltage<br>RESET, EXTAL NMI           |           | V <sub>CC</sub> –0.6 | _       | V <sub>CC</sub> +0.3  | V    |

| VIH2   | Input High Voltage<br>except RESET, EXTAL<br>NMI |           | 2.0                  |         | V <sub>CC</sub> +0.3  | V    |

| VIH3   | Input High Voltage<br>CKS, CKA0, CKA1            |           | 2.4                  |         | V <sub>DD</sub> + 0.3 | V    |

| VIL1   | Input Low Voltage<br>RESET, EXTAL NMI            |           | -0.3                 |         | 0.6                   | V    |

| VIL2   | Input Low Voltage<br>except RESET, EXTAL<br>NMI  |           | -0.3                 |         | 0.8                   | V    |

214

|                   |              |            |       |     |     |        |      |     |     |       |        |                                |   |   | FI | ags |   |            |

|-------------------|--------------|------------|-------|-----|-----|--------|------|-----|-----|-------|--------|--------------------------------|---|---|----|-----|---|------------|

|                   |              |            |       |     | Add | ressin | g    |     |     |       |        |                                | 7 | 6 | 4  | 2   | 1 | 0          |

| Operation<br>Name | Mnemonics    | Op Code    | Immed | Ext | Ind | Reg    | Regl | Imp | Rel | Bytes | States | Operation                      | s | z | н  | P/V | N | с          |

| OR                | OR g         | 10 110 g   |       |     |     | S      |      | D   |     | 1     | 4      | Ar + gr→Ar                     | ↑ | ↑ | R  | Ρ   | R | R          |

|                   | OR (HL)      | 10 110 110 |       |     |     |        | s    | D   |     | 1     | 6      | Ar + (HL) <sub>M</sub> →Ar     | ↑ | ↑ | R  | Р   | R | R          |

|                   | OR m         | 11 110 110 | s     |     |     |        |      | D   |     | 2     | 6      | Ar + m→Ar                      | ↑ | ↑ | R  | Р   | R | R          |

|                   |              | <m></m>    |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   | OR (IX + d)  | 11 011 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar + (IX + d) <sub>M</sub> →Ar | ↑ | ↑ | R  | Р   | R | R          |

|                   |              | 10 110 110 |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   | OR (IY + d)  | 11 111 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar + (IY + d) <sub>M</sub> →Ar | ↑ | ↑ | R  | Р   | R | R          |

|                   |              | 10 110 110 |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

| SUB               | SUB g        | 10 010 g   |       |     |     | s      |      | D   |     | 1     | 4      | Ar-gr→Ar                       | ↑ | ↑ | ↑  | v   | s | ↑          |

|                   | SUB (HL)     | 10 010 110 |       |     |     |        | s    | D   |     | 1     | 6      | Ar-(HL) <sub>M</sub> →Ar       | ↑ | ↑ | ↑  | v   | s | ↑          |

|                   | SUB m        | 11 010 110 | s     |     |     |        |      | D   |     | 2     | 6      | Ar-m→Ar                        | ↑ | ↑ | ↑  | v   | s | ↑          |

|                   |              | <m></m>    |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   | SUB (IX + d) | 11 011 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar-(IX + d) <sub>M</sub> -c→Ar | ↑ | ↑ | ↑  | v   | s | ↑          |

|                   |              | 10 011 110 |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   | SUB (IY + d) | 11 111 101 |       |     | s   |        |      | D   |     | 3     | 14     | Ar-(IY + d) <sub>M</sub> -c→Ar | ↑ | ↑ | ↑  | V   | s | $\uparrow$ |

|                   |              | 10 010 110 |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |        |                                |   |   |    |     |   |            |

# Table 38. Arithmetic and Logical Instructions (8-bit) (Continued)

217

|                   |              |            |       |     |     |        |      |     |     |       |            |                  |            |   | F | lags |   |            |

|-------------------|--------------|------------|-------|-----|-----|--------|------|-----|-----|-------|------------|------------------|------------|---|---|------|---|------------|

|                   |              |            |       |     | Add | Iressi | ing  |     |     |       |            |                  | 7          | 6 | 4 | 2    | 1 | 0          |

| Operation<br>Name | Mnemonics    | Op Code    | Immed | Ext | Ind | Reg    | Regi | Imp | Rel | Bytes | State<br>s | Operation        | s          | z | н | P/V  | N | с          |

|                   | RLC (IX + d) | 11 011 101 |       |     | S/D |        |      |     |     | 4     | 19         |                  | $\uparrow$ | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | 00 000 110 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RLC (IY + d) | 11 111 101 |       |     | S/D |        |      |     |     | 4     | 19         |                  | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 11 001 011 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | 00 000 110 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RLD          | 11 101 101 |       |     |     |        |      | S/D |     | 2     | 16         |                  | $\uparrow$ | ↑ | R | Р    | R | •          |

|                   |              | 01 101 111 |       |     |     |        |      |     |     |       |            | C b7 <b>∢</b> b0 |            |   |   |      |   |            |

|                   | RRA          | 00 011 111 |       |     |     |        |      | S/D |     | 1     | 3          |                  | •          | • | R | •    | R | ↑          |

|                   | RRg          | 11 001 011 |       |     |     | S/D    |      |     |     | 2     | 7          |                  | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 00 011 g   |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RR (HL)      | 11 001 011 |       |     |     |        | S/D  |     |     | 2     | 13         |                  | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 00 011 110 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RR (IX + d)  | 11 011 101 |       |     | S/D |        |      |     |     | 4     | 19         |                  | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 11 001 011 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | 00 011 110 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RR (IY + d)  | 11 111 101 |       |     | S/D |        |      |     |     | 4     | 19         | b0b7 C           | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 11 001 011 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | 00 011 110 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RRCA         | 00 001 111 |       |     |     |        |      | S/D |     | 1     | 3          |                  | •          | • | R | •    | R | ↑          |

|                   | RRC g        | 11 001 011 |       |     |     | S/D    |      |     |     | 2     | 7          |                  | $\uparrow$ | ↑ | R | Р    | R | ↑          |

|                   |              | 00 001 g   |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RRC (HL)     | 11 001 011 |       |     |     |        | S/D  |     |     | 2     | 13         |                  | $\uparrow$ | ↑ | R | Р    | R | ↑          |

|                   |              | 00 001 110 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   | RRC (IX + d) | 11 011 101 |       |     | S/D |        |      |     |     | 4     | 19         |                  | $\uparrow$ | ↑ | R | Р    | R | ↑          |

|                   |              | 11 001 011 |       |     |     |        |      |     |     |       |            |                  |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |        |      |     |     |       |            |                  | 1          |   |   |      |   |            |

|                   |              | 00 001 110 |       |     |     |        |      |     |     |       |            |                  | 1          |   |   |      |   |            |

|                   | RRC (IY + d) | 11 111 101 |       |     | S/D |        |      |     |     | 4     | 19         |                  | $\uparrow$ | ↑ | R | Р    | R | ↑          |

#### Table 39. Rotate and Shift Instructions (Continued)

218

|                   |              |            |       |     |     |       |      |     |     |       |            |           | Γ          |   | F | lags |   |            |

|-------------------|--------------|------------|-------|-----|-----|-------|------|-----|-----|-------|------------|-----------|------------|---|---|------|---|------------|

|                   |              |            |       |     | Add | ressi | ing  |     |     |       |            |           | 7          | 6 | 4 | 2    | 1 | 0          |

| Operation<br>Name | Mnemonics    | Op Code    | Immed | Ext | Ind | Reg   | Regi | Imp | Rel | Bytes | State<br>s | Operation | s          | z | н | P/V  | N | с          |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           | Γ          |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   |              | 00 001 110 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   | RRD          | 11 101 101 |       |     |     |       |      | S/D |     | 2     | 16         | <b>↓</b>  | $\uparrow$ | ↑ | R | Р    | R | •          |

|                   |              | 01 100 111 |       |     |     |       |      |     |     |       |            | Ar        |            |   |   |      |   | Í          |

|                   | SLA g        | 11 001 011 |       |     |     | S/D   |      |     |     | 2     | 7          | b7 b0     | $\uparrow$ | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 00 100 g   |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   | SLA (HL)     | 11 001 011 |       |     |     |       | S/D  |     |     | 2     | 13         | b7 b0     | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 00 100 110 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   | SLA (IX + d) | 11 011 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | ↑          | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            | C b7 b0   |            |   |   |      |   | Í          |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   |              | 00 100 110 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   | SLA (IY + d) | 11 111 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | ↑          | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   |              | 00 100 110 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   | SRA g        | 11 001 011 |       |     |     | S/D   |      |     |     | 2     | 7          | _         | $\uparrow$ | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 00 101 g   |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   | Í          |

|                   | SRA (HL)     | 11 001 011 |       |     |     |       | S/D  |     |     | 2     | 13         | b7 b0 C   | $\uparrow$ | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 00 101 110 |       |     |     |       |      |     |     |       |            | b7 b0 C   |            |   |   |      |   |            |

|                   | SRA (IX + d) | 11 011 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | $\uparrow$ | ↑ | R | Р    | R | $\uparrow$ |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   |              | 00 101 110 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   | SRA (IY + d) | 11 111 101 |       |     | S/D |       |      |     |     | 4     | 19         |           | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 11 001 011 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   |              | <d></d>    |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   |              | 00 101 110 |       |     |     |       |      |     |     |       |            |           |            |   |   |      |   |            |

|                   | SRL g        | 11 001 011 |       |     |     | S/D   |      |     |     | 2     | 7          |           | ↑          | ↑ | R | Р    | R | ↑          |

|                   |              | 00 111 g   |       |     |     |       |      |     |     |       |            | b7 b0 C   |            |   |   |      |   |            |

#### Table 39. Rotate and Shift Instructions (Continued)

|              |        | Machine    |                         |

|--------------|--------|------------|-------------------------|

| MNEMONICS    | Bytes  | Cycles     | States                  |

| PUSH IX      | 2      | 6          | 14                      |

| PUSH IY      | 2      | 6          | 14                      |

| PUSH zz      | 1      | 5          | 11                      |

| RES b,(HL)   | 2      | 5          | 13                      |

| RES b,(IX+d) | 4      | 7          | 19                      |

| RES b,(IY+d) | 4      | 7          | 19                      |

| RES b,g      | 2      | 3          | 7                       |

| RET          | 1      | 3          | 9                       |

| RET f        | 1      | 3          | 5                       |

|              |        |            | (If condition is false) |

|              | 1      | 4          | 10                      |

|              |        |            | (If condition is true)  |

| RETI         | 2      | 4 (R0, R1) | 12 (R0, R1)             |

|              | 10 (Z) |            | 22 (Z)                  |

| RETN         | 2      | 4          | 12                      |

| RLA          | 1      | 1          | 3                       |

| RLCA         | 1      | 1          | 3                       |

| RLC (HL)     | 2      | 5          | 13                      |

| RLC (IX-1-dl | 4      | 7          | 19                      |

| RLC (IY+d)   | 4      | 7          | 19                      |

| RLC g        | 2      | 3          | 7                       |

| RLD          | 2      | 8          | 16                      |

| RL (HL)      | 2      | 5          | 13                      |

| RL (IX+d)    | 4      | 7          | 19                      |

| RL (IY+d)    | 4      | 7          | 19                      |

| RL g         | 2      | 3          | 7                       |

| RRA          | 1      | 1          | 3                       |

| RRCA         | 1      | 1          | 3                       |

| RRC (HL)     | 2      | 5          | 13                      |

| RRC (IX+d)   | 4      | 7          | 19                      |

#### 251

# **Bus Control Signal Conditions**

# BUS AND CONTROL SIGNAL CONDITION IN EACH MACHINE CYCLE

\* (ADDRESS) invalid

Z (DATA) high impedance.

\*\* added new instructions to Z80

| Table 51.         Bus and Control Signal Condition in Each Machine Cycle |

|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------|

| Instruction            | Machine<br>Cycle | States   | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|------------------------|------------------|----------|------------------------|----------------|----|----|------|------|-----------|------|----|

|                        | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| ADD HL,ww              | MC2<br>~MC5      | TiTiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                        | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| ADD IX,xx<br>ADD IY,yy | MC2              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                        | MC3<br>~MC6      | TiTiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| ADC HL,ww              | MC1              | T1T2T3   | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SBC HL,ww              | MC2              | T1T2T3   | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                        | MC3<br>~MC6      | TiTiTiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

252

| Instruction                                                                 | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-----------------------------------------------------------------------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

| ADD A,g<br>ADC A,g                                                          | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SUB g<br>SBC A,g<br>AND g<br>OR g<br>XOR g<br>CP g                          | MC2              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| ADD A,m<br>ADC A,m                                                          | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SUB m<br>SBC A,m<br>AND m<br>OR m<br>XOR m<br>CP m                          | MC2              | T1T2T3 | 1st operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| ADD A, (HL)<br>ADC A, (HL)                                                  | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| SUB (HL)<br>SBC A, (HL)<br>AND HU<br>OR (HL)<br>XOR (HL)<br>CP (HL)         | MC2              | T1T2T3 | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| ADD A, (IX+ d)<br>ADD A, (IY+d)                                             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| ADC A, (IX+d)<br>ADC A, (IY+d)<br>SUB (IX+d)<br>SUB (IY+d)<br>SBC A, (IX+d) | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

| SBC A, (IY+ d)<br>AND (IX+d)                                                | MC3              | T1T2T3 | 1st operand<br>Address | d              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

269

| Instruction  | Machine<br>Cycle | States | Address                        | Data           | RD | WR | MREQ | IORQ | M1 | HALT | ST |

|--------------|------------------|--------|--------------------------------|----------------|----|----|------|------|----|------|----|

|              | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| OUT (m),A    | MC2              | T1T2T3 | 1st operand<br>Address         | m              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|              | MC3              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|              | MC4              | T1T2T3 | m to A0~A7<br>A to A8~A15      | А              | 1  | 0  | 1    | 0    | 1  | 1    | 1  |

|              | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| OUT (C),g    | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|              | MC3              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|              | MC4              | T1T2T3 | BC                             | g              | 1  | 0  | 1    | 0    | 1  | 1    | 1  |

|              | MC1              | T1T2T3 | 1st Op Code<br>Address         | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 0  |

| OUT0 (m),g** | MC2              | T1T2T3 | 2nd Op Code<br>Address         | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0  | 1    | 1  |

|              | MC3              | T1T2T3 | 1st operand<br>Address         | m              | 0  | 1  | 0    | 1    | 1  | 1    | 1  |

|              | MC4              | Ti     | *                              | Z              | 1  | 1  | 1    | 1    | 1  | 1    | 1  |

|              | MC5              | T1T2T3 | m to A0~A7<br>00H to<br>A8~A15 | g              | 1  | 0  | 1    | 0    | 1  | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

# 281

# **Operating Modes Summary**

Т

Г

## **REQUEST ACCEPTANCES IN EACH OPERATING MODE**

Т

| Current<br>Status<br>Request                                                  | Normal<br>Operation<br>(CPU mode<br>and IOSTOP<br>Mode)        | WAIT State                                                   | Refresh<br>Cycle                                                                           | Interrupt<br>Acknowledge<br>Cycle                      | DMA Cycle                                                     | BUS<br>RELEASE<br>Mode                                                                       | SLEEP<br>Mode                                                         | SYSTEM<br>STOP<br>Mode                                                     |

|-------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|

| WAIT                                                                          | Acceptable                                                     | Acceptable                                                   | Not<br>acceptable                                                                          | Acceptable                                             | Acceptable                                                    | Not<br>acceptable                                                                            | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| Refresh Request<br>Request of Refresh<br>by the on-chip<br>Refresh Controller | Refresh cycle<br>begins at the<br>end of Machine<br>Cycle (MC) | Not<br>acceptable                                            | Not<br>acceptable                                                                          | Refresh cycle<br>begins at the<br>end MC               | Refresh cycle<br>begins at the<br>end of MC                   | Not<br>acceptable                                                                            | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| DREQ0<br>DREQ1                                                                | DMA cycle<br>begins at the<br>end of MC                        | DMA cycle<br>begins at the<br>end of MC                      | Acceptable<br>Refresh cycle<br>precedes.<br>DMA cycle<br>begins at the<br>end of one<br>MC | Acceptable<br>DMA cycle<br>begins at the<br>end of MC. | Acceptable<br>Refer to<br>"DMA<br>Controller"<br>for details. | Acceptable<br>*After BUS<br>RELEASE<br>cycle, DMA<br>cycle begins<br>at the end of<br>one MC | Not<br>acceptable                                                     | Not<br>acceptable                                                          |

| BUSREQ                                                                        | Bus is released<br>at the end of<br>MC                         | Not<br>acceptable                                            | Not<br>acceptable                                                                          | Bus is released<br>at the end of<br>MC                 | Bus is<br>released at the<br>end of MC                        | Continue<br>BUS<br>RELEASE<br>mode                                                           | Acceptable                                                            | Acceptable                                                                 |

| Interrupt INTO,<br>INT1,<br>INT2                                              | Accepted after<br>executing the<br>current<br>instruction.     | Accepted<br>after<br>executing the<br>current<br>instruction | Not<br>acceptable                                                                          | Not<br>acceptable                                      | Not<br>acceptable                                             | Not<br>acceptable                                                                            | Acceptable<br>Return from<br>SLEEP<br>mode to<br>normal<br>operation. | Acceptable<br>Return from<br>SYSTEM<br>STOP mode<br>to normal<br>operation |

Table 53.

Request Acceptances in Each Operating Mode

T

1

т

Т

DMA TEND0 output 108 E clock (memory and I/O R/W cycles) 201 E clock (R/W and INTACK cycles) 167 E clock (SLEEP and SYSTEM STOP modes) 168 E clock BUS RELEASE, SLEEP and SYS-TEM STOP modes) 201 E clock minimum timing example of PWEL and PWEH) 202 External clock rise and fall 204 HALT 33 I/O Read and Write cycles with IOC = 0.17I/O read and write cycles with IOC=1 17 I/O read/write timing 23 Input rise and fall time 204 Instruction 24 INT0 interrupt mode 2 80 INT0 mode 0 76 INT0 mode 1 78 INT1, INT2 and Internal interrupts 86 M1 temporary enable 16 Memory read/write timing (with Wait state) 22 Memory read/write timing (without Wait state) 21 NMI and DMA operation 115 Op Code Fetch timing (with Wait state) 20 Op Code Fetch timing (without Wait state) 19 PRT bus release mode 167 Refresh cycle 87 RESET 25 RTS0 140

SLEEP 35 TRAP timing - 2nd Op Code Undefined 71 TRAP timing - 3rd Op Code Undefined 72 WAIT 28 TRAP 68

Interrupt 70 Timing 71

# U

Undefined Fetch Object (UFO) 68

# V

Vector acquisition INT0 mode 2 79 INT1, INT2 81

Vector table 82

#### W

Wait state generation I/O Wait insertion 29 Memory and 29 Programmable Wait state insertion 28 Wait input and reset 30 Wait state insertion 30