#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 10MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | -40°C ~ 100°C (TA)                                     |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018010vec |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Z8018x Family MPU User Manual

This publication is subject to replacement by a later edition. To determine whether a later edition exists, or to request copies of publications, contact

ZiLOG Worldwide Headquarters 532 Race Street San Jose, CA 95126-3432 Telephone: 408.558.8500 Fax: 408.558.8300 www.ZiLOG.com

Windows is a registered trademark of Microsoft Corporation.

#### **Document Disclaimer**

© 2003 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses or other rights are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

# Table of Contents

| Z80180, Z8S180, Z8L180 MPU Operation                 | 1   |

|------------------------------------------------------|-----|

| Features                                             | .1  |

| General Description                                  | .1  |

| Pin Description                                      | .7  |

| Architecture                                         | 2   |

| Operation Modes1<br>CPU Timing1                      |     |

| Wait State Generator                                 | 27  |

| (Z80180-Class Processors Only)                       |     |

| (Z8S180/Z8L180 only)                                 |     |

| STANDBY Mode                                         |     |

| STANDBY Mode Exit wiht BUS REQUEST                   | 8   |

| STANDBY Mode EXit with External Interrupts           | ;9  |

| IDLE Mode 4                                          |     |

| STANDBY-QUICK RECOVERY Mode                          |     |

| Internal I/O Registers4                              | 1   |

| MMU Register Description                             | 50  |

| Interrupts                                           | 5   |

| Interrupt Acknowledge Cycle Timings                  | 32  |

| Interrupt Sources During RESET                       | 33  |

| Dynamic RAM Refresh Control                          | 36  |

| DMA Controller (DMAC)                                | )() |

| Asynchronous Serial Communication Interface (ASCI)11 | 5   |

| r                  |            |      |   |    |                 |

|--------------------|------------|------|---|----|-----------------|

| V <sub>SS</sub> 1  | $\bigcirc$ |      | - | 64 | Phi             |

| XTAL 2             | $\bigcirc$ |      | _ | 63 | RD              |

| EXTAL 3            |            |      |   | 62 | WR              |

| WAIT 4             |            |      |   | 61 | MI              |

| BUSACK 5           |            |      |   | 60 | E               |

| BUSREQ 6           |            |      | - | 59 | MREQ            |

| RESET 7            |            |      | - | 58 | IORQ            |

| NMI 8              |            |      |   | 57 | RFSH            |

| INT0 9             |            |      | - | 56 | HALT            |

| INT1 10            |            |      | - | 55 | TEND1           |

| INT2 11            |            |      | _ | 54 | DREQ1           |

| ST 12              |            |      | - | 53 | CKS             |

| A0 13              |            |      | - | 52 | RXS/CTS1        |

| A1 14              |            |      |   | 51 | TXS             |

| A2 15              |            |      |   | 50 | CKA1/TEND0      |

| A3 16              | Z8         | X180 | - | 49 | RXA1            |

| A4 17              |            |      |   | 48 | TXA1            |

| A5 18              |            |      |   | 47 | CKA0/DREQ0      |

| A6 <u>19</u>       |            |      | - | 46 | RXA0            |

| A7 20              |            |      |   | 45 | TXA0            |

| A8 21              |            |      | - | 44 | DCO0            |

| A9 22              |            |      |   | 43 | CTS0            |

| A10 23             |            |      | - | 42 | RTS0            |

| A11 24             |            |      |   | 41 | D7              |

| A12 25             |            |      |   | 40 | D6              |

| A13 26             |            |      |   | 39 | D5              |

| A14 27             |            |      | - | 38 | D4              |

| A15 28             |            |      | - | 37 | D3              |

| A16 29             |            |      |   | 36 | D2              |

| A17 30             |            |      | - | 35 | D1              |

| A18/TOUT 31        |            |      | F | 34 | D0              |

| V <sub>CC</sub> 32 |            |      |   | 33 | V <sub>SS</sub> |

Figure 1. 64-Pin DIP

**TOUT.** *Timer Out (Output, Active High).* TOUT is the pulse output from PRT channel 1. This line is multiplexed with A18 of the address bus.

**TXA0, TXA1.** *Transmit Data 0 and 1 (Outputs, Active High).* These signals are the transmitted data from the ASCI channels. Transmitted data changes are with respect to the falling edge of the transmit clock.

**TXS.** *Clocked Serial Transmit Data (Output, Active High).* This line is the transmitted data from the CSIO channel.

**WAIT.** *Wait (Input; Active Low).* WAIT indicates to the CPU that the addressed memory or I/O devices are not ready for a data transfer. This input is used to induce additional clock cycles into the current machine cycle. The WAIT input is sampled on the falling edge of T2 (and subsequent Wait States). If the input is sampled Low, then additional Wait States are inserted until the WAIT input is sampled High, at which time execution continues.

**WR.** Write (Output, Active Low, 3-state). WR indicates that the CPU data bus holds valid data to be stored at the addressed I/O or memory location.

**XTAL.** *Crystal (Input, Active High). Crystal oscillator connection.* This pin must be left open if an external clock is used instead of a crystal. The oscillator input is not a TTL level (reference DC characteristics).

Multiplexed pins are described in Table 2.

The external bus is IDLE while the CPU computes the effective address. Finally, the computed memory location is written with the contents of the CPU register (g).

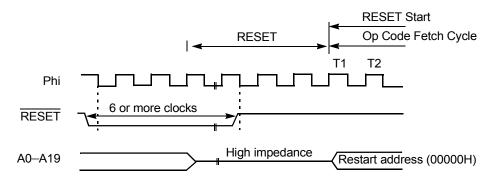

#### **RESET Timing**

Figure 15 depicts the Z8X180 hardware RESET timing. If the  $\overline{\text{RESET}}$  pin is Low for six or more clock cycles, processing is terminated and the Z8X180 restarts execution from (logical and physical) address 00000H.

Figure 15. RESET Timing Diagram

#### **BUSREQ/BUSACK Bus Exchange Timing**

The Z8X180 can coordinate the exchange of control, address and data bus ownership with another bus master. The alternate bus master can request the bus release by asserting the BUSREQ (Bus Request) input Low. After the Z8X180 releases the bus, it relinquishes control to the alternate bus master by asserting the BUSACK (Bus Acknowledge) output Low.

The bus may be released by the Z8X180 at the end of each machine cycle. In this context, a machine cycle consists of a minimum of three clock cycles (more if wait states are inserted) for Op Code fetch, memory read/ write, and I/O read/write cycles. Except for these cases, a machine cycle corresponds to one clock cycle.

25

If the Global Interrupt Enable Flag IEF1 is set to 1, and if an interrupt source is enabled in the ITC, asserting the corresponding interrupt input causes the Z8S180/Z8L180-class processors to exit STANDBY mode. The CPU performs an interrupt acknowledge sequence appropriate to the input being asserted when clocking is resumed if:

- The interrupt input follows the normal interrupt daisy-chain protocol

- The interrupt source is active until the acknowledge cycle is complete

If the Global Interrupt Enable Flag IEF1 is disabled (reset to 0) and if an interrupt source is enabled in the ITC, asserting the corresponding interrupt input still causes the Z8S180/Z8L180-class processors to exit STANDBY mode. The CPU proceeds to fetch and execute instructions that follow the SLEEP instruction when clocking resumes.

If the Extend Maskable Interrupt input is not active until clocking resumes, the Z8S180/Z8L180-class processors do not exit STANDBY mode. If the Non-Maskable Interrupt ( $\overline{NMI}$ ) is not active until clocking resumes, the Z8S180/Z8L180-class processors still exits the STANDBY mode even if the interrupt sources go away before the timer times out, because  $\overline{NMI}$  is edge-triggered. The condition is latched internally when  $\overline{NMI}$  is asserted Low.

# **IDLE Mode**

IDLE mode is another power-down mode offered by the Z8S180/ Z8L180-class processors.

- 1. Set bits 6 and 3 to 0 and 1, respectively.

- 2. Set the I/O STOP bit (bit 5 of ICR, I/O Address = 3FH to 1.

- 3. Execute the SLEEP instruction

When the part is in IDLE mode, the clock oscillator is kept oscillating, but the clock to the rest of the internal circuit, including the CLKOUT, is stopped completely. IDLE mode is exited in a similar way as STANDBY mode, using RESET, BUS REQUEST or EXTERNAL INTERRUPTS,

|         |                                                |          | A          | ldress     |      |

|---------|------------------------------------------------|----------|------------|------------|------|

|         | Register                                       | Mnemonic | Binary     | Hex        | Page |

| INT     | IL Register (Interrupt Vector Low<br>Register) | IL       | XX110011   | 33H        | 67   |

|         | INT/TRAP Control Register                      | ITC      | XX110100   | 34H        | 68   |

|         | Reserved                                       |          | XX110101   | 35H        |      |

| Refresh | Refresh Control Register                       | RCR      | XX110110   | 36H        | 88   |

|         | Reserved                                       |          | XX110111   | 37H        |      |

| MMU     | MMU Common Base Register                       | CBR      | XX111000   | 38H        | 61   |

|         | MMU Bank Base Register                         | BBR      | XX111001   | 39H        | 62   |

|         | MMU Common/Bank Area Register                  | CBAR     | XX111010   | 3AH        | 60   |

| I/O     | Reserved                                       |          | XX111011   | 3BH        |      |

|         |                                                |          | $\uparrow$ | $\uparrow$ |      |

|         |                                                |          | XX111101   | 3DH        |      |

|         | Operation Mode Control Register                | OMCR     | XX111110   | 3EH        | 15   |

|         | I/O Control Register                           | ICR      | XX111111   | 3FH        | 42   |

#### Table 7. I/O Address Map (Z8S180/Z8L180-Class Processors Only) (Continued)

61

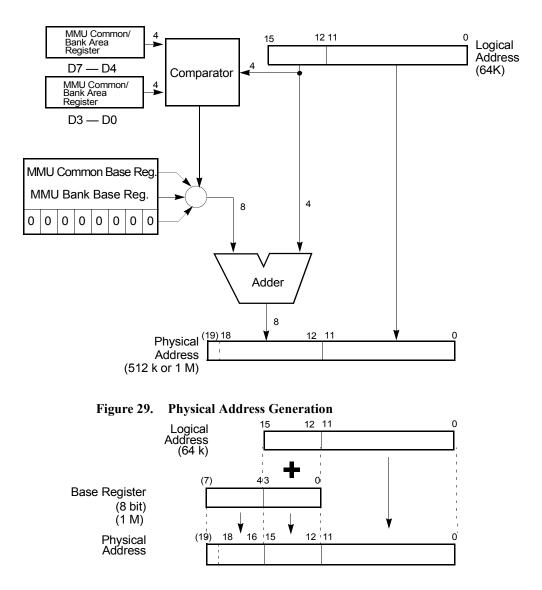

## MMU Common Base Register (CBR)

CBR specifies the base address (on 4K boundaries) used to generate a 20bit physical address for Common Area 1 accesses. All bits of CBR are reset to 0 during RESET.

MMU Common Base Register (CBR: 38H)

| Bit                             | 7           | 6         | 5          | 4              | 3           | 2   | 1   | 0   |

|---------------------------------|-------------|-----------|------------|----------------|-------------|-----|-----|-----|

| Bit/Field                       | CB7         | CB6       | CB5        | CB4            | CB3         | CB2 | CB1 | CB0 |

| R/W                             | R/W         | R/W       | R/W        | R/W            | R/W         | R/W | R/W | R/W |

| Reset                           | 0           | 0         | 0          | 0              | 0           | 0   | 0   | 0   |

| Note: $\mathbf{R} = \mathbf{R}$ | and $W = V$ | Vrito V - | Indotormin | at $2 = N_{c}$ | at Applicat | 10  |     |     |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                     |

|-----------------|-----------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 7–0             | СВ7—0     | R/W |       | CBR specifies the base address (on 4KB boundaries) used<br>to generate a 20-bit physical address for Common Area 1<br>accesses. |

Z8018x Family MPU User Manual

64

Figure 30. Physical Address Generation 2

| Bit<br>Position | Bit/Field | R/W | Value                           | Description                                                                          |

|-----------------|-----------|-----|---------------------------------|--------------------------------------------------------------------------------------|

| 2-0             |           | R/W | 000<br>001<br>010<br>011<br>111 | DMA1 ext TOUT/DREQ<br>DMA1 ASCI0<br>DMA1 ASCI1<br>DMA1 ESCC<br>DMA1 PIA27-20 (P1284) |

# **DMA Register Description**

#### Bit 7

This bit must be set to 1 only when both DMA channels are set to take their requests from the same device. If this bit is 1 (it resets to 0), the TEND output of DMA channel o sets a flip-flop, so that thereafter the device's request is visible to channel 1, but not visible to channel 0. The internal TEND signal of channel 1 clears the FF, so that thereafter, the device's request is visible to channel 0, but no visible to channel 1.

If DMA request are from differing sources, DMA channel 0 request is forced onto DMA channel 1 after TEND output of DMA channel 0 sets the flop-flop to alternate.

#### Bit 6

When both DMA channels are programmed to take their requests from the same device, this bit (FF mentioned in the previous paragraph) controls which channel the device's request is presented to: 0 = DMA0, 1 = DMA l. When Bit 7 is 1, this bit is automatically toggled by the channel end output of the channels.

108

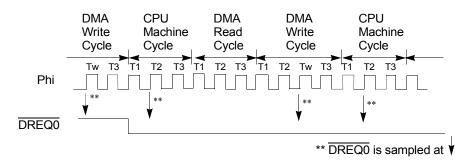

rising edge of the clock prior to T3 at which time the DMA operation (re)starts. Figure 48 depicts the edge-sense DMA timing.

# Figure 48. CPU Operation and DMA Operation DREQ0 is Programmed for Edge-Sense

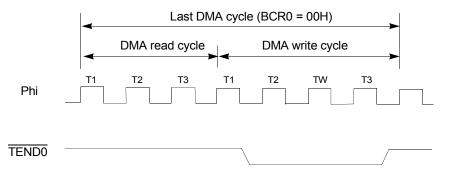

During the transfers for channel 0, the  $\overline{\text{TEND0}}$  output goes Low synchronous with the write cycle of the last (BCR0 = 00H) DMA transfer (Reference Figure 49).

## Figure 49. TEND0 Output Timing Diagram

The DREQ0 and TEND0 pins are programmably multiplexed with the CKA0 and CKA1 ASCI clock input/outputs. However, when DMA channel 0 is programmed for memory to/from I/O (and memory to/from

158

return accurate data without requiring the timer to be stopped. The write procedure requires the PRT to be stopped.

For reading (without stopping the timer), TMDR is read in the order of lower byte - higher byte (TMDRnL, TMDRnH). The lower byte read (TMDRnL) stores the higher byte value in an internal register. The following higher byte read (TMDRnH) accesses this internal register. This procedure insures timer data validity by eliminating the problem of potential 16-bit timer updating between each 8-bit read. Specifically, reading TMDR in higher byte–lower byte order may result in invalid data. Note the implications of TMDR higher byte internal storage for applications which may read only the lower and/or higher bytes. In normal operation all TMDR read routines must access both the lower and higher bytes, in that order. For writing, the TMDR down counting must be inhibited using the TDE (Timer Down Count Enable) bits in the TCR (Timer Control Register). Then, any or both higher and lower bytes of TMDR can be freely written (and read) in any order.

# CSI/O Transmit/Receive Data Register (TRDR: I/O Address = 0BH).

TRDR is used for both CSI/O transmission and reception. Thus, the system design must insure that the constraints of half-duplex operation are met (Transmit and receive operation cannot occur simultaneously). For example, if a CSI/O transmission is attempted while the CSI/O is receiving data, the CSI/O does not work.

TRDR is not buffered. Attempting to perform a CSI/O transmit while the previous transmit data is still being shifted out causes the shift data to be immediately updated, thereby corrupting the transmit operation in progress. Similarly, reading TRDR during a transmit or receive must be avoided.

# **DC** Characteristics

This section describes the DC characteristics of the Z8X180 family and absolute maximum rating for these products.

# **ABSOLUTE MAXIMUM RATING**

| Item                  | Symbol | Value          | Unit |

|-----------------------|--------|----------------|------|

| Supply Voltage        | Vcc    | - 0.3 ~ + 7.0  | V    |

| Input Voltage         | Vin    | -0.3 ~ Vcc+0.3 | V    |

| Operating Temperature | Topr   | 0 ~ 70         | °C   |

| Extended Temperature  | Text   | -40 ~ 85       | °C   |

| Storage Temperature   | Tstg   | - 55 ~ +150    | °C   |

Table 27. Absolute Maximum Rating

Permanent IC damage may occur if maximum ratings are exceeded. Normal operation should be under recommended operating conditions. If these conditions are exceeded, it could affect reliability of IC.

# Table 31. Z8S180 AC Characteristics (Continued) $V_{DD} = 5V \pm 10\%$ or $V_{DD} = 3.3V \pm 10\%$ ; 33-MHz Characteristics Apply Only to 5V Operation

|     |                   |                                     | MHz MI |     | 80—33<br>1Hz |     |      |

|-----|-------------------|-------------------------------------|--------|-----|--------------|-----|------|

| No. | Symbol            | Item                                | Min    | Max | Min          | Max | Unit |

| 31  | t <sub>INTS</sub> | INT Set-up Time to PHI Fall         | 20     |     | 15           |     | ns   |

| 32  | t <sub>INTH</sub> | INT Hold Time from PHI Fall         | 10     | _   | 10           |     | ns   |

| 33  | t <sub>NMIW</sub> | NMI Pulse Width                     | 35     |     | 25           |     | ns   |

| 34  | t <sub>BRS</sub>  | BUSREQ Set-up Time to PHI Fall      | 10     |     | 10           |     | ns   |

| 35  | t <sub>BRH</sub>  | BUSREQ Hold Time from PHI Fall      | 10     |     | 10           |     | ns   |

| 36  | t <sub>BAD1</sub> | PHI Rise to BUSACK Fall Delay       |        | 25  |              | 15  | ns   |

| 37  | t <sub>BAD2</sub> | PHI Fall to BUSACK Rise Delay       |        | 25  |              | 15  | ns   |

| 38  | t <sub>BZD</sub>  | PHI Rise to Bus Floating Delay Time |        | 40  |              | 30  | ns   |

| 39  | t <sub>MEWH</sub> | MREQ Pulse Width (High)             | 35     |     | 25           |     | ns   |

| 40  | t <sub>MEWL</sub> | MREQ Pulse Width (Low)              | 35     |     | 25           |     | ns   |

| 41  | t <sub>RFD1</sub> | PHI Rise to RFSH Fall Delay         |        | 20  |              | 15  | ns   |

| 42  | t <sub>RFD2</sub> | PHI Rise to RFSH Rise Delay         |        | 20  |              | 15  | ns   |

| 43  | t <sub>HAD1</sub> | PHI Rise to HALT Fall Delay         |        | 15  |              | 15  | ns   |

| 44  | t <sub>HAD2</sub> | PHI Rise to HALT Rise Delay         |        | 15  |              | 15  | ns   |

| 45  | t <sub>DRQS</sub> | DREQ1 Set-up Time to PHI Rise       | 20     |     | 15           |     | ns   |

| 46  | t <sub>DRQH</sub> | DREQ1 Hold Time from PHI Rise       | 20     |     | 15           |     | ns   |

| 47  | t <sub>TED1</sub> | PHI Fall to TENDi Fall Delay        |        | 25  |              | 15  | ns   |

| 48  | t <sub>TED2</sub> | PHI Fall to TENDi Rise Delay        |        | 25  |              | 15  | ns   |

| 49  | t <sub>ED1</sub>  | PHI Rise to E Rise Delay            |        | 30  | _            | 15  | ns   |

| 50  | t <sub>ED2</sub>  | PHI Fall or Rise to E Fall Delay    |        | 30  |              | 15  | ns   |

| 51  | P <sub>WEH</sub>  | E Pulse Width (High)                | 25     |     | 20           |     | ns   |

| 52  | P <sub>WEL</sub>  | E Pulse Width (Low)                 | 50     |     | 40           |     | ns   |

| 53  | t <sub>Er</sub>   | Enable Rise Time                    |        | 10  |              | 10  | ns   |

195

#### I/O Write Cycle\* I/O Read Cycle\* Opcode Fetch Cycle $T_2$ T<sub>3</sub> $T_1$ $T_2$ T<sub>3</sub> $T_1$ Τ<sub>1</sub> Τw Tw 2 3 PHI ADDRESS М 20 20 19 19 WAIT MREQ 8 29 IORQ 11 28 13 RD 9 9 25-22 WR 26 14 M1 18 10 ST 16 15 Data IN 24 23 Data OUT 62 62-63 - 63 RESET 68 - 67 67 **⊢** 68

# **Timing Diagrams**

Figure 81. AC Timing Diagram 1

255

| Instruction                                            | Machine<br>Cycle | States         | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ST |

|--------------------------------------------------------|------------------|----------------|------------------------|----------------|----|----|------|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                        | MC1              | T1T2T3         | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

| CPI<br>CPD                                             | MC2              | T1T2T3         | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|                                                        | MC3              | T1T2T3         | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|                                                        | MC4<br>~MC6      | TiTiTi         | *                      | Z              | 1  | 1  | 1    |      | 1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|                                                        | MC1              | T1T2T3         | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

| CPIR<br>CPDR<br>(If $BC_R \neq 0$ and $Ar = (HI)$ , .) | MC2              | T1T2T3         | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

| $Ar = (HL)_M$                                          | MC3              | T1T2T3         | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|                                                        | MC4~M<br>C8      | TiTiTi<br>TiTi | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|                                                        | MC1              | T1T2T3         | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

| CPIR<br>CPDR<br>(If BC <sub>R</sub> =0 or              | MC2              | T1T2T3         | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

| $Ar = (HL)_M$                                          | MC3              | T1T2T3         | HL                     | DATA           | 0  | 1  | 0    | 1    | 1         | 0     1     0       0     1     1       1     1     1       1     1     1       1     1     1       0     1     0       0     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1       1     1     1 | 1  |

|                                                        | MC4~M<br>C6      | TiTiTi         | *                      | Z              | 1  | 1  | 1    | 1    | 1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1  |

| CPL                                                    | MC1              | T1T2T3         | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

| DAA                                                    | MC1              | T1T2T3         | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

|                                                        | MC2              | Ti             | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

| DI*1                                                   | MC1              | T1T2T3         | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0  |

| * 1 Interrupt reque                                    | est is not sai   | npled.         |                        |                |    |    |      |      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

UM005003-0703

257

| Instruction              | Machine<br>Cycle | States | Address                 | Data            | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|--------------------------|------------------|--------|-------------------------|-----------------|----|----|------|------|-----------|------|----|

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| EX (SP),IX<br>EX (SP),IY | MC2              | T1T2T3 | 2nd Op Code<br>Address  | 2nd Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                          | MC3              | T1T2T3 | SP                      | DATA            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                          | MC4              | T1T2T3 | SP+1                    | DATA            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                          | MC5              | Ti     | *                       | Z               | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                          | MC6              | T1T2T3 | SP+1                    | IXH<br>IYH      | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                          | MC7              | T1T2T3 | SP                      | IXL<br>IYL      | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| HALT                     | —                | _      | Next Op Code<br>Address | Next Op<br>Code | 0  | 1  | 0    | 1    | 0         | 0    | 0  |

| IM1                      | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| IM2                      | MC2              | T1T2T3 | 2nd Op Code<br>Address  | 2nd Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| DEC g                    | MC2              | Ti     | *                       | Z               | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                          | MC1              | T1T2T3 | 1st Op Code<br>Address  | 1st Op<br>Code  | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

|                          | MC2              | T1T2T3 | HL                      | DATA            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                          | MC3              | Ti     | *                       | Z               | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                          | MC4              | T1T2T3 | HL                      | DATA            | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

#### Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

UM005003-0703

278

| Instruction | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

| TST g**     | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

|             | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| TST m**     | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | T1T2T3 | 1st operand<br>Address | m              | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| TST (HL)**  | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 2  | 0    | 2    | 0         | 2    | 0  |

|             | MC2              | T1T2T3 | 2nd Op Code<br>Address | 2nd Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 1  |

|             | MC3              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|             | MC4              | T1T23  | HL                     | Data           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

## Table 51. Bus and Control Signal Condition in Each Machine Cycle (Continued)

#### 287

# **Status Signals**

# **PIN OUTPUTS IN EACH OPERATING MODE**

Table 55 describes pin outputs in each operating mode.

| Mode                                                        |                                           | <u>M1</u> | MREQ | IORQ | RD | WR | RFSH | HALT | BUSACK | ST | Address<br>BUS | Data<br>BUS |

|-------------------------------------------------------------|-------------------------------------------|-----------|------|------|----|----|------|------|--------|----|----------------|-------------|

| CPU<br>Operation                                            | Op Code Fetch<br>(1st Op Code)            | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

|                                                             | Op Code Fetch<br>(except 1 st Op<br>Code) | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

|                                                             | MemRead                                   | 1         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

|                                                             | Memory Write                              | 1         | 0    | 1    | 1  | 0  | 1    | 1    | 1      | 1  | А              | OUT         |

|                                                             | I/O Read                                  | 1         | 1    | 0    | 0  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

|                                                             | I/O Write                                 | 1         | 1    | 0    | 1  | 0  | 1    | 1    | 1      | 1  | А              | OUT         |

|                                                             | Internal<br>Operation                     | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 1  | А              | IN          |

| Refresh                                                     |                                           | 1         | 0    | 1    | 1  | 1  | 0    | 1    | 1      | *  | А              | IN          |

| Interrupt<br>Acknowledge<br>Cycle<br>(1st Machine<br>Cycle) | NMI                                       | 0         | 0    | 1    | 0  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

|                                                             | <b>INTO</b>                               | 0         | 1    | 0    | 1  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

|                                                             | INT1, INT2 &<br>Internal<br>Interrupts    | 1         | 1    | 1    | 1  | 1  | 1    | 1    | 1      | 0  | А              | IN          |

| BUS RELEASE                                                 |                                           | 1         | Z    | Z    | Z  | Z  | 1    | 1    | 0      | *  | Z              | IN          |

| HALT                                                        |                                           | 0         | 0    | 1    | 0  | 1  | 1    | 0    | 1      | 0  | А              | IN          |

| SLEEP                                                       |                                           | 1         | 1    | 1    | 1  | 1  | 1    | 0    | 1      | 1  | 1              | IN          |

#### Table 55. Pin Outputs in Each Operating Mode

291

|           |              | Pin Status in Each Operation Mode |                   |              |                |  |  |  |

|-----------|--------------|-----------------------------------|-------------------|--------------|----------------|--|--|--|

| Symbol    | Pin Function | RESET                             | SLEEP             | IOSTOP       | SYSTEM<br>STOP |  |  |  |

| MREQ      | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |

| Е         |              | 0                                 | E Clock<br>Output | <del>~</del> | ←              |  |  |  |

| <u>M1</u> | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |

| WR        | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |

| RD        | —            | 1                                 | 1                 | OUT          | 1              |  |  |  |

| Phi       |              | Phi Clock<br>Output               | <del>~</del>      | <b>←</b>     | ←              |  |  |  |

Table 56.

Pin Status During RESET and LOW POWER OPERATION Modes (Continued)

- 1: HIGH 0: LOW A: Programmable Z: High Impedance

- IN (A): Input (Active) IN (N): Input (Not active) OUT: Output

- H: Holds the previous state

- $\leftarrow$ : same as the left