#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                               |

|---------------------------------|--------------------------------------------------------|

| Core Processor                  | Z80180                                                 |

| Number of Cores/Bus Width       | 1 Core, 8-Bit                                          |

| Speed                           | 10MHz                                                  |

| Co-Processors/DSP               | -                                                      |

| RAM Controllers                 | DRAM                                                   |

| Graphics Acceleration           | No                                                     |

| Display & Interface Controllers | -                                                      |

| Ethernet                        | -                                                      |

| SATA                            | -                                                      |

| USB                             | -                                                      |

| Voltage - I/O                   | 5.0V                                                   |

| Operating Temperature           | 0°C ~ 70°C (TA)                                        |

| Security Features               | -                                                      |

| Package / Case                  | 68-LCC (J-Lead)                                        |

| Supplier Device Package         | 68-PLCC                                                |

| Purchase URL                    | https://www.e-xfl.com/product-detail/zilog/z8018010vsc |

|                                 |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | Table 23.  | Timer Output Control                        | 163 |

|-------------|------------|---------------------------------------------|-----|

|             | Table 24.  | E Clock Timing in Each Condition            | 166 |

|             | Table 25.  | Z8X180 Operating Frequencies                | 169 |

| Software A  | rchitectur | e                                           |     |

|             | Table 26.  | Instruction Set Summary                     |     |

| DC Charac   | eteristics |                                             |     |

|             | Table 27.  | Absolute Maximum Rating                     |     |

|             | Table 28.  | Z80180 DC Characteristics                   |     |

|             | Table 29.  | Z8S180 DC Characteristics                   |     |

|             | Table 30.  | Z8L180 DC Characteristics                   |     |

| AC Charac   | teristics  |                                             |     |

|             | Table 31.  | Z8S180 AC Characteristics                   | 193 |

| Instruction | Set        |                                             |     |

|             | Table 32.  | Register Values                             |     |

|             | Table 33.  | Bit Values                                  |     |

|             | Table 34.  | Instruction Values                          |     |

|             | Table 35.  | Address Values                              |     |

|             | Table 36.  | Flag Conditions                             |     |

|             | Table 37.  | Operations Mnemonics                        |     |

|             | Table 38.  | Arithmetic and Logical Instructions (8-bit) |     |

|             | Table 39.  | Rotate and Shift Instructions               |     |

|             | Table 40.  | Arithmetic Instructions (16-bit)            |     |

|             | Table 41.  | 8-Bit Load                                  |     |

|             | Table 42.  | 16-Bit Load                                 |     |

#### **Central Processing Unit**

The CPU is microcoded to provide a core that is object code compatible with the Z80 CPU. It also provides a superset of the Z80 instruction set, including 8-bit multiply and divide. This core has been enhanced to allow many of the instructions to execute in fewer clock cycles.

#### **DMA Controller**

The DMA controller provides high speed transfers between memory and I/O devices. Transfer operations supported are memory-to-memory, memory to/from I/O and I/O to I/O. Transfer modes supported are REQUEST, BURST, and CYCLE STEAL. DMA transfers can access the full 1MB addressing range with a block length up to 64KB, and can cross over 64K boundaries.

#### Asynchronous Serial Communications Interface (ASCI)

The ASCI logic provides two individual full-duplex UARTs. Each channel includes a programmable baud rate generator and modem control signals. The ASCI channels can also support a multiprocessor communications format.

## Programmable Reload Timer (PRT)

This logic consists of two separate channels, each containing a 16-bit counter (timer) and count reload register. The time base for the counters is derived from the system clock (divided by 20) before reaching the counter. PRT channel 1 provides an optional output to allow for waveform generation.

## **Clocked Serial I/O (CSIO)**

The CSIO channel provides a half-duplex serial transmitter and receiver. This channel can be used for simple high-speed data connection to another microprocessor or microcomputer.

50

|     |                                           |          | A        | ldress |      |

|-----|-------------------------------------------|----------|----------|--------|------|

|     | Register                                  | Mnemonic | Binary   | Hex    | Page |

| DMA | DMA Source Address Register Ch 0L         | SAR0L    | XX100000 | 20H    | 93   |

|     | DMA Source Address Register Ch 0H         | SAR0H    | XX100001 | 21H    | 93   |

|     | DMA Source Address Register Ch 0B         | SAR0B    | XX100010 | 22H    | 93   |

|     | DMA Destination Address Register Ch<br>0L | DAR0L    | XX100011 | 23H    | 94   |

|     | DMA Destination Address Register Ch<br>0H | DAR0H    | XX100100 | 24H    | 94   |

|     | DMA Destination Address Register Ch<br>0B | DAR0B    | XX100101 | 25H    | 94   |

|     | DMA Byte Count Register Ch 0L             | BCR0L    | XX100110 | 26H    | 94   |

|     | DMA Byte Count Register Ch 0H             | BCR0H    | XX100111 | 27H    | 94   |

|     | DMA Memory Address Register Ch 1L         | MAR1L    | XX101000 | 28H    | 94   |

|     | DMA Memory Address Register Ch 1H         | MAR1H    | XX101001 | 29H    | 94   |

|     | DMA Memory Address Register Ch 1B         | MAR1B    | XX101010 | 2AH    | 94   |

|     | DMA I/O Address Register Ch 1L            | IAR1L    | XX101011 | 2BH    | 102  |

|     | DMA I/O Address Register Ch 1H            | IAR1H    | XX101100 | 2CH    | 102  |

|     | DMA I/O Address Register Ch 1             | IAR1B    | XX101101 | 2DH    | 94   |

|     | DMA Byte Count Register Ch 1L             | BCR1L    | XX101110 | 2EH    | 94   |

|     | DMA Byte Count Register Ch 1H             | BCR1H    | XX101111 | 2FH    | 94   |

|     | DMA Status Register                       | DSTAT    | XX110000 | 30H    | 95   |

|     | DMA Mode Register                         | DMODE    | XX110001 | 31H    | 97   |

|     | DMA/WAIT Control Register                 | DCNTL    | XX110010 | 32H    | 101  |

## Table 7. I/O Address Map (Z8S180/Z8L180-Class Processors Only) (Continued)

| Bit<br>Position | Bit/Field     | R/W | Value  | Description                                         |

|-----------------|---------------|-----|--------|-----------------------------------------------------|

| 2               | LNIO          | R/W | 0<br>1 | Standard Drive<br>33% Drive on certain external I/O |

| 1               | LNCPUCTL      | R/W | 0<br>1 | Standard Drive<br>33% Drive on CPU control signals  |

| 0               | LNAD/<br>DATA | R/W | 0<br>1 | Standard Drive<br>33% drive on A10–A0, D7–D0        |

## Memory Management Unit (MMU)

The Z8X180 features an on-chip MMU which performs the translation of the CPU 64KB (16-bit addresses 0000H to FFFFH) logical memory address space into a 1024KB (20-bit addresses 00000H to FFFFFH) physical memory address space. Address translation occurs internally in parallel with other CPU operation.

## **Logical Address Spaces**

The 64KB CPU logical address space is interpreted by the MMU as consisting of up to three separate logical address areas, Common Area 0, Bank Area, and Common Area 1.

As depicted in Figure 23, a variety of logical memory configurations are possible. The boundaries between the Common and Bank Areas can be programmed with 4KB resolution.

## **MMU and RESET**

During RESET, all bits of the CA field of CBAR are set to 1 while all bits of the BA field of CBAR, CBR and BBR are reset to 0. The logical 64KB address space corresponds directly with the first 64KB 0000H to FFFFH) of the 1024KB 0000H. to FFFFFH) physical address space. Thus, after RESET, the Z8X180 begins execution at logical and physical address 0.

## **MMU Register Access Timing**

When data is written into CBAR, CBR or BBR, the value is effective from the cycle immediately following the I/O write cycle which updates these registers.

During MMU programming insure that CPU program execution is not disrupted. The next cycle following MMU register programming is normally an Op Code fetch from the newly translated address. One technique is to localize all MMU programming routines in a Common Area that is always enabled.

memory mapped I/O. transfers, the CKA0/DREQ0 pin automatically functions as input pin or output pin even if it has been programmed as output pin for CKA0. And the CKA1/TEND0 pin functions as an input or an output pin for TEND0 by setting CKA1D to 1 in CNTLA1.

To initiate memory to/from I/O (and memory to/from memory mapped I/O) DMA transfer for channel 0, perform the following operations:

1. Load the memory and I/O or memory mapped I/O source and destination addresses into SAR0 and DAR0.

I/O addresses (not memory mapped I/O are limited to 16 bits (A0–A15). Make sure that bits A16, A17 and A19 are 0 (A18 is a don't care) to correctly enable the external  $\overline{\text{DREQ0}}$  input.

- 2. Specify memory to/from I/O or memory to/from memory mapped I/O mode and address increment/decrement in the SM0, SM1, DM0 and DM1 bits of DMODE.

- 3. Load the number of bytes to transfer in BCR0.

- 4. Specify whether DREQ0 is edge- or level-sense by programming the DMS0 bit of DCNTL.

- 5. Enable or disable DMA termination interrupt with the DIE0 bit in DSTAT.

- 6. Program DE0: = 1 (with  $\overline{\text{DWEO}}$  = 0 in the same access) in DSTAT and the DMA operation begins under the control of the  $\overline{\text{DREQ0}}$  input.

## Memory to ASCI - Channel 0

Channel 0 has extra capability to support DMA transfer to/from the onchip two channel ASCI. In this case, the external  $\overline{DREQ0}$  input is not used for DMA timing. Rather, the ASCI status bits are used to generate an internal  $\overline{DREQ0}$  The TDRE (Transmit Data Register Empty) bit and the RDRF (Receive Data Register Full) bit are used to generate an internal

123

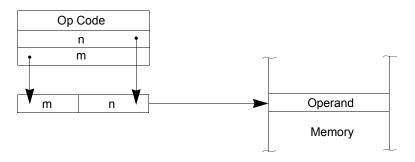

## ASCI Control Register A0, 1 (CNTLA0, 1)

Each ASCI channel Control Register A configures the major operating modes such as receiver/transmitter enable and disable, data format, and multiprocessor communication mode.

ASCI Status Register 1 (STAT1: 05H)

| Bit                                                                 | 7    | 6    | 5  | 4  | 3   | 2     | 1    | 0   |

|---------------------------------------------------------------------|------|------|----|----|-----|-------|------|-----|

| Bit/Field                                                           | RDRF | OVRN | PE | FE | RIE | CTS1E | TDRE | TIE |

| R/W                                                                 | R    | R    | R  | R  | R/W | R/W   | R    | R/W |

| Reset                                                               | 0    | 0    | 0  | 0  | 0   | 0     | 0    | 0   |

| Note: $R = Read$ $W = Write$ $X = Indeterminate$ ? = Not Applicable |      |      |    |    |     |       |      |     |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7               | RDRF      | R   |       | <b>Receive Data Register Full</b> — RDRF is set to 1 when an incoming data byte is loaded into RDR. Note that if a framing or parity error occurs, RDRF is still set and the receive data (which generated the error) is still loaded into RDR. RDRF is cleared to 0 by reading RDR, when the DCD0 input is High, in IOSTOP mode, and during RESET. |

| 6               | OVRN      | R   |       | <b>Overrun Error</b> — OVRN is set to 1 when RDR is full<br>and RSR becomes full. OVRN is cleared to 0 when the<br>EFR bit (Error Flag Reset) of CNTLA is written to 0,<br>when DCD0 is High, in IOSTOP mode, and during<br>RESET.                                                                                                                  |

| 5               | PE        | R   |       | <b>Parity Error</b> — PE is set to 1 when a parity error is detected on an incoming data byte and ASCI parity detection is enabled (the MOD1 bit of CNTLA is set to 1). PE is cleared to 0 when the EFR bit (Error Flag Reset) of CNTLA is written to 0, when DCD0 is High, in IOSTOP mode, and during RESET.                                       |

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                            |

|-----------------|-----------|-----|-------|--------------------------------------------------------------------------------------------------------|

| 2-0             | MOD2–0    | R/W |       | ASCI Data Format Mode 2, 1, 0 — These bits program the ASCI data format as follows.                    |

|                 |           |     |       | MOD2                                                                                                   |

|                 |           |     |       | 0: 7 bit data                                                                                          |

|                 |           |     |       | 1: 8 bit data                                                                                          |

|                 |           |     |       | MOD1                                                                                                   |

|                 |           |     |       | 0: No parity                                                                                           |

|                 |           |     |       | 1: Parity enabled                                                                                      |

|                 |           |     |       | MOD0                                                                                                   |

|                 |           |     |       | 0: 1 stop bit                                                                                          |

|                 |           |     |       | 1: 2 stop bits                                                                                         |

|                 |           |     |       | The data formats available based on all combinations of MOD2, MOD1 and MOD0 are described in Table 17. |

137

| Bit<br>Position | Bit/Field                  | R/W | Value  | Description                                         |

|-----------------|----------------------------|-----|--------|-----------------------------------------------------|

| 2               | Break<br>Feature<br>Enable | R/W | 0<br>1 | Break Feature Enable On<br>Break Feature Enable Off |

| 1               | Break<br>Detect<br>(RO)    | R/W | 0<br>1 | Break Detect On<br>Break Detect Off                 |

| 0               | Send<br>Break              | R/W | 0<br>1 | Normal Xmit<br>Drive TXA Low                        |

Each ASCI channel control register B configures multiprocessor mode, parity and baud rate selection.

ASCI0 Time Constant Low Register (I/O Address: 1AH) (Z8S180/L180-Class Processors Only)

| Bit                                                             | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                                           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: $R = Read$ W = Write X = Indeterminate ? = Not Applicable |     |     |     |     |     |     |     |     |

ASCI0 Time Constant High Register (I/O Address: 1BH) (Z8S180/L180-Class Processors Only)

| Bit                                                                                                                                       | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                                                                                                                       | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                                                                                                                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Note: $\mathbf{R} = \mathbf{R}$ and $\mathbf{W} = \mathbf{W}$ rite $\mathbf{X} = \mathbf{I}$ indeterminate $2 = \mathbf{N}$ of Applicable |     |     |     |     |     |     |     |     |

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

152

- c. Poll the RE bit in CNTR until RE = 0.

- d. Read the receive data from TRDR.

- e. Repeat steps 2 to 4 for each receive data byte.

- Receive–Interrupts

- a. Poll the RE bit in CNTR until RE is 0.

- b. Set the RE and EIE bits in CNTR to 1.

- c. When the receive interrupt occurs read the receive data from TRDR.

- d. Set the RE bit in CNTR to 1.

- e. Repeat steps 3 and 4 for each receive data byte.

## **CSI/O Operation Timing Notes**

- Transmitter clocking and receiver sampling timings are different from internal and external clocking modes. Figure 59 to Figure 62 illustrate CSI/O Transmit/Receive Timing.

- The transmitter and receiver is disabled TE and RE = 0) when initializing or changing the baud rate.

## **CSI/O Operation Notes**

- Disable the transmitter and receiver (TE and RE = 0) before initializing or changing the baud rate. When changing the baud rate after completion of transmission or reception, a delay of at least one bit time is required before baud rate modification.

- When RE or TE is cleared to 0 by software, a corresponding receive or transmit operation is immediately terminated. Normally, TE or RE is only cleared to 0 when EF is 1.

- Simultaneous transmission and reception is not possible. Thus, TE and RE are not both 1 at the same time.

| Bit<br>Position | Bit/Field | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|-----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–6             | TIF1–0    | R   |       | <b>TIF1: Timer Interrupt Flag</b> — When TMDR1<br>decrements to 0, TIF1 is set to 1. This generates an<br>interrupt request if enabled by TIE1 = 1. TIF1 is reset to 0<br>when TCR is read and the higher or lower byte of<br>TMDR1 is read. During RESET, TIF1 is cleared to 0.<br>When TMDR0 decrements to 0, TIF0 is set to 1. This<br>generates an interrupt request if enabled by TIE0 = 1.<br>TIF0 is reset to 0 when TCR is read and the higher or<br>lower byte of TMDR0 is read. During RESET, TIF0 is<br>cleared to 0. |

| 5-4             | TIE1–0    | R/W |       | <b>Timer Interrupt Enable</b> — When TIE1 is set to 1, TIF1<br>= 1 generates a CPU interrupt request. When TIE1 is reset<br>to 0, the interrupt request is inhibited. During RESET,<br>TIE1 is cleared to 0.<br>When TIE0 is set to 1, TIF0 = 1 generates a CPU interrupt<br>request. When TIE0 is reset to 0, the interrupt request is<br>inhibited. During RESET, TIE0 is cleared to 0.                                                                                                                                        |

| 3-2             | TOC1-0    | R/W |       | <b>Timer Output Control</b> — TOC1, and TOC0 control the output of PRT1 using the multiplexed A18/TOUT pin as shown in Table 23. During RESET, TOC1 and TOC0 are cleared to 0. This selects the address function for A18/TOUT. By programming TOC1 and TOC0 the A18/TOUT pin can be forced HIGH, LOW, or toggled when TMDR1 decrements to 0. Reference Table 23.                                                                                                                                                                 |

| 1-0             | TDE1–0    | R/W |       | <b>Timer Down Count Enable</b> — TDE1 and TDE0 enable<br>and disable down counting for TMDR1 and TMDR0<br>respectively. When TDEn ( $n = 0, 1$ ) is set to 1, down<br>counting is executed for TMDRn. When TDEn is reset to<br>0, down counting is stopped and TMDRn is freely read or<br>written. TDE1 and TDE0 are cleared to 0 during RESET<br>and TMDRn does not decrement until TDEn is set to 1.                                                                                                                           |

These devices require connection with the Z8X180 synchronous E clock output. The speed (access time) required for the peripheral devices are determined by the Z8X180 clock rate. Table 24, and Figure 67 through Figure 70 define E clock output timing.

Wait States are inserted in Op Code fetch, memory read/write, and I/O read/write cycles which extend the duration of E clock output High. During I/O read/write cycles with no Wait States (only occurs during on-chip I/O register accesses), E does not go High.

| Condition                                               | Duration of E Clock Output High |                        |  |  |  |  |

|---------------------------------------------------------|---------------------------------|------------------------|--|--|--|--|

| Op Code Fetch Cycle<br>Memory Read/Write Cycle          | T2 rise - T3 fall               | (1.5 Phi + nw x Phi)   |  |  |  |  |

| I/O read Cycle                                          | 1st Tw rise - T3 fall           | (0.5Phi + nw x Phi)    |  |  |  |  |

| I/O Write Cycle                                         | 1st Tw rise - T3 rise           | In <sub>w</sub> x Phi) |  |  |  |  |

| NMI Acknowledge 1st MC                                  | T2 rise - T3 fall               | (1.5 Phi)              |  |  |  |  |

| INT0 Acknowledge 1st MC                                 | 1st Tw rise - T3 fall           | (0.50 + nw x Phi)      |  |  |  |  |

| BUS RELEASE mode<br>SLEEP mode<br>SYSTEM STOP mode      | Phi fall - Phi fall             | (2 Phi or 1 Phi)       |  |  |  |  |

| Note: nw = the number of Wait States; MC: Machine Cycle |                                 |                        |  |  |  |  |

| Table 24. | E Clock | Timing in | Each | Condition |

|-----------|---------|-----------|------|-----------|

|-----------|---------|-----------|------|-----------|

166

# Software Architecture

## **INSTRUCTION SET**

The Z80180 is object code-compatible with the Z80 CPU. Refer to the Z80 CPU Technical Manual or the Z80 Assembly Language Programming Manual for further details.

| Table 26. | Instruction S | Set Summary |

|-----------|---------------|-------------|

|-----------|---------------|-------------|

| New Instructions | Operation                                            |

|------------------|------------------------------------------------------|

| SLP              | Enter SLEEP mode                                     |

| MLT              | 8-bit multiply with 16-bit result                    |

| INO g, (m)       | Input contents of immediate I/O address              |

| OUT0 (m), g      | Output register contents to immediate I/O address    |

| OTIM             | Block output - increment                             |

| OTIMR            | Block output - increment and repeat                  |

| OTDM             | Block output - decrement                             |

| OTDMR            | Block output - decrement and repeat                  |

| TSTIO m          | Non-destructive AND, I/O port, and accumulator       |

| TST g            | Non-destructive AND, register, and accumulator       |

| TST m            | Non-destructive AND, immediate data, and accumulator |

| TST (HL)         | Non-destructive AND, memory data, and accumulator    |

## **SLP** - Sleep

The SLP instruction causes the Z80180 to enter the SLEEP low power consumption mode. See page 32 for a complete description of the SLEEP state.

181

#### 8-bit Register

| g or g field ' | Register |  |  |  |

|----------------|----------|--|--|--|

| 0              | В        |  |  |  |

| 0 0 1          | С        |  |  |  |

| 0 1 0          | D        |  |  |  |

| 0 1 1          | E        |  |  |  |

| 1 0 0          | Н        |  |  |  |

| 1 0 1          | L        |  |  |  |

| 1 1 0          |          |  |  |  |

| 1 1 1          | А        |  |  |  |

|                |          |  |  |  |

| ww field | Register |

|----------|----------|

| 0 0      | ВC       |

| 0 1      | DE       |

| 1 0      | ΗL       |

| 1 1      | SP       |

| xx field | Register |

|----------|----------|

| 0 0      | ВС       |

| 0 1      | DE       |

| 1 0      | ΙX       |

| 1 1      | SP       |

#### 16-bit Register

| •        |          |

|----------|----------|

| zz field | Register |

| 0 0      | ВС       |

| 0 1      | DE       |

| 1 0      | ΗL       |

| 1 1      | AF       |

| yy field | Register |

|----------|----------|

| 0 0      | ВС       |

| 0 1      | DE       |

| 1 0      | ΙY       |

| 1 1      | SP       |

Suffixed H and L ww,xx,yy,zz (ex. wwH,IXL) indicate upper and lower 8-bit of the 16-bit register respectively.

## Figure 75. Register Direct — Bit Field Definitions

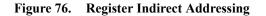

## **Register Indirect (REG)**

The memory operand address is contained in one of the 16-bit General Purpose Registers (BC, DE, and HL) as illustrated in Figure 76.

182

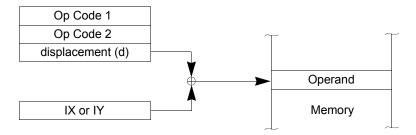

## Indexed (INDX)

The memory operand address is calculated using the contents of an Index Register (IX or IY) and an 8-bit signed displacement specified in the instruction. Refer to Figure 77

Figure 77. Indexed Addressing

# **Extended (EXT)**

The memory operand address is specified by two bytes contained in the instruction, as depicted in Figure 78.

Figure 78. Extended Addressing

|            |       | Machine |                                                                    |

|------------|-------|---------|--------------------------------------------------------------------|

| MNEMONICS  | Bytes | Cycles  | States                                                             |

|            | 3     | 6       | 16                                                                 |

|            |       |         | (If condition is true)                                             |

| CALL mn    | 3     | 6       | 16                                                                 |

| CCF        | 1     | 1       | 3                                                                  |

| CPD        | 2     | 6       | 12                                                                 |

| CPDR       | 2     | 8       | 14                                                                 |

|            |       |         | $(\text{If BC}_R \neq 0 \text{ and } \text{Ar} \neq (\text{HL})_M$ |

|            | 2     | 6       | 12                                                                 |

|            |       |         | $(\text{If BC}_{R} = 0 \text{ or } \text{Ar} = (\text{HL})_{M}$    |

| CP (HL)    | 1     | 2       | 6                                                                  |

| СРІ        | 2     | 6       | 12                                                                 |

| CPIR       | 2     | 8       | 14                                                                 |

|            |       |         | $(\text{If BC}_R \neq 0 \text{ and } \text{Ar} \neq (\text{HL})_M$ |

|            | 2     | 6       | 12                                                                 |

|            |       |         | $(If BCR = 0 \text{ or } Ar = (HL)_M$                              |

| CP (IX+d)  | 3     | 6       | 14                                                                 |

| CP (IY+d)  | 3     | 6       | 14                                                                 |

| CPL        | 1     | 1       | 3                                                                  |

| CP m       | 2     | 2       | 6                                                                  |

| CP g       | 1     | 2       | 4                                                                  |

| DAA        | 1     | 2       | 4                                                                  |

| DEC (HL)   | 1     | 4       | 10                                                                 |

| DEC IX     | 2     | 3       | 7                                                                  |

| DEC IY     | 2     | 3       | 7                                                                  |

| DEC (IX+d) | 3     | 8       | 18                                                                 |

| DEC (IY+d) | 3     | 8       | 18                                                                 |

| DEC g      | 1     | 2       | 4                                                                  |

| DEC ww     | 1     | 2       | 4                                                                  |

| DI         | 1     | 1       | 3                                                                  |

| DJNZ j     | 2     | 5       | 9 (if Br $\neq$ 0)                                                 |

238

|               |       | Machine |                     |

|---------------|-------|---------|---------------------|

| MNEMONICS     | Bytes | Cycles  | States              |

| LD g,g'       | 1     | 2       | 4                   |

| LD SP,HL      | 1     | 2       | 4                   |

| LD SP,IX      | 2     | 3       | 7                   |

| LD SP,IY      | 2     | 3       | 7                   |

| MLT ww"       | 2     | 13      | 17                  |

| NEG           | 2     | 2       | 6                   |

| NOP           | 1     | 1       | 3                   |

| OR (HL)       | 1     | 2       | 6                   |

| OR (IX+d)     | 3     | 6       | 14                  |

| OR (IY+d)     | 3     | 6       | 14                  |

| OR m          | 2     | 2       | 6                   |

| OR g          | 1     | 2       | 4                   |

| OTDM**        | 2     | 6       | 14                  |

| OTDMR**       | 2     | 8       | 16 (If Br $\neq$ 0) |

|               | 2     | 6       | 14 (If Br = 0)      |

| OTDR          | 2     | 6       | 14 (If Br $\neq$ 0) |

|               | 2     | 4       | 12 (If Br = $0$     |

| OTIM**        | 2     | 6       | 14                  |

| OTIMR**       | 2     | 8       | 16 (If Br $\neq$ 0) |

|               | 2     | 6       | 14 (If Br = 0)      |

| OTIR          | 2     | 6       | 14 (If Br $\neq$ 0) |

|               | 2     | 4       | 12 (If Br = $0$ )   |

| OUTD          | 2     | 4       | 12                  |

| OUTI          | 2     | 4       | 12                  |

| OUT (m),A     | 2     | 4       | 10                  |

| OUT (C),g     | 2     | 4       | 10                  |

| OUT0 (m),g ** | 3     | 5       | 13                  |

| POP IX        | 2     | 4       | 12                  |

| POP IY        | 2     | 4       | 12                  |

| POP zz        | 1     | 3       | 9                   |

242

256

| Instruction             | Machine<br>Cycle | States | Address                | Data           | RD | WR | MREQ | IORQ | <u>M1</u> | HALT | ST |

|-------------------------|------------------|--------|------------------------|----------------|----|----|------|------|-----------|------|----|

|                         | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| DJNZ j (If Br $\neq$ 0) | MC2              | Ti*2   | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| (11 D1 + 0)             | MC3              | T1T2T3 | 1st operand<br>Address | j-2            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                         | MC4~M<br>C5      | TiTi   | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                         | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| DJNZ j<br>(If Br=0)     | MC2              | Ti*1   | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

| (п.в. о)                | MC3              | T1T2T3 | 1st operand<br>Address | j-2            | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| EI*3                    | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| EX DE, HL<br>EXX        | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| EX AF, AF'              | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st<br>Op Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

|                         | MC2              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                         | MC1              | T1T2T3 | 1st Op Code<br>Address | 1st Op<br>Code | 0  | 1  | 0    | 1    | 0         | 1    | 0  |

| EX (SP), HL             | MC2              | T1T2T3 | SP                     | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

| LA (51), HL             | MC3              | T1T2T3 | SP+1                   | DATA           | 0  | 1  | 0    | 1    | 1         | 1    | 1  |

|                         | MC4              | Ti     | *                      | Z              | 1  | 1  | 1    | 1    | 1         | 1    | 1  |

|                         | MC5              | T1T2T3 | SP+1                   | Н              | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

|                         | MC6              | T1T2T3 | SP                     | L              | 1  | 0  | 0    | 1    | 1         | 1    | 1  |

Table 51.

Bus and Control Signal Condition in Each Machine Cycle (Continued)

\*2 DMA, REFRESH, or BUS RELEASE cannot be executed after this state. (Request is ignored) \*3 Interrupt request is not sampled.

294

## Table 57. Internal I/O Registers (Continued)

308

Memory and I/O Wait state insertion 29 Memory management unit (MMU) 13 Memory to ASCI 109 Memory to memory 105 MMU Register description 60 Mode HALT 31 IOSTOP 35 SLEEP 33 SYSTEM STOP 35 Modem control signals 138

# Ν

NMI and DMA operation timing diagram 115 Use 74 Non-maskable interrupt 72

# 0

On-chip clock generator Circuit board design rules 170 External clock interface 169 Operating frequencies 168 Operation modes Control register 84 CPU timing 18 IOC 16 M1 Enable 15 M1 temporary enable 16

## Ρ

Pin description A0 through CTS1 7 BUSREQ through RFSH 9 D0 through INT2 8 RTS0 through TEND1 10 TEST through XTAL 10 Pin package 64-pin DIP 3 68-pin PLCC 4 80-pin QFP 5 Programmable reload timer (PRT) 14 Programming Level-sense 109 PRT Block diagram 157 Bus release mode timing diagram 167 Interrupt request generation 164 Timer control register 161

# R

Refresh 87 Control register 88 Register ASCI Control A0 125 ASCI Control A1 128 ASCI Control B 131 ASCI Status 0 120 ASCI Status 1 123