Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

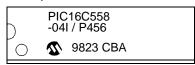

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c554-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

Note: For additional information on enhancements, see Appendix A

### CMOS Technology:

- Low power, high speed CMOS EPROM technology

- Fully static design

- Wide operating voltage range

2.5V to 5.5V

- Commercial, Industrial and Extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

#### **Device Differences**

| Device    | Voltage Range | Oscillator |

|-----------|---------------|------------|

| PIC16C554 | 2.5 - 5.5     | (Note 1)   |

| PIC16C557 | 2.5 - 5.5     | (Note 1)   |

| PIC16C558 | 2.5 - 5.5     | (Note 1)   |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

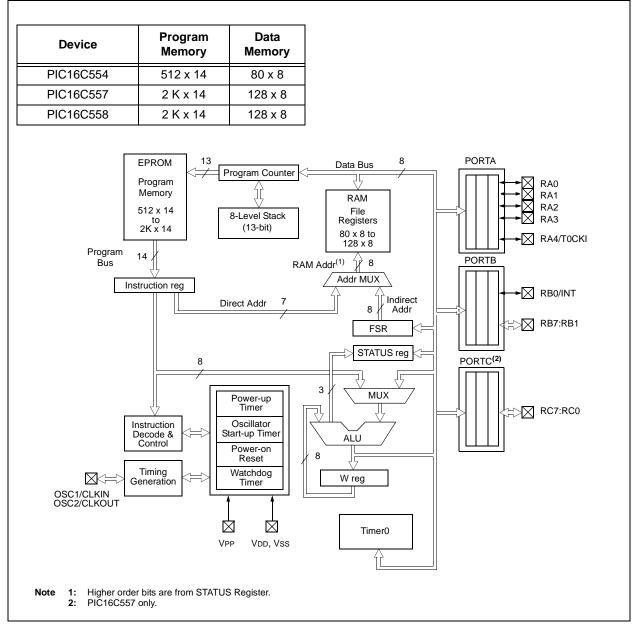

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C55X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C55X uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently from 8-bit wide data words. Instruction opcodes are 14-bit wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a singlecycle (200 ns @ 20 MHz) except for program branches. The table below lists the memory (EPROM and RAM).

| Device    | Program<br>Memory<br>(EPROM) | Data<br>Memor<br>(RAM) |

|-----------|------------------------------|------------------------|

| PIC16C554 | 512                          | 80                     |

| PIC16C557 | 2 K                          | 128                    |

| PIC16C558 | 2 K                          | 128                    |

The PIC16C554 addresses 512 x 14 on-chip program memory. The PIC16C557 and PIC16C558 addresses 2 K x 14 program memory. All program memory is internal.

The PIC16C55X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped into the data memory. The PIC16C55X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C55X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C55X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

# PIC16C55X

# FIGURE 3-1: BLOCK DIAGRAM

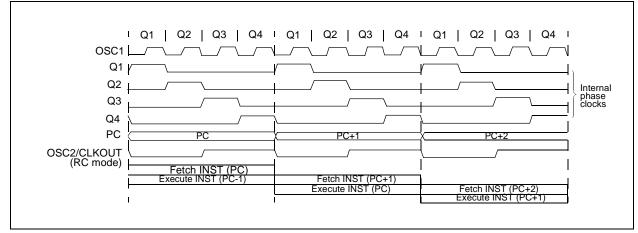

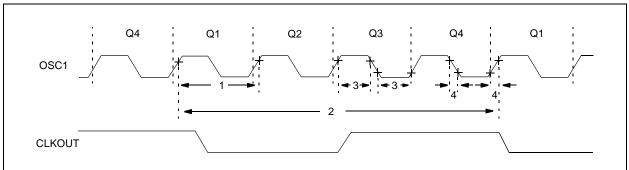

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2.

# 3.2 Instruction Flow/Pipelining

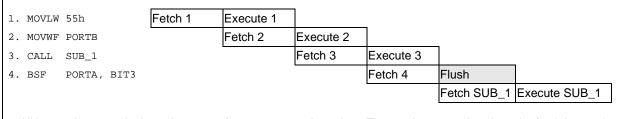

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle

while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

# FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

# EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

# 4.0 MEMORY ORGANIZATION

### 4.1 Program Memory Organization

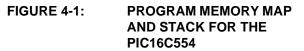

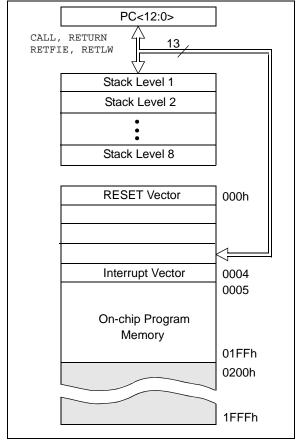

The PIC16C55X has a 13-bit program counter capable of addressing an 8 K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C554 and 2K x 14 (0000h - 07FFh) for the PIC16C557 and PIC16C558 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 spaces in the PIC16C554, or 2K x 14 space of the PIC16C558 and PIC16C557. The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2).

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C557 AND PIC16C558

#### 4.2 Data Memory Organization

The data memory (Figure 4-3 through Figure 4-5) is partitioned into two banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bank 0 is selected when the RP0 bit (STATUS <5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-6Fh (Bank 0) on the PIC16C554 and 20-7Fh (Bank 0) and A0-BFh (Bank 1) on the PIC16C558 and PIC16C557 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $80 \times 8$  in the PIC16C554 and 128 x 8 in the PIC16C557 and PIC16C558. Each can be accessed either directly or indirectly through the File Select Register, FSR (Section 4.4).

#### FIGURE 4-5: DATA MEMORY MAP FOR THE PIC16C558

| File File Address Address                         |                     |                     |     |  |  |

|---------------------------------------------------|---------------------|---------------------|-----|--|--|

| 00h                                               | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h |  |  |

| 01h                                               | TMR0                | OPTION              | 81h |  |  |

| 02h                                               | PCL                 | PCL                 | 82h |  |  |

| 03h                                               | STATUS              | STATUS              | 83h |  |  |

| 04h                                               | FSR                 | FSR                 | 84h |  |  |

| 05h                                               | PORTA               | TRISA               | 85h |  |  |

| 06h                                               | PORTB               | TRISB               | 86h |  |  |

| 07h                                               | 1 OKID              | THOE                | 87h |  |  |

| 08h                                               |                     |                     | 88h |  |  |

| 09h                                               |                     |                     | 89h |  |  |

| 0Ah                                               | PCLATH              | PCLATH              | 8Ah |  |  |

| 0Bh                                               | INTCON              | INTCON              | 8Bh |  |  |

| 0Dh                                               | INTCON              | INTCON              | 8Ch |  |  |

| 0Dh                                               |                     |                     | 8Dh |  |  |

| 0Eh                                               |                     | PCON                | 8Eh |  |  |

| 0En<br>0Fh                                        |                     | FCON                | 8Fh |  |  |

| 10h                                               |                     |                     | 90h |  |  |

| 10h<br>11h                                        |                     |                     | _   |  |  |

|                                                   |                     |                     | 91h |  |  |

| 12h                                               |                     |                     | 92h |  |  |

| 13h                                               |                     |                     | 93h |  |  |

| 14h                                               |                     |                     | 94h |  |  |

| 15h                                               |                     |                     | 95h |  |  |

| 16h                                               |                     |                     | 96h |  |  |

| 17h                                               |                     |                     | 97h |  |  |

| 18h                                               |                     |                     | 98h |  |  |

| 19h                                               |                     |                     | 99h |  |  |

| 1Ah                                               |                     |                     | 9Ah |  |  |

| 1Bh                                               |                     |                     | 9Bh |  |  |

| 1Ch                                               |                     |                     | 9Ch |  |  |

| 1Dh                                               |                     |                     | 9Dh |  |  |

| 1Eh                                               |                     |                     | 9Eh |  |  |

| 1Fh                                               |                     |                     | 9Fh |  |  |

| 20h                                               | Conoral             | Conorol             | A0h |  |  |

|                                                   | General<br>Purpose  | General<br>Purpose  |     |  |  |

|                                                   | Register            | Register            | BFh |  |  |

|                                                   |                     |                     |     |  |  |

|                                                   |                     |                     | C0h |  |  |

|                                                   |                     |                     |     |  |  |

|                                                   |                     |                     | -   |  |  |

|                                                   |                     |                     |     |  |  |

| 7Fh                                               |                     |                     | FFh |  |  |

|                                                   | Bank 0              | Bank 1              |     |  |  |

| Unimplemented data memory locations, read as '0'. |                     |                     |     |  |  |

| Note 1: Not a physical register.                  |                     |                     |     |  |  |

|                                                   |                     |                     |     |  |  |

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM.

The Special Function Registers can be classified into two sets (core and peripheral). The special function registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

# 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-1 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}$ ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a low or high should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

# 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

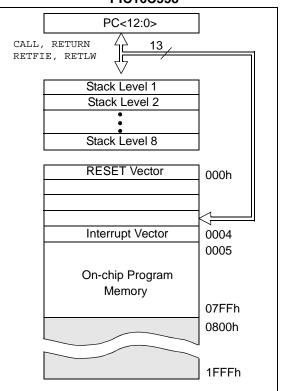

# 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

#### FIGURE 6-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

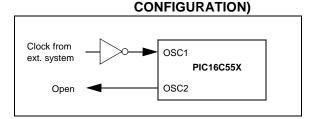

FIGURE 6-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

#### TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges                                                                                                                                        |                               |                                         |                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|

| Mode                                                                                                                                          | Freq                          | OSC1(C1)                                | OSC2(C2)                                |

| ХТ                                                                                                                                            | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |

| HS                                                                                                                                            | 8.0 MHz<br>16.0 MHz           | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |

| <b>Note 1:</b> Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design |                               |                                         |                                         |

| of the oscillator but also increases the    |

|---------------------------------------------|

| start-up time. These values are for design  |

| guidance only. Since each resonator has     |

| its own characteristics, the user should    |

| consult with the resonator manufacturer for |

| appropriate values of external compo-       |

| nents.                                      |

| TABLE 6-2: | <b>CAPACITOR SELECTION FOR</b> |

|------------|--------------------------------|

|            | CRYSTAL OSCILLATOR             |

|            | (PRELIMINARY)                  |

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC1(C1)    | OSC2(C2)     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|

| LP      | 32 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 - 100 pF | 68 - 100 pF  |

|         | 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 - 30 pF  | 15 - 30 pF   |

| XT      | 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 - 150 pF | 150 - 200 pF |

|         | 2 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |

|         | 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |

| HS      | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |

|         | 10 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |

|         | 20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |

| Note 1: | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid over-<br>driving crystals with low-drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>with the crystal manufacturer for appropri-<br>ate values of external components. |             |              |

#### TABLE 6-5:INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset                          | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. **Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register             | Address | Power-on Reset | MCLR Reset during normal<br>operation<br>MCLR Reset during SLEEP<br>WDT Reset | Wake-up from SLEEP<br>through interrupt<br>Wake-up from SLEEP<br>through WDT timeout |

|----------------------|---------|----------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| W                    | —       | XXXX XXXX      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| INDF                 | 00h     | _              | _                                                                             | _                                                                                    |

| TMR0                 | 01h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PCL                  | 02h     | 0000 0000      | 0000 0000                                                                     | PC + 1 <sup>(2)</sup>                                                                |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                      | uuuq quuu <sup>(3)</sup>                                                             |

| FSR                  | 04h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PORTA                | 05h     | x xxxx         | u uuuu                                                                        | u uuuu                                                                               |

| PORTB                | 06h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PORTC <sup>(4)</sup> | 06h     | xxxx xxxx      | uuuu uuuu                                                                     | սսսս սսսս                                                                            |

| PCLATH               | 0Ah     | 0 0000         | 0 0000                                                                        | u uuuu                                                                               |

| INTCON               | 0Bh     | 0000 000x      | 0000 000u                                                                     | uuuu uuuu <sup>(1)</sup>                                                             |

| OPTION               | 81h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| TRISA                | 85h     | 1 1111         | 1 1111                                                                        | u uuuu                                                                               |

| TRISB                | 86h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| TRISC <sup>(4)</sup> | 86h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| PCON                 | 8Eh     | 0-             | u-                                                                            | u-                                                                                   |

#### TABLE 6-6: INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 6-5 for RESET value for specific condition.

4: PIC16C557 only.

#### 6.5.1 RB0/INT INTERRUPT

An external interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION<6>) is set, or falling if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 6.8 for details on SLEEP and Figure 6-14 for timing of wakeup from SLEEP through RB0/INT interrupt.

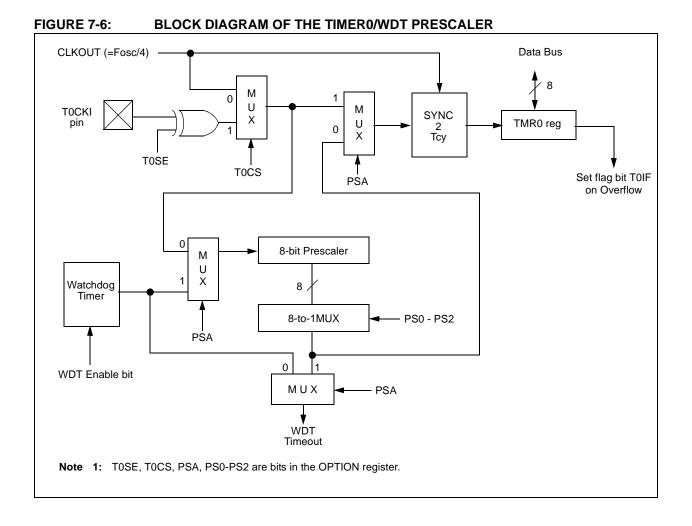

#### 6.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 7.0.

#### 6.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may get set.

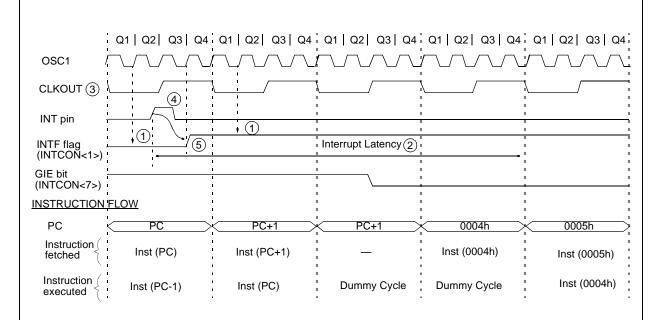

FIGURE 6-12: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3-4 TCY where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in RC Oscillator mode.

- 4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT. Lines 5-7 are required only if the desired postscaler rate is 1:1 (PS<2:0> = 000) or 1:2 (PS<2:0> = 001).

| EXAMPLE 7-1: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (TIMER0→WDT)       |

|       | · · · · ·            |                          |

|-------|----------------------|--------------------------|

| BCF   | STATUS, RPO          | ;Skip if already in      |

|       |                      | ;Bank 0 CLRWDT Clear WDT |

| CLRF  | TMR0                 | ;Clear TMR0 & Prescaler  |

| BSF   | STATUS, RPO          | ;Bank 1                  |

| MOVLW | '00101111 <i>'</i> b | ;These 3 lines (5, 6, 7) |

| MOVWF | OPTION               | ;Are required only if    |

|       |                      | ;Desired PS<2:0> are     |

|       |                      | ;CLRWDT 000 or 001       |

| MOVLW | '00101xxx'b          | ;Set Postscaler to       |

| MOVWF | OPTION               | ;Desired WDT rate        |

| BCF   | STATUS, RPO          | ;Return to Bank 0        |

|       |                      |                          |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (           | · / · ····=···/     |

|--------|-------------|---------------------|

| CLRWDT |             | ;Clear WDT and      |

|        |             | ;prescaler          |

| BSF    | STATUS, RPO |                     |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| MOVWF  | OPTION      |                     |

| BCF    | STATUS, RPO |                     |

|        |             |                     |

# TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                   | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-------------------------|-------|--------|--------|--------|-----------|-----------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 m | ïmer0 module's register |       |        |        |        | xxxx xxxx | uuuu uuuu |                 |                                 |

| 0Bh/8Bh | INTCON | GIE      | Reserved                | TOIE  | INTE   | RBIE   | T0IF   | INTF      | RBIF      | 0000 000x       | 0000 000x                       |

| 81h     | OPTION | RBPU     | INTEDG                  | TOCS  | TOSE   | PSA    | PS2    | PS1       | PS0       | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        | _                       |       | TRISA4 | TRISA3 | TRISA2 | TRISA1    | TRISA0    | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0',

**Note 1:** Shaded bits are not used by TMR0 module.

# PIC16C55X

| BCF              | Bit Clea                                                                      | ar f          |            |      |  |  |

|------------------|-------------------------------------------------------------------------------|---------------|------------|------|--|--|

| Syntax:          | [ label ]                                                                     | BCF 1         | f,b        |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |               |            |      |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                                     |               |            |      |  |  |

| Status Affected: | None                                                                          |               |            |      |  |  |

| Encoding:        | 01                                                                            | 00bb          | bfff       | ffff |  |  |

| Description:     | Bit 'b' in re                                                                 | gister 'f' is | s cleared. |      |  |  |

| Words:           | 1                                                                             |               |            |      |  |  |

| Cycles:          | 1                                                                             |               |            |      |  |  |

| Example          | BCF                                                                           | FLAG_F        | REG, 7     |      |  |  |

|                  | Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |               |            |      |  |  |

|  | Bit | Set | f |

|--|-----|-----|---|

|--|-----|-----|---|

BSF

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |        |        |   |  |  |  |

|------------------|---------------------------------------------------------------------|--------|--------|---|--|--|--|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |        |        |   |  |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |        |        |   |  |  |  |

| Status Affected: | None                                                                |        |        |   |  |  |  |

| Encoding:        | 01 01bb bfff ffff                                                   |        |        |   |  |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |        |        |   |  |  |  |

| Words:           | 1                                                                   |        |        |   |  |  |  |

| Cycles:          | 1                                                                   |        |        |   |  |  |  |

| Example          | BSF                                                                 | FLAG_F | REG, 7 | , |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction          |        |        |   |  |  |  |

|                  | FLAG_REG = 0x8A                                                     |        |        |   |  |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                     |  |  |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0' then the next<br>instruction is skipped. If bit 'b' is '0' then<br>the next instruction fetched during the<br>current instruction execution is dis-<br>carded, and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•                                                                                                                                                                                                        |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | PC = address HERE                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                  | After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1> = 1,<br>PO = address TRUE                                                                                                                                                                       |  |  |  |  |  |  |

|                  | PC = address FALSE                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

# PIC16C55X

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                            |  |  |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                  |              |      |      |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|--|--|

| Syntax:          | [ label ]                                                                                                                                               | RETUR        | N    |      |  |  |

| Operands:        | None                                                                                                                                                    |              |      |      |  |  |

| Operation:       | $TOS \to PC$<br>None                                                                                                                                    |              |      |      |  |  |

| Status Affected: |                                                                                                                                                         |              |      |      |  |  |

| Encoding:        | 00                                                                                                                                                      | 0000         | 0000 | 1000 |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two-cycle instruction. |              |      |      |  |  |

| Words:           | 1                                                                                                                                                       |              |      |      |  |  |

| Cycles:          | 2                                                                                                                                                       |              |      |      |  |  |

| Example          | RETURN                                                                                                                                                  |              |      |      |  |  |

|                  | After Inte<br>PC                                                                                                                                        | rrupt<br>= T | OS   |      |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                              | I                     |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                              | S                     |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                     | 0                     |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                          | 0                     |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                  | St                    |  |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                     | E                     |  |  |  |  |

| Description:     | The W register is loaded with the eight D<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |                       |  |  |  |  |

| Words:           | 1                                                                                                                                                                                     |                       |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                     |                       |  |  |  |  |

| Example          | CALL TABLE;W contains table<br>;offset value<br>• ;W now has table<br>value<br>•                                                                                                      | W<br>C <u>y</u><br>Ex |  |  |  |  |

| TABLE            | <pre>ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;</pre>                                                                                                                      |                       |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                    |                       |  |  |  |  |

|                  | W = 0x07                                                                                                                                                                              |                       |  |  |  |  |

|                  | After Instruction                                                                                                                                                                     |                       |  |  |  |  |

|                  | W = value of k8                                                                                                                                                                       |                       |  |  |  |  |

| RLF             | Rotate Left f through Carry                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| yntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    |  |  |  |  |  |  |  |

| perands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                          |  |  |  |  |  |  |  |

| peration:       | See description below                                                                                                                                                                                       |  |  |  |  |  |  |  |

| tatus Affected: | С                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| ncoding:        | 00 1101 dfff ffff                                                                                                                                                                                           |  |  |  |  |  |  |  |

| escription:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |  |  |  |  |  |  |  |

| /ords:          | 1                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| ycles:          | 1                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| xample          | RLF REG1,0                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                 | Before Instruction                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                 | <b>REG1</b> = 1110 0110                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                 | C = 0                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                 | After Instruction                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                 | <b>REG1</b> = 1110 0110                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                 | W = 1100 1100                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                 | C = 1                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                 |                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RRF               | Rotate Right f through Carry                                                                                                                                                                                 |                                               |                  |                    |             |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|--------------------|-------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                    | RRF 1                                         | ,d               |                    |             |  |  |  |

| Operands:         | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                  |                                               |                  |                    |             |  |  |  |

| Operation:        | See description below                                                                                                                                                                                        |                                               |                  |                    |             |  |  |  |

| Status Affected:  | С                                                                                                                                                                                                            |                                               |                  |                    |             |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                           | 1100                                          | dff              | f                  | ffff        |  |  |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                                               |                  |                    |             |  |  |  |

|                   | C Register f                                                                                                                                                                                                 |                                               |                  |                    |             |  |  |  |

|                   |                                                                                                                                                                                                              |                                               | Regist           | ter f              | ┠┺          |  |  |  |

| Words:            | 1                                                                                                                                                                                                            |                                               | Regist           | ter f              | ]•          |  |  |  |

| Words:<br>Cycles: | 1<br>1                                                                                                                                                                                                       | ]-▶[                                          | Regist           | ter f              | <b>]•</b> ] |  |  |  |

|                   | •                                                                                                                                                                                                            | ]-•[                                          |                  | ter f              | <b>]</b> •] |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                            |                                               | REG              |                    | <u>}</u>    |  |  |  |

| Cycles:           | 1<br>RRF                                                                                                                                                                                                     | struction                                     | REG              | \$1,0              | .0          |  |  |  |

| Cycles:           | 1<br>RRF<br>Before In:                                                                                                                                                                                       | struction                                     | REG<br>n<br>1110 | \$1,0              | .0          |  |  |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG                                                                                                                                                                                 | struction<br>1 = 1<br>= (                     | REG<br>n<br>1110 | \$1,0              | .0          |  |  |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG<br>C                                                                                                                                                                            | struction<br>1 = 1<br>= 0<br>ruction          | REG<br>n<br>1110 | \$1,0              | -           |  |  |  |

| Cycles:           | 1<br>RRF<br>Before Inst<br>REG<br>C<br>After Inst                                                                                                                                                            | struction<br>1 = 1<br>= (<br>ruction<br>1 = 1 | REG<br>N<br>L110 | ;1,0<br>011<br>011 | .0          |  |  |  |

#### SLEEP

| Syntax:          | [ <i>label</i><br>]                                                                                                                                                                                                                                        | SLEEP |      |      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|

| Operands:        | None                                                                                                                                                                                                                                                       |       |      |      |  |  |  |

| Operation:       | 00h $\rightarrow$ WDT,<br>0 $\rightarrow$ WDT prescaler,<br>1 $\rightarrow$ TO,<br>0 $\rightarrow$ PD                                                                                                                                                      |       |      |      |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                     |       |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                         | 0000  | 0110 | 0011 |  |  |  |

| Description:     | The power-down status bit, <u>PD</u> is<br>cleared. Timeout status bit, <u>TO</u> is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 6.8 for more details. |       |      |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                          |       |      |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                          |       |      |      |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                      |       |      |      |  |  |  |

| SUBLW               | Subtract W from Literal  |                                                                                                                                      |             |          |  |  |  |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBLW k |                                                                                                                                      |             |          |  |  |  |

| Operands:           | $0 \le k \le 255$        |                                                                                                                                      |             |          |  |  |  |

| Operation:          | $k - (W) \to (W)$        |                                                                                                                                      |             |          |  |  |  |

| Status<br>Affected: | C, DC, Z                 |                                                                                                                                      |             |          |  |  |  |

| Encoding:           | 11                       | 110x kkkk kkkk                                                                                                                       |             |          |  |  |  |

| Description:        | plement met              | The W register is subtracted (2's com-<br>plement method) from the eight bit literal<br>'k'. The result is placed in the W register. |             |          |  |  |  |

| Words:              | 1                        |                                                                                                                                      |             |          |  |  |  |

| Cycles:             | 1                        |                                                                                                                                      |             |          |  |  |  |

| Example 1:          | SUBLW                    | 0x02                                                                                                                                 |             |          |  |  |  |

|                     | Before Inst              | ruction                                                                                                                              |             |          |  |  |  |

|                     | W                        | = 1                                                                                                                                  |             |          |  |  |  |

|                     | С                        | = ?                                                                                                                                  | )           |          |  |  |  |

|                     | After Instru             | After Instruction                                                                                                                    |             |          |  |  |  |

|                     | W                        | = 1                                                                                                                                  |             |          |  |  |  |

|                     | С                        | = 1                                                                                                                                  | ; result is | positive |  |  |  |

| Example 2:          | Before Inst              | Before Instruction                                                                                                                   |             |          |  |  |  |

|                     | W                        | = 2                                                                                                                                  | <u>2</u>    |          |  |  |  |

|                     | С                        | = ?                                                                                                                                  | )           |          |  |  |  |

|                     | After Instru             | ction                                                                                                                                |             |          |  |  |  |

|                     | W                        | = 0                                                                                                                                  | )           |          |  |  |  |

|                     | С                        | = 1                                                                                                                                  | ; result is | s zero   |  |  |  |

| Example 3:          | Before Instruction       |                                                                                                                                      |             |          |  |  |  |

|                     | W                        | = 3                                                                                                                                  | 3           |          |  |  |  |

|                     | С                        | = ?                                                                                                                                  | <b>)</b>    |          |  |  |  |

|                     | After Instru             | ction                                                                                                                                |             |          |  |  |  |

|                     | W                        |                                                                                                                                      | )xFF        |          |  |  |  |

|                     | C                        | = 0                                                                                                                                  | ); result i | s nega-  |  |  |  |

tive

$\odot$  1996-2013 Microchip Technology Inc.

# 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Cha       | racteristi     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                               |     |           | $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial and |                                               |

|--------------|----------------|-------------------------------------------------------|-------------------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Param<br>No. | Sym            | Characteristic                                        | Min Typ† Max Units Conditions |     |           |                                                                                                                     | Conditions                                    |

| D020         | IPD            | Power-Down Current <sup>(3)</sup>                     |                               |     |           |                                                                                                                     |                                               |

|              |                | 16LC55X                                               | _                             | 0.7 | 2         | μΑ                                                                                                                  | VDD = 3.0V, WDT disabled                      |

|              |                | 16C55X                                                | —                             | 1.0 | 2.5<br>15 | μΑ<br>μΑ                                                                                                            | VDD = 4.0V, WDT disabled<br>(+85°C to +125°C) |

|              | $\Delta I$ WDT | WDT Current <sup>(5)</sup>                            |                               |     |           |                                                                                                                     |                                               |