Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c554-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

|                                          | _   |

|------------------------------------------|-----|

| .0 General Description                   | . 5 |

| .0 PIC16C55X Device Varieties            | . 7 |

| .0       General Description             | . 9 |

| .0 Memory Organization                   | 13  |

|                                          |     |

| 0.0 Special Features of the CPU          | 31  |

| .0 Timer0 Module                         |     |

| 0 Instruction Set Summary                | 53  |

| .0 Development Support                   | 67  |

| 0.0 Electrical Specifications            | 73  |

| 1.0 Packaging Information                | 87  |

| vppendix A: Enhancements                 | 97  |

| ppendix B: Compatibility                 | 97  |

| ndex                                     | 99  |

| Dn-Line Support 1                        | 01  |

| Systems Information and Upgrade Hot Line | 01  |

| Dn-Line Support                          | 02  |

| Product Identification System            | 03  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

#### TABLE 1-1: PIC16C55X FAMILY OF DEVICES

|             |                                      | PIC16C554                        | PIC16C557                        | PIC16C558                 |

|-------------|--------------------------------------|----------------------------------|----------------------------------|---------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 20                        |

| Memory      | EPROM Program Memory<br>(x14 words)  | 512                              | 2K                               | 2K                        |

|             | Data Memory (bytes)                  | 80                               | 128                              | 128                       |

| Peripherals | Timer Module(s)                      | TMR0                             | TMR0                             | TMR0                      |

|             | Interrupt Sources                    | 3                                | 3                                | 3                         |

|             | I/O Pins                             | 13                               | 22                               | 13                        |

| Features    | Voltage Range (Volts)                | 2.5-5.5                          | 2.5-5.5                          | 2.5-5.5                   |

| catares     | Brown-out Reset                      | —                                | —                                | —                         |

|             | Packages                             | 18-pin DIP, SOIC;<br>20-pin SSOP | 28-pin DIP, SOIC;<br>28-pin SSOP | 18-pin DIP, SOIC,<br>SSOP |

I/O current capability. All PIC16C55X Family devices use serial programming with clock pin RB6 and data pin RB7.

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C55X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C55X uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently from 8-bit wide data words. Instruction opcodes are 14-bit wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a singlecycle (200 ns @ 20 MHz) except for program branches. The table below lists the memory (EPROM and RAM).

| Device    | Program<br>Memory<br>(EPROM) | Data<br>Memor<br>(RAM) |

|-----------|------------------------------|------------------------|

| PIC16C554 | 512                          | 80                     |

| PIC16C557 | 2 K                          | 128                    |

| PIC16C558 | 2 K                          | 128                    |

The PIC16C554 addresses 512 x 14 on-chip program memory. The PIC16C557 and PIC16C558 addresses 2 K x 14 program memory. All program memory is internal.

The PIC16C55X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped into the data memory. The PIC16C55X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C55X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C55X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

| TABLE 3-1:         | PIC16C55X PINOUT DES |                        |       |                       |                       |                                                                                                                                                                                                                   |

|--------------------|----------------------|------------------------|-------|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name               | PDIP                 |                        |       | Pin<br>Type           | Buffer<br>Type        | Description                                                                                                                                                                                                       |

| 00000000000        |                      | SOIC                   | SSOP  |                       |                       | Description                                                                                                                                                                                                       |

| OSC1/CLKIN         | 16                   | 16                     | 18    |                       | ST/CMOS               | Oscillator crystal input/external clock source output.                                                                                                                                                            |

| OSC2/CLKOUT        | 15                   | 15                     | 17    | 0                     | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/VPP           | 4                    | 4                      | 4     | I/P                   | ST                    | Master clear (Reset) input/programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                           |

| RA0                | 17                   | 17                     | 19    | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA1                | 18                   | 18                     | 20    | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA2                | 1                    | 1                      | 1     | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA3                | 2                    | 2                      | 2     | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA4/T0CKI          | 3                    | 3                      | 3     | I/O                   | ST                    | Bi-directional I/O port or external clock input for TMR0.<br>Output is open drain type.                                                                                                                           |

| RB0/INT            | 6                    | 6                      | 7     | I/O                   | TTL/ST <sup>(1)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. RB0/INT can also be selected as an external interrupt pin.                                                                          |

| RB1                | 7                    | 7                      | 8     | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |

| RB2                | 8                    | 8                      | 9     | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |

| RB3                | 9                    | 9                      | 10    | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |

| RB4                | 10                   | 10                     | 11    | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                            |

| RB5                | 11                   | 11                     | 12    | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                            |

| RB6                | 12                   | 12                     | 13    | I/O                   | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for<br>internal weak pull-up. Interrupt-on-change pin. Serial pro-<br>gramming clock.                                                                          |

| RB7                | 13                   | 13                     | 14    | I/O                   | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin. Serial pro-<br>gramming data.                                                                              |

| RC0 <sup>(3)</sup> | 18                   | 18                     | 18    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC1 <sup>(3)</sup> | 19                   | 19                     | 19    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC2 <sup>(3)</sup> | 20                   | 20                     | 20    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC3 <sup>(3)</sup> | 21                   | 21                     | 21    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC4 <sup>(3)</sup> | 22                   | 22                     | 22    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC5 <sup>(3)</sup> | 22                   | 22                     | 22    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

|                    |                      |                        |       |                       |                       |                                                                                                                                                                                                                   |

| RC6 <sup>(3)</sup> | 24                   | 24                     | 24    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC7 <sup>(3)</sup> | 25                   | 25                     | 25    | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| Vss                | 5                    | 5                      | 5,6   | P                     |                       | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| VDD                | 14                   | 14                     | 15,16 | P                     |                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Legend:            |                      | = Output<br>= Not used |       | /O = Input<br>= Input | output                | P = Power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

|                    |                      | L = TTL inp            |       | – input               |                       |                                                                                                                                                                                                                   |

TABLE 3-1: PIC16C55X PINOUT DESCRIPTION

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: PIC16C557 only.

## 3.1 Clocking Scheme/Instruction Cycle

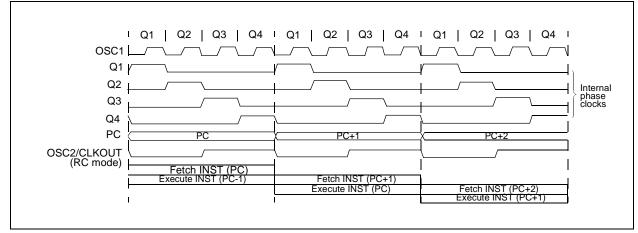

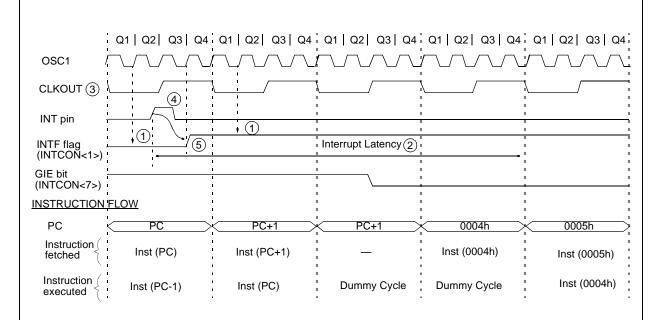

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

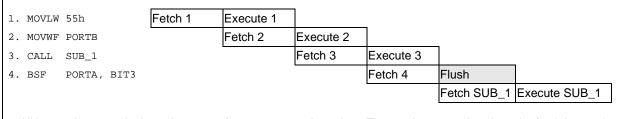

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle

while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### 6.0 SPECIAL FEATURES OF THE CPU

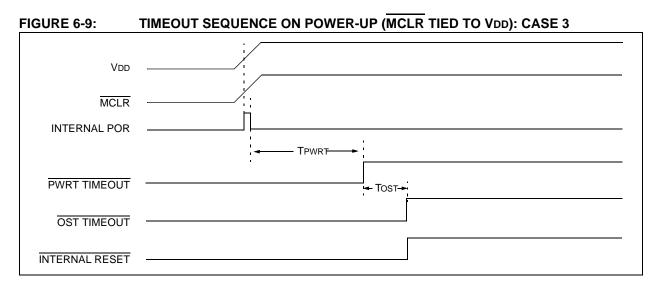

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### TABLE 6-5:INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset                          | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. **Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register             | Address | Power-on Reset | MCLR Reset during normal<br>operation<br>MCLR Reset during SLEEP<br>WDT Reset | Wake-up from SLEEP<br>through interrupt<br>Wake-up from SLEEP<br>through WDT timeout |

|----------------------|---------|----------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| W                    | —       | XXXX XXXX      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| INDF                 | 00h     | _              | _                                                                             | _                                                                                    |

| TMR0                 | 01h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PCL                  | 02h     | 0000 0000      | 0000 0000                                                                     | PC + 1 <sup>(2)</sup>                                                                |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                      | uuuq quuu <sup>(3)</sup>                                                             |

| FSR                  | 04h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PORTA                | 05h     | x xxxx         | u uuuu                                                                        | u uuuu                                                                               |

| PORTB                | 06h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PORTC <sup>(4)</sup> | 06h     | xxxx xxxx      | uuuu uuuu                                                                     | սսսս սսսս                                                                            |

| PCLATH               | 0Ah     | 0 0000         | 0 0000                                                                        | u uuuu                                                                               |

| INTCON               | 0Bh     | 0000 000x      | 0000 000u                                                                     | uuuu uuuu <sup>(1)</sup>                                                             |

| OPTION               | 81h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| TRISA                | 85h     | 1 1111         | 1 1111                                                                        | u uuuu                                                                               |

| TRISB                | 86h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| TRISC <sup>(4)</sup> | 86h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| PCON                 | 8Eh     | 0-             | u-                                                                            | u-                                                                                   |

#### TABLE 6-6: INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 6-5 for RESET value for specific condition.

4: PIC16C557 only.

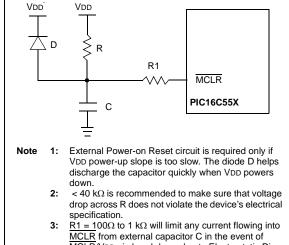

#### FIGURE 6-10: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

#### 6.5.1 RB0/INT INTERRUPT

An external interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION<6>) is set, or falling if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 6.8 for details on SLEEP and Figure 6-14 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 6.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 7.0.

#### 6.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may get set.

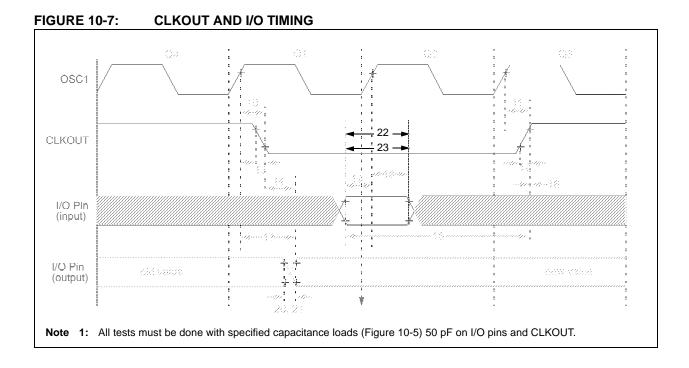

FIGURE 6-12: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3-4 TCY where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in RC Oscillator mode.

- 4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

## 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \le k \le 255$                                                                                                       |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| Words:           | 1                                                                                                                       |

| Cycles:          | 1                                                                                                                       |

| Example          | ADDLW 0x15                                                                                                              |

|                  | Before Instruction                                                                                                      |

|                  | W = 0x10                                                                                                                |

|                  | After Instruction                                                                                                       |

|                  | W = 0x25                                                                                                                |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |

| ANDLW            | AND Li                                  | teral wit  | h W            |          |  |

|------------------|-----------------------------------------|------------|----------------|----------|--|

| Syntax:          | [ label ]                               | ANDLW      | / k            |          |  |

| Operands:        | $0 \le k \le 2$                         | 255        |                |          |  |

| Operation:       | (W) .AN                                 | ID. (k) →  | • (W)          |          |  |

| Status Affected: | Z                                       |            |                |          |  |

| Encoding:        | 11                                      | 1001       | kkkk           | kkkk     |  |

|                  | The conter<br>AND'ed wi<br>result is pl | th the eig | ht bit literal | 'k'. The |  |

| Words:           | 1                                       |            |                |          |  |

| Cycles:          | 1                                       |            |                |          |  |

| Example          | ANDLW                                   | 0x5F       |                |          |  |

|                  | Before Instruction                      |            |                |          |  |

|                  | W                                       | =          | 0xA3           |          |  |

|                  | After Ins                               | struction  |                |          |  |

|                  | W                                       | =          | 0x03           |          |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                         |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |  |  |

-

| CLRW             | Clear W                              | V        |              |        |  |  |

|------------------|--------------------------------------|----------|--------------|--------|--|--|

| Syntax:          | [label] CLRW                         |          |              |        |  |  |

| Operands:        | None                                 |          |              |        |  |  |

| Operation:       | $00h \rightarrow (V 1 \rightarrow Z$ | V)       |              |        |  |  |

| Status Affected: | Z                                    |          |              |        |  |  |

| Encoding:        | 00                                   | 0001     | 0000         | 0011   |  |  |

| Description:     | W register set.                      | is clear | ed. Zero bit | (Z) is |  |  |

| Words:           | 1                                    |          |              |        |  |  |

| Cycles:          | 1                                    |          |              |        |  |  |

| Example          | CLRW                                 |          |              |        |  |  |

|                  | Before Instruction                   |          |              |        |  |  |

|                  | W                                    | =        | 0x5A         |        |  |  |

|                  | After Instruction                    |          |              |        |  |  |

|                  | W                                    | =        | 0x00         |        |  |  |

|                  | Z                                    | =        | 1            |        |  |  |

| COMF             | Comple                                                                                                                                                | ement f          |      |      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                             | [label] COMF f,d |      |      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                        | 7                |      |      |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (des$                                                                                                                     | st)              |      |      |  |  |  |  |

| Status Affected: | Z                                                                                                                                                     |                  |      |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                    | 1001             | dfff | ffff |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the result is<br>stored in W. If 'd' is 1 the result is<br>stored back in register 'f'. |                  |      |      |  |  |  |  |

| Words:           | 1                                                                                                                                                     |                  |      |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                     |                  |      |      |  |  |  |  |

| Example          | COMF                                                                                                                                                  | REG1,0           | )    |      |  |  |  |  |

|                  | Before In                                                                                                                                             | struction        |      |      |  |  |  |  |

|                  | REG1 = 0x13                                                                                                                                           |                  |      |      |  |  |  |  |

|                  | After Instruction                                                                                                                                     |                  |      |      |  |  |  |  |

|                  | REG                                                                                                                                                   | 1 =              | 0x13 |      |  |  |  |  |

|                  | W                                                                                                                                                     | =                | 0xEC |      |  |  |  |  |

| Clear Watchdog Timer                                                                                                              |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [label] CLRWDT                                                                                                                    |  |  |  |  |  |  |

| None                                                                                                                              |  |  |  |  |  |  |

| $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$ |  |  |  |  |  |  |

| TO, PD                                                                                                                            |  |  |  |  |  |  |

| 00 0000 0110 0100                                                                                                                 |  |  |  |  |  |  |

| CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits TO<br>and PD are set.    |  |  |  |  |  |  |

| 1                                                                                                                                 |  |  |  |  |  |  |

| 1                                                                                                                                 |  |  |  |  |  |  |

| CLRWDT                                                                                                                            |  |  |  |  |  |  |

| Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = $1$<br>PD = $1$ |  |  |  |  |  |  |

|                                                                                                                                   |  |  |  |  |  |  |

.....

| DECF             | Decrement f                                                                                                                                 |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                             |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                           |  |  |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                           |  |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                           |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                           |  |  |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                                 |  |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                       |  |  |  |  |  |  |

|                  |                                                                                                                                             |  |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                    |

| Operands:        | None                                                                                                                                                                                                              |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                     |

| Status Affected: | None                                                                                                                                                                                                              |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                 |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                 |

| Cycles:          | 2                                                                                                                                                                                                                 |

| Example          | RETFIE                                                                                                                                                                                                            |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                            |

| RETURN           | Return                  | from Su                 | Ibroutine                                           | •                 |

|------------------|-------------------------|-------------------------|-----------------------------------------------------|-------------------|

| Syntax:          | [ label ]               | RETUR                   | N                                                   |                   |

| Operands:        | None                    |                         |                                                     |                   |

| Operation:       | $TOS\toF$               | ъС                      |                                                     |                   |

| Status Affected: | None                    |                         |                                                     |                   |

| Encoding:        | 00                      | 0000                    | 0000                                                | 1000              |

| Description:     | POPed an<br>is loaded i | d the top<br>nto the pr | tine. The s<br>of the stack<br>ogram counstruction. | k (TOS)<br>inter. |

| Words:           | 1                       |                         |                                                     |                   |

| Cycles:          | 2                       |                         |                                                     |                   |

| Example          | RETURN                  |                         |                                                     |                   |

|                  | After Inte<br>PC        | rrupt<br>= T            | OS                                                  |                   |

| RETLW            | Return with Literal in W                                                                                                                                                            | I                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | S                     |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | 0                     |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        | 0                     |

| Status Affected: | None                                                                                                                                                                                | St                    |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   | E                     |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. | D                     |

| Words:           | 1                                                                                                                                                                                   |                       |

| Cycles:          | 2                                                                                                                                                                                   |                       |

| Example          | CALL TABLE;W contains table<br>;offset value<br>• ;W now has table<br>value<br>•                                                                                                    | W<br>C <u>y</u><br>Ex |

| TABLE            | <pre>ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;</pre>                                                                                                                    |                       |

|                  | Before Instruction                                                                                                                                                                  |                       |

|                  | W = 0x07                                                                                                                                                                            |                       |

|                  | After Instruction                                                                                                                                                                   |                       |

|                  | W = value of k8                                                                                                                                                                     |                       |

| RLF             | Rotate Left f through Carry                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| yntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    |  |  |  |  |  |  |  |

| perands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                                                                    |  |  |  |  |  |  |  |

| peration:       | See description below                                                                                                                                                                                       |  |  |  |  |  |  |  |

| tatus Affected: | С                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| ncoding:        | 00 1101 dfff ffff                                                                                                                                                                                           |  |  |  |  |  |  |  |

| escription:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |  |  |  |  |  |  |  |

| /ords:          | 1                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| ycles:          | 1                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| xample          | RLF REG1,0                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                 | Before Instruction                                                                                                                                                                                          |  |  |  |  |  |  |  |

|                 | <b>REG1</b> = 1110 0110                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                 | C = 0                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                 | After Instruction                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                 | <b>REG1</b> = 1110 0110                                                                                                                                                                                     |  |  |  |  |  |  |  |

|                 | W = 1100 1100                                                                                                                                                                                               |  |  |  |  |  |  |  |

|                 | C = 1                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|                 |                                                                                                                                                                                                             |  |  |  |  |  |  |  |

<sup>© 1996-2013</sup> Microchip Technology Inc.

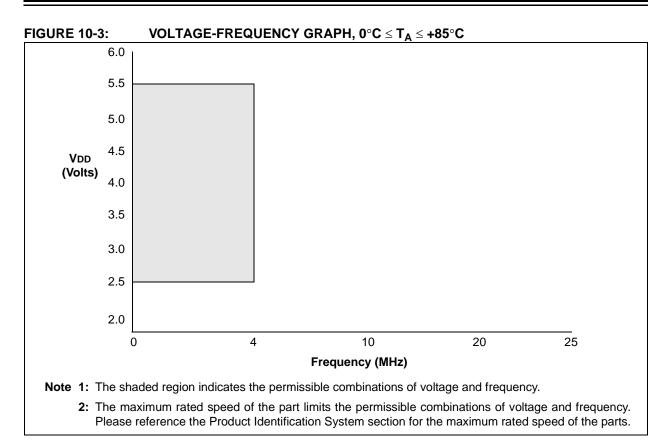

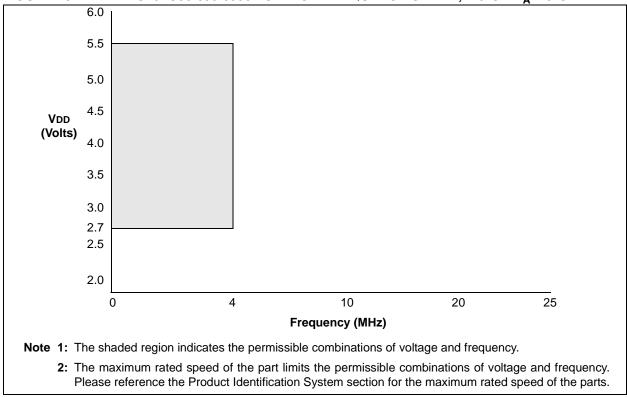

#### 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Characteristics |      |                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |            |        |                                                                                           |

|--------------------|------|-----------------------------------------------|------------------------------------------------------|------|------------|--------|-------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                                | Min                                                  | Тур† | Max        | Units  | Conditions                                                                                |

|                    | Vdd  | Supply Voltage                                |                                                      |      |            |        |                                                                                           |

| D001               |      | 16LC55X                                       | 3.0<br>2.5                                           | _    | 5.5<br>5.5 | V      | XT and RC osc configuration<br>LP osc configuration                                       |

| D001<br>D001A      |      | 16C55X                                        | 3.0<br>4.5                                           |      | 5.5<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                                   |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —                                                    | 1.5* | —          | V      | Device in SLEEP mode                                                                      |

| D003               | VPOR | VDD Start Voltage to<br>ensure Power-on Reset | —                                                    | Vss  | —          | V      | See Section 6.4, Power-on Reset for details                                               |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*                                                | _    | —          | V/ms   | See Section 6.4, Power-on Reset for details                                               |

|                    | Idd  | Supply Current <sup>(2)</sup>                 |                                                      |      |            |        |                                                                                           |

| D010               |      | 16LC55X                                       | _                                                    | 1.4  | 2.5        | mA     | XT and RC osc configuration<br>Fosc = 2.0 MHz, VDD = 3.0V, WDT<br>disabled <sup>(4)</sup> |

| D010A              |      |                                               | _                                                    | 26   | 53         | μA     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT<br>disabled                        |

| D010               |      | 16C55X                                        | _                                                    | 1.8  | 3.3        | mA     | XT and RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V,<br>WDT disabled <sup>(4)</sup>   |

| D010A              |      |                                               | _                                                    | 35   | 70         | μΑ     | LP osc configuration,<br>PIC16C55X-04 only<br>Fosc = 32 kHz, VDD = 4.0V,<br>WDT disabled  |

| D013               |      |                                               | —                                                    | 9.0  | 20         | mA     | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V,<br>WDT disabled                        |

These parameters are characterized but not tested.

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

<u>OSC1</u> = external square wave, from rail to rail; all I/O pins configured as input, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as input and tied to VDD or Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Cha       | racteristi     | cs                                |     |      |           |          |                                               |

|--------------|----------------|-----------------------------------|-----|------|-----------|----------|-----------------------------------------------|

| Param<br>No. | Sym            | Characteristic                    | Min | Тур† | Max       | Units    | Conditions                                    |

| D020         | IPD            | Power-Down Current <sup>(3)</sup> |     |      |           |          |                                               |

|              |                | 16LC55X                           | _   | 0.7  | 2         | μA       | VDD = 3.0V, WDT disabled                      |

|              |                | 16C55X                            | —   | 1.0  | 2.5<br>15 | μΑ<br>μΑ | VDD = 4.0V, WDT disabled<br>(+85°C to +125°C) |

|              | $\Delta I$ WDT | WDT Current <sup>(5)</sup>        |     |      |           |          |                                               |

|              |                | 16LC55X                           | _   | 6.0  | 15        | μΑ       | VDD = 3.0V                                    |

|              |                | 16C55X                            | _   | 6.0  | 20        | μΑ       | VDD = 4.0V<br>(+85°C to +125°C)               |

\* These parameters are characterized but not tested.

**†** Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins configured as input, pulled to VDD,

- $\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as input and tied to VDD or VSS.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

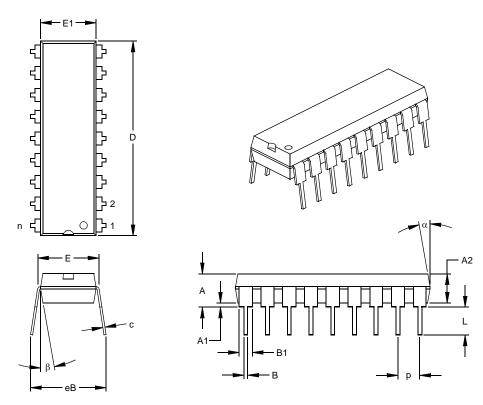

### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                            | Units    |      | INCHES* |      |       | MILLIMETERS |       |  |

|----------------------------|----------|------|---------|------|-------|-------------|-------|--|

| Dimensio                   | n Limits | MIN  | NOM     | MAX  | MIN   | NOM         | MAX   |  |

| Number of Pins             | n        |      | 18      |      |       | 18          |       |  |

| Pitch                      | р        |      | .100    |      |       | 2.54        |       |  |

| Top to Seating Plane       | А        | .140 | .155    | .170 | 3.56  | 3.94        | 4.32  |  |

| Molded Package Thickness   | A2       | .115 | .130    | .145 | 2.92  | 3.30        | 3.68  |  |

| Base to Seating Plane      | A1       | .015 |         |      | 0.38  |             |       |  |

| Shoulder to Shoulder Width | Е        | .300 | .313    | .325 | 7.62  | 7.94        | 8.26  |  |

| Molded Package Width       | E1       | .240 | .250    | .260 | 6.10  | 6.35        | 6.60  |  |

| Overall Length             | D        | .890 | .898    | .905 | 22.61 | 22.80       | 22.99 |  |

| Tip to Seating Plane       | L        | .125 | .130    | .135 | 3.18  | 3.30        | 3.43  |  |

| Lead Thickness             | С        | .008 | .012    | .015 | 0.20  | 0.29        | 0.38  |  |

| Upper Lead Width           | B1       | .045 | .058    | .070 | 1.14  | 1.46        | 1.78  |  |

| Lower Lead Width           | В        | .014 | .018    | .022 | 0.36  | 0.46        | 0.56  |  |

| Overall Row Spacing §      | eB       | .310 | .370    | .430 | 7.87  | 9.40        | 10.92 |  |

| Mold Draft Angle Top       | α        | 5    | 10      | 15   | 5     | 10          | 15    |  |

| Mold Draft Angle Bottom    | β        | 5    | 10      | 15   | 5     | 10          | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

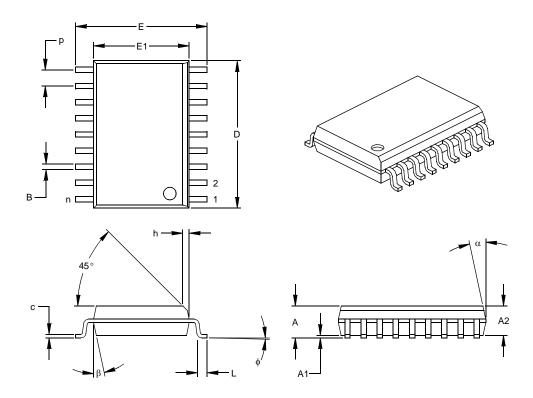

#### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)