Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                |                                                                           |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c554-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 2.0 PIC16C55X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C55X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PROMATE<sup>®</sup> programmers both support programming of the PIC16C55X.

#### 2.2 One-Time Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

### 2.4 Serialized Quick-Turnaround Production (SQTP<sup>™</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

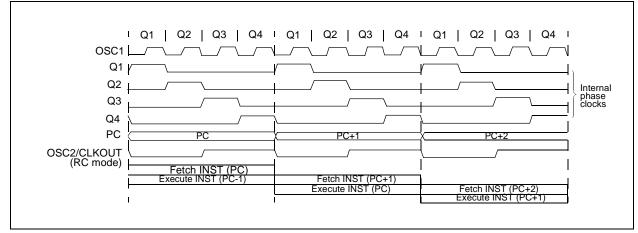

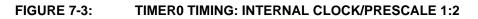

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle

while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

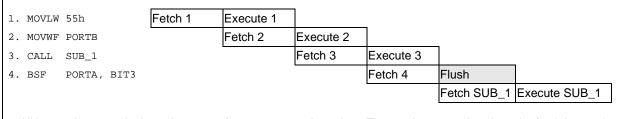

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

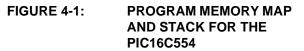

## 4.0 MEMORY ORGANIZATION

#### 4.1 Program Memory Organization

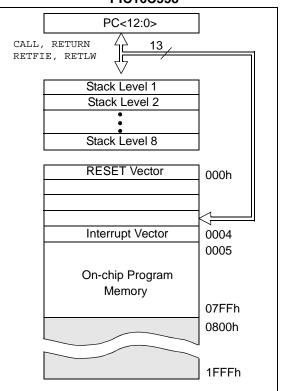

The PIC16C55X has a 13-bit program counter capable of addressing an 8 K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C554 and 2K x 14 (0000h - 07FFh) for the PIC16C557 and PIC16C558 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 spaces in the PIC16C554, or 2K x 14 space of the PIC16C558 and PIC16C557. The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2).

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C557 AND PIC16C558

#### 4.2 Data Memory Organization

The data memory (Figure 4-3 through Figure 4-5) is partitioned into two banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bank 0 is selected when the RP0 bit (STATUS <5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-6Fh (Bank 0) on the PIC16C554 and 20-7Fh (Bank 0) and A0-BFh (Bank 1) on the PIC16C558 and PIC16C557 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $80 \times 8$  in the PIC16C554 and 128 x 8 in the PIC16C557 and PIC16C558. Each can be accessed either directly or indirectly through the File Select Register, FSR (Section 4.4).

#### TABLE 5-1: PORTA FUNCTIONS

| Name      | Bit # | Buffer<br>Type | Function                                                                             |

|-----------|-------|----------------|--------------------------------------------------------------------------------------|

| RA0       | Bit 0 | ST             | Bi-directional I/O port.                                                             |

| RA1       | Bit 1 | ST             | Bi-directional I/O port.                                                             |

| RA2       | Bit 2 | ST             | Bi-directional I/O port.                                                             |

| RA3       | Bit 3 | ST             | Bi-directional I/O port.                                                             |

| RA4/T0CKI | Bit 4 | ST             | Bi-directional I/O port or external clock input for TMR0. Output is open drain type. |

Legend: ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | —     | _     |       | RA4    | RA3    | RA2    | RA1    | RA0    | x xxxx          | u uuuu                          |

| 85h     | TRISA | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged

**Note 1:** Shaded bits are not used by PORTA.

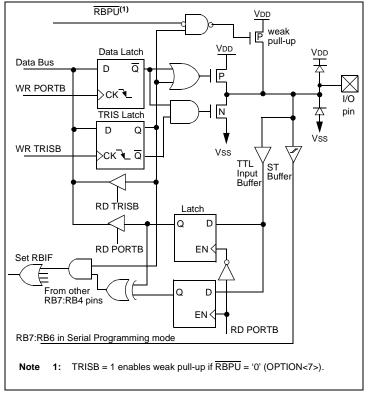

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (this will end the mismatch condition)

- Clear flag bit RBIF

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allows easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552 in the Microchip *Embedded Control Handbook*.)

**Note 1:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### FIGURE 5-3: BLOCK DIAGRAM OF RB7:RB4 PINS

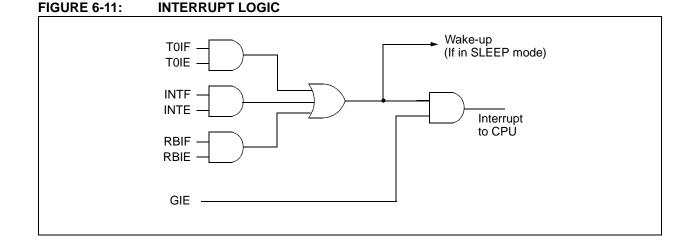

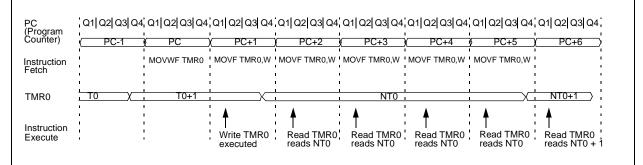

#### 6.5 Interrupts

The PIC16C55X has 3 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "Return from Interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 6-12). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

© 1996-2013 Microchip Technology Inc.

#### 6.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |

|-------|------------------------------|------|-----|-----------|------|--|

|       | protecting windowed devices. |      |     |           |      |  |

#### 6.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

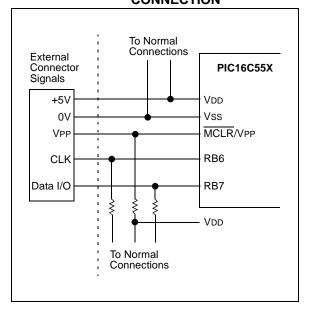

#### 6.11 In-Circuit Serial Programming™

The PIC16C55X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 6-15.

#### FIGURE 6-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## **PIC16C55X**

T0IF interrupt flag is sampled here (every Q1). Note 1:

Interrupt latency = 4 Tcr, where Tcr = instruction cycle time. CLKOUT is available only in RC Oscillator mode. 2:

3:

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT. Lines 5-7 are required only if the desired postscaler rate is 1:1 (PS<2:0> = 000) or 1:2 (PS<2:0> = 001).

| EXAMPLE 7-1: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (TIMER0→WDT)       |

|       | · · · · ·            |                          |

|-------|----------------------|--------------------------|

| BCF   | STATUS, RPO          | ;Skip if already in      |

|       |                      | ;Bank 0 CLRWDT Clear WDT |

| CLRF  | TMR0                 | ;Clear TMR0 & Prescaler  |

| BSF   | STATUS, RPO          | ;Bank 1                  |

| MOVLW | '00101111 <i>'</i> b | ;These 3 lines (5, 6, 7) |

| MOVWF | OPTION               | ;Are required only if    |

|       |                      | ;Desired PS<2:0> are     |

|       |                      | ;CLRWDT 000 or 001       |

| MOVLW | '00101xxx'b          | ;Set Postscaler to       |

| MOVWF | OPTION               | ;Desired WDT rate        |

| BCF   | STATUS, RPO          | ;Return to Bank 0        |

|       |                      |                          |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (           | · / · ····=···/     |

|--------|-------------|---------------------|

| CLRWDT |             | ;Clear WDT and      |

|        |             | ;prescaler          |

| BSF    | STATUS, RPO |                     |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| MOVWF  | OPTION      |                     |

| BCF    | STATUS, RPO |                     |

|        |             |                     |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6           | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-----------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 m | odule's registe | r     |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | Reserved        | TOIE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

| 81h     | OPTION | RBPU     | INTEDG          | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        | _               |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0',

**Note 1:** Shaded bits are not used by TMR0 module.

NOTES:

# PIC16C55X

| CLRW             | Clear W                                                               | V        |              |        |  |  |

|------------------|-----------------------------------------------------------------------|----------|--------------|--------|--|--|

| Syntax:          | [label] CLRW                                                          |          |              |        |  |  |

| Operands:        | None                                                                  |          |              |        |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |          |              |        |  |  |

| Status Affected: | Z                                                                     |          |              |        |  |  |

| Encoding:        | 00                                                                    | 0001     | 0000         | 0011   |  |  |

| Description:     | W register set.                                                       | is clear | ed. Zero bit | (Z) is |  |  |

| Words:           | 1                                                                     |          |              |        |  |  |

| Cycles:          | 1                                                                     |          |              |        |  |  |

| Example          | CLRW                                                                  |          |              |        |  |  |

|                  | Before In                                                             | structio | n            |        |  |  |

|                  | W                                                                     | =        | 0x5A         |        |  |  |

|                  | After Inst                                                            | ruction  |              |        |  |  |

|                  | W                                                                     | =        | 0x00         |        |  |  |

|                  | Z                                                                     | =        | 1            |        |  |  |

| COMF             | Complement f                                                                                                                                          |           |      |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                             |           |      |      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                        | 7         |      |      |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (des$                                                                                                                     | st)       |      |      |  |  |  |

| Status Affected: | Z                                                                                                                                                     |           |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                    | 1001      | dfff | ffff |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the result is<br>stored in W. If 'd' is 1 the result is<br>stored back in register 'f'. |           |      |      |  |  |  |

| Words:           | 1                                                                                                                                                     |           |      |      |  |  |  |

| Cycles:          | 1                                                                                                                                                     |           |      |      |  |  |  |

| Example          | COMF                                                                                                                                                  | REG1,0    | )    |      |  |  |  |

|                  | Before In                                                                                                                                             | struction |      |      |  |  |  |

|                  | REG                                                                                                                                                   | 1 =       | 0x13 |      |  |  |  |

|                  | After Instruction                                                                                                                                     |           |      |      |  |  |  |

|                  | REG                                                                                                                                                   | 1 =       | 0x13 |      |  |  |  |

|                  | W                                                                                                                                                     | =         | 0xEC |      |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                          |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                |  |  |  |  |  |

| Operands:        | None                                                                                                                                                          |  |  |  |  |  |

| Operation:       | $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$                             |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                        |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                             |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                             |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                             |  |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                        |  |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction                                                                                                    |  |  |  |  |  |

|                  | WDT counter = $0x00$                                                                                                                                          |  |  |  |  |  |

|                  | $\underline{WDT}$ prescaler = 0                                                                                                                               |  |  |  |  |  |

|                  | $\overline{TO} = 1$                                                                                                                                           |  |  |  |  |  |

|                  | PD = 1                                                                                                                                                        |  |  |  |  |  |

....

| DECF             | Decrement f                                                                                                                                 |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                           |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                           |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                           |  |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                                 |  |  |  |  |  |

|                  | Before Instruction                                                                                                                          |  |  |  |  |  |

|                  | CNT = 0x01                                                                                                                                  |  |  |  |  |  |

|                  | Z = 0                                                                                                                                       |  |  |  |  |  |

|                  | After Instruction                                                                                                                           |  |  |  |  |  |

|                  | CNT = 0x00                                                                                                                                  |  |  |  |  |  |

|                  | Z = 1                                                                                                                                       |  |  |  |  |  |

|                  |                                                                                                                                             |  |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                       |      |      |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                          |      |      |      |  |

| Operands:        | $0 \le k \le 255$                                                                                                 |      |      |      |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |      |      |      |  |

| Status Affected: | Z                                                                                                                 |      |      |      |  |

| Encoding:        | 11                                                                                                                | 1010 | kkkk | kkkk |  |

| Description:     | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. |      |      |      |  |

| Words:           | 1                                                                                                                 |      |      |      |  |

| Cycles:          | 1                                                                                                                 |      |      |      |  |

| Example:         | XORLW                                                                                                             | 0xAF |      |      |  |

|                  | Before Instruction                                                                                                |      |      |      |  |

|                  | W                                                                                                                 | =    | 0xB5 |      |  |

|                  | After Instruction                                                                                                 |      |      |      |  |

|                  | W                                                                                                                 | =    | 0x1A |      |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                                 |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                       |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                     |  |  |  |  |

| Encoding:        | 00 0110 dfff ffff                                                                                                                                                                     |  |  |  |  |

| Description:     | Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                     |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                     |  |  |  |  |

| Example          | XORWF REG 1                                                                                                                                                                           |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                    |  |  |  |  |

|                  | REG = 0xAF<br>W = 0xB5                                                                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                                                                                     |  |  |  |  |

|                  | REG = 0x1A                                                                                                                                                                            |  |  |  |  |

|                  | W = 0xB5                                                                                                                                                                              |  |  |  |  |

$\odot$  1996-2013 Microchip Technology Inc.

## 10.0 ELECTRICAL SPECIFICATIONS

| Absolute Maximum Ratings †                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature under bias40° to +125°C                                                                                                      |

| Storage Temperature                                                                                                                              |

| Voltage on any pin with respect to Vss (except VDD and MCLR)0.6V to VDD +0.6V                                                                    |

| Voltage on VDD with respect to Vss 0 to +7.5V                                                                                                    |

| Voltage on MCLR with respect to Vss0 to +14V                                                                                                     |

| Total power Dissipation (Note 1)1.0W                                                                                                             |

| Maximum Current out of Vss pin                                                                                                                   |

| Maximum Current into VDD pin250 mA                                                                                                               |

| Input Clamp Current, Iικ (VI < 0 or VI > VDD)±20 mA                                                                                              |

| Output Clamp Current, IOK (V0 < 0 or V0 > VDD)±20 mA                                                                                             |

| Maximum Output Current sunk by any I/O pin25 mA                                                                                                  |

| Maximum Output Current sourced by any I/O pin25 mA                                                                                               |

| Maximum Current sunk by PORTA, PORTB and PORTC                                                                                                   |

| Maximum Current sourced by PORTA, PORTB and PORTC                                                                                                |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD-VOH) x IOH} + $\Sigma$ (VOI x IOL) |

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 10.2 DC Characteristics: PIC16C55X (Commercial, Industrial, Extended) PIC16LC55X(Commercial, Industrial, Extended)

| DC Cha        | racteris | tics                                        | Standard Ope<br>Operating tem | -      | re -40°C ≤ T.<br>0°C ≤ T | A ≤ +8<br>īA ≤ +7 | <b>s otherwise stated)</b><br>5°C for industrial and<br>70°C for commercial and<br>25°C for automotive |

|---------------|----------|---------------------------------------------|-------------------------------|--------|--------------------------|-------------------|--------------------------------------------------------------------------------------------------------|

|               |          | 1                                           | Operating volt                | age Vo | D range as de            | scribed           | d in DC spec Table 10-1                                                                                |

| Param.<br>No. | Sym      | Characteristic                              | Min                           | Тур†   | Max                      | Unit              | Conditions                                                                                             |

|               | VIL      | Input Low Voltage                           |                               |        |                          |                   |                                                                                                        |

|               |          | I/O ports                                   |                               |        |                          |                   |                                                                                                        |

| D030          |          | with TTL buffer                             | Vss                           | _      | 0.8V<br>0.15 Vdd         | V                 | VDD = 4.5V to 5.5V<br>otherwise                                                                        |

| D031          |          | with Schmitt Trigger input                  | Vss                           |        | 0.2 Vdd                  | V                 |                                                                                                        |

| D032          |          | MCLR, RA4/T0CKI,OSC1 (in RC mode)           | Vss                           | _      | 0.2 VDD                  | V                 | (Note1)                                                                                                |

| D033          |          | OSC1 (in XT* and HS)                        | Vss                           | —      | 0.3 VDD                  | V                 |                                                                                                        |

|               |          | OSC1 (in LP*)                               | Vss                           | —      | 0.6 Vdd-1.0              | V                 |                                                                                                        |

|               | Vін      | Input High Voltage                          |                               |        |                          |                   |                                                                                                        |

|               |          | I/O ports                                   |                               | —      |                          |                   |                                                                                                        |

| D040          |          | with TTL buffer                             | 2.0V<br>0.8 + 0.25 VDD        | _      | Vdd<br>Vdd               | V<br>V            | VDD = 4.5V to 5.5V<br>otherwise                                                                        |

| D041          |          | with Schmitt Trigger input                  | 0.8V                          |        | Vdd                      |                   |                                                                                                        |

| D042          |          | MCLR RA4/T0CKI                              | 0.8 Vdd                       | —      | Vdd                      | V                 |                                                                                                        |

| D043<br>D043A |          | OSC1 (XT*, HS and LP*)<br>OSC1 (in RC mode) | 0.7 Vdd<br>0.9 Vdd            | —      | Vdd                      | V                 | (Note1)                                                                                                |

| D070          | Ipurb    | PORTB weak pull-up current                  | 50                            | 200    | 400                      | μΑ                | VDD = 5.0V, VPIN = VSS                                                                                 |

|               | ١L       | Input Leakage Current <sup>(2)(3)</sup>     |                               |        |                          |                   |                                                                                                        |

|               |          | I/O ports (Except PORTA)                    |                               |        | ±1.0                     | μΑ                | $Vss \le VPIN \le VDD, \text{ pin at hi-impedance}$                                                    |

| D060          |          | PORTA                                       | —                             | —      | ±0.5                     | μA                | $Vss \le VPIN \le VDD, pin at hi-impedance$                                                            |

| D061          |          | RA4/T0CKI                                   | —                             | —      | ±1.0                     | μΑ                | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                               |

| D063          |          | OSC1, MCLR                                  | —                             | —      | ±5.0                     | μΑ                | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration                                            |

|               | Vol      | Output Low Voltage                          |                               |        |                          |                   |                                                                                                        |

| D080          |          | I/O ports                                   | —                             | —      | 0.6                      | V                 | IOL=8.5 mA, VDD=4.5V, -40° to<br>+85°C                                                                 |

|               |          |                                             | —                             | —      | 0.6                      | V                 | IOL=7.0 mA, VDD=4.5V, +125°C                                                                           |

| D083          |          | OSC2/CLKOUT                                 | _                             | —      | 0.6                      | V                 | IOL=1.6 mA, VDD=4.5V, -40° to<br>+85°C                                                                 |

|               |          | (RC only)                                   | —                             | —      | 0.6                      | V                 | IOL=1.2 mA, VDD=4.5V, +125°C                                                                           |

|               | Vон      | Output High Voltage <sup>(3)</sup>          |                               |        |                          |                   |                                                                                                        |

| D090          |          | I/O ports (Except RA4)                      | VDD-0.7                       | —      | _                        | V                 | IOH=-3.0 mA, VDD=4.5V, -40° to<br>+85°C                                                                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C55X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

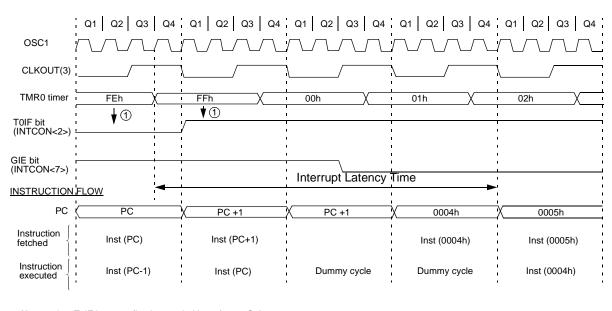

#### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units     | INCHES* |      | MILLIMETERS |       |       |       |

|--------------------------|-----------|---------|------|-------------|-------|-------|-------|

| Dimensi                  | on Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins           | n         |         | 18   |             |       | 18    |       |

| Pitch                    | р         |         | .050 |             |       | 1.27  |       |

| Overall Height           | Α         | .093    | .099 | .104        | 2.36  | 2.50  | 2.64  |

| Molded Package Thickness | A2        | .088    | .091 | .094        | 2.24  | 2.31  | 2.39  |

| Standoff §               | A1        | .004    | .008 | .012        | 0.10  | 0.20  | 0.30  |

| Overall Width            | E         | .394    | .407 | .420        | 10.01 | 10.34 | 10.67 |

| Molded Package Width     | E1        | .291    | .295 | .299        | 7.39  | 7.49  | 7.59  |

| Overall Length           | D         | .446    | .454 | .462        | 11.33 | 11.53 | 11.73 |

| Chamfer Distance         | h         | .010    | .020 | .029        | 0.25  | 0.50  | 0.74  |

| Foot Length              | L         | .016    | .033 | .050        | 0.41  | 0.84  | 1.27  |

| Foot Angle               | ¢         | 0       | 4    | 8           | 0     | 4     | 8     |

| Lead Thickness           | С         | .009    | .011 | .012        | 0.23  | 0.27  | 0.30  |

| Lead Width               | В         | .014    | .017 | .020        | 0.36  | 0.42  | 0.51  |

| Mold Draft Angle Top     | α         | 0       | 12   | 15          | 0     | 12    | 15    |

| Mold Draft Angle Bottom  | β         | 0       | 12   | 15          | 0     | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

NOTES:

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                   | x <u>xx</u> xxx                                                                                                               | Examples:                                                                                                                                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device To         | emperature Package Pattern<br>Range                                                                                           | a) PIC17C756–16L Commercial Temp.,<br>PLCC package, 16 MHz,<br>normal VDD limits                                                                         |

| Device            | PIC17C756: Standard VDD range<br>PIC17C756T: (Tape and Reel)<br>PIC17LC756: Extended VDD range                                | <ul> <li>b) PIC17LC756–08/PT Commercial Temp.,<br/>TQFP package, 8MHz,<br/>extended VDD limits</li> <li>c) PIC17C756–33I/PT Industrial Temp.,</li> </ul> |

| Temperature Range | $\begin{array}{rcl} - & = & 0^{\circ}C \text{ to } +70^{\circ}C \\ I & = & -40^{\circ}C \text{ to } +85^{\circ}C \end{array}$ | TQFP package, 33 MHz,<br>normal VDD limits                                                                                                               |

| Package           | CL = Windowed LCC<br>PT = TQFP<br>L = PLCC                                                                                    |                                                                                                                                                          |

| Pattern           | QTP, SQTP, ROM Code (factory specified) or<br>Special Requirements. Blank for OTP and<br>Windowed devices.                    |                                                                                                                                                          |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)

NOTES: