#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c554t-04-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C55X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C55X uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently from 8-bit wide data words. Instruction opcodes are 14-bit wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a singlecycle (200 ns @ 20 MHz) except for program branches. The table below lists the memory (EPROM and RAM).

| Device    | Program<br>Memory<br>(EPROM) | Data<br>Memor<br>(RAM) |  |

|-----------|------------------------------|------------------------|--|

| PIC16C554 | 512                          | 80                     |  |

| PIC16C557 | 2 K                          | 128                    |  |

| PIC16C558 | 2 K                          | 128                    |  |

The PIC16C554 addresses 512 x 14 on-chip program memory. The PIC16C557 and PIC16C558 addresses 2 K x 14 program memory. All program memory is internal.

The PIC16C55X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped into the data memory. The PIC16C55X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C55X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C55X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

# 3.1 Clocking Scheme/Instruction Cycle

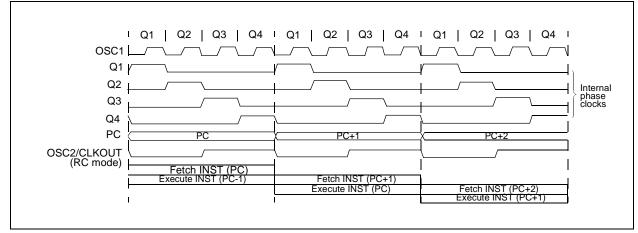

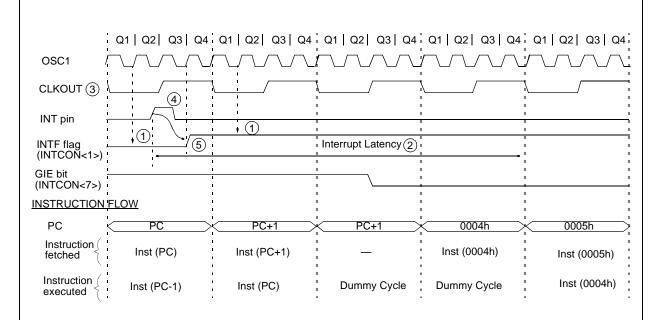

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle

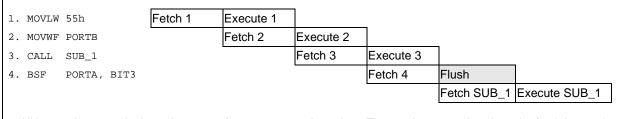

while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

| Address                                       | Name                                                    | Bit 7                                          | Bit 6                                                                                          | Bit 5            | Bit 4               | Bit 3            | Bit 2        | Bit 1                        | Bit 0            | Value on<br>POR Reset                            | Detail on<br>Page:       |

|-----------------------------------------------|---------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|--------------|------------------------------|------------------|--------------------------------------------------|--------------------------|

| Bank 0                                        |                                                         |                                                |                                                                                                |                  |                     |                  |              |                              |                  |                                                  |                          |

| 00h                                           | INDF                                                    |                                                | Addressing this location uses contents of FSR to address data memory (not a physical register) |                  |                     |                  |              |                              |                  | XXXX XXXX                                        | 21                       |

| 01h                                           | TMR0                                                    | Timer0 N                                       | /lodule's Re                                                                                   | egister          |                     |                  |              |                              |                  | xxxx xxxx                                        | 47                       |

| 02h                                           | PCL                                                     | Program                                        | Counter's                                                                                      | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 03h                                           | STATUS                                                  | IRP <sup>(2)</sup>                             | RP1 <sup>(2)</sup>                                                                             | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 04h                                           | FSR                                                     | Indirect of                                    | data memo                                                                                      | ry address       | s pointer           |                  |              |                              |                  | xxxx xxxx                                        | 21                       |

| 05h                                           | PORTA                                                   | -                                              | —                                                                                              | —                | RA4                 | RA3              | RA2          | RA1                          | RA0              | x xxxx                                           | 23                       |

| 06h                                           | PORTB                                                   | RB7                                            | RB6                                                                                            | RB5              | RB4                 | RB3              | RB2          | RB1                          | RB0              | xxxx xxxx                                        | 25                       |

| 07h                                           | PORTC <sup>(4)</sup>                                    | RC7                                            | RC6                                                                                            | RC5              | RC4                 | RC3              | RC2          | RC1                          | RC0              | xxxx xxxx                                        | 27                       |

| 08h                                           | _                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                |                          |

| 09h                                           | _                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Ah                                           | PCLATH                                                  | _                                              | —                                                                                              |                  | Write but           | fer for upp      | per 5 bits o | of progran                   | n counter        | 0 0000                                           | 21                       |

| 0Bh                                           | INTCON                                                  | GIE                                            | (3)                                                                                            | T0IE             | INTE                | RBIE             | T0IF         | INTF                         | RBIF             | 0000 000x                                        | 19                       |

| 0Ch                                           | —                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Dh-1Eh                                       | —                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                | —                        |

| 1Fh                                           | —                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                | _                        |

| Bank 1                                        |                                                         |                                                |                                                                                                |                  |                     |                  |              |                              |                  |                                                  |                          |

| 80h                                           | INDF                                                    | Addressi<br>physical                           | ing this loca<br>register)                                                                     | ation uses       | contents            | of FSR to a      | address d    | ata memo                     | ory (not a       | XXXX XXXX                                        | 21                       |

| 81h                                           | OPTION                                                  | RBPU                                           | INTEDG                                                                                         | TOCS             | T0SE                | PSA              | PS2          | PS1                          | PS0              | 1111 1111                                        | 18                       |

| 82h                                           | PCL                                                     | Program                                        | Counter's                                                                                      | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 83h                                           | STATUS                                                  | _                                              | _                                                                                              | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 84h                                           | FSR                                                     |                                                |                                                                                                | Indirect d       | ata memo            | ry address       | s pointer    |                              |                  | xxxx xxxx                                        | 21                       |

| 85h                                           | TRISA                                                   | -                                              | —                                                                                              | —                | TRISA4              | TRISA3           | TRISA2       | TRISA1                       | TRISA0           | 1 1111                                           | 23                       |

| 86h                                           | TDIOD                                                   |                                                |                                                                                                |                  |                     |                  | TDIODO       | TDICD4                       |                  |                                                  | 05                       |

| 0011                                          | TRISB                                                   | TRISB7                                         | TRISB6                                                                                         | TRISB5           | TRISB4              | TRISB3           | TRISB2       | TRISB1                       | TRISB0           | 1111 1111                                        | 25                       |

| 87h                                           | TRISB                                                   | TRISB7<br>TRISC7                               | TRISB6<br>TRISC6                                                                               | TRISB5<br>TRISC5 | TRISB4<br>TRISC4    | TRISB3<br>TRISC3 | TRISB2       | TRISC1                       | TRISB0<br>TRISC0 | 1111 1111<br>1111 1111                           | 25                       |

|                                               |                                                         |                                                | TRISC6                                                                                         |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h                                           |                                                         | TRISC7                                         | TRISC6<br>mented                                                                               |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h<br>88h                                    |                                                         | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                               |                  | TRISC4              |                  | TRISC2       | TRISC1                       | TRISC0           |                                                  | 27<br>—                  |

| 87h<br>88h<br>89h                             | TRISC <sup>(4)</sup><br>—<br>—                          | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                               |                  | TRISC4              | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—                              | 27<br>—<br>—             |

| 87h<br>88h<br>89h<br>8Ah                      | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple                   | TRISC6<br>mented<br>mented<br>(3)                                                              | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh               | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br><br>GIE        | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                    | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch        | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                    | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch<br>8Dh | TRISC <sup>(4)</sup><br>—<br>PCLATH<br>INTCON<br>—<br>— | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>—<br>(3)<br>mented<br>mented                                               | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1<br>of program<br>INTF | TRISC0           | 1111 1111<br>                                    | 27<br>—<br>21<br>19<br>— |

#### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C55X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved, always maintain these bits clear.

3: Bit 6 of INTCON register is reserved for future use. Always maintain this bit as clear.

4: PIC16C557 only.

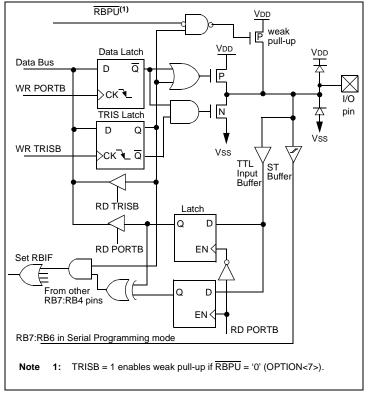

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (this will end the mismatch condition)

- Clear flag bit RBIF

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allows easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552 in the Microchip *Embedded Control Handbook*.)

**Note 1:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### FIGURE 5-3: BLOCK DIAGRAM OF RB7:RB4 PINS

## 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

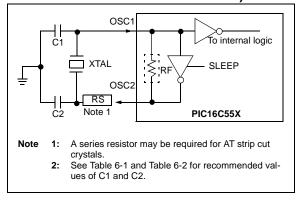

# 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

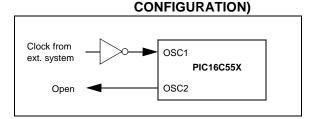

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

#### FIGURE 6-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

FIGURE 6-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

#### TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges  |                                                                                                                                              |                                         |                                         |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| Mode    | Freq                                                                                                                                         | OSC1(C1)                                | OSC2(C2)                                |  |  |

| ХТ      | 455 kHz<br>2.0 MHz<br>4.0 MHz                                                                                                                | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |

| HS      | 8.0 MHz<br>16.0 MHz                                                                                                                          | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |

| Note 1: | Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design |                                         |                                         |  |  |

| of the oscillator but also increases the    |

|---------------------------------------------|

| start-up time. These values are for design  |

| guidance only. Since each resonator has     |

| its own characteristics, the user should    |

| consult with the resonator manufacturer for |

| appropriate values of external compo-       |

| nents.                                      |

| TABLE 6-2: | <b>CAPACITOR SELECTION FOR</b> |

|------------|--------------------------------|

|            | CRYSTAL OSCILLATOR             |

|            | (PRELIMINARY)                  |

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC1(C1)    | OSC2(C2)     |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--|--|

| LP      | 32 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 - 100 pF | 68 - 100 pF  |  |  |

|         | 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 - 30 pF  | 15 - 30 pF   |  |  |

| XT      | 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 - 150 pF | 150 - 200 pF |  |  |

|         | 2 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |  |

|         | 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |  |

| HS      | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |  |

|         | 10 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |  |  |

|         | 20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |  |  |

| Note 1: | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid over-<br>driving crystals with low-drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>with the crystal manufacturer for appropri-<br>ate values of external components. |             |              |  |  |

#### 6.5.1 RB0/INT INTERRUPT

An external interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION<6>) is set, or falling if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before reenabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 6.8 for details on SLEEP and Figure 6-14 for timing of wakeup from SLEEP through RB0/INT interrupt.

#### 6.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 7.0.

#### 6.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may get set.

FIGURE 6-12: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3-4 TCY where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in RC Oscillator mode.

- 4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

| Address | Name         | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other RESETS |

|---------|--------------|-------|----------|-------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 2007h   | Config. bits | —     | Reserved | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |              |                           |

| 81h     | OPTION       | RBPU  | INTEDG   | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111    | 1111 1111                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

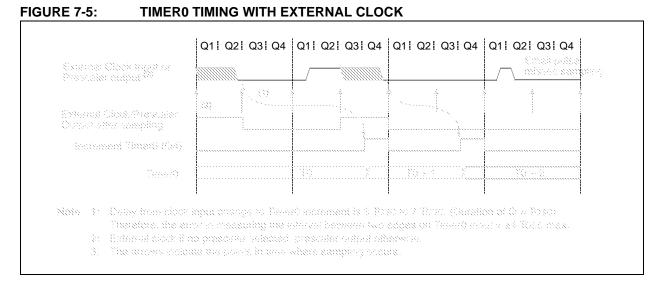

### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

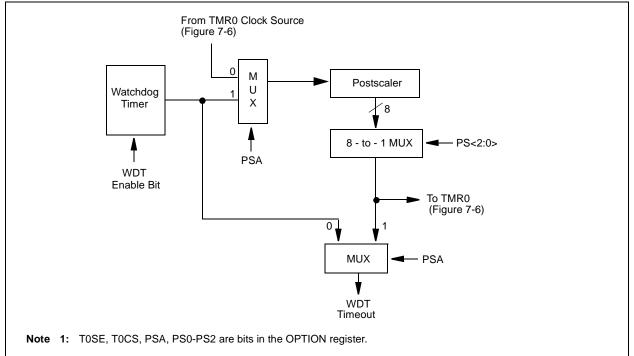

### 7.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

Note: There is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

© 1996-2013 Microchip Technology Inc.

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT. Lines 5-7 are required only if the desired postscaler rate is 1:1 (PS<2:0> = 000) or 1:2 (PS<2:0> = 001).

| EXAMPLE 7-1: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (TIMER0→WDT)       |

| BCF   | STATUS, RPO          | ;Skip if already in      |

|-------|----------------------|--------------------------|

|       |                      | ;Bank 0 CLRWDT Clear WDT |

| CLRF  | TMR0                 | ;Clear TMR0 & Prescaler  |

| BSF   | STATUS, RPO          | ;Bank 1                  |

| MOVLW | '00101111 <i>'</i> b | ;These 3 lines (5, 6, 7) |

| MOVWF | OPTION               | ;Are required only if    |

|       |                      | ;Desired PS<2:0> are     |

|       |                      | ;CLRWDT 000 or 001       |

| MOVLW | '00101xxx'b          | ;Set Postscaler to       |

| MOVWF | OPTION               | ;Desired WDT rate        |

| BCF   | STATUS, RPO          | ;Return to Bank 0        |

|       |                      |                          |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (           | · / · ····=···/     |

|--------|-------------|---------------------|

| CLRWDT |             | ;Clear WDT and      |

|        |             | ;prescaler          |

| BSF    | STATUS, RPO |                     |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| MOVWF  | OPTION      |                     |

| BCF    | STATUS, RPO |                     |

|        |             |                     |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                         | Bit 6    | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|-------------------------------|----------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | TMR0 Timer0 module's register |          |       |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE                           | Reserved | TOIE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

| 81h     | OPTION | RBPU                          | INTEDG   | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _                             | —        |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0',

**Note 1:** Shaded bits are not used by TMR0 module.

NOTES:

# PIC16C55X

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                       | IORWF                             | Inclusive OR W with f                                                                                                                                                   |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                  | Syntax:                           | [ <i>label</i> ] IORWF f,d                                                                                                                                              |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                           | Operands:                         | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                             |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                             | Operation:                        | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                       |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         | Status Affected:                  | Z                                                                                                                                                                       |  |  |

| Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                            | Encoding:                         | 00 0100 dfff ffff                                                                                                                                                       |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. | Description:<br>Words:<br>Cycles: | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>1 |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                            | Example                           | IORWF RESULT, 0                                                                                                                                                         |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                         |                                   | Before Instruction<br>RESULT = 0x13                                                                                                                                     |  |  |

| Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                      |                                   | W = 0x91<br>After Instruction<br>RESULT = 0x13<br>W = 0x93                                                                                                              |  |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if $CNT = 0$ ,<br>PC = address CONTINUE<br>if $CNT \neq 0$ ,<br>PC = address HERE + 1                                                                                                                                                       |                                   | Z = 1                                                                                                                                                                   |  |  |

| IORLW            | Inclusiv                     | ve OR I   | Literal wit                                    | h W      |  |  |

|------------------|------------------------------|-----------|------------------------------------------------|----------|--|--|

| Syntax:          | [ label ]                    | IORLV     | / k                                            |          |  |  |

| Operands:        | $0 \le k \le 255$            |           |                                                |          |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W) |           |                                                |          |  |  |

| Status Affected: | Z                            |           |                                                |          |  |  |

| Encoding:        | 11                           | 1000      | kkkk                                           | kkkk     |  |  |

| Description:     | OR'ed with                   | n the eig | e W register<br>ht bit literal<br>the W regist | 'k'. The |  |  |

| Words:           | 1                            |           |                                                |          |  |  |

| Cycles:          | 1                            |           |                                                |          |  |  |

| Example          | IORLW                        | 0x35      |                                                |          |  |  |

|                  | Before In                    | structio  | n                                              |          |  |  |

|                  | W                            | =         | 0x9A                                           |          |  |  |

|                  | After Inst                   | ruction   |                                                |          |  |  |

|                  | W                            | =         | 0xBF                                           |          |  |  |

|                  | Z                            | =         | 1                                              |          |  |  |

| MOVLW            | Move Literal to W                                                                          |      |      |      |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|------|------|------|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |      |      |      |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                        |      |      |      |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |      |      |      |  |  |  |

| Status Affected: | None                                                                                       |      |      |      |  |  |  |

| Encoding:        | 11                                                                                         | 00xx | kkkk | kkkk |  |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |      |      |      |  |  |  |

| Words:           | 1                                                                                          |      |      |      |  |  |  |

| Cycles:          | 1                                                                                          |      |      |      |  |  |  |

| Example          | MOVLW                                                                                      | 0x5A |      |      |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                              |      |      |      |  |  |  |

| RRF               | Rotate                                                                                                                                                                                                       | Right f                                       | throu            | igh (              | Carry       |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|--------------------|-------------|--|

| Syntax:           | [ label ]                                                                                                                                                                                                    | RRF 1                                         | ,d               |                    |             |  |

| Operands:         | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                  |                                               |                  |                    |             |  |

| Operation:        | See description below                                                                                                                                                                                        |                                               |                  |                    |             |  |

| Status Affected:  | С                                                                                                                                                                                                            |                                               |                  |                    |             |  |

| Encoding:         | 00 1100 dfff ffff                                                                                                                                                                                            |                                               |                  |                    |             |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                                               |                  |                    |             |  |

|                   |                                                                                                                                                                                                              |                                               |                  |                    |             |  |

|                   |                                                                                                                                                                                                              |                                               | Regist           | ter f              | ┠┺          |  |

| Words:            | 1                                                                                                                                                                                                            |                                               | Regist           | ter f              | ]•          |  |

| Words:<br>Cycles: | 1<br>1                                                                                                                                                                                                       | ]-▶[                                          | Regist           | ter f              | <b>]•</b> ] |  |

|                   | •                                                                                                                                                                                                            | ]-•[                                          |                  | ter f              | <b>]</b> •] |  |

| Cycles:           | 1                                                                                                                                                                                                            |                                               | REG              |                    | <u>}</u>    |  |

| Cycles:           | 1<br>RRF                                                                                                                                                                                                     | struction                                     | REG              | \$1,0              | .0          |  |

| Cycles:           | 1<br>RRF<br>Before Ins                                                                                                                                                                                       | struction                                     | REG<br>n<br>1110 | \$1,0              | .0          |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG                                                                                                                                                                                 | struction<br>1 = 1<br>= (                     | REG<br>n<br>1110 | \$1,0              | .0          |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG<br>C                                                                                                                                                                            | struction<br>1 = 1<br>= 0<br>ruction          | REG<br>n<br>1110 | \$1,0              | -           |  |

| Cycles:           | 1<br>RRF<br>Before Ins<br>REG<br>C<br>After Instr                                                                                                                                                            | struction<br>1 = 2<br>= 0<br>ruction<br>1 = 2 | REG<br>N<br>L110 | ;1,0<br>011<br>011 | .0          |  |

#### SLEEP

| Syntax:          | [ <i>label</i><br>]                                                                                                                                                                                                                                       | SLEEP |      |      |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|

| Operands:        | None                                                                                                                                                                                                                                                      |       |      |      |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                |       |      |      |  |

| Status Affected: | $\overline{\text{TO}}, \overline{\text{PD}}$                                                                                                                                                                                                              |       |      |      |  |

| Encoding:        | 00                                                                                                                                                                                                                                                        | 0000  | 0110 | 0011 |  |

| Description:     | The power-down status bit, <u>PD</u> is<br>cleared. Timeout status bit, <u>TO</u> is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 6.8 for more details |       |      |      |  |

| Words:           | 1                                                                                                                                                                                                                                                         |       |      |      |  |

| Cycles:          | 1                                                                                                                                                                                                                                                         |       |      |      |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                     |       |      |      |  |

| SUBLW               | Subtract W from Literal |                                                                                                                                      |             |          |  |  |  |

|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|--|--|--|

| Syntax:             | [label] S               | UBLW                                                                                                                                 | k           |          |  |  |  |

| Operands:           | $0 \le k \le 255$       | $0 \le k \le 255$                                                                                                                    |             |          |  |  |  |

| Operation:          | k - (W) → (             | $k - (W) \to (W)$                                                                                                                    |             |          |  |  |  |

| Status<br>Affected: | C, DC, Z                |                                                                                                                                      |             |          |  |  |  |

| Encoding:           | 11                      | 110x                                                                                                                                 | kkkk        | kkkk     |  |  |  |

| Description:        | plement met             | The W register is subtracted (2's com-<br>plement method) from the eight bit literal<br>'k'. The result is placed in the W register. |             |          |  |  |  |

| Words:              | 1                       |                                                                                                                                      |             |          |  |  |  |

| Cycles:             | 1                       |                                                                                                                                      |             |          |  |  |  |

| Example 1:          | SUBLW                   | 0x02                                                                                                                                 |             |          |  |  |  |

|                     | Before Inst             | ruction                                                                                                                              |             |          |  |  |  |

|                     | W                       | = 1                                                                                                                                  |             |          |  |  |  |

|                     | С                       | = ?                                                                                                                                  | <b>)</b>    |          |  |  |  |

|                     | After Instru            | ction                                                                                                                                |             |          |  |  |  |

|                     | W                       | = 1                                                                                                                                  |             |          |  |  |  |

|                     | С                       | = 1                                                                                                                                  | ; result is | positive |  |  |  |

| Example 2:          | Before Inst             | ruction                                                                                                                              |             |          |  |  |  |

|                     | W                       | = 2                                                                                                                                  | 2           |          |  |  |  |

|                     | С                       | = ?                                                                                                                                  | )           |          |  |  |  |

|                     | After Instru            | ction                                                                                                                                |             |          |  |  |  |

|                     | W                       | = 0                                                                                                                                  | )           |          |  |  |  |

|                     | С                       | = 1                                                                                                                                  | ; result is | s zero   |  |  |  |

| Example 3:          | Before Inst             | ruction                                                                                                                              |             |          |  |  |  |

|                     | W                       | = 3                                                                                                                                  | 3           |          |  |  |  |

|                     | С                       | = ?                                                                                                                                  | )           |          |  |  |  |

|                     | After Instru            | ction                                                                                                                                |             |          |  |  |  |

|                     | W                       |                                                                                                                                      | )xFF        |          |  |  |  |

|                     | C                       | = 0                                                                                                                                  | ); result i | s nega-  |  |  |  |

tive

$\odot$  1996-2013 Microchip Technology Inc.

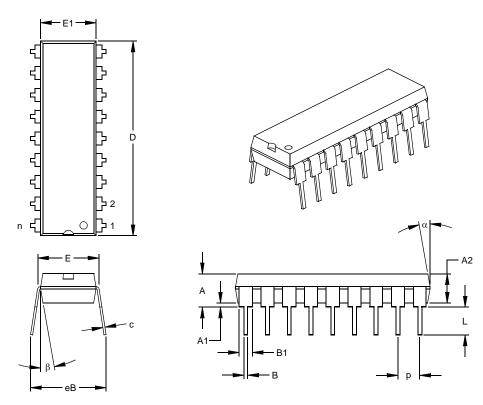

## 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                            | Units    | INCHES* |      |      | MILLIMETERS |       |       |

|----------------------------|----------|---------|------|------|-------------|-------|-------|

| Dimensio                   | n Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n        |         | 18   |      |             | 18    |       |

| Pitch                      | р        |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | А        | .140    | .155 | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2       | .115    | .130 | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1       | .015    |      |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е        | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1       | .240    | .250 | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D        | .890    | .898 | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L        | .125    | .130 | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С        | .008    | .012 | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .045    | .058 | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В        | .014    | .018 | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eB       | .310    | .370 | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α        | 5       | 10   | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5       | 10   | 15   | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

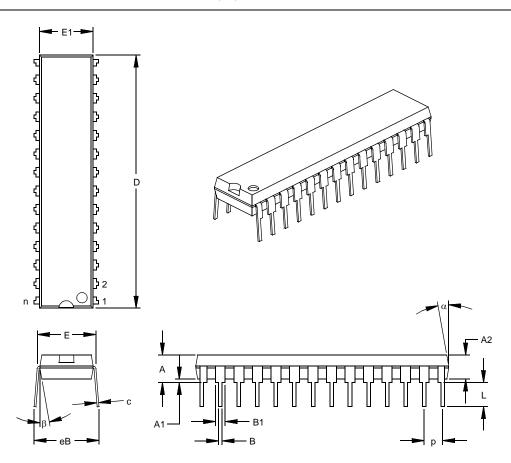

# 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| ision L | imits<br>n<br>p | MIN                                                                                                              | NOM                                                    | MAX                                                     | MIN                                                    | NOM                                                    | MAX                                                     |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

|         |                 |                                                                                                                  |                                                        |                                                         |                                                        |                                                        | 100 01                                                  |

|         | n               |                                                                                                                  | 28                                                     |                                                         |                                                        | 28                                                     |                                                         |

|         | Р               |                                                                                                                  | .100                                                   |                                                         |                                                        | 2.54                                                   |                                                         |

|         | Α               | .140                                                                                                             | .150                                                   | .160                                                    | 3.56                                                   | 3.81                                                   | 4.06                                                    |

|         | A2              | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |