#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558-04e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

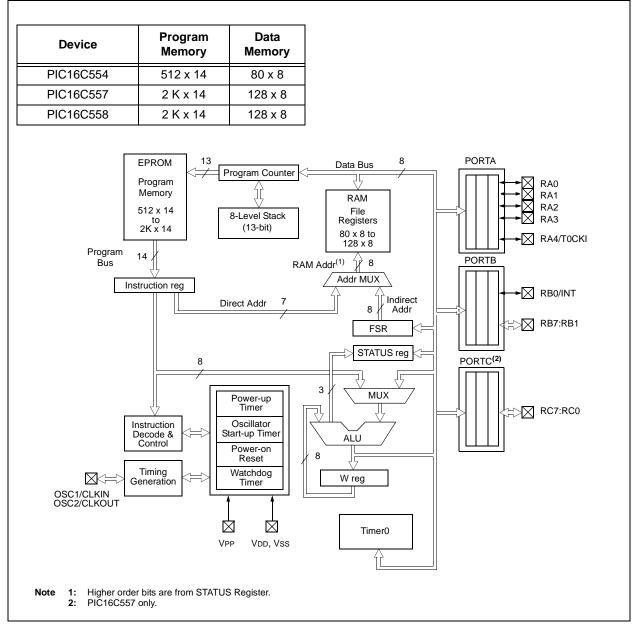

#### TABLE 1-1: PIC16C55X FAMILY OF DEVICES

|             |                                      | PIC16C554                        | PIC16C557                        | PIC16C558                 |  |

|-------------|--------------------------------------|----------------------------------|----------------------------------|---------------------------|--|

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 20                        |  |

| Memory      | EPROM Program Memory<br>(x14 words)  | 512                              | 2K                               | 2K                        |  |

|             | Data Memory (bytes)                  | 80                               | 128                              | 128                       |  |

| Peripherals | Timer Module(s)                      | TMR0                             | TMR0                             | TMR0                      |  |

|             | Interrupt Sources                    | 3                                | 3                                | 3                         |  |

|             | I/O Pins                             | 13                               | 22                               | 13                        |  |

| Features    | Voltage Range (Volts)                | 2.5-5.5                          | 2.5-5.5                          | 2.5-5.5                   |  |

| catares     | Brown-out Reset                      | —                                | —                                | —                         |  |

|             | Packages                             | 18-pin DIP, SOIC;<br>20-pin SSOP | 28-pin DIP, SOIC;<br>28-pin SSOP | 18-pin DIP, SOIC,<br>SSOP |  |

I/O current capability. All PIC16C55X Family devices use serial programming with clock pin RB6 and data pin RB7.

# PIC16C55X

## FIGURE 3-1: BLOCK DIAGRAM

#### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

#### TABLE 5-1: PORTA FUNCTIONS

| Name      | Bit # | Buffer<br>Type | Function                                                                             |

|-----------|-------|----------------|--------------------------------------------------------------------------------------|

| RA0       | Bit 0 | ST             | Bi-directional I/O port.                                                             |

| RA1       | Bit 1 | ST             | Bi-directional I/O port.                                                             |

| RA2       | Bit 2 | ST             | Bi-directional I/O port.                                                             |

| RA3       | Bit 3 | ST             | Bi-directional I/O port.                                                             |

| RA4/T0CKI | Bit 4 | ST             | Bi-directional I/O port or external clock input for TMR0. Output is open drain type. |

Legend: ST = Schmitt Trigger input

#### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | —     | _     |       | RA4    | RA3    | RA2    | RA1    | RA0    | x xxxx          | u uuuu                          |

| 85h     | TRISA | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged

**Note 1:** Shaded bits are not used by PORTA.

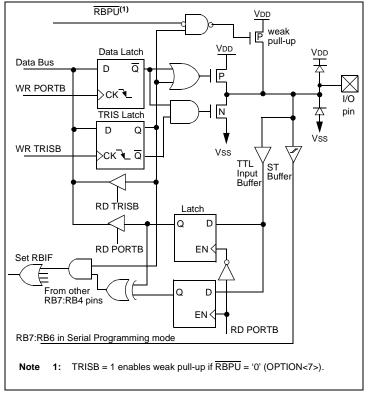

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (this will end the mismatch condition)

- Clear flag bit RBIF

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allows easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552 in the Microchip *Embedded Control Handbook*.)

**Note 1:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### FIGURE 5-3: BLOCK DIAGRAM OF RB7:RB4 PINS

## 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-1 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}$ ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a low or high should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip. NOTES:

#### **REGISTER 6-1: CONFIGURATION WORD**

|          | CP1                | CP0                                                                                                                                                    | CP1        | CP0         | CP1       | CP0      | —        | Reserved     | CP1       | CP0      | PWRTE        | WDTE        | F0SC1 | F0SC0 |

|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-----------|----------|----------|--------------|-----------|----------|--------------|-------------|-------|-------|

|          | bit 13             |                                                                                                                                                        |            |             |           |          |          |              |           |          |              |             |       | bit 0 |

|          |                    |                                                                                                                                                        |            | (4)         |           |          |          |              |           |          |              |             |       |       |

| bit 13-8 |                    |                                                                                                                                                        | protection |             | ion off   |          |          |              |           |          |              |             |       |       |

| bit 5-4  | 10 = 04<br>01 = 02 | 11 = Program Memory code protection off<br>10 = 0400h - 07FFh code protected<br>01 = 0200h - 07FFh code protected<br>11 = 0000h - 07FFh code protected |            |             |           |          |          |              |           |          |              |             |       |       |

| bit 7    | Unimpl             | emented                                                                                                                                                | I: Read as | s '1'       |           |          |          |              |           |          |              |             |       |       |

| bit 6    | Reserv             | ed: Do no                                                                                                                                              | ot use     |             |           |          |          |              |           |          |              |             |       |       |

| bit 3    | 1 = PW             | : Power-<br>RT disab<br>RT enabl                                                                                                                       | led        | Enable bi   | t         |          |          |              |           |          |              |             |       |       |

| bit 2    | WDTE:              | Watchdo                                                                                                                                                | g Timer E  | nable bit   |           |          |          |              |           |          |              |             |       |       |

|          |                    | T enable<br>T disable                                                                                                                                  | -          |             |           |          |          |              |           |          |              |             |       |       |

| bit 1-0  | FOSC1              | :FOSC0:                                                                                                                                                | Oscillator | r Selectior | n bits    |          |          |              |           |          |              |             |       |       |

|          |                    | C oscillato                                                                                                                                            |            |             |           |          |          |              |           |          |              |             |       |       |

|          |                    | S oscillato<br>F oscillato                                                                                                                             |            |             |           |          |          |              |           |          |              |             |       |       |

|          | 00 = LF            | oscillato                                                                                                                                              | or         |             |           |          |          |              |           |          |              |             |       |       |

|          | Note               | <b>1:</b> All c                                                                                                                                        | of the CP1 | I:CP0 pair  | s have to | be given | the same | value to ena | ble the o | code pro | tection sche | eme listed. |       |       |

|          |                    |                                                                                                                                                        |            |             |           |          |          |              |           |          |              |             |       |       |

|          | Legend             | 1:                                                                                                                                                     |            |             |           |          |          |              |           |          |              |             |       |       |

| Legend:                  |                  |                               |                    |

|--------------------------|------------------|-------------------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read a | s '0'              |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

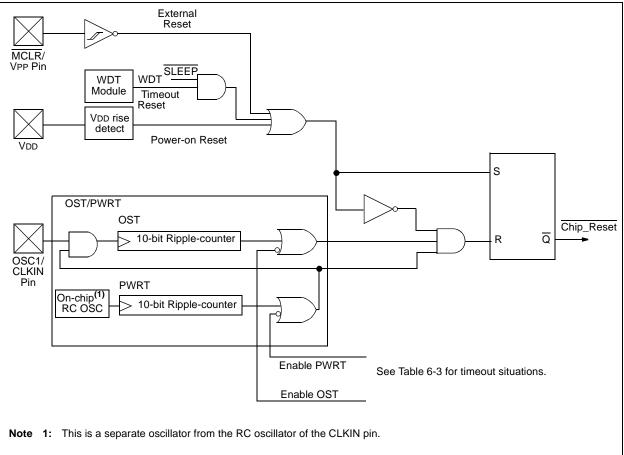

### 6.3 RESET

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers. A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

## 6.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 6-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 6-1:

- Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- Restores the W register

#### EXAMPLE 6-1: SAVING THE STATUS AND W REGISTERS IN RAM

|       | 117            |                                           |

|-------|----------------|-------------------------------------------|

| MOVWF | W_TEMP         | ;copy W to TEMP<br>;register, could be in |

|       |                | -                                         |

|       |                | ;either bank                              |

| SWAPF | STATUS,W       | ;swap STATUS to be                        |

|       |                | ;saved into W                             |

| BCF   | STATUS, RPO    | ;change to bank0                          |

|       |                | ;regardless of                            |

|       |                | ;current bank                             |

| MOVWF | STATUS_TEMP    | ;save STATUS to bank0                     |

|       |                | ;register                                 |

| :     |                |                                           |

| :     |                |                                           |

| :     |                |                                           |

| SWAPF | STATUS_TEMP, W | 1;swap STATUS_TEMP                        |

|       |                | ;register into W, sets                    |

|       |                | ;bank to original state                   |

| MOVWF | STATUS         | ;move W into STATUS                       |

|       |                | ;register                                 |

| SWAPF | W_TEMP,F       | ;swap W_TEMP                              |

| SWAPF | W_TEMP,W       | ;swap W_TEMP into W                       |

## 6.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT timeout generates a device RESET. If the device is in SLEEP mode, a WDT timeout causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 6.1).

#### 6.7.1 WDT PERIOD

The WDT has a nominal timeout period of 18 ms, (with no prescaler). The timeout periods vary with temperature, VDD and process variations from part-to-part (see DC specs). If longer timeout periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, timeout periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer timeout.

#### 6.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT timeout occurs.

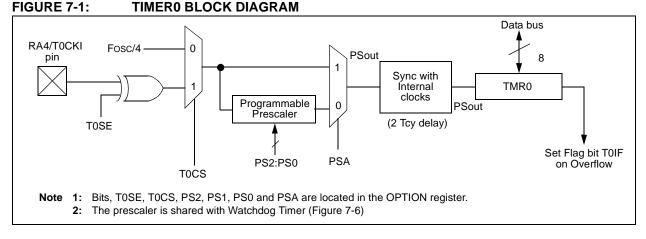

## 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

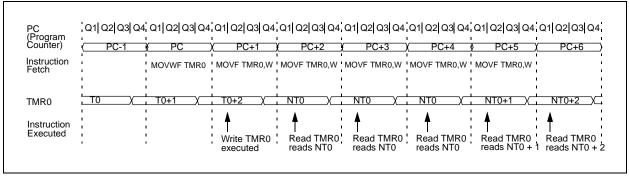

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

## 7.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

## FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

NOTES:

# 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \le k \le 255$                                                                                                       |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| Words:           | 1                                                                                                                       |

| Cycles:          | 1                                                                                                                       |

| Example          | ADDLW 0x15                                                                                                              |

|                  | Before Instruction                                                                                                      |

|                  | W = 0x10                                                                                                                |

|                  | After Instruction                                                                                                       |

|                  | W = 0x25                                                                                                                |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                         |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |  |  |

| ANDLW            | AND Li                                                                                                              | teral wit | h W   |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|-----------|-------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                           | ANDLW     | / k   |      |  |  |  |

| Operands:        | $0 \le k \le 2$                                                                                                     | 255       |       |      |  |  |  |

| Operation:       | (W) .AN                                                                                                             | ID. (k) → | • (W) |      |  |  |  |

| Status Affected: | Z                                                                                                                   |           |       |      |  |  |  |

| Encoding:        | 11                                                                                                                  | 1001      | kkkk  | kkkk |  |  |  |

|                  | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |           |       |      |  |  |  |

| Words:           | 1                                                                                                                   |           |       |      |  |  |  |

| Cycles:          | 1                                                                                                                   |           |       |      |  |  |  |

| Example          | ANDLW                                                                                                               | 0x5F      |       |      |  |  |  |

|                  | Before I                                                                                                            | nstructio | on    |      |  |  |  |

|                  | W                                                                                                                   | =         | 0xA3  |      |  |  |  |

|                  | After Ins                                                                                                           | struction |       |      |  |  |  |

|                  | W                                                                                                                   | =         | 0x03  |      |  |  |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                       |  |  |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |  |  |  |  |

-

## 9.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 9.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

#### 9.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

## 9.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 9.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can also link relocatable objects from pre-compiled libraries, using directives from a linker script.

The MPLIB object librarian is a librarian for precompiled code to be used with the MPLINK object linker. When a routine from a library is called from another source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. The MPLIB object librarian manages the creation and modification of library files.

The MPLINK object linker features include:

- Integration with MPASM assembler and MPLAB C17 and MPLAB C18 C compilers.

- Allows all memory areas to be defined as sections to provide link-time flexibility.

The MPLIB object librarian features include:

- Easier linking because single libraries can be included instead of many smaller files.

- Helps keep code maintainable by grouping related modules together.

- Allows libraries to be created and modules to be added, listed, replaced, deleted or extracted.

## 9.5 MPLAB SIM Software Simulator

The MPLAB SIM software simulator allows code development in a PC-hosted environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file, or user-defined key press, to any of the pins. The execution can be performed in single step, execute until break, or Trace mode.

The MPLAB SIM simulator fully supports symbolic debugging using the MPLAB C17 and the MPLAB C18 C compilers and the MPASM assembler. The software simulator offers the flexibility to develop and debug code outside of the laboratory environment, making it an excellent multi-project software development tool.

## 9.6 MPLAB ICE High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB ICE universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily re configured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE in-circuit emulator system has been designed as a real-time emulation system, with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows environment were chosen to best make these features available to you, the end user.

## 9.7 ICEPIC In-Circuit Emulator

The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One-Time-Programmable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules, or daughter boards. The emulator is capable of emulating without target application circuitry being present.

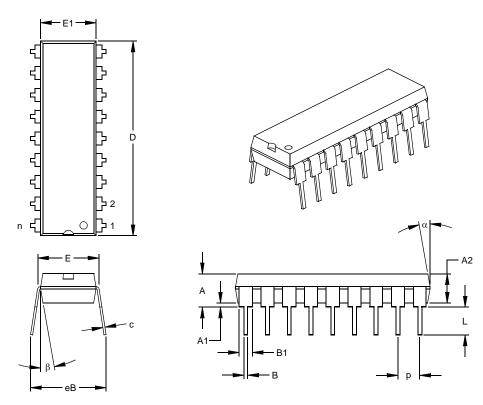

## 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                            | Units    |      | INCHES* |      | MILLIMETERS |       |       |  |

|----------------------------|----------|------|---------|------|-------------|-------|-------|--|

| Dimensio                   | n Limits | MIN  | NOM     | MAX  | MIN         | NOM   | MAX   |  |

| Number of Pins             | n        |      | 18      |      |             | 18    |       |  |

| Pitch                      | р        |      | .100    |      |             | 2.54  |       |  |

| Top to Seating Plane       | А        | .140 | .155    | .170 | 3.56        | 3.94  | 4.32  |  |

| Molded Package Thickness   | A2       | .115 | .130    | .145 | 2.92        | 3.30  | 3.68  |  |

| Base to Seating Plane      | A1       | .015 |         |      | 0.38        |       |       |  |

| Shoulder to Shoulder Width | Е        | .300 | .313    | .325 | 7.62        | 7.94  | 8.26  |  |

| Molded Package Width       | E1       | .240 | .250    | .260 | 6.10        | 6.35  | 6.60  |  |

| Overall Length             | D        | .890 | .898    | .905 | 22.61       | 22.80 | 22.99 |  |

| Tip to Seating Plane       | L        | .125 | .130    | .135 | 3.18        | 3.30  | 3.43  |  |

| Lead Thickness             | С        | .008 | .012    | .015 | 0.20        | 0.29  | 0.38  |  |

| Upper Lead Width           | B1       | .045 | .058    | .070 | 1.14        | 1.46  | 1.78  |  |

| Lower Lead Width           | В        | .014 | .018    | .022 | 0.36        | 0.46  | 0.56  |  |

| Overall Row Spacing §      | eB       | .310 | .370    | .430 | 7.87        | 9.40  | 10.92 |  |

| Mold Draft Angle Top       | α        | 5    | 10      | 15   | 5           | 10    | 15    |  |

| Mold Draft Angle Bottom    | β        | 5    | 10      | 15   | 5           | 10    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

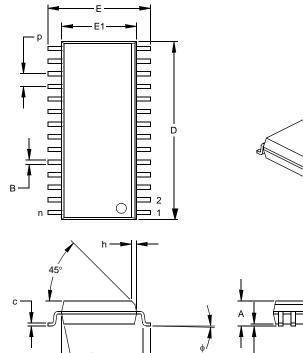

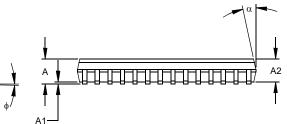

#### 28-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                                | Units       |      | INCHES* |      | N     | <b>IILLIMETERS</b> | 6     |

|--------------------------------|-------------|------|---------|------|-------|--------------------|-------|

| Dimens                         | sion Limits | MIN  | NOM     | MAX  | MIN   | NOM                | MAX   |

| Number of Pins                 | n           |      | 28      |      |       | 28                 |       |

| Pitch                          | р           |      | .050    |      |       | 1.27               |       |

| Overall Height                 | А           | .093 | .099    | .104 | 2.36  | 2.50               | 2.64  |

| Molded Package Thickness       | A2          | .088 | .091    | .094 | 2.24  | 2.31               | 2.39  |

| Standoff §                     | A1          | .004 | .008    | .012 | 0.10  | 0.20               | 0.30  |

| Overall Width                  | E           | .394 | .407    | .420 | 10.01 | 10.34              | 10.67 |

| Molded Package Width           | E1          | .288 | .295    | .299 | 7.32  | 7.49               | 7.59  |

| Overall Length                 | D           | .695 | .704    | .712 | 17.65 | 17.87              | 18.08 |

| Chamfer Distance               | h           | .010 | .020    | .029 | 0.25  | 0.50               | 0.74  |

| Foot Length                    | L           | .016 | .033    | .050 | 0.41  | 0.84               | 1.27  |

| Foot Angle Top                 | φ           | 0    | 4       | 8    | 0     | 4                  | 8     |

| Lead Thickness                 | С           | .009 | .011    | .013 | 0.23  | 0.28               | 0.33  |

| Lead Width                     | В           | .014 | .017    | .020 | 0.36  | 0.42               | 0.51  |

| Mold Draft Angle Top           | α           | 0    | 12      | 15   | 0     | 12                 | 15    |

| Mold Draft Angle Bottom        | β           | 0    | 12      | 15   | 0     | 12                 | 15    |

| * O a starallia a Danama ata a |             |      |         |      |       |                    |       |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

JEDEC Equivalent: MS-013

Drawing No. C04-052

# INDEX

## A

| ADDLW Instruction      |    |

|------------------------|----|

| ADDWF Instruction      |    |

| ANDLW Instruction      |    |

| ANDWF Instruction      |    |

| Architectural Overview | 9  |

| Assembler              |    |

| MPASM Assembler        | 67 |

|                        |    |

## В

| BCF Instruction    |    |

|--------------------|----|

| Block Diagram      |    |

| TIMER0             | 47 |

| TMR0/WDT PRESCALER | 50 |

| BSF Instruction    |    |

| BTFSC Instruction  |    |

| BTFSS Instruction  | 57 |

|                    |    |

# С

| CALL Instruction                  | 57 |

|-----------------------------------|----|

| Clocking Scheme/Instruction Cycle |    |

| CLRF Instruction                  | 57 |

| CLRW Instruction                  |    |

| CLRWDT Instruction                |    |

| Code Protection                   |    |

| COMF Instruction                  |    |

| Configuration Bits                | 31 |

|                                   |    |

## D

| Data Memory Organization |    |

|--------------------------|----|

| DECF Instruction         | 58 |

| DECFSZ Instruction       | 59 |

| Development Support      | 67 |

# Ε

| Errata3                             |  |

|-------------------------------------|--|

| External Crystal Oscillator Circuit |  |

# G

| General purpose Register File13 |  |

|---------------------------------|--|

| GOTO Instruction                |  |

## I

|                                             | ~~ |

|---------------------------------------------|----|

| I/O Ports                                   |    |

| I/O Programming Considerations              | 28 |

| ICEPIC In-Circuit Emulator                  |    |

| ID Locations                                | 46 |

| INCF Instruction                            |    |

| INCFSZ Instruction                          |    |

| In-Circuit Serial Programming               | 46 |

| Indirect Addressing, INDF and FSR Registers | 21 |

| Instruction Flow/Pipelining                 | 12 |

| Instruction Set                             |    |

| ADDLW                                       | 55 |

| ADDWF                                       | 55 |

| ANDLW                                       | 55 |

| ANDWF                                       | 55 |

| BCF                                         | 56 |

| BSF                                         | 56 |

| BTFSC                                       | 56 |

| BTFSS                                       | 57 |

| CALL                                        | 57 |

| CLRF                                        | 57 |

| CLRW                    | 58 |

|-------------------------|----|

| CLRWDT                  | 58 |

| COMF                    | 58 |

| DECF                    | 58 |

| DECFSZ                  | 59 |

| GOTO                    | 59 |

| INCF                    | 59 |

| INCFSZ                  | 60 |

| IORLW                   | 60 |

| IORWF                   | 60 |

| MOVF                    | 61 |

| MOVLW                   | 60 |

| MOVWF                   | 61 |

| NOP                     | 61 |

| OPTION                  | 61 |

| RETFIE                  | 62 |

| RETLW                   | 62 |

| RETURN                  | 62 |

| RLF                     | 62 |

| RRF                     | 63 |

| SLEEP                   | 63 |

| SUBLW                   | 63 |

| SUBWF                   | 64 |

| SWAPF                   | 64 |

| TRIS                    | 64 |

| XORLW                   | 65 |

| XORWF                   | 65 |

| Instruction Set Summary | 53 |

| INT Interrupt           | 42 |

| INTCON Register         | 19 |

| Interrupts              | 41 |

| IORLW Instruction       | 60 |

| IORWF Instruction       | 60 |

|                         |    |

## Κ

## М

| MOVF Instruction                                         |

|----------------------------------------------------------|

| MOVLW Instruction                                        |

| MOVWF Instruction                                        |

| MPLAB C17 and MPLAB C18 C Compilers 67                   |

| MPLAB ICD In-Circuit Debugger 69                         |

| MPLAB ICE High Performance Universal In-Circuit Emulator |

| with MPLAB IDE                                           |

| MPLAB Integrated Development Environment Software 67     |

| MPLINK Object Linker/MPLIB Object Librarian 68           |

## Ν

| NOP Instruction | . 61 |

|-----------------|------|

|                 | . 01 |

## 0

| One-Time-Programmable (OTP) Devices | 7  |

|-------------------------------------|----|

| OPTION Instruction                  | 61 |

| OPTION Register                     |    |

| Oscillator Configurations           | 33 |

| Oscillator Start-up Timer (OST)     | 36 |

## Ρ

| ) |

|---|

| ) |

| ) |

| ) |

| ) |

|   |

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                   | x <u>xx</u> xxx                                                                                                               | Examples:                                                                                                                                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device To         | emperature Package Pattern<br>Range                                                                                           | a) PIC17C756–16L Commercial Temp.,<br>PLCC package, 16 MHz,<br>normal VDD limits                                                                         |

| Device            | PIC17C756: Standard VDD range<br>PIC17C756T: (Tape and Reel)<br>PIC17LC756: Extended VDD range                                | <ul> <li>b) PIC17LC756–08/PT Commercial Temp.,<br/>TQFP package, 8MHz,<br/>extended VDD limits</li> <li>c) PIC17C756–33I/PT Industrial Temp.,</li> </ul> |

| Temperature Range | $\begin{array}{rcl} - & = & 0^{\circ}C \text{ to } +70^{\circ}C \\ I & = & -40^{\circ}C \text{ to } +85^{\circ}C \end{array}$ | TQFP package, 33 MHz,<br>normal VDD limits                                                                                                               |

| Package           | CL = Windowed LCC<br>PT = TQFP<br>L = PLCC                                                                                    |                                                                                                                                                          |

| Pattern           | QTP, SQTP, ROM Code (factory specified) or<br>Special Requirements. Blank for OTP and<br>Windowed devices.                    |                                                                                                                                                          |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

## Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)