Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5КВ (2К х 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558-04e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 2.0 PIC16C55X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C55X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PROMATE<sup>®</sup> programmers both support programming of the PIC16C55X.

## 2.2 One-Time Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 Serialized Quick-Turnaround Production (SQTP<sup>™</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number. bit 5

### 4.2.2.2 OPTION Register

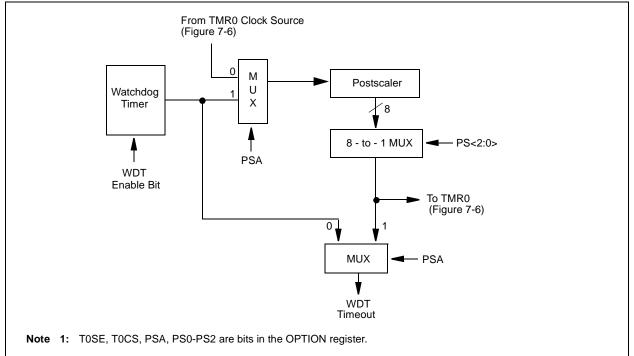

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

| Note 1: To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |  |  |

|---------------------------------------------------|--|--|--|--|--|--|--|--|

| TMR0, assign the prescaler to the WDT             |  |  |  |  |  |  |  |  |

| (PSA = 1).                                        |  |  |  |  |  |  |  |  |

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit7  |        |       |       |       |       |       | bit0  |

|       |        |       |       |       |       |       |       |

- bit 7 **RBPU**: PORTB Pull-up Enable bit

- 1 = PORTB pull-ups are disabled

- 0 = PORTB pull-ups are enabled by individual port latch values

### bit 6 **INTEDG**: Interrupt Edge Select bit

- 1 = Interrupt on rising edge of RB0/INT pin

- 0 = Interrupt on falling edge of RB0/INT pin

- TOCS: TMR0 Clock Source Select bit

- 1 = Transition on RA4/T0CKI pin

- 0 = Internal instruction cycle clock (CLKOUT)

- bit 4 TOSE: TMR0 Source Edge Select bit

- 1 = Increment on high-to-low transition on RA4/T0CKI pin

- 0 = Increment on low-to-high transition on RA4/T0CKI pin

### bit 3 **PSA**: Prescaler Assignment bit

- 1 = Prescaler is assigned to the WDT

- 0 = Prescaler is assigned to the Timer0 module

### bit 2-0 PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1 : 128   | 1:64     |

| 111       | 1 : 256   | 1 : 128  |

| Legend:                  |                  |                      |                    |

|--------------------------|------------------|----------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources.

| Note: | Interrupt flag bits get set when an interrupt |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|

|       | condition occurs regardless of the state of   |  |  |  |  |

|       | its corresponding enable bit or the global    |  |  |  |  |

|       | enable bit, GIE (INTCON<7>).                  |  |  |  |  |

| REGISTER 4-3: | : INTCON REGISTER (ADDRESS 0BH OR 8BH)                                                                                                                  |                                                                                                                  |              |              |            |            |                 |       |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------|------------|-----------------|-------|--|

|               | R/W-0                                                                                                                                                   | Reserved                                                                                                         | R/W-0        | R/W-0        | R/W-0      | R/W-0      | R/W-0           | R/W-x |  |

|               | GIE                                                                                                                                                     | —                                                                                                                | T0IE         | INTE         | RBIE       | T0IF       | INTF            | RBIF  |  |

|               | bit7                                                                                                                                                    |                                                                                                                  |              |              |            |            |                 | bit0  |  |

|               |                                                                                                                                                         |                                                                                                                  |              |              |            |            |                 |       |  |

| bit 7         | GIE: Global                                                                                                                                             | IE: Global Interrupt Enable bit                                                                                  |              |              |            |            |                 |       |  |

|               |                                                                                                                                                         | 1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                              |              |              |            |            |                 |       |  |

| bit 6         | Reserved:                                                                                                                                               | For future use                                                                                                   | . Always m   | aintain this | bit clear. |            |                 |       |  |

| bit 5         | TOIE: TMR(                                                                                                                                              | Overflow Inte                                                                                                    | errupt Enab  | le bit       |            |            |                 |       |  |

|               |                                                                                                                                                         | s the TMR0 int<br>s the TMR0 in                                                                                  |              |              |            |            |                 |       |  |

| bit 4         | INTE: RB0/                                                                                                                                              | INT External I                                                                                                   | nterrupt En  | able bit     |            |            |                 |       |  |

|               |                                                                                                                                                         | <ul><li>1 = Enables the RB0/INT external interrupt</li><li>0 = Disables the RB0/INT external interrupt</li></ul> |              |              |            |            |                 |       |  |

| bit 3         | RBIE: RB P                                                                                                                                              | RBIE: RB Port Change Interrupt Enable bit                                                                        |              |              |            |            |                 |       |  |

|               | <ul><li>1 = Enables the RB port change interrupt</li><li>0 = Disables the RB port change interrupt</li></ul>                                            |                                                                                                                  |              |              |            |            |                 |       |  |

| bit 2         | T0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                  |                                                                                                                  |              |              |            |            |                 |       |  |

|               | <ul> <li>1 = TMR0 register has overflowed (must be cleared in software)</li> <li>0 = TMR0 register did not overflow</li> </ul>                          |                                                                                                                  |              |              |            |            |                 |       |  |

| bit 1         | bit 1 INTF: RB0/INT External Interrupt Flag bit                                                                                                         |                                                                                                                  |              |              |            |            |                 |       |  |

|               | <ul> <li>1 = The RB0/INT external interrupt occurred (must be cleared in software)</li> <li>0 = The RB0/INT external interrupt did not occur</li> </ul> |                                                                                                                  |              |              |            |            |                 |       |  |

| bit 0         | RBIF: RB P                                                                                                                                              | ort Change In                                                                                                    | terrupt Flag | g bit        |            |            |                 |       |  |

|               | 1 = When at least one of the RB7:RB4 pins changed state (must be cleared in software)                                                                   |                                                                                                                  |              |              |            |            |                 |       |  |

|               | 0 = None of the RB7:RB4 pins have changed state                                                                                                         |                                                                                                                  |              |              |            |            |                 |       |  |

|               | Legend:                                                                                                                                                 |                                                                                                                  |              |              |            |            |                 |       |  |

|               | R = Readat                                                                                                                                              | ole bit                                                                                                          | W = W        | ritable bit  | U = Unir   | nplemented | bit, read as '( | )'    |  |

|               | - n = Value at POR reset $'1'$ = Bit is set $'0'$ = Bit is cleared x = Bit is unknown                                                                   |                                                                                                                  |              |              |            |            |                 |       |  |

## REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

© 1996-2013 Microchip Technology Inc.

### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

# 5.3 PORTC and TRISC Registers<sup>(1)</sup>

PORTC is a 8-bit wide latch. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISC register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISC register puts the contents of the output latch on the selected pin(s).

Reading the PORTC register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch

FIGURE 5-5: BLOCK DIAGRAM OF

### PORT PINS RC<7:0> Data Bus D Q Vdd WR PORT ск 🔪 Q P Data Latch Q Ν D I/O pin WR T<u>RISC</u> Q ∘ск҇∢\_ Vss Vss TRIS Latch TTL Input Buffer RD TRISC Q D FN. **RD PORTC**

| Name | Bit # | Buffer Type | Function                 |

|------|-------|-------------|--------------------------|

| RC0  | Bit 0 | TTL         | Bi-directional I/O port. |

| RC1  | Bit 1 | TTL         | Bi-directional I/O port. |

| RC2  | Bit 2 | TTL         | Bi-directional I/O port. |

| RC3  | Bit 3 | TTL         | Bi-directional I/O port. |

| RC4  | Bit 4 | TTL         | Bi-directional I/O port. |

| RC5  | Bit 5 | TTL         | Bi-directional I/O port. |

| RC6  | Bit 6 | TTL         | Bi-directional I/O port. |

| RC7  | Bit 7 | TTL         | Bi-directional I/O port. |

Legend: ST = Schmitt Trigger, TTL = TTL input

### TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC AND TRISC

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 07h     | PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx       | uuuu uuuu                       |

| 87h     | TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged Note 1: PIC16C557 ONLY.

# 6.3 RESET

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

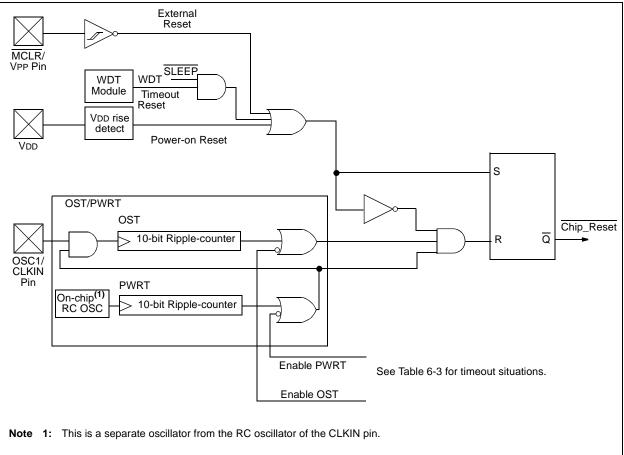

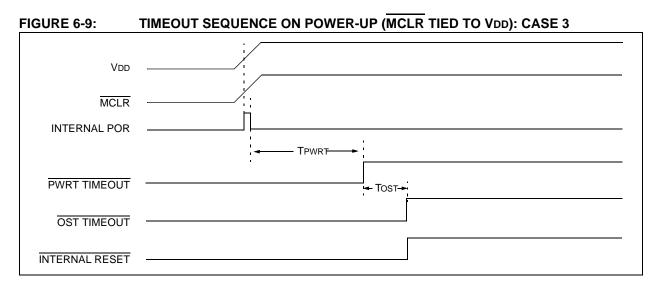

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers. A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

# PIC16C55X

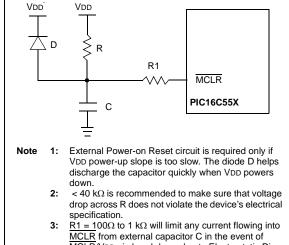

### FIGURE 6-10: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

| Address | Name         | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other RESETS |

|---------|--------------|-------|----------|-------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 2007h   | Config. bits | _     | Reserved | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |              |                           |

| 81h     | OPTION       | RBPU  | INTEDG   | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111    | 1111 1111                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

#### 6.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the  $\overline{TO}$  bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or hiimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The T0CKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |  |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | by a WDT timeout does not drive MCLR      |  |  |  |  |  |  |  |  |  |  |  |

|       | pin low.                                  |  |  |  |  |  |  |  |  |  |  |  |

#### 6.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- External RESET input on MCLR pin 1

- Watchdog Timer Wake-up (if WDT was enabled) 2.

- Interrupt from RB0/INT pin or RB Port change 3.

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device RESET. PD bit, which is set on power-up is cleared when SLEEP is invoked. TO bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes-up from SLEEP, regardless of the source of wake-up.

#### Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q1 Q2 Q3 Q4 OSC1 MMM Tost<sup>(2)</sup> CLKOUT(4) INT pin INTF flag (INTCON<1>) Interrupt Latency<sup>(2)</sup> GIE bit (INTCON<7>) Processor in SLEEP **INSTRUCTION FLOW** PC PC+2 PC + 2PC+' PC+2 0004h 0005 Instruction fetched Inst(PC + 1) Inst(PC + 2) Inst(0004h) Inst(0005h) Inst(PC) = SLEEPInstruction executed Inst(PC - 1) SLEEP Inst(PC + 1) Dummy cycle Dummy cycle Inst(0004h) 1: XT, HS or LP Oscillator mode assumed. Note

#### **FIGURE 6-14:** WAKE-UP FROM SLEEP THROUGH INTERRUPT

TOST = 1024Tosc (drawing not to scale). This delay will not be there for RC osc mode. 2:

GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line. 3:

CLKOUT is not available in these osc modes, but shown here for timing reference. 4:

# PIC16C55X

| BCF              | Bit Clea                                                                      | ar f   |        |      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------|--------|--------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                     | BCF 1  | f,b    |      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |        |        |      |  |  |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                                     |        |        |      |  |  |  |  |

| Status Affected: | None                                                                          |        |        |      |  |  |  |  |

| Encoding:        | 01                                                                            | 00bb   | bfff   | ffff |  |  |  |  |

| Description:     | Description: Bit 'b' in register 'f' is cleared.                              |        |        |      |  |  |  |  |

| Words:           | 1                                                                             |        |        |      |  |  |  |  |

| Cycles:          | 1                                                                             |        |        |      |  |  |  |  |

| Example          | BCF                                                                           | FLAG_F | REG, 7 |      |  |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |        |        |      |  |  |  |  |

| Bit Se | t f |

|--------|-----|

|--------|-----|

BSF

| Syntax:                                      | [ <i>label</i> ] BSF f,b                                            |        |        |   |  |  |  |  |  |  |

|----------------------------------------------|---------------------------------------------------------------------|--------|--------|---|--|--|--|--|--|--|

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |        |        |   |  |  |  |  |  |  |

| Operation: $1 \rightarrow (f < b >)$         |                                                                     |        |        |   |  |  |  |  |  |  |

| Status Affected: None                        |                                                                     |        |        |   |  |  |  |  |  |  |

| Encoding:                                    | 01 01bb bfff ffff                                                   |        |        |   |  |  |  |  |  |  |

| Description: Bit 'b' in register 'f' is set. |                                                                     |        |        |   |  |  |  |  |  |  |

| Words:                                       | 1                                                                   |        |        |   |  |  |  |  |  |  |

| Cycles:                                      | 1                                                                   |        |        |   |  |  |  |  |  |  |

| Example                                      | BSF                                                                 | FLAG_F | REG, 7 | , |  |  |  |  |  |  |

|                                              | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction          |        |        |   |  |  |  |  |  |  |

|                                              | FLAG_REG = 0x8A                                                     |        |        |   |  |  |  |  |  |  |

| BTFSC                                                                        | Bit Test, Skip if Clear                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                      | [ label ] BTFSC f,b                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Operands:                                                                    | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Operation:                                                                   | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                             | None                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                    | 01 10bb bfff ffff                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Description:                                                                 | If bit 'b' in register 'f' is '0' then the next<br>instruction is skipped. If bit 'b' is '0' then<br>the next instruction fetched during the<br>current instruction execution is dis-<br>carded, and a $NOP$ is executed instead,<br>making this a two-cycle instruction. |  |  |  |  |  |  |  |  |  |

| Words:                                                                       | 1                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                      | 1(2)                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| Example                                                                      | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|                                                                              | Before Instruction                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|                                                                              | PC = address HERE                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1> = 1. |                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|                                                                              | PC = address FALSE                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

# 9.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

### 9.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

# 9.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

### 9.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

# 9.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

## 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Characteristics |      |                                               |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |        |                                                                                           |  |  |

|--------------------|------|-----------------------------------------------|------------|------------------------------------------------------|------------|--------|-------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym  | Characteristic                                | Min        | Тур†                                                 | Max        | Units  | Conditions                                                                                |  |  |

|                    | Vdd  | Supply Voltage                                |            |                                                      |            |        |                                                                                           |  |  |

| D001               |      | 16LC55X                                       | 3.0<br>2.5 | _                                                    | 5.5<br>5.5 | V      | XT and RC osc configuration<br>LP osc configuration                                       |  |  |

| D001<br>D001A      |      | 16C55X                                        | 3.0<br>4.5 |                                                      | 5.5<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                                   |  |  |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —          | 1.5*                                                 | —          | V      | Device in SLEEP mode                                                                      |  |  |

| D003               | VPOR | VDD Start Voltage to<br>ensure Power-on Reset | —          | Vss                                                  | —          | V      | See Section 6.4, Power-on Reset for details                                               |  |  |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _                                                    | —          | V/ms   | See Section 6.4, Power-on Reset for details                                               |  |  |

|                    | Idd  | Supply Current <sup>(2)</sup>                 |            |                                                      |            |        |                                                                                           |  |  |

| D010               |      | 16LC55X                                       | _          | 1.4                                                  | 2.5        | mA     | XT and RC osc configuration<br>Fosc = 2.0 MHz, VDD = 3.0V, WDT<br>disabled <sup>(4)</sup> |  |  |

| D010A              |      |                                               | _          | 26                                                   | 53         | μA     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT<br>disabled                        |  |  |

| D010               |      | 16C55X                                        | _          | 1.8                                                  | 3.3        | mA     | XT and RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V,<br>WDT disabled <sup>(4)</sup>   |  |  |

| D010A              |      |                                               | _          | 35                                                   | 70         | μΑ     | LP osc configuration,<br>PIC16C55X-04 only<br>Fosc = 32 kHz, VDD = 4.0V,<br>WDT disabled  |  |  |

| D013               |      |                                               | —          | 9.0                                                  | 20         | mA     | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V,<br>WDT disabled                        |  |  |

These parameters are characterized but not tested.

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

<u>OSC1</u> = external square wave, from rail to rail; all I/O pins configured as input, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as input and tied to VDD or Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

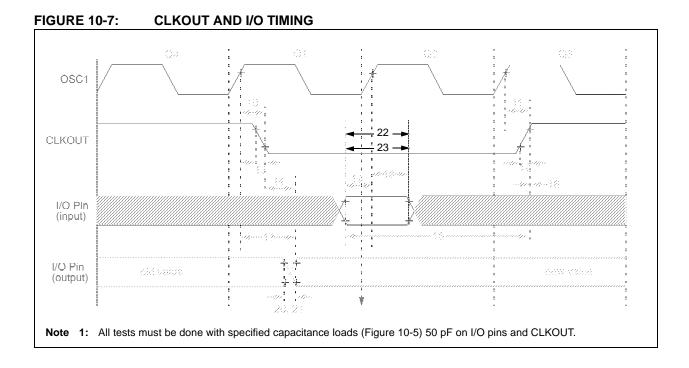

### **10.4** Timing Diagrams and Specifications

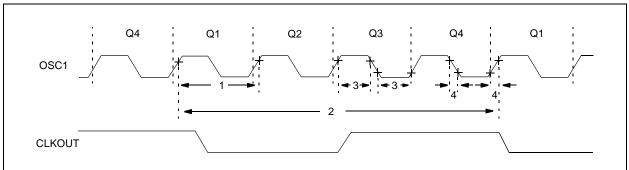

### FIGURE 10-6: EXTERNAL CLOCK TIMING

### TABLE 10-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                          | Min  | Тур†  | Max    | Units | Conditions                   |

|------------------|-------|-----------------------------------------|------|-------|--------|-------|------------------------------|

|                  | Fos   | External CLKIN Frequency <sup>(1)</sup> | DC   | —     | 4      | MHz   | XT and RC osc mode, VDD=5.0V |

|                  |       |                                         | DC   | —     | 20     | MHz   | HS osc mode                  |

|                  |       |                                         | DC   | —     | 200    | kHz   | LP osc mode                  |

|                  |       | Oscillator Frequency <sup>(1)</sup>     | DC   | _     | 4      | MHz   | RC osc mode, VDD=5.0V        |

|                  |       |                                         | 0.1  | —     | 4      | MHz   | XT osc mode                  |

|                  |       |                                         | 1    | _     | 20     | MHz   | HS osc mode                  |

|                  |       |                                         | DC   | -     | 200    | kHz   | LP osc mode                  |

| 1                | Tosc  | External CLKIN Period <sup>(1)</sup>    | 250  | _     | _      | ns    | XT and RC osc mode           |

|                  |       |                                         | 50   | —     | —      | ns    | HS osc mode                  |

|                  |       |                                         | 5    | —     | _      | μs    | LP osc mode                  |

|                  |       | Oscillator Period <sup>(1)</sup>        | 250  | _     | _      | ns    | RC osc mode                  |

|                  |       |                                         | 250  | —     | 10,000 | ns    | XT osc mode                  |

|                  |       |                                         | 50   | —     | 1,000  | ns    | HS osc mode                  |

|                  |       |                                         | 5    | —     | —      | μs    | LP osc mode                  |

| 2                | Тсу   | Instruction Cycle Time <sup>(1)</sup>   | 1.0  | Fos/4 | DC     | μs    | Tcy=Fos/4                    |

| 3*               | TosL, | External Clock in (OSC1) High or        | 100* | —     | —      | ns    | XT osc mode                  |

|                  | TosH  | Low Time                                | 2*   | —     | —      | μs    | LP osc mode                  |

|                  |       |                                         | 20*  | —     | —      | ns    | HS osc mode                  |

| 4*               | TosR, | External Clock in (OSC1) Rise or        | 25*  | —     | —      | ns    | XT osc mode                  |

|                  | TosF  | Fall Time                               | 50*  | —     | —      | ns    | LP osc mode                  |

|                  |       |                                         | 15*  | —     | —      | ns    | HS osc mode                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0 V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# PIC16C55X

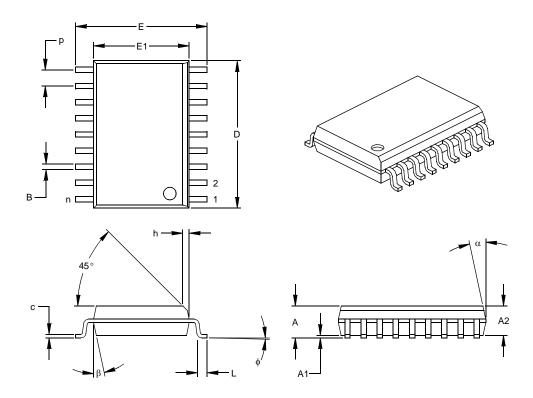

### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                          | Units |      | INCHES* |      | MILLIMETERS |       |       |  |

|--------------------------|-------|------|---------|------|-------------|-------|-------|--|

| Dimensi                  | MIN   | NOM  | MAX     | MIN  | NOM         | MAX   |       |  |

| Number of Pins           | n     |      | 18      |      |             | 18    |       |  |

| Pitch                    | р     |      | .050    |      |             | 1.27  |       |  |

| Overall Height           | Α     | .093 | .099    | .104 | 2.36        | 2.50  | 2.64  |  |

| Molded Package Thickness | A2    | .088 | .091    | .094 | 2.24        | 2.31  | 2.39  |  |

| Standoff §               | A1    | .004 | .008    | .012 | 0.10        | 0.20  | 0.30  |  |

| Overall Width            | E     | .394 | .407    | .420 | 10.01       | 10.34 | 10.67 |  |

| Molded Package Width     | E1    | .291 | .295    | .299 | 7.39        | 7.49  | 7.59  |  |

| Overall Length           | D     | .446 | .454    | .462 | 11.33       | 11.53 | 11.73 |  |

| Chamfer Distance         | h     | .010 | .020    | .029 | 0.25        | 0.50  | 0.74  |  |

| Foot Length              | L     | .016 | .033    | .050 | 0.41        | 0.84  | 1.27  |  |

| Foot Angle               | ¢     | 0    | 4       | 8    | 0           | 4     | 8     |  |

| Lead Thickness           | С     | .009 | .011    | .012 | 0.23        | 0.27  | 0.30  |  |

| Lead Width               | В     | .014 | .017    | .020 | 0.36        | 0.42  | 0.51  |  |

| Mold Draft Angle Top     | α     | 0    | 12      | 15   | 0           | 12    | 15    |  |

| Mold Draft Angle Bottom  | β     | 0    | 12      | 15   | 0           | 12    | 15    |  |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES:

NOTES: