#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558-04i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 3-1:         |                | Pin Numb               | INOUT D |                       |                       |                                                                                                                                                                                                                   |

|--------------------|----------------|------------------------|---------|-----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name               | PDIP SOIC SSOP |                        |         | Pin<br>Type           | Buffer<br>Type        | Description                                                                                                                                                                                                       |

| 00000000000        |                |                        |         |                       |                       | Description                                                                                                                                                                                                       |

| OSC1/CLKIN         | 16             | 16                     | 18      |                       | ST/CMOS               | Oscillator crystal input/external clock source output.                                                                                                                                                            |

| OSC2/CLKOUT        | 15             | 15                     | 17      | 0                     | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/VPP           | 4              | 4                      | 4       | I/P                   | ST                    | Master clear (Reset) input/programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                           |

| RA0                | 17             | 17                     | 19      | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA1                | 18             | 18                     | 20      | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA2                | 1              | 1                      | 1       | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA3                | 2              | 2                      | 2       | I/O                   | ST                    | Bi-directional I/O port                                                                                                                                                                                           |

| RA4/T0CKI          | 3              | 3                      | 3       | I/O                   | ST                    | Bi-directional I/O port or external clock input for TMR0.<br>Output is open drain type.                                                                                                                           |

| RB0/INT            | 6              | 6                      | 7       | I/O                   | TTL/ST <sup>(1)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. RB0/INT can also be selected as an external interrupt pin.                                                                          |

| RB1                | 7              | 7                      | 8       | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |

| RB2                | 8              | 8                      | 9       | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |

| RB3                | 9              | 9                      | 10      | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |

| RB4                | 10             | 10                     | 11      | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                            |

| RB5                | 11             | 11                     | 12      | I/O                   | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                            |

| RB6                | 12             | 12                     | 13      | I/O                   | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for<br>internal weak pull-up. Interrupt-on-change pin. Serial pro-<br>gramming clock.                                                                          |

| RB7                | 13             | 13                     | 14      | I/O                   | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin. Serial pro-<br>gramming data.                                                                              |

| RC0 <sup>(3)</sup> | 18             | 18                     | 18      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC1 <sup>(3)</sup> | 19             | 19                     | 19      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC2 <sup>(3)</sup> | 20             | 20                     | 20      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC3 <sup>(3)</sup> | 21             | 21                     | 21      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC4 <sup>(3)</sup> | 22             | 22                     | 22      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC5 <sup>(3)</sup> | 22             | 22                     | 22      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

|                    |                |                        |         |                       |                       |                                                                                                                                                                                                                   |

| RC6 <sup>(3)</sup> | 24             | 24                     | 24      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| RC7 <sup>(3)</sup> | 25             | 25                     | 25      | I/O                   | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |

| Vss                | 5              | 5                      | 5,6     | P                     |                       | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| VDD                | 14             | 14                     | 15,16   | P                     |                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Legend:            |                | = Output<br>= Not used |         | /O = Input<br>= Input | output                | P = Power<br>ST = Schmitt Trigger input                                                                                                                                                                           |

|                    |                | L = TTL inp            |         | – input               |                       |                                                                                                                                                                                                                   |

TABLE 3-1: PIC16C55X PINOUT DESCRIPTION

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: PIC16C557 only.

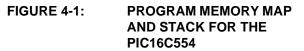

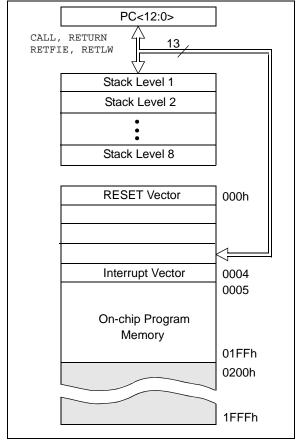

## 4.0 MEMORY ORGANIZATION

#### 4.1 Program Memory Organization

The PIC16C55X has a 13-bit program counter capable of addressing an 8 K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C554 and 2K x 14 (0000h - 07FFh) for the PIC16C557 and PIC16C558 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 spaces in the PIC16C554, or 2K x 14 space of the PIC16C558 and PIC16C557. The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2).

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C557 AND PIC16C558

#### 4.2 Data Memory Organization

The data memory (Figure 4-3 through Figure 4-5) is partitioned into two banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bank 0 is selected when the RP0 bit (STATUS <5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-6Fh (Bank 0) on the PIC16C554 and 20-7Fh (Bank 0) and A0-BFh (Bank 1) on the PIC16C558 and PIC16C557 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $80 \times 8$  in the PIC16C554 and 128 x 8 in the PIC16C557 and PIC16C558. Each can be accessed either directly or indirectly through the File Select Register, FSR (Section 4.4).

| Address                                       | Name                                                    | Bit 7                                          | Bit 6                                                                                             | Bit 5            | Bit 4               | Bit 3            | Bit 2        | Bit 1                        | Bit 0            | Value on<br>POR Reset                            | Detail on<br>Page:       |

|-----------------------------------------------|---------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|--------------|------------------------------|------------------|--------------------------------------------------|--------------------------|

| Bank 0                                        |                                                         |                                                |                                                                                                   |                  |                     |                  |              |                              |                  |                                                  |                          |

| 00h                                           | INDF                                                    |                                                | Addressing this location uses contents of FSR to address data memory (not a<br>physical register) |                  |                     |                  |              | ory (not a                   | XXXX XXXX        | 21                                               |                          |

| 01h                                           | TMR0                                                    | Timer0 N                                       | imer0 Module's Register                                                                           |                  |                     |                  |              |                              |                  | xxxx xxxx                                        | 47                       |

| 02h                                           | PCL                                                     | Program                                        | Counter's                                                                                         | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 03h                                           | STATUS                                                  | IRP <sup>(2)</sup>                             | RP1 <sup>(2)</sup>                                                                                | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 04h                                           | FSR                                                     | Indirect of                                    | data memo                                                                                         | ry address       | s pointer           |                  |              |                              |                  | xxxx xxxx                                        | 21                       |

| 05h                                           | PORTA                                                   | -                                              | —                                                                                                 | —                | RA4                 | RA3              | RA2          | RA1                          | RA0              | x xxxx                                           | 23                       |

| 06h                                           | PORTB                                                   | RB7                                            | RB6                                                                                               | RB5              | RB4                 | RB3              | RB2          | RB1                          | RB0              | xxxx xxxx                                        | 25                       |

| 07h                                           | PORTC <sup>(4)</sup>                                    | RC7                                            | RC6                                                                                               | RC5              | RC4                 | RC3              | RC2          | RC1                          | RC0              | xxxx xxxx                                        | 27                       |

| 08h                                           | _                                                       | Unimple                                        | mented                                                                                            |                  |                     |                  |              |                              |                  | _                                                |                          |

| 09h                                           | _                                                       | Unimple                                        | mented                                                                                            |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Ah                                           | PCLATH                                                  | _                                              | —                                                                                                 |                  | Write but           | fer for upp      | per 5 bits o | of progran                   | n counter        | 0 0000                                           | 21                       |

| 0Bh                                           | INTCON                                                  | GIE                                            | (3)                                                                                               | T0IE             | INTE                | RBIE             | T0IF         | INTF                         | RBIF             | 0000 000x                                        | 19                       |

| 0Ch                                           | —                                                       | Unimple                                        | mented                                                                                            |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Dh-1Eh                                       | —                                                       | Unimple                                        | mented                                                                                            |                  |                     |                  |              |                              |                  | _                                                | —                        |

| 1Fh                                           | —                                                       | Unimple                                        | mented                                                                                            |                  |                     |                  |              |                              |                  | _                                                | _                        |

| Bank 1                                        |                                                         |                                                |                                                                                                   |                  |                     |                  |              |                              |                  |                                                  |                          |

| 80h                                           | INDF                                                    | Addressi<br>physical                           | ing this loca<br>register)                                                                        | ation uses       | contents            | of FSR to a      | address d    | ata memo                     | ory (not a       | XXXX XXXX                                        | 21                       |

| 81h                                           | OPTION                                                  | RBPU                                           | INTEDG                                                                                            | TOCS             | T0SE                | PSA              | PS2          | PS1                          | PS0              | 1111 1111                                        | 18                       |

| 82h                                           | PCL                                                     | Program                                        | Counter's                                                                                         | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 83h                                           | STATUS                                                  | _                                              | _                                                                                                 | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 84h                                           | FSR                                                     |                                                |                                                                                                   | Indirect d       | ata memo            | ry address       | s pointer    |                              |                  | xxxx xxxx                                        | 21                       |

| 85h                                           | TRISA                                                   | -                                              | —                                                                                                 | —                | TRISA4              | TRISA3           | TRISA2       | TRISA1                       | TRISA0           | 1 1111                                           | 23                       |

| 86h                                           | TDIOD                                                   |                                                |                                                                                                   |                  |                     |                  | TDIODO       | TDICD4                       |                  |                                                  | 05                       |

| 0011                                          | TRISB                                                   | TRISB7                                         | TRISB6                                                                                            | TRISB5           | TRISB4              | TRISB3           | TRISB2       | TRISB1                       | TRISB0           | 1111 1111                                        | 25                       |

| 87h                                           | TRISB                                                   | TRISB7<br>TRISC7                               | TRISB6<br>TRISC6                                                                                  | TRISB5<br>TRISC5 | TRISB4<br>TRISC4    | TRISB3<br>TRISC3 | TRISB2       | TRISC1                       | TRISB0<br>TRISC0 | 1111 1111<br>1111 1111                           | 25                       |

|                                               |                                                         |                                                | TRISC6                                                                                            |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h                                           |                                                         | TRISC7                                         | TRISC6<br>mented                                                                                  |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h<br>88h                                    |                                                         | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                                  |                  | TRISC4              |                  | TRISC2       | TRISC1                       | TRISC0           |                                                  | 27<br>—                  |

| 87h<br>88h<br>89h                             | TRISC <sup>(4)</sup><br>—<br>—                          | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                                  |                  | TRISC4              | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—                              | 27<br>—<br>—             |

| 87h<br>88h<br>89h<br>8Ah                      | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple                   | TRISC6<br>mented<br>mented<br>(3)                                                                 | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh               | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br><br>GIE        | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                       | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch        | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                       | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch<br>8Dh | TRISC <sup>(4)</sup><br>—<br>PCLATH<br>INTCON<br>—<br>— | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>—<br>(3)<br>mented<br>mented                                                  | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1<br>of program<br>INTF | TRISC0           | 1111 1111<br>                                    | 27<br>—<br>21<br>19<br>— |

#### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C55X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved, always maintain these bits clear.

3: Bit 6 of INTCON register is reserved for future use. Always maintain this bit as clear.

4: PIC16C557 only.

#### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

NOTES:

## 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

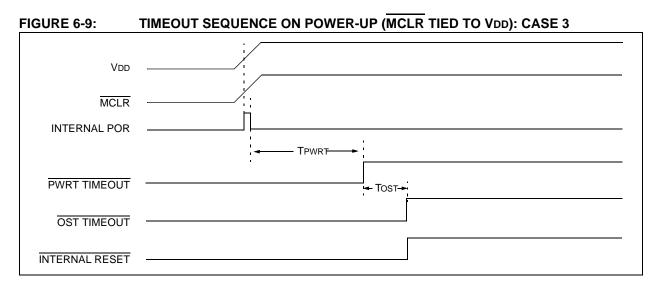

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

### 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

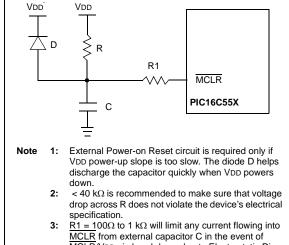

# PIC16C55X

#### FIGURE 6-10: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

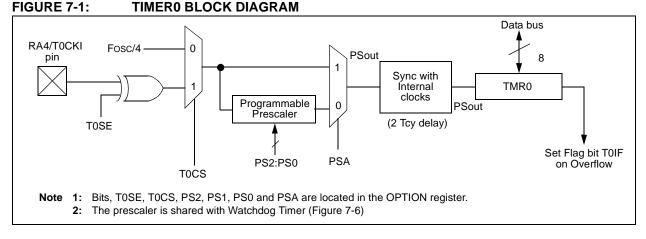

## 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

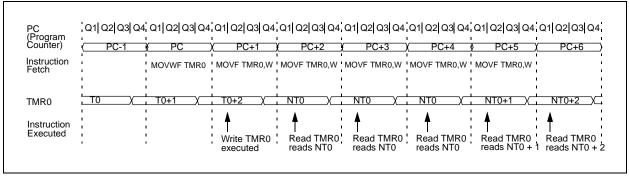

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

## 7.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

## FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT. Lines 5-7 are required only if the desired postscaler rate is 1:1 (PS<2:0> = 000) or 1:2 (PS<2:0> = 001).

| EXAMPLE 7-1: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (TIMER0→WDT)       |

|       | · · · · ·            |                          |

|-------|----------------------|--------------------------|

| BCF   | STATUS, RPO          | ;Skip if already in      |

|       |                      | ;Bank 0 CLRWDT Clear WDT |

| CLRF  | TMR0                 | ;Clear TMR0 & Prescaler  |

| BSF   | STATUS, RPO          | ;Bank 1                  |

| MOVLW | '00101111 <i>'</i> b | ;These 3 lines (5, 6, 7) |

| MOVWF | OPTION               | ;Are required only if    |

|       |                      | ;Desired PS<2:0> are     |

|       |                      | ;CLRWDT 000 or 001       |

| MOVLW | '00101xxx'b          | ;Set Postscaler to       |

| MOVWF | OPTION               | ;Desired WDT rate        |

| BCF   | STATUS, RPO          | ;Return to Bank 0        |

|       |                      |                          |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (           | · / · ····=···/     |

|--------|-------------|---------------------|

| CLRWDT |             | ;Clear WDT and      |

|        |             | ;prescaler          |

| BSF    | STATUS, RPO |                     |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| MOVWF  | OPTION      |                     |

| BCF    | STATUS, RPO |                     |

|        |             |                     |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6           | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-----------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 m | odule's registe | r     |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | Reserved        | TOIE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

| 81h     | OPTION | RBPU     | INTEDG          | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        | _               |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0',

**Note 1:** Shaded bits are not used by TMR0 module.

NOTES:

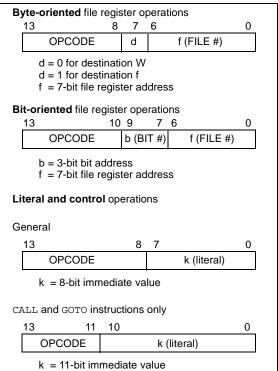

## 8.0 INSTRUCTION SET SUMMARY

Each PIC16C55X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C55X instruction set summary in Table 8-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 8-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field         | Description                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                                              |

| x             | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It<br>is the recommended form of use for compatibil-<br>ity with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                       |

| label         | Label name                                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                                             |

| то            | Timeout bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                                          |

| [ ]           | Options                                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                                 |

| ∈             | In the set of                                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 8-1 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 8-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16C55X

| CLRW             | Clear W                              | V        |              |        |

|------------------|--------------------------------------|----------|--------------|--------|

| Syntax:          | [ label ]                            | CLRW     |              |        |

| Operands:        | None                                 |          |              |        |

| Operation:       | $00h \rightarrow (V 1 \rightarrow Z$ | V)       |              |        |

| Status Affected: | Z                                    |          |              |        |

| Encoding:        | 00                                   | 0001     | 0000         | 0011   |

| Description:     | W register set.                      | is clear | ed. Zero bit | (Z) is |

| Words:           | 1                                    |          |              |        |

| Cycles:          | 1                                    |          |              |        |

| Example          | CLRW                                 |          |              |        |

|                  | Before In                            | structio | n            |        |

|                  | W                                    | =        | 0x5A         |        |

|                  | After Inst                           | ruction  |              |        |

|                  | W                                    | =        | 0x00         |        |

|                  | Z                                    | =        | 1            |        |

| COMF             | Complement f                                                   |                             |                              |      |  |  |  |

|------------------|----------------------------------------------------------------|-----------------------------|------------------------------|------|--|--|--|

| Syntax:          | [ label ]                                                      | COMF                        | f,d                          |      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | 7                           |                              |      |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (des$                              | st)                         |                              |      |  |  |  |

| Status Affected: | Z                                                              |                             |                              |      |  |  |  |

| Encoding:        | 00                                                             | 1001                        | dfff                         | ffff |  |  |  |

| Description:     | The conter<br>compleme<br>stored in V<br>stored bac            | nted. If 'd<br>V. If 'd' is | ' is 0 the re<br>1 the resul |      |  |  |  |

| Words:           | 1                                                              |                             |                              |      |  |  |  |

| Cycles:          | 1                                                              |                             |                              |      |  |  |  |

| Example          | COMF                                                           | REG1,0                      | )                            |      |  |  |  |

|                  | Before In                                                      | struction                   |                              |      |  |  |  |

|                  | REG                                                            | 1 =                         | 0x13                         |      |  |  |  |

|                  | After Inst                                                     | ruction                     |                              |      |  |  |  |

|                  | REG                                                            | 1 =                         | 0x13                         |      |  |  |  |

|                  | W                                                              | =                           | 0xEC                         |      |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                          |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                |  |  |  |  |  |

| Operands:        | None                                                                                                                                                          |  |  |  |  |  |

| Operation:       | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow PD$                                                 |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                        |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                             |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                             |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                             |  |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                        |  |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction                                                                                                    |  |  |  |  |  |

|                  | WDT counter = $0x00$                                                                                                                                          |  |  |  |  |  |

|                  | $\underline{WDT}$ prescaler = 0                                                                                                                               |  |  |  |  |  |

|                  | $\overline{TO} = 1$                                                                                                                                           |  |  |  |  |  |

|                  | PD = 1                                                                                                                                                        |  |  |  |  |  |

....

| DECF             | Decrement f                                                                                                                                 |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                            |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                           |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                           |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                           |  |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                                 |  |  |  |  |  |

|                  | Before Instruction                                                                                                                          |  |  |  |  |  |

|                  | CNT = 0x01                                                                                                                                  |  |  |  |  |  |

|                  | Z = 0                                                                                                                                       |  |  |  |  |  |

|                  | After Instruction                                                                                                                           |  |  |  |  |  |

|                  | CNT = 0x00                                                                                                                                  |  |  |  |  |  |

|                  | Z = 1                                                                                                                                       |  |  |  |  |  |

|                  |                                                                                                                                             |  |  |  |  |  |

## 9.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 9.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

### 9.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

## 9.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 10.3 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

#### 1. TppS2ppS

2. TppS

| т      |                                         |    |              |  |

|--------|-----------------------------------------|----|--------------|--|

| F      | Frequency                               | Т  | Time         |  |

| Lowerc | ase subscripts (pp) and their meanings: |    |              |  |

| рр     |                                         |    |              |  |

| ck     | CLKOUT                                  | OS | OSC1         |  |

| io     | I/O port                                | t0 | TOCKI        |  |

| mc     | MCLR                                    |    |              |  |

| Upperc | ase letters and their meanings:         |    |              |  |

| S      |                                         |    |              |  |

| F      | Fall                                    | Р  | Period       |  |

| Н      | High                                    | R  | Rise         |  |

| I      | Invalid (Hi-impedance)                  | V  | Valid        |  |

| L      | Low                                     | Z  | Hi-impedance |  |

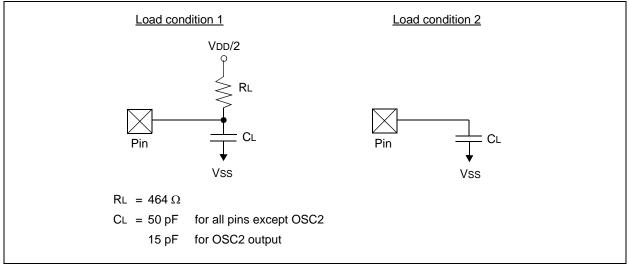

## FIGURE 10-5: LOAD CONDITIONS

NOTES:

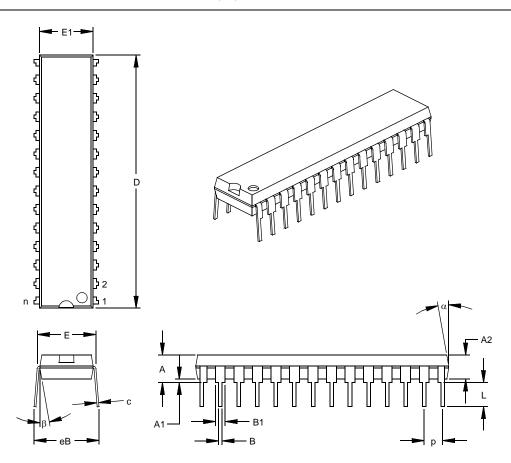

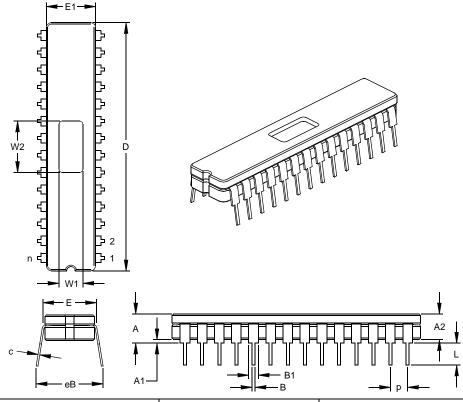

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| ision L                    | n  | MIN                                                      | NOM                                                    | MAX                                                     | MIN                                                    | NOM                                                    | MAX                                                     |

|----------------------------|----|----------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

|                            |    |                                                          |                                                        |                                                         |                                                        |                                                        | IVIAA                                                   |

|                            |    |                                                          | 28                                                     |                                                         |                                                        | 28                                                     |                                                         |

|                            | р  |                                                          | .100                                                   |                                                         |                                                        | 2.54                                                   |                                                         |

|                            | Α  | .140                                                     | .150                                                   | .160                                                    | 3.56                                                   | 3.81                                                   | 4.06                                                    |

| Molded Package Thickness   |    | .125                                                     | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

| Base to Seating Plane      |    | .015                                                     |                                                        |                                                         | 0.38                                                   |                                                        |                                                         |

| Shoulder to Shoulder Width |    | .300                                                     | .310                                                   | .325                                                    | 7.62                                                   | 7.87                                                   | 8.26                                                    |

|                            | E1 | .275                                                     | .285                                                   | .295                                                    | 6.99                                                   | 7.24                                                   | 7.49                                                    |

| Overall Length             |    | 1.345                                                    | 1.365                                                  | 1.385                                                   | 34.16                                                  | 34.67                                                  | 35.18                                                   |

|                            | L  | .125                                                     | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|                            | С  | .008                                                     | .012                                                   | .015                                                    | 0.20                                                   | 0.29                                                   | 0.38                                                    |

| Upper Lead Width           |    | .040                                                     | .053                                                   | .065                                                    | 1.02                                                   | 1.33                                                   | 1.65                                                    |

| Lower Lead Width           |    | .016                                                     | .019                                                   | .022                                                    | 0.41                                                   | 0.48                                                   | 0.56                                                    |

| Ş                          | eB | .320                                                     | .350                                                   | .430                                                    | 8.13                                                   | 8.89                                                   | 10.92                                                   |

| Mold Draft Angle Top       |    | 5                                                        | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

| Mold Draft Angle Bottom β  |    | 5                                                        | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

|                            | §  | A<br>A2<br>A1<br>E<br>E1<br>D<br>L<br>C<br>B1<br>B1<br>B | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

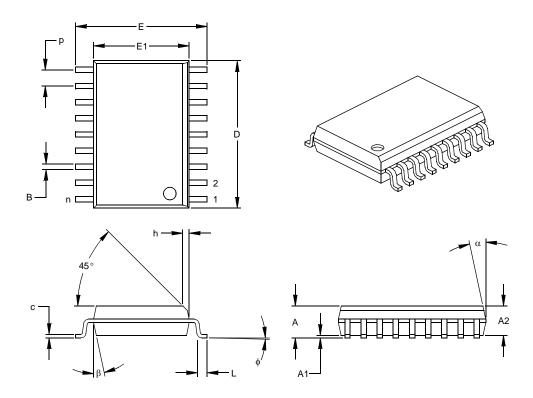

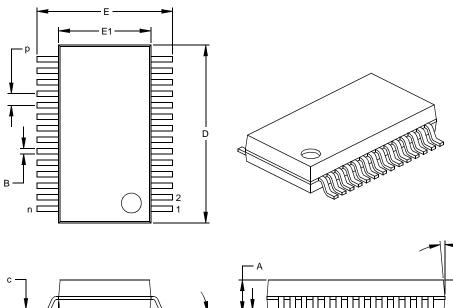

#### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                           | Units            | INCHES* |      |      | MILLIMETERS |       |       |

|---------------------------|------------------|---------|------|------|-------------|-------|-------|

| Dimensio                  | Dimension Limits |         |      | MAX  | MIN         | NOM   | MAX   |

| Number of Pins            | n                |         | 18   |      |             | 18    |       |

| Pitch                     | р                |         | .050 |      |             | 1.27  |       |

| Overall Height            | Α                | .093    | .099 | .104 | 2.36        | 2.50  | 2.64  |

| Molded Package Thickness  | A2               | .088    | .091 | .094 | 2.24        | 2.31  | 2.39  |

| Standoff §                | A1               | .004    | .008 | .012 | 0.10        | 0.20  | 0.30  |

| Overall Width             | Е                | .394    | .407 | .420 | 10.01       | 10.34 | 10.67 |

| Molded Package Width      | E1               | .291    | .295 | .299 | 7.39        | 7.49  | 7.59  |

| Overall Length            | D                | .446    | .454 | .462 | 11.33       | 11.53 | 11.73 |

| Chamfer Distance          | h                | .010    | .020 | .029 | 0.25        | 0.50  | 0.74  |

| Foot Length               | L                | .016    | .033 | .050 | 0.41        | 0.84  | 1.27  |

| Foot Angle                | ¢                | 0       | 4    | 8    | 0           | 4     | 8     |

| Lead Thickness            | С                | .009    | .011 | .012 | 0.23        | 0.27  | 0.30  |

| Lead Width                | В                | .014    | .017 | .020 | 0.36        | 0.42  | 0.51  |

| Mold Draft Angle Top      | α                | 0       | 12   | 15   | 0           | 12    | 15    |

| Mold Draft Angle Bottom β |                  | 0       | 12   | 15   | 0           | 12    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-013

Drawing No. C04-051

#### 28-Lead Ceramic Dual In-line with Window (JW) - 300 mil (CERDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units | INCHES* |       |       | MILLIMETERS |       |       |

|----------------------------|-------|---------|-------|-------|-------------|-------|-------|

| Dimensio                   | MIN   | NOM     | MAX   | MIN   | NOM         | MAX   |       |

| Number of Pins             | n     |         | 28    |       |             | 28    |       |

| Pitch                      |       |         | .100  |       |             | 2.54  |       |

| Top to Seating Plane       | Α     | .170    | .183  | .195  | 4.32        | 4.64  | 4.95  |

| Ceramic Package Height     |       | .155    | .160  | .165  | 3.94        | 4.06  | 4.19  |

| Standoff                   | A1    | .015    | .023  | .030  | 0.38        | 0.57  | 0.76  |

| Shoulder to Shoulder Width | E     | .300    | .313  | .325  | 7.62        | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1    | .285    | .290  | .295  | 7.24        | 7.37  | 7.49  |

| Overall Length             | D     | 1.430   | 1.458 | 1.485 | 36.32       | 37.02 | 37.72 |

| Tip to Seating Plane       | L     | .135    | .140  | .145  | 3.43        | 3.56  | 3.68  |

| Lead Thickness             | С     | .008    | .010  | .012  | 0.20        | 0.25  | 0.30  |

| Upper Lead Width           | B1    | .050    | .058  | .065  | 1.27        | 1.46  | 1.65  |

| Lower Lead Width           | В     | .016    | .019  | .021  | 0.41        | 0.47  | 0.53  |

| Overall Row Spacing §      | eB    | .345    | .385  | .425  | 8.76        | 9.78  | 10.80 |

| Window Width               | W1    | .130    | .140  | .150  | 3.30        | 3.56  | 3.81  |

| Window Length              |       | .290    | .300  | .310  | 7.37        | 7.62  | 7.87  |

Significant Characteristic JEDEC Equivalent: MO-058 Drawing No. C04-080

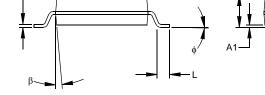

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units      | INCHES |      |      | MILLIMETERS* |        |        |

|---------------------------|------------|--------|------|------|--------------|--------|--------|

| Dimens                    | ion Limits | MIN    | NOM  | MAX  | MIN          | NOM    | MAX    |

| Number of Pins            | n          |        | 28   |      |              | 28     |        |

| Pitch                     | р          |        | .026 |      |              | 0.65   |        |

| Overall Height            | А          | .068   | .073 | .078 | 1.73         | 1.85   | 1.98   |

| Molded Package Thickness  | A2         | .064   | .068 | .072 | 1.63         | 1.73   | 1.83   |

| Standoff §                | A1         | .002   | .006 | .010 | 0.05         | 0.15   | 0.25   |

| Overall Width             | E          | .299   | .309 | .319 | 7.59         | 7.85   | 8.10   |

| Molded Package Width      | E1         | .201   | .207 | .212 | 5.11         | 5.25   | 5.38   |

| Overall Length            | D          | .396   | .402 | .407 | 10.06        | 10.20  | 10.34  |

| Foot Length               | L          | .022   | .030 | .037 | 0.56         | 0.75   | 0.94   |

| Lead Thickness            | С          | .004   | .007 | .010 | 0.10         | 0.18   | 0.25   |

| Foot Angle                | φ          | 0      | 4    | 8    | 0.00         | 101.60 | 203.20 |

| Lead Width                | В          | .010   | .013 | .015 | 0.25         | 0.32   | 0.38   |

| Mold Draft Angle Top      | α          | 0      | 5    | 10   | 0            | 5      | 10     |

| Mold Draft Angle Bottom β |            | 0      | 5    | 10   | 0            | 5      | 10     |

**Controlling Parameter** § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

A2

NOTES: