#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

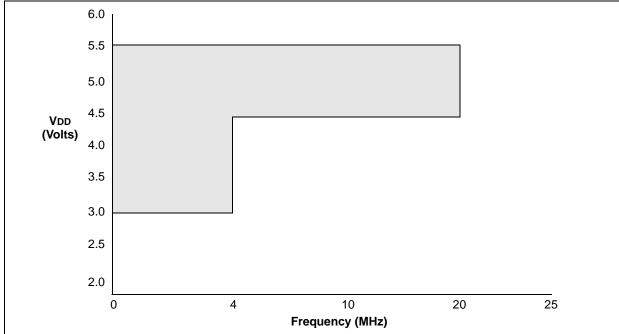

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 13                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

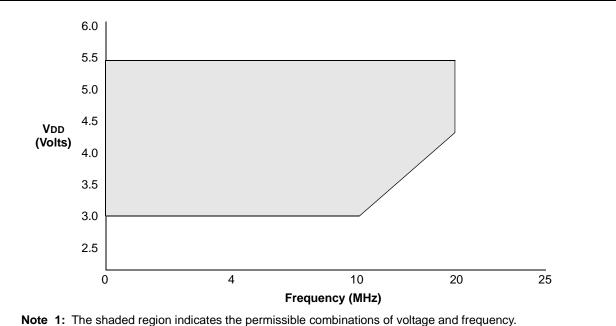

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

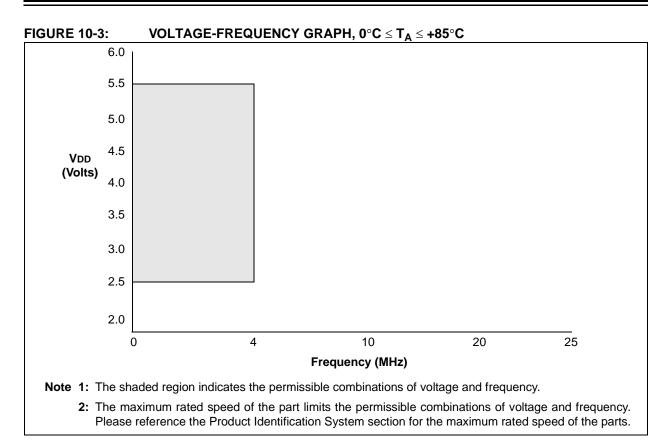

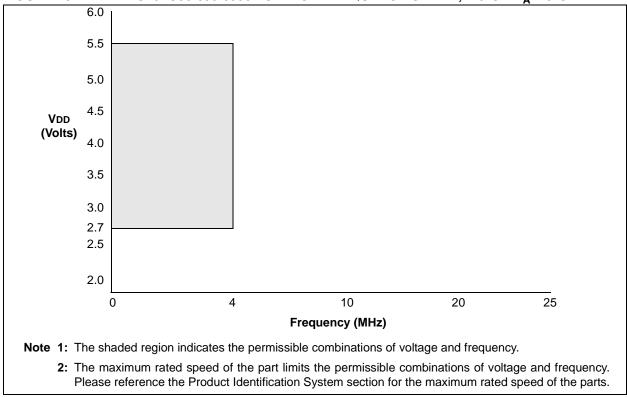

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

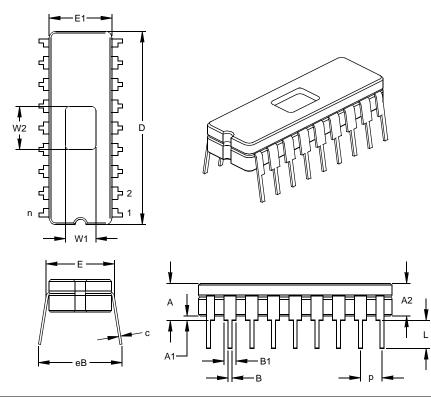

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 18-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558-20-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

|                                          | _   |

|------------------------------------------|-----|

| .0 General Description                   | . 5 |

| .0 PIC16C55X Device Varieties            | . 7 |

| .0       General Description             | . 9 |

| .0 Memory Organization                   | 13  |

|                                          |     |

| 0.0 Special Features of the CPU          | 31  |

| .0 Timer0 Module                         |     |

| 0 Instruction Set Summary                | 53  |

| .0 Development Support                   | 67  |

| 0.0 Electrical Specifications            | 73  |

| 1.0 Packaging Information                | 87  |

| vppendix A: Enhancements                 | 97  |

| ppendix B: Compatibility                 | 97  |

| ndex                                     | 99  |

| Dn-Line Support 1                        | 01  |

| Systems Information and Upgrade Hot Line | 01  |

| Dn-Line Support                          | 02  |

| Product Identification System            | 03  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

| Address                                       | Name                                                    | Bit 7                                          | Bit 6                                                                                            | Bit 5            | Bit 4               | Bit 3            | Bit 2        | Bit 1                        | Bit 0            | Value on<br>POR Reset                            | Detail on<br>Page:       |

|-----------------------------------------------|---------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|--------------|------------------------------|------------------|--------------------------------------------------|--------------------------|

| Bank 0                                        |                                                         |                                                |                                                                                                  |                  |                     |                  |              |                              |                  |                                                  |                          |

| 00h                                           | INDF                                                    |                                                | Addressing this location uses contents of FSR to address data memory (not a<br>hysical register) |                  |                     |                  |              |                              |                  |                                                  | 21                       |

| 01h                                           | TMR0                                                    | Timer0 N                                       | Timer0 Module's Register                                                                         |                  |                     |                  |              |                              |                  |                                                  | 47                       |

| 02h                                           | PCL                                                     | Program                                        | Program Counter's (PC) Least Significant Byte                                                    |                  |                     |                  |              |                              |                  | 0000 0000                                        | 21                       |

| 03h                                           | STATUS                                                  | IRP <sup>(2)</sup>                             | RP1 <sup>(2)</sup>                                                                               | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 04h                                           | FSR                                                     | Indirect of                                    | data memo                                                                                        | ry address       | s pointer           |                  |              |                              |                  | xxxx xxxx                                        | 21                       |

| 05h                                           | PORTA                                                   | -                                              | —                                                                                                | —                | RA4                 | RA3              | RA2          | RA1                          | RA0              | x xxxx                                           | 23                       |

| 06h                                           | PORTB                                                   | RB7                                            | RB6                                                                                              | RB5              | RB4                 | RB3              | RB2          | RB1                          | RB0              | xxxx xxxx                                        | 25                       |

| 07h                                           | PORTC <sup>(4)</sup>                                    | RC7                                            | RC6                                                                                              | RC5              | RC4                 | RC3              | RC2          | RC1                          | RC0              | xxxx xxxx                                        | 27                       |

| 08h                                           | _                                                       | Unimple                                        | mented                                                                                           |                  |                     |                  |              |                              |                  | _                                                |                          |

| 09h                                           | _                                                       | Unimple                                        | mented                                                                                           |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Ah                                           | PCLATH                                                  | _                                              | —                                                                                                |                  | Write but           | fer for upp      | per 5 bits o | of progran                   | n counter        | 0 0000                                           | 21                       |

| 0Bh                                           | INTCON                                                  | GIE                                            | (3)                                                                                              | T0IE             | INTE                | RBIE             | T0IF         | INTF                         | RBIF             | 0000 000x                                        | 19                       |

| 0Ch                                           | —                                                       | Unimple                                        | mented                                                                                           |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Dh-1Eh                                       | —                                                       | Unimple                                        | mented                                                                                           |                  |                     |                  |              |                              |                  | _                                                | —                        |

| 1Fh                                           | —                                                       | Unimple                                        | Unimplemented                                                                                    |                  |                     |                  |              |                              |                  | _                                                | _                        |

| Bank 1                                        |                                                         |                                                |                                                                                                  |                  |                     |                  |              |                              |                  |                                                  |                          |

| 80h                                           | INDF                                                    | Addressi<br>physical                           | ing this loca<br>register)                                                                       | ation uses       | contents            | of FSR to a      | address d    | ata memo                     | ory (not a       | XXXX XXXX                                        | 21                       |

| 81h                                           | OPTION                                                  | RBPU                                           | INTEDG                                                                                           | TOCS             | T0SE                | PSA              | PS2          | PS1                          | PS0              | 1111 1111                                        | 18                       |

| 82h                                           | PCL                                                     | Program                                        | Counter's                                                                                        | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 83h                                           | STATUS                                                  | _                                              | _                                                                                                | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 84h                                           | FSR                                                     |                                                |                                                                                                  | Indirect d       | ata memo            | ry address       | s pointer    |                              |                  | xxxx xxxx                                        | 21                       |

| 85h                                           | TRISA                                                   | -                                              | —                                                                                                | —                | TRISA4              | TRISA3           | TRISA2       | TRISA1                       | TRISA0           | 1 1111                                           | 23                       |

| 86h                                           | TDIOD                                                   |                                                |                                                                                                  |                  |                     |                  | TDIODO       | TDICD4                       |                  |                                                  | 05                       |

| 0011                                          | TRISB                                                   | TRISB7                                         | TRISB6                                                                                           | TRISB5           | TRISB4              | TRISB3           | TRISB2       | TRISB1                       | TRISB0           | 1111 1111                                        | 25                       |

| 87h                                           | TRISB                                                   | TRISB7<br>TRISC7                               | TRISB6<br>TRISC6                                                                                 | TRISB5<br>TRISC5 | TRISB4<br>TRISC4    | TRISB3<br>TRISC3 | TRISB2       | TRISC1                       | TRISB0<br>TRISC0 | 1111 1111<br>1111 1111                           | 25                       |

|                                               |                                                         |                                                | TRISC6                                                                                           |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h                                           |                                                         | TRISC7                                         | TRISC6<br>mented                                                                                 |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h<br>88h                                    |                                                         | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                                 |                  | TRISC4              |                  | TRISC2       | TRISC1                       | TRISC0           |                                                  | 27<br>—                  |

| 87h<br>88h<br>89h                             | TRISC <sup>(4)</sup><br>—<br>—                          | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                                 |                  | TRISC4              | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—                              | 27<br>—<br>—             |

| 87h<br>88h<br>89h<br>8Ah                      | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple                   | TRISC6<br>mented<br>mented<br>(3)                                                                | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh               | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br><br>GIE        | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                      | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch        | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                      | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch<br>8Dh | TRISC <sup>(4)</sup><br>—<br>PCLATH<br>INTCON<br>—<br>— | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>—<br>(3)<br>mented<br>mented                                                 | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1<br>of program<br>INTF | TRISC0           | 1111 1111<br>                                    | 27<br>—<br>21<br>19<br>— |

#### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C55X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved, always maintain these bits clear.

3: Bit 6 of INTCON register is reserved for future use. Always maintain this bit as clear.

4: PIC16C557 only.

#### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

### 5.0 I/O PORTS

The PIC16C554 and PIC16C558 have two ports, PORTA and PORTB. The PIC16C557 has three ports, PORTA, PORTB and PORTC.

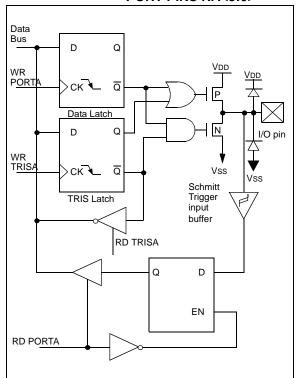

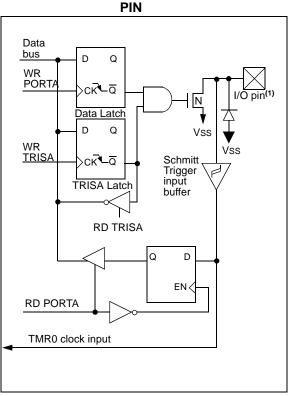

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open-drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Note 1: On RESET, the TRISA register is set to all inputs.

FIGURE 5-1: BLOCK DIAGRAM OF PORT PINS RA<3:0>

#### FIGURE 5-2: BL

BLOCK DIAGRAM OF RA4

## 5.3 PORTC and TRISC Registers<sup>(1)</sup>

PORTC is a 8-bit wide latch. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISC register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISC register puts the contents of the output latch on the selected pin(s).

Reading the PORTC register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch

FIGURE 5-5: BLOCK DIAGRAM OF

#### PORT PINS RC<7:0> Data Bus D Q Vdd WR PORT ск 🔪 Q P Data Latch Q Ν D I/O pin WR T<u>RISC</u> Q ∘ск҇∢\_ Vss Vss TRIS Latch TTL Input Buffer RD TRISC Q D FN. **RD PORTC**

| Name | Bit # | Buffer Type | Function                 |

|------|-------|-------------|--------------------------|

| RC0  | Bit 0 | TTL         | Bi-directional I/O port. |

| RC1  | Bit 1 | TTL         | Bi-directional I/O port. |

| RC2  | Bit 2 | TTL         | Bi-directional I/O port. |

| RC3  | Bit 3 | TTL         | Bi-directional I/O port. |

| RC4  | Bit 4 | TTL         | Bi-directional I/O port. |

| RC5  | Bit 5 | TTL         | Bi-directional I/O port. |

| RC6  | Bit 6 | TTL         | Bi-directional I/O port. |

| RC7  | Bit 7 | TTL         | Bi-directional I/O port. |

Legend: ST = Schmitt Trigger, TTL = TTL input

#### TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC AND TRISC

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 07h     | PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx       | uuuu uuuu                       |

| 87h     | TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged Note 1: PIC16C557 ONLY.

#### 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

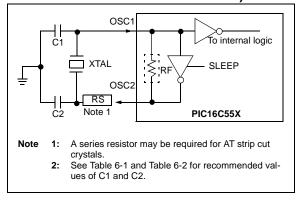

## 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

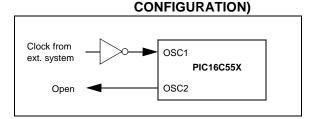

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

#### FIGURE 6-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

FIGURE 6-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

#### TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges                                                                                                                                       |                               |                                         |                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|

| Mode                                                                                                                                         | Freq                          | OSC1(C1)                                | OSC2(C2)                                |  |

| ХТ                                                                                                                                           | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |

| HS                                                                                                                                           | 8.0 MHz<br>16.0 MHz           | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design |                               |                                         |                                         |  |

| of the oscillator but also increases the    |

|---------------------------------------------|

| start-up time. These values are for design  |

| guidance only. Since each resonator has     |

| its own characteristics, the user should    |

| consult with the resonator manufacturer for |

| appropriate values of external compo-       |

| nents.                                      |

| TABLE 6-2: | <b>CAPACITOR SELECTION FOR</b> |

|------------|--------------------------------|

|            | CRYSTAL OSCILLATOR             |

|            | (PRELIMINARY)                  |

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC1(C1)                               | OSC2(C2)                                 |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|--|

| LP      | 32 kHz<br>200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68 - 100 pF<br>15 - 30 pF              | 68 - 100 pF<br>15 - 30 pF                |  |

| XT      | XT 100 kHz 68 -<br>2 MHz 15 -<br>4 MHz 15 -                                                                                                                                                                                                                                                                                                                                                                                                            |                                        | 150 - 200 pF<br>15 - 30 pF<br>15 - 30 pF |  |

| HS      | 8 MHz<br>10 MHz<br>20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 - 30 pF<br>15 - 30 pF<br>15 - 30 pF | 15 - 30 pF<br>15 - 30 pF<br>15 - 30 pF   |  |

| Note 1: | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid over-<br>driving crystals with low-drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>with the crystal manufacturer for appropri-<br>ate values of external components. |                                        |                                          |  |

#### 6.4.5 POWER CONTROL/STATUS REGISTER (PCON)

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET if POR is '0', it will indicate that a Poweron Reset must have occurred (VDD may have gone too low).

#### TABLE 6-3: TIMEOUT IN VARIOUS SITUATIONS

| Oscillator    | Powe              | Wake-up from |           |

|---------------|-------------------|--------------|-----------|

| Configuration | PWRTE = 0         | PWRTE = 1    | SLEEP     |

| XT, HS, LP    | 72 ms + 1024 Tosc | 1024 Tosc    | 1024 Tosc |

| RC            | 72 ms             | _            | —         |

#### TABLE 6-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                    |

|-----|----|----|------------------------------------|

| 0   | 1  | 1  | Power-on Reset                     |

| 0   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0  | u  | WDT Reset                          |

| 1   | 0  | 0  | WDT Wake-up                        |

| 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1  | 0  | MCLR Reset during SLEEP            |

#### 6.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |

#### 6.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

#### 6.11 In-Circuit Serial Programming™

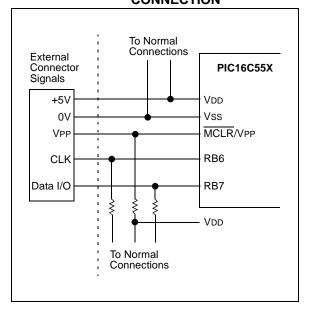

The PIC16C55X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 6-15.

#### FIGURE 6-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 8.0 INSTRUCTION SET SUMMARY

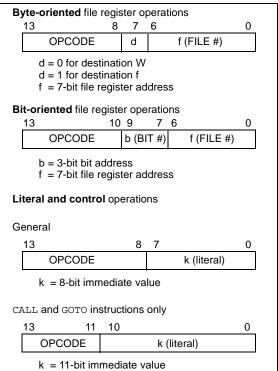

Each PIC16C55X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C55X instruction set summary in Table 8-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 8-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field         | Description                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                                              |

| x             | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It<br>is the recommended form of use for compatibil-<br>ity with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                       |

| label         | Label name                                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                                             |

| то            | Timeout bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                                          |

| [ ]           | Options                                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                                 |

| ∈             | In the set of                                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

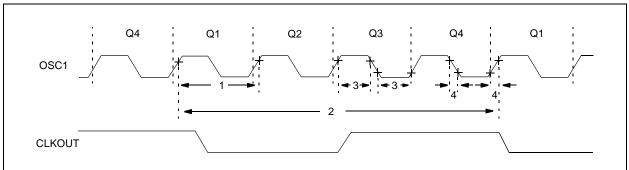

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 8-1 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 8-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

### 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                       |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                       |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |  |  |  |  |

| Words:           | 1                                                                                                                       |  |  |  |  |

| Cycles:          | 1                                                                                                                       |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                      |  |  |  |  |

|                  | W = 0x10                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                       |  |  |  |  |

|                  | W = 0x25                                                                                                                |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |

| ANDLW            | AND Li                                                                                                              | teral wit | h W   |      |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|-----------|-------|------|--|

| Syntax:          | [ label ]                                                                                                           | ANDLW     | / k   |      |  |

| Operands:        | $0 \le k \le 2$                                                                                                     | 255       |       |      |  |

| Operation:       | (W) .AN                                                                                                             | ID. (k) → | • (W) |      |  |

| Status Affected: | Z                                                                                                                   |           |       |      |  |

| Encoding:        | 11                                                                                                                  | 1001      | kkkk  | kkkk |  |

|                  | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |           |       |      |  |

| Words:           | 1                                                                                                                   |           |       |      |  |

| Cycles:          | 1                                                                                                                   |           |       |      |  |

| Example          | ANDLW                                                                                                               | 0x5F      |       |      |  |

|                  | Before I                                                                                                            | nstructio | on    |      |  |

|                  | W = 0xA3                                                                                                            |           |       |      |  |

|                  | After Instruction                                                                                                   |           |       |      |  |

|                  | W                                                                                                                   | =         | 0x03  |      |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                         |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |  |

-

# PIC16C55X

| MOVF             | Move f                                                                                      |                                                                  |                                                                         |                                                    |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------|

| Syntax:          | [ label ]                                                                                   | MOVF                                                             | f,d                                                                     |                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                              | 7                                                                |                                                                         |                                                    |

| Operation:       | $(f) \rightarrow (des$                                                                      | st)                                                              |                                                                         |                                                    |

| Status Affected: | Z                                                                                           |                                                                  |                                                                         |                                                    |

| Encoding:        | 00                                                                                          | 1000                                                             | dfff                                                                    | ffff                                               |

| Description:     | The conte<br>moved to<br>upon the<br>tination is<br>destination<br>= 1 is use<br>since stat | a destina<br>status of<br>W regis<br>on is file r<br>oful to tes | ation dep<br>f d. If d =<br>ter. If d =<br>register f i<br>st a file re | endant<br>0, des-<br>1, the<br>tself. d<br>egister |

| Words:           | 1                                                                                           |                                                                  |                                                                         |                                                    |

| Cycles:          | 1                                                                                           |                                                                  |                                                                         |                                                    |

| Example          | MOVF                                                                                        | FSR,                                                             | 0                                                                       |                                                    |

|                  | After Inst<br>W<br>Z                                                                        |                                                                  | e in FSR I                                                              | register                                           |

| NOP              | No Operation  |      |      |      |

|------------------|---------------|------|------|------|

| Syntax:          | [ label ]     | NOP  |      |      |

| Operands:        | None          |      |      |      |

| Operation:       | No operation  |      |      |      |

| Status Affected: | None          |      |      |      |

| Encoding:        | 00            | 0000 | 0xx0 | 0000 |

| Description:     | No operation. |      |      |      |

| Words:           | 1             |      |      |      |

| Cycles:          | 1             |      |      |      |

| Example          | NOP           |      |      |      |

| MOVWF            | Move W to f                                |  |  |  |

|------------------|--------------------------------------------|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |

| Status Affected: | None                                       |  |  |  |

| Encoding:        | 00 0000 1fff ffff                          |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |

| Words:           | 1                                          |  |  |  |

| Cycles:          | 1                                          |  |  |  |

| Example          | MOVWF OPTION                               |  |  |  |

|                  | Before Instruction                         |  |  |  |

|                  | OPTION = 0xFF                              |  |  |  |

|                  | W = 0x4F                                   |  |  |  |

|                  | After Instruction                          |  |  |  |

|                  | OPTION = 0x4F                              |  |  |  |

|                  | W = 0x4F                                   |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                             |       |      |      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                   |       |      |      |  |

| Operands:        | None                                                                                                                                                                                                                                             |       |      |      |  |

| Operation:       | $(W) \rightarrow O$                                                                                                                                                                                                                              | PTION |      |      |  |

| Status Affected: | None                                                                                                                                                                                                                                             |       |      |      |  |

| Encoding:        | 00                                                                                                                                                                                                                                               | 0000  | 0110 | 0010 |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it. |       |      |      |  |

| Words:           | 1                                                                                                                                                                                                                                                |       |      |      |  |

| Cycles:          | 1                                                                                                                                                                                                                                                |       |      |      |  |

| Example          |                                                                                                                                                                                                                                                  |       |      |      |  |

|                  | To maintain upward compatibility<br>with future PIC MCU products, do<br>not use this instruction.                                                                                                                                                |       |      |      |  |

|                  |                                                                                                                                                                                                                                                  |       |      |      |  |

# PIC16C55X

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                    |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                              |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                           |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                 |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                 |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                            |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                            |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                  |              |      |      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|

| Syntax:          | [ label ]                                                                                                                                               | RETUR        | N    |      |

| Operands:        | None                                                                                                                                                    |              |      |      |

| Operation:       | $TOS \to PC$                                                                                                                                            |              |      |      |

| Status Affected: | None                                                                                                                                                    |              |      |      |

| Encoding:        | 00                                                                                                                                                      | 0000         | 0000 | 1000 |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two-cycle instruction. |              |      |      |

| Words:           | 1                                                                                                                                                       |              |      |      |

| Cycles:          | 2                                                                                                                                                       |              |      |      |

| Example          | RETURN                                                                                                                                                  |              |      |      |

|                  | After Inte<br>PC                                                                                                                                        | rrupt<br>= T | OS   |      |

| RETLW            | Return with Literal in W                                                                                                                                                            | I                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | S                     |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | 0                     |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        | 0                     |

| Status Affected: | None                                                                                                                                                                                | St                    |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   | E                     |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. | D                     |

| Words:           | 1                                                                                                                                                                                   |                       |

| Cycles:          | 2                                                                                                                                                                                   |                       |

| Example          | CALL TABLE;W contains table<br>;offset value<br>• ;W now has table<br>value<br>•                                                                                                    | W<br>C <u>y</u><br>Ex |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>RETLW kn ; End of table                                                                                         |                       |

|                  | Before Instruction                                                                                                                                                                  |                       |

|                  | W = 0x07                                                                                                                                                                            |                       |

|                  | After Instruction                                                                                                                                                                   |                       |

|                  | W = value of k8                                                                                                                                                                     |                       |

| RLF             | Rotate Left f through Carry                                                                                                                                                                                 |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| yntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    |  |  |  |  |  |

| perands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                           |  |  |  |  |  |

| peration:       | See description below                                                                                                                                                                                       |  |  |  |  |  |

| tatus Affected: | С                                                                                                                                                                                                           |  |  |  |  |  |

| ncoding:        | 00 1101 dfff ffff                                                                                                                                                                                           |  |  |  |  |  |

| escription:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |  |  |  |  |  |

| /ords:          | 1                                                                                                                                                                                                           |  |  |  |  |  |

| ycles:          | 1                                                                                                                                                                                                           |  |  |  |  |  |

| xample          | RLF REG1,0                                                                                                                                                                                                  |  |  |  |  |  |

|                 | Before Instruction                                                                                                                                                                                          |  |  |  |  |  |

|                 | <b>REG1</b> = 1110 0110                                                                                                                                                                                     |  |  |  |  |  |

|                 | C = 0                                                                                                                                                                                                       |  |  |  |  |  |

|                 | After Instruction                                                                                                                                                                                           |  |  |  |  |  |