Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558-20-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Special Microcontroller Features:**

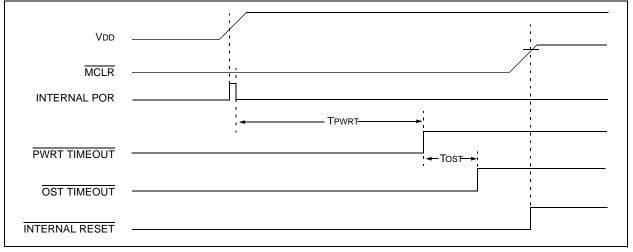

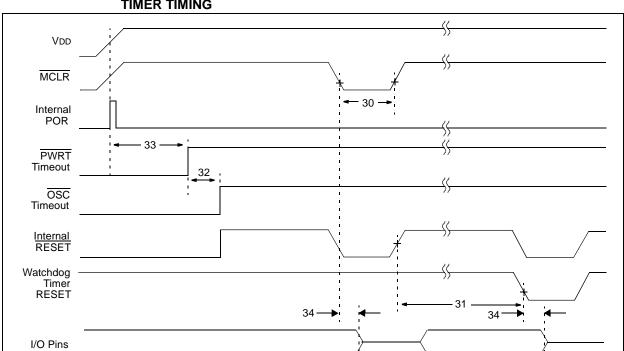

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- Power saving SLEEP mode

- Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

Note: For additional information on enhancements, see Appendix A

### CMOS Technology:

- Low power, high speed CMOS EPROM technology

- Fully static design

- Wide operating voltage range

2.5V to 5.5V

- Commercial, Industrial and Extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical 3.0V, 32 kHz

- < 1.0 μA typical standby current @ 3.0V

### **Device Differences**

| Device    | Voltage Range | Oscillator |

|-----------|---------------|------------|

| PIC16C554 | 2.5 - 5.5     | (Note 1)   |

| PIC16C557 | 2.5 - 5.5     | (Note 1)   |

| PIC16C558 | 2.5 - 5.5     | (Note 1)   |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

### **Table of Contents**

|                                          | _   |

|------------------------------------------|-----|

| .0 General Description                   | . 5 |

| .0 PIC16C55X Device Varieties            | . 7 |

| .0       General Description             | . 9 |

| .0 Memory Organization                   | 13  |

|                                          |     |

| 0.0 Special Features of the CPU          | 31  |

| .0 Timer0 Module                         |     |

| 0 Instruction Set Summary                | 53  |

| .0 Development Support                   | 67  |

| 0.0 Electrical Specifications            | 73  |

| 1.0 Packaging Information                | 87  |

| vppendix A: Enhancements                 | 97  |

| ppendix B: Compatibility                 | 97  |

| ndex                                     | 99  |

| Dn-Line Support 1                        | 01  |

| Systems Information and Upgrade Hot Line | 01  |

| Dn-Line Support                          | 02  |

| Product Identification System            | 03  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

# 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

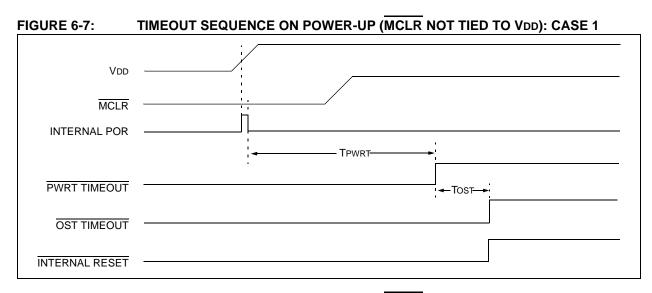

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

# 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### 6.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a pre-packaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

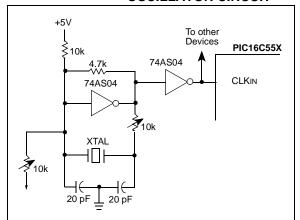

Figure 6-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 6-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

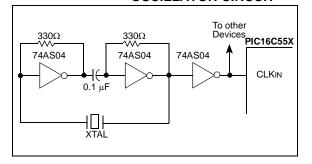

Figure 6-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The  $330\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 6-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

# 6.2.4 RC OSCILLATOR

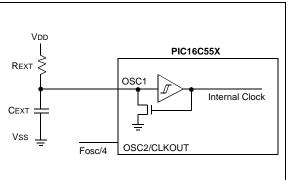

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 6-5 shows how the R/C combination is connected to the PIC16C55X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 6-5: RC OSCILLATOR MODE

## TABLE 8-2: PIC16C55X INSTRUCTION SET

| Mnemonic, Description C<br>Operands |      | 14-Bit Opcode                |         | e Status |      | Neter |      |             |       |

|-------------------------------------|------|------------------------------|---------|----------|------|-------|------|-------------|-------|

|                                     |      | Description                  |         | MSb      |      |       | LSb  | Affected    | Notes |

|                                     |      | BYTE-ORIENTED FILE REGIS     | STER OF | PERAT    | IONS |       |      |             |       |

| ADDWF                               | f, d | Add W and f                  | 1       | 00       | 0111 | dfff  | ffff | C,DC,Z      | 1,2   |

| ANDWF                               | f, d | AND W with f                 | 1       | 00       | 0101 | dfff  | ffff | Z           | 1,2   |

| CLRF                                | f    | Clear f                      | 1       | 00       | 0001 | lfff  | ffff | Z           | 2     |

| CLRW                                | -    | Clear W                      | 1       | 00       | 0001 | 0000  | 0011 | Z           |       |

| COMF                                | f, d | Complement f                 | 1       | 00       | 1001 | dfff  | ffff | Z           | 1,2   |

| DECF                                | f, d | Decrement f                  | 1       | 00       | 0011 | dfff  | ffff | Z           | 1,2   |

| DECFSZ                              | f, d | Decrement f, Skip if 0       | 1(2)    | 00       | 1011 | dfff  | ffff |             | 1,2,3 |

| INCF                                | f, d | Increment f                  | 1       | 00       | 1010 | dfff  | ffff | Z           | 1,2   |

| INCFSZ                              | f, d | Increment f, Skip if 0       | 1(2)    | 00       | 1111 | dfff  | ffff |             | 1,2,3 |

| IORWF                               | f, d | Inclusive OR W with f        | 1       | 00       | 0100 | dfff  | ffff | Z           | 1,2   |

| MOVF                                | f, d | Move f                       | 1       | 00       | 1000 |       | ffff | z           | 1,2   |

| MOVWF                               | f    | Move W to f                  | 1       | 00       | 0000 |       | ffff | _           | - ,=  |

| NOP                                 | -    | No Operation                 | 1       | 00       | 0000 | 0xx0  | 0000 |             |       |

| RLF                                 | f, d | Rotate Left f through Carry  | 1       | 00       |      | dfff  |      | С           | 1,2   |

| RRF                                 | f, d | Rotate Right f through Carry | 1       | 00       | 1100 | dfff  |      | Č           | 1,2   |

| SUBWF                               | f, d | Subtract W from f            | 1       | 00       | 0010 | dfff  |      | C,DC,Z      | 1,2   |

| SWAPF                               | f, d | Swap nibbles in f            | 1       | 00       | 1110 |       | ffff | 0,20,2      | 1,2   |

| XORWF                               | f, d | Exclusive OR W with f        | 1       | 00       | 0110 |       | ffff | Z           | 1,2   |

|                                     |      | BIT-ORIENTED FILE REGIST     |         | RATION   | IS   |       |      |             |       |

| BCF                                 | f, b | Bit Clear f                  | 1       | 01       | 00bb | bfff  | ffff |             | 1,2   |

| BSF                                 | f, b | Bit Set f                    | 1       | 01       | 01bb | bfff  | ffff |             | 1,2   |

| BTFSC                               | f, b | Bit Test f, Skip if Clear    | 1(2)    | 01       | 10bb | bfff  | ffff |             | 3     |

| BTFSS                               | f, b | Bit Test f, Skip if Set      | 1(2)    | 01       | 11bb | bfff  | ffff |             | 3     |

|                                     |      | LITERAL AND CONTROL          | OPERAT  | IONS     |      |       |      |             |       |

| ADDLW                               | k    | Add literal and W            | 1       | 11       | 111x | kkkk  | kkkk | C,DC,Z      |       |

| ANDLW                               | k    | AND literal with W           | 1       | 11       | 1001 | kkkk  | kkkk | Z           |       |

| CALL                                | k    | Call subroutine              | 2       | 10       | 0kkk | kkkk  | kkkk |             |       |

| CLRWDT                              | -    | Clear Watchdog Timer         | 1       | 00       | 0000 | 0110  | 0100 | TO,PD       |       |

| GOTO                                | k    | Go to address                | 2       | 10       | 1kkk | kkkk  | kkkk | ,           |       |

| IORLW                               | k    | Inclusive OR literal with W  | 1       | 11       | 1000 | kkkk  | kkkk | Z           |       |

| MOVLW                               | k    | Move literal to W            | 1       | 11       |      | kkkk  |      |             |       |

| RETFIE                              | -    | Return from interrupt        | 2       | 00       | 0000 | 0000  | 1001 |             |       |

| RETLW                               | k    | Return with literal in W     | 2       | 11       |      | kkkk  |      |             |       |

| RETURN                              | -    | Return from Subroutine       | 2       | 00       | 0000 | 0000  | 1000 |             |       |

| SLEEP                               | -    | Go into Standby mode         | 1       | 00       | 0000 | 0110  | 0011 | TO,PD       |       |

| SUBLW                               | k    | Subtract W from literal      | 1       | 11       |      | kkkk  |      | C,DC,Z      |       |

| XORLW                               | k    | Exclusive OR literal with W  | 1       | 11       |      | kkkk  |      | 0,00,2<br>Z |       |

|                                     |      |                              | -       |          |      |       |      | <u>ک</u>    |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |

| Operands:        | $0 \le k \le 255$                                                                                                       |

| Operation:       | $(W) + k \to (W)$                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |

| Words:           | 1                                                                                                                       |

| Cycles:          | 1                                                                                                                       |

| Example          | ADDLW 0x15                                                                                                              |

|                  | Before Instruction                                                                                                      |

|                  | W = 0x10                                                                                                                |

|                  | After Instruction                                                                                                       |

|                  | W = 0x25                                                                                                                |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |

| ANDLW            | AND Li                                  | teral wit  | h W            |          |

|------------------|-----------------------------------------|------------|----------------|----------|

| Syntax:          | [ label ]                               | ANDLW      | / k            |          |

| Operands:        | $0 \le k \le 2$                         | 255        |                |          |

| Operation:       | (W) .AN                                 | ID. (k) →  | • (W)          |          |

| Status Affected: | Z                                       |            |                |          |

| Encoding:        | 11                                      | 1001       | kkkk           | kkkk     |

|                  | The conter<br>AND'ed wi<br>result is pl | th the eig | ht bit literal | 'k'. The |

| Words:           | 1                                       |            |                |          |

| Cycles:          | 1                                       |            |                |          |

| Example          | ANDLW                                   | 0x5F       |                |          |

|                  | Before I                                | nstructio  | on             |          |

|                  | W                                       | =          | 0xA3           |          |

|                  | After Ins                               | struction  |                |          |

|                  | W                                       | =          | 0x03           |          |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                         |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |

-

# PIC16C55X

| BCF              | Bit Clea                           | ar f          |            |          |

|------------------|------------------------------------|---------------|------------|----------|

| Syntax:          | [ label ]                          | BCF 1         | f,b        |          |

| Operands:        | $0 \le f \le 1$<br>$0 \le b \le 1$ |               |            |          |

| Operation:       | $0 \rightarrow (f < $              | b>)           |            |          |

| Status Affected: | None                               |               |            |          |

| Encoding:        | 01                                 | 00bb          | bfff       | ffff     |

| Description:     | Bit 'b' in re                      | gister 'f' is | s cleared. |          |

| Words:           | 1                                  |               |            |          |

| Cycles:          | 1                                  |               |            |          |

| Example          | BCF                                | FLAG_F        | REG, 7     |          |

|                  | After Inst                         | G_REG         |            | C7<br>47 |

|  | Bit | Set | f |

|--|-----|-----|---|

|--|-----|-----|---|

BSF

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |               |        |      |

|------------------|---------------------------------------------------------------------|---------------|--------|------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |               |        |      |

| Operation:       | $1 \rightarrow (f < b >)$                                           |               |        |      |

| Status Affected: | None                                                                |               |        |      |

| Encoding:        | 01                                                                  | 01bb          | bfff   | ffff |

| Description:     | Bit 'b' in re                                                       | gister 'f' is | s set. |      |

| Words:           | 1                                                                   |               |        |      |

| Cycles:          | 1                                                                   |               |        |      |

| Example          | BSF                                                                 | FLAG_F        | REG, 7 | ,    |

|                  | Before In<br>FLA<br>After Inst                                      | G_REG         |        | 0A   |

|                  | FLAG                                                                | G_REG         | = 0x   | 8A   |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                 |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                     |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                     |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                                 |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                    |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                       |  |  |

| Description:     | If bit 'b' in register 'f' is '0' then the next<br>instruction is skipped. If bit 'b' is '0' then<br>the next instruction fetched during the<br>current instruction execution is dis-<br>carded, and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                       |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                    |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•                                                                                                                                                                                                        |  |  |

|                  | Before Instruction                                                                                                                                                                                                                                                      |  |  |

|                  | PC = address HERE                                                                                                                                                                                                                                                       |  |  |

|                  | After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                                       |  |  |

|                  | PC = address FALSE                                                                                                                                                                                                                                                      |  |  |

# PIC16C55X

| CLRW             | Clear W                              |                                                                       |      |      |  |  |  |  |  |  |

|------------------|--------------------------------------|-----------------------------------------------------------------------|------|------|--|--|--|--|--|--|

| Syntax:          | [label] CLRW                         |                                                                       |      |      |  |  |  |  |  |  |

| Operands:        | None                                 |                                                                       |      |      |  |  |  |  |  |  |

| Operation:       | $00h \rightarrow (V 1 \rightarrow Z$ | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |      |      |  |  |  |  |  |  |

| Status Affected: | Z                                    |                                                                       |      |      |  |  |  |  |  |  |

| Encoding:        | 00                                   | 0001                                                                  | 0000 | 0011 |  |  |  |  |  |  |

| Description:     | W register set.                      | W register is cleared. Zero bit (Z) is set.                           |      |      |  |  |  |  |  |  |

| Words:           | 1                                    |                                                                       |      |      |  |  |  |  |  |  |

| Cycles:          | 1                                    |                                                                       |      |      |  |  |  |  |  |  |

| Example          | CLRW                                 |                                                                       |      |      |  |  |  |  |  |  |

|                  | Before In                            | structio                                                              | n    |      |  |  |  |  |  |  |

|                  | W = 0x5A                             |                                                                       |      |      |  |  |  |  |  |  |

|                  | After Inst                           | ruction                                                               |      |      |  |  |  |  |  |  |

|                  | W                                    | =                                                                     | 0x00 |      |  |  |  |  |  |  |

|                  | Z                                    | =                                                                     | 1    |      |  |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                          |                    |      |      |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|--|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                             | [ label ] COMF f,d |      |      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                        | 7                  |      |      |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (des$                                                                                                                     | st)                |      |      |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                     |                    |      |      |  |  |  |  |  |

| Encoding:        | 00                                                                                                                                                    | 1001               | dfff | ffff |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the result is<br>stored in W. If 'd' is 1 the result is<br>stored back in register 'f'. |                    |      |      |  |  |  |  |  |

| Words:           | 1                                                                                                                                                     |                    |      |      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                     |                    |      |      |  |  |  |  |  |

| Example          | COMF                                                                                                                                                  | REG1,0             | )    |      |  |  |  |  |  |

|                  | Before In                                                                                                                                             | struction          |      |      |  |  |  |  |  |

|                  | REG1 = 0x13                                                                                                                                           |                    |      |      |  |  |  |  |  |

|                  | After Inst                                                                                                                                            | ruction            |      |      |  |  |  |  |  |

|                  | REG                                                                                                                                                   | 1 =                | 0x13 |      |  |  |  |  |  |

|                  | W                                                                                                                                                     | W = 0xEC           |      |      |  |  |  |  |  |

| Clear Watchdog Timer                                                                                                                                                  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [label] CLRWDT                                                                                                                                                        |  |  |  |  |  |  |

| None                                                                                                                                                                  |  |  |  |  |  |  |

| $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WDT} \text{ prescaler,} \\ 1 \rightarrow \underline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |  |  |

| TO, PD                                                                                                                                                                |  |  |  |  |  |  |

| 00 0000 0110 0100                                                                                                                                                     |  |  |  |  |  |  |

| CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits TO<br>and PD are set.                                        |  |  |  |  |  |  |

| 1                                                                                                                                                                     |  |  |  |  |  |  |

| 1                                                                                                                                                                     |  |  |  |  |  |  |

| CLRWDT                                                                                                                                                                |  |  |  |  |  |  |

| Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = $1$<br>PD = $1$                                     |  |  |  |  |  |  |

|                                                                                                                                                                       |  |  |  |  |  |  |

.....

| DECF             | Decrement f                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                   |  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                             |  |  |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                           |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                           |  |  |  |  |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                           |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                           |  |  |  |  |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                                 |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                       |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                             |  |  |  |  |  |  |  |  |

# PIC16C55X

| MOVF             | Move f                                                                                                                                                                                                                                                                            |      |      |      |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                                         | MOVF | f,d  |      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                        |      |      |      |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |      |      |      |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |      |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                                                | 1000 | dfff | ffff |  |  |  |

| Description:     | The contents of register f is<br>moved to a destination dependant<br>upon the status of d. If $d = 0$ , des-<br>tination is W register. If $d = 1$ , the<br>destination is file register f itself. d<br>= 1 is useful to test a file register<br>since status flag Z is affected. |      |      |      |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                 |      |      |      |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                 |      |      |      |  |  |  |

| Example          | MOVF                                                                                                                                                                                                                                                                              | FSR, | 0    |      |  |  |  |

|                  | After Instruction<br>W = value in FSR registe<br>Z = 1                                                                                                                                                                                                                            |      |      |      |  |  |  |

| NOP              | No Operation |      |      |      |  |  |  |  |

|------------------|--------------|------|------|------|--|--|--|--|

| Syntax:          | [ label ]    | NOP  |      |      |  |  |  |  |

| Operands:        | None         |      |      |      |  |  |  |  |

| Operation:       | No operation |      |      |      |  |  |  |  |

| Status Affected: | None         |      |      |      |  |  |  |  |

| Encoding:        | 00           | 0000 | 0xx0 | 0000 |  |  |  |  |

| Description:     | No operat    | ion. |      |      |  |  |  |  |

| Words:           | 1            |      |      |      |  |  |  |  |

| Cycles:          | 1            |      |      |      |  |  |  |  |

| Example          | NOP          |      |      |      |  |  |  |  |

| MOVWF            | Move W to f                                |  |  |  |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 lfff ffff                          |  |  |  |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                          |  |  |  |  |  |  |  |

| Cycles:          | 1                                          |  |  |  |  |  |  |  |

| Example          | MOVWF OPTION                               |  |  |  |  |  |  |  |

|                  | Before Instruction                         |  |  |  |  |  |  |  |

|                  | OPTION = 0xFF                              |  |  |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |  |  |

|                  | After Instruction                          |  |  |  |  |  |  |  |

|                  | OPTION = 0x4F                              |  |  |  |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                             |       |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|--|

| Syntax:          | [label] OPTION                                                                                                                                                                                                                                   |       |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                             |       |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow O$                                                                                                                                                                                                                              | PTION |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                             |       |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                                                                                |       |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it. |       |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                |       |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                |       |  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                                                                                  |       |  |  |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC MCU products, do<br>not use this instruction.                                                                                                                                                |       |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                  |       |  |  |  |  |  |  |  |

# 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Characteristics |      |                                               |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |        |                                                                                           |  |

|--------------------|------|-----------------------------------------------|------------|------------------------------------------------------|------------|--------|-------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym  | Characteristic                                | Min        | Conditions                                           |            |        |                                                                                           |  |

|                    | Vdd  | Supply Voltage                                |            |                                                      |            |        |                                                                                           |  |

| D001               |      | 16LC55X                                       | 3.0<br>2.5 | _                                                    | 5.5<br>5.5 | V      | XT and RC osc configuration<br>LP osc configuration                                       |  |

| D001<br>D001A      |      | 16C55X                                        | 3.0<br>4.5 |                                                      | 5.5<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                                   |  |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —          | 1.5*                                                 | —          | V      | Device in SLEEP mode                                                                      |  |

| D003               | VPOR | VDD Start Voltage to<br>ensure Power-on Reset | —          | Vss                                                  | —          | V      | See Section 6.4, Power-on Reset for details                                               |  |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _                                                    | —          | V/ms   | See Section 6.4, Power-on Reset for details                                               |  |

|                    | Idd  | Supply Current <sup>(2)</sup>                 |            |                                                      |            |        |                                                                                           |  |

| D010               |      | 16LC55X                                       | _          | 1.4                                                  | 2.5        | mA     | XT and RC osc configuration<br>Fosc = 2.0 MHz, VDD = 3.0V, WDT<br>disabled <sup>(4)</sup> |  |

| D010A              |      |                                               | _          | 26                                                   | 53         | μA     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT<br>disabled                        |  |

| D010               |      | 16C55X                                        | _          | 1.8                                                  | 3.3        | mA     | XT and RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V,<br>WDT disabled <sup>(4)</sup>   |  |

| D010A              |      |                                               | _          | 35                                                   | 70         | μΑ     | LP osc configuration,<br>PIC16C55X-04 only<br>Fosc = 32 kHz, VDD = 4.0V,<br>WDT disabled  |  |

| D013               |      |                                               | —          | 9.0                                                  | 20         | mA     | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V,<br>WDT disabled                        |  |

These parameters are characterized but not tested.

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

<u>OSC1</u> = external square wave, from rail to rail; all I/O pins configured as input, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as input and tied to VDD or Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### **FIGURE 10-8:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### **TABLE 10-3**: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                  | Min    | Тур†         | Max  | Units | Conditions                |

|--------------|----------|-------------------------------------------------|--------|--------------|------|-------|---------------------------|

| 30           | TmcL     | MCLR Pulse Width (low)                          | 2000   |              | —    | ns    | -40° to +85°C             |

| 31           | Twdt     | Watchdog Timer Timeout Period<br>(No Prescaler) | 7*     | 18           | 33*  | ms    | VDD = 5.0V, -40° to +85°C |

| 32           | Tost     | Oscillation Start-up Timer Period               | —      | 1024<br>Tosc | —    | —     | Tosc = OSC1 period        |

| 33           | Tpwrt    | Power-up Timer Period                           | 28*    | 72           | 132* | ms    | VDD = 5.0V, -40° to +85°C |

| 34           | Tioz     | I/O hi-impedance from MCLR low                  |        | —            | 2.0* | μS    |                           |

| *            | These na | arameters are characterized but not             | tested |              |      |       |                           |

These parameters are characterized but not tested.

Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

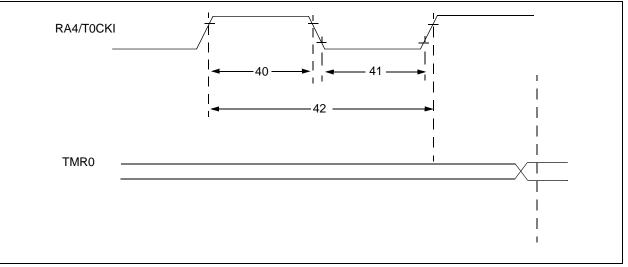

# TABLE 10-4: TIMER0 CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Max | Units | Conditions                            |

|--------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 TCY + 20*          | —    | _   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | _   | ns    |                                       |

| 41           | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 TCY + 20*          | _    | _   | ns    |                                       |

|              |      |                        | With Prescaler | 10*                    | _    | _   | ns    |                                       |

| 42           | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N |      | _   | ns    | N = prescale value<br>(1, 2, 4,, 256) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

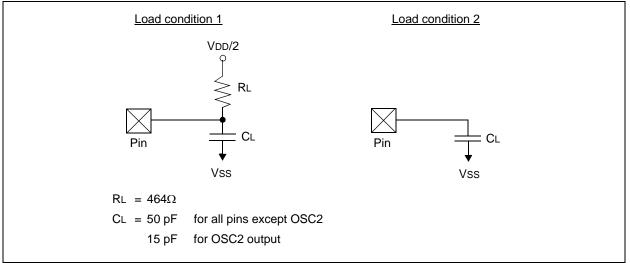

# FIGURE 10-10: LOAD CONDITIONS

© 1996-2013 Microchip Technology Inc.

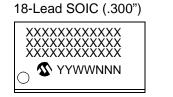

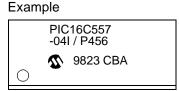

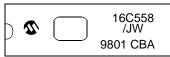

# Package Marking Information (Cont'd)

### Example PIC16C558 -04I / S0218 S0218 9818 CDK

$\cap$

##

### 18-Lead CERDIP Windowed

### Example

### 28-Lead CERDIP Windowed

Example

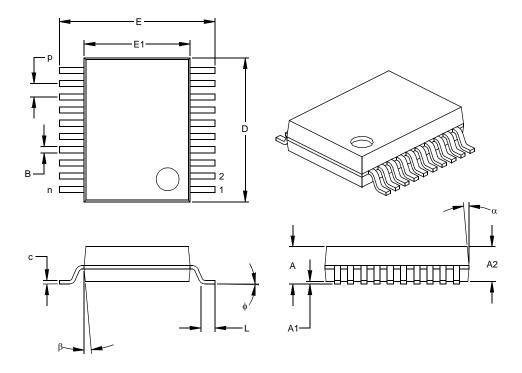

### 20-Lead Plastic Shrink Small Outline (SS) – 209 mil, 5.30 mm (SSOP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units INCHES*            |          |      |      |      | N    | IILLIMETERS |        |

|--------------------------|----------|------|------|------|------|-------------|--------|

| Dimensio                 | n Limits | MIN  | NOM  | MAX  | MIN  | NOM         | MAX    |

| Number of Pins           | n        |      | 20   |      |      | 20          |        |

| Pitch                    | р        |      | .026 |      |      | 0.65        |        |

| Overall Height           | А        | .068 | .073 | .078 | 1.73 | 1.85        | 1.98   |

| Molded Package Thickness | A2       | .064 | .068 | .072 | 1.63 | 1.73        | 1.83   |

| Standoff §               | A1       | .002 | .006 | .010 | 0.05 | 0.15        | 0.25   |

| Overall Width            | E        | .299 | .309 | .322 | 7.59 | 7.85        | 8.18   |

| Molded Package Width     | E1       | .201 | .207 | .212 | 5.11 | 5.25        | 5.38   |

| Overall Length           | D        | .278 | .284 | .289 | 7.06 | 7.20        | 7.34   |

| Foot Length              | L        | .022 | .030 | .037 | 0.56 | 0.75        | 0.94   |

| Lead Thickness           | С        | .004 | .007 | .010 | 0.10 | 0.18        | 0.25   |

| Foot Angle               | ø        | 0    | 4    | 8    | 0.00 | 101.60      | 203.20 |

| Lead Width               | В        | .010 | .013 | .015 | 0.25 | 0.32        | 0.38   |

| Mold Draft Angle Top     | α        | 0    | 5    | 10   | 0    | 5           | 10     |

| Mold Draft Angle Bottom  | β        | 0    | 5    | 10   | 0    | 5           | 10     |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MO-150 Drawing No. C04-072

© 1996-2013 Microchip Technology Inc.

NOTES:

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                   | x <u>xx</u> xxx                                                                                                               | Examples:                                                                                                                                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device To         | emperature Package Pattern<br>Range                                                                                           | a) PIC17C756–16L Commercial Temp.,<br>PLCC package, 16 MHz,<br>normal VDD limits                                                                         |

| Device            | PIC17C756: Standard VDD range<br>PIC17C756T: (Tape and Reel)<br>PIC17LC756: Extended VDD range                                | <ul> <li>b) PIC17LC756–08/PT Commercial Temp.,<br/>TQFP package, 8MHz,<br/>extended VDD limits</li> <li>c) PIC17C756–33I/PT Industrial Temp.,</li> </ul> |

| Temperature Range | $\begin{array}{rcl} - & = & 0^{\circ}C \text{ to } +70^{\circ}C \\ I & = & -40^{\circ}C \text{ to } +85^{\circ}C \end{array}$ | TQFP package, 33 MHz,<br>normal VDD limits                                                                                                               |

| Package           | CL = Windowed LCC<br>PT = TQFP<br>L = PLCC                                                                                    |                                                                                                                                                          |

| Pattern           | QTP, SQTP, ROM Code (factory specified) or<br>Special Requirements. Blank for OTP and<br>Windowed devices.                    |                                                                                                                                                          |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

# Sales and Support

### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)

NOTES:

NOTES: