Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558-20i-p |

|                            |                                                                           |

## **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- · Power saving SLEEP mode

- · Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

Note: For additional information on enhancements, see Appendix A

## **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- · Fully static design

- Wide operating voltage range

- 2.5V to 5.5V

- Commercial, Industrial and Extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical 3.0V, 32 kHz

- < 1.0  $\mu$ A typical standby current @ 3.0V

## **Device Differences**

| Device    | Voltage Range | Oscillator |

|-----------|---------------|------------|

| PIC16C554 | 2.5 - 5.5     | (Note 1)   |

| PIC16C557 | 2.5 - 5.5     | (Note 1)   |

| PIC16C558 | 2.5 - 5.5     | (Note 1)   |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

#### 2.0 PIC16C55X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C55X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART® and PROMATE® programmers both support programming of the PIC16C55X.

# 2.2 One-Time Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 Serialized Quick-Turnaround Production (SQTPsm) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

#### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C55X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C55X uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently from 8-bit wide data words. Instruction opcodes are 14-bit wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a singlecycle (200 ns @ 20 MHz) except for program branches. The table below lists the memory (EPROM and RAM).

| Device    | Program<br>Memory<br>(EPROM) | Data<br>Memor<br>(RAM) |

|-----------|------------------------------|------------------------|

| PIC16C554 | 512                          | 80                     |

| PIC16C557 | 2 K                          | 128                    |

| PIC16C558 | 2 K                          | 128                    |

The PIC16C554 addresses 512 x 14 on-chip program memory. The PIC16C557 and PIC16C558 addresses 2 K x 14 program memory. All program memory is internal.

The PIC16C55X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped into the data memory. The PIC16C55X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C55X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C55X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the <u>STATUS</u> register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

FIGURE 4-3: DATA MEMORY MAP FOR THE PIC16C554

|                                                                                     |                     | PIC16C554           |                 |  |  |

|-------------------------------------------------------------------------------------|---------------------|---------------------|-----------------|--|--|

| File<br>Address                                                                     | 3                   |                     | File<br>Address |  |  |

| 00h                                                                                 | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h                                                                                 | TMR0                | OPTION              | 81h             |  |  |

| 02h                                                                                 | PCL                 | PCL                 | 82h             |  |  |

| 03h                                                                                 | STATUS              | STATUS              | 83h             |  |  |

| 04h                                                                                 | FSR                 | FSR                 | 84h             |  |  |

| 05h                                                                                 | PORTA               | TRISA               | 85h             |  |  |

| 06h                                                                                 | PORTB               | TRISB               | 86h             |  |  |

| 07h                                                                                 |                     |                     | 87h             |  |  |

| 08h                                                                                 |                     |                     | 88h             |  |  |

| 09h                                                                                 |                     |                     | 89h             |  |  |

| 0Ah                                                                                 | PCLATH              | PCLATH              | 8Ah             |  |  |

| 0Bh                                                                                 | INTCON              | INTCON              | 8Bh             |  |  |

| 0Ch                                                                                 |                     |                     | 8Ch             |  |  |

| 0Dh                                                                                 |                     |                     | 8Dh             |  |  |

| 0Eh                                                                                 |                     | PCON                | 8Eh             |  |  |

| 0Fh                                                                                 |                     |                     | 8Fh             |  |  |

| 10h                                                                                 |                     |                     | 90h             |  |  |

| 11h                                                                                 |                     |                     | 91h             |  |  |

| 12h                                                                                 |                     |                     | 92h             |  |  |

| 13h                                                                                 |                     |                     | 93h             |  |  |

| 14h                                                                                 |                     |                     | 94h             |  |  |

| 15h                                                                                 |                     |                     | 95h             |  |  |

| 16h                                                                                 |                     |                     | 96h             |  |  |

| 17h                                                                                 |                     |                     | 97h             |  |  |

| 18h                                                                                 |                     |                     | 98h             |  |  |

| 19h                                                                                 |                     |                     | 99h             |  |  |

| 1Ah                                                                                 |                     |                     | 9Ah             |  |  |

| 1Bh                                                                                 |                     |                     | 9Bh             |  |  |

| 1Ch                                                                                 |                     |                     | 9Ch             |  |  |

| 1Dh                                                                                 |                     |                     | 9Dh             |  |  |

| 1Eh                                                                                 |                     |                     | 9Eh             |  |  |

| 1Fh                                                                                 |                     |                     | 9Fh             |  |  |

| 20h                                                                                 |                     |                     | A0h             |  |  |

|                                                                                     | General             |                     | 7.011           |  |  |

|                                                                                     | Purpose<br>Register |                     |                 |  |  |

| 6Fh                                                                                 | rtogistei           |                     |                 |  |  |

| 70h                                                                                 |                     |                     |                 |  |  |

|                                                                                     |                     |                     |                 |  |  |

| '                                                                                   |                     |                     | 7               |  |  |

|                                                                                     |                     |                     |                 |  |  |

| 7Fh                                                                                 |                     |                     | FFh             |  |  |

| ''''                                                                                | Bank 0              | Bank 1              |                 |  |  |

| Unimplemented data memory locations, read as '0'.  Note 1: Not a physical register. |                     |                     |                 |  |  |

FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C557

| File<br>Address                                   | <b>.</b>            |                     | File<br>Address |  |  |

|---------------------------------------------------|---------------------|---------------------|-----------------|--|--|

| 00h                                               | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h                                               | TMR0                | OPTION              | 81h             |  |  |

| 02h                                               | PCL                 | PCL                 | 82h             |  |  |

| 03h                                               | STATUS              | STATUS              | 83h             |  |  |

| 04h                                               | FSR                 | FSR                 | 84h             |  |  |

| 05h                                               | PORTA               | TRISA               | 85h             |  |  |

| 06h                                               | PORTB               | TRISB               | 86h             |  |  |

| 07h                                               | PORTC               | TRISC               | 87h             |  |  |

| 08h                                               |                     |                     | 88h             |  |  |

| 09h                                               |                     |                     | 89h             |  |  |

| 0Ah                                               | PCLATH              | PCLATH              | 8Ah             |  |  |

| 0Bh                                               | INTCON              | INTCON              | 8Bh             |  |  |

| 0Ch                                               |                     |                     | 8Ch             |  |  |

| 0Dh                                               |                     |                     | 8Dh             |  |  |

| 0Eh                                               |                     | PCON                | 8Eh             |  |  |

| 0Fh                                               |                     |                     | 8Fh             |  |  |

| 10h                                               |                     |                     | 90h             |  |  |

| 11h                                               |                     |                     | 91h             |  |  |

| 12h                                               |                     |                     | 92h             |  |  |

| 13h                                               |                     |                     | 93h             |  |  |

| 14h                                               |                     |                     | 94h             |  |  |

| 15h                                               |                     |                     | 95h             |  |  |

| 16h                                               |                     |                     | 96h             |  |  |

| 17h                                               |                     |                     | 97h             |  |  |

| 18h                                               |                     |                     | 98h             |  |  |

| 19h                                               |                     |                     | 99h             |  |  |

| 1Ah                                               |                     |                     | 9Ah             |  |  |

| 1Bh                                               |                     |                     | 9Bh             |  |  |

| 1Ch                                               |                     |                     | 9Ch             |  |  |

| 1Dh                                               |                     |                     | 9Dh             |  |  |

| 1Eh                                               |                     |                     | 9Eh             |  |  |

| 1Fh                                               |                     |                     | 9Fh             |  |  |

| 20h                                               |                     |                     | _               |  |  |

| 2011                                              | General             | General             | A0h             |  |  |

|                                                   | Purpose             | Purpose             |                 |  |  |

|                                                   | Register            | Register            | BFh             |  |  |

|                                                   |                     |                     | C0h             |  |  |

|                                                   |                     |                     |                 |  |  |

|                                                   |                     |                     | ]               |  |  |

|                                                   |                     |                     | 7               |  |  |

|                                                   |                     |                     | <sub>==</sub> . |  |  |

| 7Fh <sup>L</sup>                                  | Bank 0              | Bank 1              | J FFh           |  |  |

| <b>—</b>                                          |                     |                     |                 |  |  |

| Unimplemented data memory locations, read as '0'. |                     |                     |                 |  |  |

| Note 1:                                           | Not a physical reg  | ister.              |                 |  |  |

|                                                   |                     |                     |                 |  |  |

## **5.0 I/O PORTS**

The PIC16C554 and PIC16C558 have two ports, PORTA and PORTB. The PIC16C557 has three ports, PORTA, PORTB and PORTC.

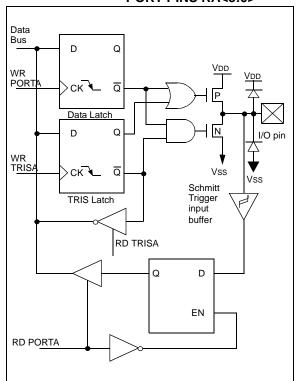

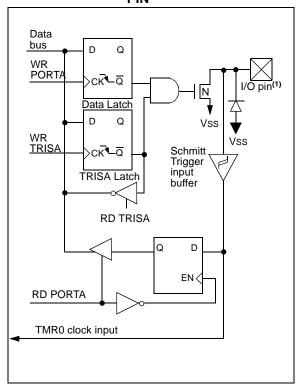

## 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open-drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

**Note 1:** On RESET, the TRISA register is set to all inputs.

FIGURE 5-1: BLOCK DIAGRAM OF PORT PINS RA<3:0>

FIGURE 5-2: BLOCK DIAGRAM OF RA4

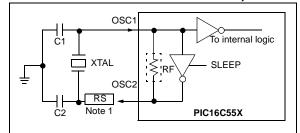

## 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

## 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

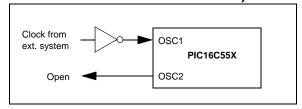

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

FIGURE 6-1: CRYSTAL OPERATION

(OR CERAMIC

RESONATOR) (HS, XT OR

LP OSC

CONFIGURATION)

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: See Table 6-1 and Table 6-2 for recommended values of C1 and C2.

FIGURE 6-2: EXTERNAL CLOCK INPUT

OPERATION (HS, XT OR

LP OSC

CONFIGURATION)

TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges |          |             |             |

|--------|----------|-------------|-------------|

| Mode   | Freq     | OSC1(C1)    | OSC2(C2)    |

| XT     | 455 kHz  | 22 - 100 pF | 22 - 100 pF |

|        | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |

|        | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |

| HS     | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |

|        | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |

Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult with the resonator manufacturer for appropriate values of external components.

TABLE 6-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (PRELIMINARY)

| Mode | Freq    | OSC1(C1)    | OSC2(C2)     |

|------|---------|-------------|--------------|

| LP   | 32 kHz  | 68 - 100 pF | 68 - 100 pF  |

|      | 200 kHz | 15 - 30 pF  | 15 - 30 pF   |

| XT   | 100 kHz | 68 - 150 pF | 150 - 200 pF |

|      | 2 MHz   | 15 - 30 pF  | 15 - 30 pF   |

|      | 4 MHz   | 15 - 30 pF  | 15 - 30 pF   |

| HS   | 8 MHz   | 15 - 30 pF  | 15 - 30 pF   |

|      | 10 MHz  | 15 - 30 pF  | 15 - 30 pF   |

|      | 20 MHz  | 15 - 30 pF  | 15 - 30 pF   |

Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid over-driving crystals with low-drive level specification. Since each crystal has its own characteristics, the user should consult with the crystal manufacturer for appropriate values of external components.

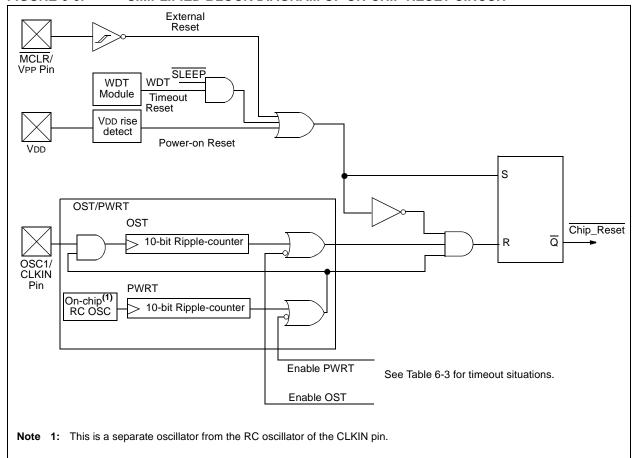

#### 6.3 RESET

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers.

A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

#### FIGURE 6-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

TABLE 6-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset                          | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', <math>q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

TABLE 6-6: INITIALIZATION CONDITION FOR REGISTERS

| Register             | Address | Power-on Reset | MCLR Reset during normal operation MCLR Reset during SLEEP WDT Reset | Wake-up from SLEEP<br>through interrupt<br>Wake-up from SLEEP<br>through WDT timeout |

|----------------------|---------|----------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| W                    | _       | xxxx xxxx      | uuuu uuuu                                                            | uuuu uuuu                                                                            |

| INDF                 | 00h     | _              | _                                                                    | _                                                                                    |

| TMR0                 | 01h     | xxxx xxxx      | uuuu uuuu                                                            | uuuu uuuu                                                                            |

| PCL                  | 02h     | 0000 0000      | 0000 0000                                                            | PC + 1 <sup>(2)</sup>                                                                |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                             | uuuq quuu <sup>(3)</sup>                                                             |

| FSR                  | 04h     | xxxx xxxx      | uuuu uuuu                                                            | uuuu uuuu                                                                            |

| PORTA                | 05h     | x xxxx         | u uuuu                                                               | u uuuu                                                                               |

| PORTB                | 06h     | xxxx xxxx      | uuuu uuuu                                                            | uuuu uuuu                                                                            |

| PORTC <sup>(4)</sup> | 06h     | xxxx xxxx      | uuuu uuuu                                                            | uuuu uuuu                                                                            |

| PCLATH               | 0Ah     | 0 0000         | 0 0000                                                               | u uuuu                                                                               |

| INTCON               | 0Bh     | 0000 000x      | 0000 000u                                                            | uuuu uuuu <sup>(1)</sup>                                                             |

| OPTION               | 81h     | 1111 1111      | 1111 1111                                                            | uuuu uuuu                                                                            |

| TRISA                | 85h     | 1 1111         | 1 1111                                                               | u uuuu                                                                               |

| TRISB                | 86h     | 1111 1111      | 1111 1111                                                            | uuuu uuuu                                                                            |

| TRISC <sup>(4)</sup> | 86h     | 1111 1111      | 1111 1111                                                            | uuuu uuuu                                                                            |

| PCON                 | 8Eh     | 0-             | u-                                                                   | u-                                                                                   |

$\mbox{Legend: } u \mbox{= unchanged, } x \mbox{= unknown, - = unimplemented bit, reads as '0', } \mbox{$q$ = value depends on condition.}$

- Note 1: One or more bits in INTCON will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- **3:** See Table 6-5 for RESET value for specific condition.

- 4: PIC16C557 only.

## 6.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 6-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 6-1:

- · Stores the W register

- Stores the STATUS register in Bank 0

- · Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 6-1: SAVING THE STATUS AND W REGISTERS IN RAM

```

MOVWF W_TEMP

;copy W to TEMP

;register, could be in

;either bank

; swap STATUS to be

SWAPF STATUS.W

;saved into W

BCF

STATUS, RPO

; change to bank 0

;regardless of

current bank

; save STATUS to bank0

MOVWF STATUS_TEMP

;register

:

SWAPF STATUS TEMP, W; swap STATUS TEMP

;register into W, sets

;bank to original state

MOVWF STATUS

;move W into STATUS

;register

SWAPF W TEMP, F

;swap W TEMP

SWAPF W_TEMP,W

;swap W_TEMP into W

```

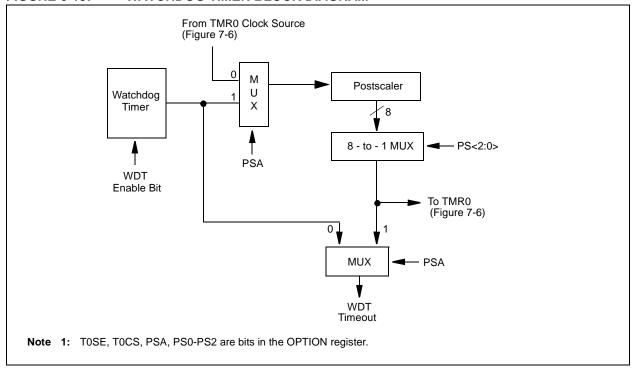

#### 6.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT timeout generates a device RESET. If the device is in SLEEP mode, a WDT timeout causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 6.1).

#### 6.7.1 WDT PERIOD

The WDT has a nominal timeout period of 18 ms, (with no prescaler). The timeout periods vary with temperature, VDD and process variations from part-to-part (see DC specs). If longer timeout periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, timeout periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer timeout.

## 6.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT timeout occurs.

FIGURE 6-13: WATCHDOG TIMER BLOCK DIAGRAM

TABLE 6-7: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other RESETS |

|---------|--------------|-------|----------|-------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 2007h   | Config. bits | _     | Reserved | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |              |                           |

| 81h     | OPTION       | RBPU  | INTEDG   | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111    | 1111 1111                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

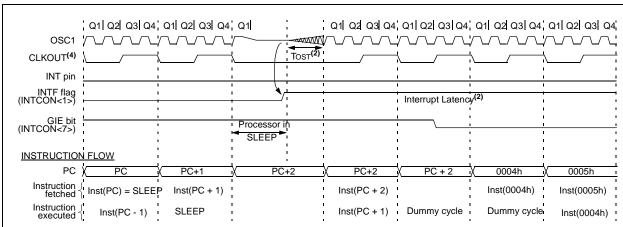

#### 6.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or himpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or Vss, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{MCLR}$  pin must be at a logic high level (VIHMC).

Note: It should be noted that a RESET gen<u>erated</u> by a WDT timeout does not drive MCLR pin low.

#### 6.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin or RB Port change

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register  $\overline{\text{can}}$  be used to determine the cause of device RESET.  $\overline{\text{PD}}$  bit, which is  $\overline{\text{set}}$  on power-up is cleared when SLEEP is invoked.  $\overline{\text{TO}}$  bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

ote: If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes-up from SLEEP, regardless of the source of wake-up.

#### FIGURE 6-14: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP Oscillator mode assumed.

- 2: Tost = 1024Tosc (drawing not to scale). This delay will not be there for RC osc mode.

- 3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in these osc modes, but shown here for timing reference.

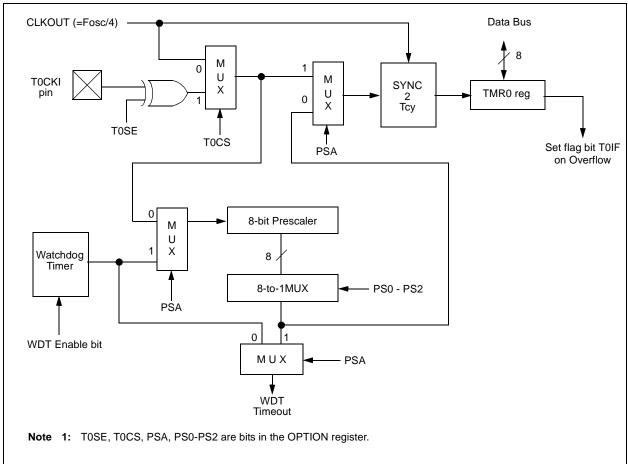

## FIGURE 7-6: BLOCK DIAGRAM OF THE TIMERO/WDT PRESCALER

#### 8.0 INSTRUCTION SET SUMMARY

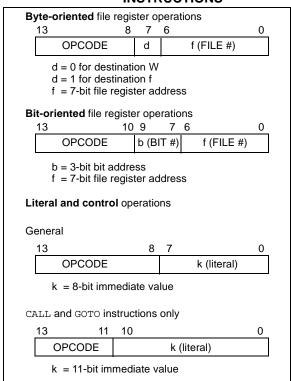

Each PIC16C55X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C55X instruction set summary in Table 8-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 8-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                     |

| W             | Working register (accumulator)                                                                                                                                           |

| b             | Bit address within an 8-bit file register                                                                                                                                |

| k             | Literal field, constant data or label                                                                                                                                    |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                             |

| label         | Label name                                                                                                                                                               |

| TOS           | Top of Stack                                                                                                                                                             |

| PC            | Program Counter                                                                                                                                                          |

| PCLATH        | Program Counter High Latch                                                                                                                                               |

| GIE           | Global Interrupt Enable bit                                                                                                                                              |

| WDT           | Watchdog Timer/Counter                                                                                                                                                   |

| TO            | Timeout bit                                                                                                                                                              |

| PD            | Power-down bit                                                                                                                                                           |

| dest          | Destination either the W register or the specified register file location                                                                                                |

| [ ]           | Options                                                                                                                                                                  |

| ( )           | Contents                                                                                                                                                                 |

| $\rightarrow$ | Assigned to                                                                                                                                                              |

| < >           | Register bit field                                                                                                                                                       |

| €             | In the set of                                                                                                                                                            |

| italics       | User defined term (font is courier)                                                                                                                                      |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 8-1 lists the instructions recognized by the MPASM™ assembler.

Figure 8-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

## 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                 |                   |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|------|--|--|--|

| Syntax:          | [ label ] ADDLW k                                                                                                 |                   |      |  |  |  |

| Operands:        | $0 \le k \le 2$                                                                                                   | 255               |      |  |  |  |

| Operation:       | (W) + k                                                                                                           | $\rightarrow$ (W) |      |  |  |  |

| Status Affected: | C, DC, 2                                                                                                          | Z                 |      |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                 |                   |      |  |  |  |

| Description:     | The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. |                   |      |  |  |  |

| Words:           | 1                                                                                                                 |                   |      |  |  |  |

| Cycles:          | 1                                                                                                                 |                   |      |  |  |  |

| Example          | ADDLW                                                                                                             | 0x15              |      |  |  |  |

|                  | Before Instruction                                                                                                |                   |      |  |  |  |

|                  | W                                                                                                                 | =                 | 0x10 |  |  |  |

|                  | After Instruction                                                                                                 |                   |      |  |  |  |

|                  | W                                                                                                                 | =                 | 0x25 |  |  |  |

| ANDLW            | AND Literal with W                                                                                            |       |      |  |

|------------------|---------------------------------------------------------------------------------------------------------------|-------|------|--|

| Syntax:          | [ label ]                                                                                                     | ANDLV | V k  |  |

| Operands:        | $0 \le k \le 2$                                                                                               | 255   |      |  |

| Operation:       | (W) .AND. $(k) \rightarrow (W)$                                                                               |       |      |  |

| Status Affected: | Z                                                                                                             |       |      |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                             |       |      |  |

| Description:     | The contents of W register are AND'ed with the eight bit literal 'k'. The result is placed in the W register. |       |      |  |

| Words:           | 1                                                                                                             |       |      |  |

| Cycles:          | 1                                                                                                             |       |      |  |

| Example          | ANDLW                                                                                                         | 0x5F  |      |  |

|                  | Before Instruction                                                                                            |       |      |  |

|                  | W                                                                                                             | =     | 0xA3 |  |

|                  | After Instruction                                                                                             |       |      |  |

|                  | W                                                                                                             | =     | 0x03 |  |

| ADDWF            | Add W                                                                                                                                                            | and f |       |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|--|

| Syntax:          | [ label ]                                                                                                                                                        | ADDW  | F f,d |  |

| Operands:        | $0 \le f \le 1$ $d \in [0,1]$                                                                                                                                    |       |       |  |

| Operation:       | $(W) + (f) \rightarrow (dest)$                                                                                                                                   |       |       |  |

| Status Affected: | C, DC, Z                                                                                                                                                         |       |       |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                |       |       |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |       |       |  |

| Words:           | 1                                                                                                                                                                |       |       |  |

| Cycles:          | 1                                                                                                                                                                |       |       |  |

| Example          | ADDWF                                                                                                                                                            | FSR,  | 0     |  |

|                  | Before Instruction                                                                                                                                               |       |       |  |

|                  | W                                                                                                                                                                | =     | 0x17  |  |

|                  | FS                                                                                                                                                               | R =   | 0xC2  |  |

|                  | After Instruction                                                                                                                                                |       |       |  |

|                  | W                                                                                                                                                                | =     | 0xD9  |  |

FSR = 0xC2

| ANDWF            | AND W with f                                                                                                                                     |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                              |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                               |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                               |  |  |

| Status Affected: | Z                                                                                                                                                |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |  |  |

| Words:           | 1                                                                                                                                                |  |  |

| Cycles:          | 1                                                                                                                                                |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                     |  |  |

|                  | Before Instruction                                                                                                                               |  |  |

|                  | W = 0x17                                                                                                                                         |  |  |

|                  | FSR = 0xC2                                                                                                                                       |  |  |

|                  | After Instruction                                                                                                                                |  |  |

|                  | W = 0x17                                                                                                                                         |  |  |

|                  | FSR = 0x02                                                                                                                                       |  |  |

| XORLW | Exclusive OR Literal with W |

|-------|-----------------------------|

| AURLW | Exclusive OR Literal with W |

Syntax: [ label ] XORLW k

Operands:  $0 \le k \le 255$

Operation: (W) .XOR.  $k \rightarrow (W)$

Status Affected: Z

Encoding: 11 1010 kkkk kkkk

Description: The contents of the W register are XOR'ed with the eight bit literal 'k'.

The result is placed in the W register.

Words: 1 Cycles: 1

Example: XORLW 0xAF

Before Instruction

W = 0xB5

After Instruction

W = 0x1A

#### XORWF Exclusive OR W with f

Syntax: [ label ] XORWF f,d

Operands:  $0 \le f \le 127$  $d \in [0,1]$

a ∈ [0,1]

Operation: (W) .XOR. (f)  $\rightarrow$  (dest)

Status Affected: Z

Encoding:

Description: Exclusive OR the contents of the

00

W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register

dfff

ffff

0110

'f'.

Words: 1 Cycles: 1

Example XORWF REG 1

Before Instruction

REG = 0xAF W = 0xB5

After Instruction

REG = 0x1A W = 0xB5

## 10.0 ELECTRICAL SPECIFICATIONS

#### **Absolute Maximum Ratings †**

| Ambient Temperature under bias                                                                              | 40° to +125°C                  |

|-------------------------------------------------------------------------------------------------------------|--------------------------------|

| Storage Temperature                                                                                         | 65° to +150°C                  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                | 0.6V to VDD +0.6V              |

| Voltage on VDD with respect to Vss                                                                          | 0 to +7.5V                     |

| Voltage on MCLR with respect to Vss                                                                         | 0 to +14V                      |

| Total power Dissipation (Note 1)                                                                            | 1.0W                           |

| Maximum Current out of Vss pin                                                                              | 300 mA                         |

| Maximum Current into VDD pin                                                                                | 250 mA                         |

| Input Clamp Current, Iικ (VI < 0 or VI > VDD)                                                               | ±20 mA                         |

| Output Clamp Current, IOκ (V0 < 0 or V0 > VDD)                                                              | ±20 mA                         |

| Maximum Output Current sunk by any I/O pin                                                                  | 25 mA                          |

| Maximum Output Current sourced by any I/O pin                                                               | 25 mA                          |

| Maximum Current sunk by PORTA, PORTB and PORTC                                                              | 200 mA                         |

| Maximum Current sourced by PORTA, PORTB and PORTC                                                           | 200 mA                         |

| Note 1. Power dissination is calculated as follows: Pais - Vpp v (lpp \subseteq [qui) \subseteq [(\lpha \)] | D ((01) x [01) 1 Z(((0) x [01) |

**Note 1:** Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD-VOH) x IOH} +  $\Sigma$ (VOI x IOL)

† **NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 10-2: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter # | Sym      | Characteristic                                                        | Min                          | Тур†    | Max        | Units    |

|-------------|----------|-----------------------------------------------------------------------|------------------------------|---------|------------|----------|

| 10*         | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓ <sup>(1)</sup>                           |                              | 75<br>— | 200<br>400 | ns<br>ns |

| 11*         | TosH2ckH | OSC1 <sup>†</sup> to CLKOUT <sup>†</sup> (1)                          | _                            | 75<br>— | 200<br>400 | ns<br>ns |

| 12*         | TckR     | CLKOUT rise time <sup>(1)</sup>                                       | _                            | 35<br>— | 100<br>200 | ns<br>ns |

| 13*         | TckF     | CLKOUT fall time <sup>(1)</sup>                                       |                              | 35<br>— | 100<br>200 | ns<br>ns |

| 14*         | TckL2ioV | CLKOUT ↓ to Port out valid <sup>(1)</sup>                             | _                            | _       | 20         | ns       |

| 15*         | TioV2ckH | Port in valid before CLKOUT ↑ (1)                                     | Tosc +200 ns<br>Tosc +400 ns |         | _          | ns<br>ns |

| 16*         | TckH2ioI | Port in hold after CLKOUT ↑ (1)                                       | 0                            | _       | _          | ns       |

| 17*         | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid                                    |                              | 50      | 150<br>300 | ns<br>ns |

| 18*         | TosH2ioI | OSC1 <sup>†</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | 100<br>200                   | _       | _          | ns<br>ns |

| 19*         | TioV2osH | Port input valid to OSC1↑ (I/O in setup time)                         | 0                            | _       | _          | ns       |

| 20*         | TioR     | Port output rise time                                                 |                              | 10<br>— | 40<br>80   | ns<br>ns |

| 21*         | TioF     | Port output fall time                                                 |                              | 10<br>— | 40<br>80   | ns<br>ns |

| 22*         | Tinp     | RB0/INT pin high or low time                                          | 25<br>40                     | _       | _          | ns<br>ns |

| 23*         | Trbp     | RB<7:4> change interrupt high or low time                             | Tcy                          | _       | _          | ns       |

These parameters are characterized but not tested.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

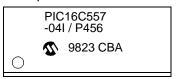

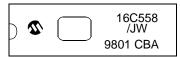

## Package Marking Information (Cont'd)

18-Lead SOIC (.300")

Example

28-Lead SOIC (.300")

Example

18-Lead CERDIP Windowed

Example

28-Lead CERDIP Windowed

Example

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device               | X /XX XXX Temperature Package Pattern Range                                                                                                                         | Examples:  a) PIC17C756–16L Commercial Temp., PLCC package, 16 MHz, normal VDD limits                                                                       |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Temperature Range Package | PIC17C756: Standard VDD range PIC17C756T: (Tape and Reel) PIC17LC756: Extended VDD range  - = 0°C to +70°C I = -40°C to +85°C  CL = Windowed LCC PT = TQFP L = PLCC | b) PIC17LC756–08/PT Commercial Temp., TQFP package, 8MHz, extended VDD limits c) PIC17C756–33I/PT Industrial Temp., TQFP package, 33 MHz, normal VDD limits |

| Pattern                          | QTP, SQTP, ROM Code (factory specified) or Special Requirements. Blank for OTP and Windowed devices.                                                                |                                                                                                                                                             |

<sup>\*</sup> JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

## **Sales and Support**

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)

# PIC16C55X

NOTES: