Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

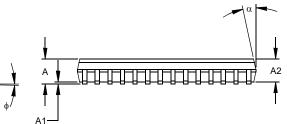

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c558t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

|                                          | _   |

|------------------------------------------|-----|

| .0 General Description                   | . 5 |

| .0 PIC16C55X Device Varieties            | . 7 |

| .0       General Description             | . 9 |

| .0 Memory Organization                   | 13  |

|                                          |     |

| 0.0 Special Features of the CPU          | 31  |

| .0 Timer0 Module                         |     |

| 0 Instruction Set Summary                | 53  |

| .0 Development Support                   | 67  |

| 0.0 Electrical Specifications            | 73  |

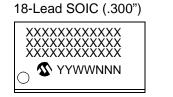

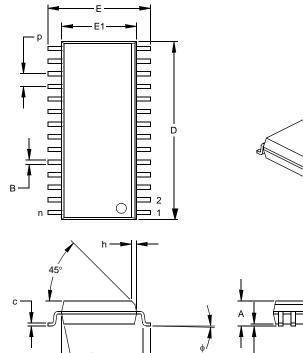

| 1.0 Packaging Information                | 87  |

| vppendix A: Enhancements                 | 97  |

| ppendix B: Compatibility                 | 97  |

| ndex                                     | 99  |

| Dn-Line Support 1                        | 01  |

| Systems Information and Upgrade Hot Line | 01  |

| Dn-Line Support                          | 02  |

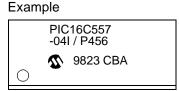

| Product Identification System            | 03  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

# 1.0 GENERAL DESCRIPTION

The PIC16C55X are 18, 20 and 28-Pin EPROM-based members of the versatile PIC16CXX family of low cost, high performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16C55X have enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16C55X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16C554 has 80 bytes of RAM. The PIC16C557 and PIC16C558 have 128 bytes of RAM. The PIC16C554 and PIC16C558 have 13 I/O pins and an 8bit timer/counter with an 8-bit programmable prescaler. The PIC16C557 has 22 I/O pins and an 8-bit timer/ counter with an 8-bit programmable prescaler.

PIC16C55X devices have special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for high speed crystals. The SLEEP (power-down) mode offers power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and RESET.

A highly reliable Watchdog Timer, with its own on-chip RC oscillator, provides protection against software lock-up. A UV-erasable CERDIP packaged version is ideal for code development while the cost effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16C55X midrange microcontroller families.

A simplified block diagram of the PIC16C55X is shown in Figure 3-1.

The PIC16C55X series fit perfectly in applications ranging from motor control to low power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C55X very versatile.

# 1.1 Family and Upward Compatibility

Users familiar with the family of microcontrollers will realize that this is an enhanced version of the architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for can be easily ported to PIC16C55X family of devices (Appendix B).

The PIC16C55X family fills the niche for users wanting to migrate up from the family and not needing various peripheral features of other members of the PIC16XX mid-range microcontroller family.

# 1.2 Development Support

The PIC16C55X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low cost development programmer and a full-featured programmer.

#### TABLE 1-1: PIC16C55X FAMILY OF DEVICES

|             |                                      | PIC16C554                        | PIC16C557                        | PIC16C558                 |

|-------------|--------------------------------------|----------------------------------|----------------------------------|---------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 20                        |

| Memory      | EPROM Program Memory<br>(x14 words)  | 512                              | 2K                               | 2K                        |

|             | Data Memory (bytes)                  | 80                               | 128                              | 128                       |

| Peripherals | Timer Module(s)                      | TMR0                             | TMR0                             | TMR0                      |

|             | Interrupt Sources                    | 3                                | 3                                | 3                         |

|             | I/O Pins                             | 13                               | 22                               | 13                        |

| Features    | Voltage Range (Volts)                | 2.5-5.5                          | 2.5-5.5                          | 2.5-5.5                   |

| catares     | Brown-out Reset                      | —                                | —                                | —                         |

|             | Packages                             | 18-pin DIP, SOIC;<br>20-pin SSOP | 28-pin DIP, SOIC;<br>28-pin SSOP | 18-pin DIP, SOIC,<br>SSOP |

I/O current capability. All PIC16C55X Family devices use serial programming with clock pin RB6 and data pin RB7.

# 2.0 PIC16C55X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C55X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PROMATE<sup>®</sup> programmers both support programming of the PIC16C55X.

# 2.2 One-Time Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 Serialized Quick-Turnaround Production (SQTP<sup>™</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

| Address                                       | Name                                                    | Bit 7                                          | Bit 6                                                                                          | Bit 5            | Bit 4               | Bit 3            | Bit 2        | Bit 1                        | Bit 0            | Value on<br>POR Reset                            | Detail on<br>Page:       |

|-----------------------------------------------|---------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|---------------------|------------------|--------------|------------------------------|------------------|--------------------------------------------------|--------------------------|

| Bank 0                                        |                                                         |                                                |                                                                                                |                  |                     |                  |              |                              |                  |                                                  |                          |

| 00h                                           | INDF                                                    |                                                | Addressing this location uses contents of FSR to address data memory (not a physical register) |                  |                     |                  |              |                              |                  | XXXX XXXX                                        | 21                       |

| 01h                                           | TMR0                                                    | Timer0 N                                       | /lodule's Re                                                                                   | egister          |                     |                  |              |                              |                  | xxxx xxxx                                        | 47                       |

| 02h                                           | PCL                                                     | Program                                        | Counter's                                                                                      | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 03h                                           | STATUS                                                  | IRP <sup>(2)</sup>                             | RP1 <sup>(2)</sup>                                                                             | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 04h                                           | FSR                                                     | Indirect of                                    | data memo                                                                                      | ry address       | s pointer           |                  |              |                              |                  | xxxx xxxx                                        | 21                       |

| 05h                                           | PORTA                                                   | -                                              | —                                                                                              | —                | RA4                 | RA3              | RA2          | RA1                          | RA0              | x xxxx                                           | 23                       |

| 06h                                           | PORTB                                                   | RB7                                            | RB6                                                                                            | RB5              | RB4                 | RB3              | RB2          | RB1                          | RB0              | xxxx xxxx                                        | 25                       |

| 07h                                           | PORTC <sup>(4)</sup>                                    | RC7                                            | RC6                                                                                            | RC5              | RC4                 | RC3              | RC2          | RC1                          | RC0              | xxxx xxxx                                        | 27                       |

| 08h                                           | _                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                |                          |

| 09h                                           | _                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Ah                                           | PCLATH                                                  | _                                              | —                                                                                              |                  | Write but           | fer for upp      | per 5 bits o | of progran                   | n counter        | 0 0000                                           | 21                       |

| 0Bh                                           | INTCON                                                  | GIE                                            | (3)                                                                                            | T0IE             | INTE                | RBIE             | T0IF         | INTF                         | RBIF             | 0000 000x                                        | 19                       |

| 0Ch                                           | —                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                |                          |

| 0Dh-1Eh                                       | —                                                       | Unimple                                        | Unimplemented                                                                                  |                  |                     |                  |              |                              |                  | _                                                | —                        |

| 1Fh                                           | —                                                       | Unimple                                        | mented                                                                                         |                  |                     |                  |              |                              |                  | _                                                | _                        |

| Bank 1                                        |                                                         |                                                |                                                                                                |                  |                     |                  |              |                              |                  |                                                  |                          |

| 80h                                           | INDF                                                    | Addressi<br>physical                           | ing this loca<br>register)                                                                     | ation uses       | contents            | of FSR to a      | address d    | ata memo                     | ory (not a       | XXXX XXXX                                        | 21                       |

| 81h                                           | OPTION                                                  | RBPU                                           | INTEDG                                                                                         | TOCS             | T0SE                | PSA              | PS2          | PS1                          | PS0              | 1111 1111                                        | 18                       |

| 82h                                           | PCL                                                     | Program                                        | Counter's                                                                                      | (PC) Leas        | t Significa         | nt Byte          |              |                              |                  | 0000 0000                                        | 21                       |

| 83h                                           | STATUS                                                  | _                                              | _                                                                                              | RP0              | TO                  | PD               | Z            | DC                           | С                | 0001 1xxx                                        | 17                       |

| 84h                                           | FSR                                                     |                                                |                                                                                                | Indirect d       | ata memo            | ry address       | s pointer    |                              |                  | xxxx xxxx                                        | 21                       |

| 85h                                           | TRISA                                                   | -                                              | —                                                                                              | —                | TRISA4              | TRISA3           | TRISA2       | TRISA1                       | TRISA0           | 1 1111                                           | 23                       |

| 86h                                           | TDIOD                                                   |                                                |                                                                                                |                  |                     |                  | TDIODO       | TDICD4                       |                  |                                                  | 05                       |

| 0011                                          | TRISB                                                   | TRISB7                                         | TRISB6                                                                                         | TRISB5           | TRISB4              | TRISB3           | TRISB2       | TRISB1                       | TRISB0           | 1111 1111                                        | 25                       |

| 87h                                           | TRISB                                                   | TRISB7<br>TRISC7                               | TRISB6<br>TRISC6                                                                               | TRISB5<br>TRISC5 | TRISB4<br>TRISC4    | TRISB3<br>TRISC3 | TRISB2       | TRISC1                       | TRISB0<br>TRISC0 | 1111 1111<br>1111 1111                           | 25                       |

|                                               |                                                         |                                                | TRISC6                                                                                         |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h                                           |                                                         | TRISC7                                         | TRISC6<br>mented                                                                               |                  |                     |                  |              |                              |                  |                                                  |                          |

| 87h<br>88h                                    |                                                         | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                               |                  | TRISC4              |                  | TRISC2       | TRISC1                       | TRISC0           |                                                  | 27<br>—                  |

| 87h<br>88h<br>89h                             | TRISC <sup>(4)</sup><br>—<br>—                          | TRISC7<br>Unimple                              | TRISC6<br>mented                                                                               |                  | TRISC4              | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—                              | 27<br>—<br>—             |

| 87h<br>88h<br>89h<br>8Ah                      | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple                   | TRISC6<br>mented<br>mented<br>(3)                                                              | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh               | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br><br>GIE        | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                    | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch        | TRISC <sup>(4)</sup><br>—<br>—<br>PCLATH                | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>mented<br>(3)<br>mented                                                    | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1                       | TRISC0           | 1111 1111<br>—<br>—<br>————————————————————————— | 27<br>—<br>—<br>21       |

| 87h<br>88h<br>89h<br>8Ah<br>8Bh<br>8Ch<br>8Dh | TRISC <sup>(4)</sup><br>—<br>PCLATH<br>INTCON<br>—<br>— | TRISC7<br>Unimple<br>Unimple<br>GIE<br>Unimple | TRISC6<br>mented<br>—<br>(3)<br>mented<br>mented                                               | TRISC5           | TRISC4<br>Write but | TRISC3           | TRISC2       | TRISC1<br>of program<br>INTF | TRISC0           | 1111 1111<br>                                    | 27<br>—<br>21<br>19<br>— |

### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16C55X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: IRP & RP1 bits are reserved, always maintain these bits clear.

3: Bit 6 of INTCON register is reserved for future use. Always maintain this bit as clear.

4: PIC16C557 only.

#### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

# 4.3 PCL and PCLATH

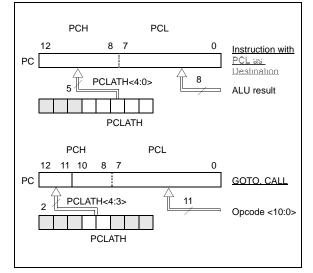

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high bits (PC<12:8>) are not directly readable or writable and come from PCLATH. On any RESET, the PC is cleared. Figure 4-6 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 4-6 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-6: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

# 4.3.2 STACK

The PIC16C55X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-1 and Figure 4-2). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RET-FIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or vectoring to an interrupt address.

# 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a nooperation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16C55X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMP | LE 4-1:                                         | INDIR                                       | INDIRECT ADDRESSING                                                                                              |  |  |  |  |

|-------|-------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NEXT  | movlw<br>movwf<br>clrf<br>incf<br>btfss<br>goto | 0x20<br>FSR<br>INDF<br>FSR<br>FSR,4<br>NEXT | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next ;yes continue</pre> |  |  |  |  |

CONTINUE:

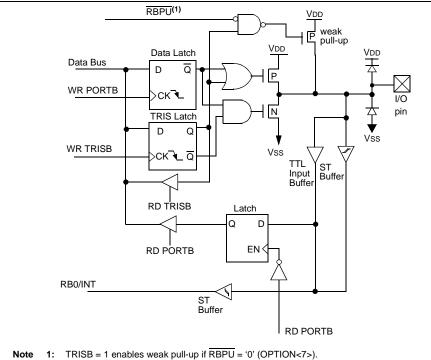

# TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit # | Buffer Type           | Function                                                                                                                       |

|---------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | Bit 0 | TTL/ST <sup>(1)</sup> | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |

| RB1     | Bit 1 | TTL                   | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |

| RB2     | Bit 2 | TTL                   | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |

| RB3     | Bit 3 | TTL                   | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |

| RB4     | Bit 4 | TTL                   | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB5     | Bit 5 | TTL                   | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up.                               |

| RB6     | Bit 6 | TTL/ST <sup>(2)</sup> | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | Bit 7 | TTL/ST <sup>(2)</sup> | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB AND TRISB

| Address  | Name   | Bit 7  | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|----------|--------|--------|----------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h      | PORTB  | RB7    | RB6      | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx xxxx       | uuuu uuuu                       |

| 86h      | TRISB  | TRISB7 | TRISB6   | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h      | OPTION | RBPU   | INTEDG   | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 0BH, 8BH | INTCON | GIE    | Reserved | TOIE   | INTE   | BRIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

Legend: x = unknown, u = unchanged

Note 1: Shaded bits are not used by PORTB.

# 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

# 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

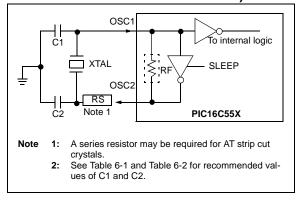

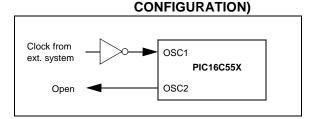

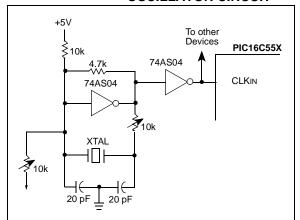

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

#### FIGURE 6-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

FIGURE 6-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

#### TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges  | Characterize                                                                                                                                 |                                         |                                         |  |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|--|--|

| Mode    | Freq                                                                                                                                         | OSC2(C2)                                |                                         |  |  |  |  |  |

| ХТ      | 455 kHz<br>2.0 MHz<br>4.0 MHz                                                                                                                | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |  |  |

| HS      | 8.0 MHz<br>16.0 MHz                                                                                                                          | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |  |  |  |

| Note 1: | Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design |                                         |                                         |  |  |  |  |  |

| of the oscillator but also increases the    |

|---------------------------------------------|

| start-up time. These values are for design  |

| guidance only. Since each resonator has     |

| its own characteristics, the user should    |

| consult with the resonator manufacturer for |

| appropriate values of external compo-       |

| nents.                                      |

| TABLE 6-2: | <b>CAPACITOR SELECTION FOR</b> |

|------------|--------------------------------|

|            | CRYSTAL OSCILLATOR             |

|            | (PRELIMINARY)                  |

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC1(C1)    | OSC2(C2)     |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|--|--|--|--|

| LP      | 32 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 - 100 pF | 68 - 100 pF  |  |  |  |  |

|         | 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 - 30 pF  | 15 - 30 pF   |  |  |  |  |

| XT      | 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 - 150 pF | 150 - 200 pF |  |  |  |  |

|         | 2 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |  |  |  |

|         | 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |  |  |  |

| HS      | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |  |  |  |  |

|         | 10 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |  |  |  |  |

|         | 20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |  |  |  |  |

| Note 1: | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid over-<br>driving crystals with low-drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>with the crystal manufacturer for appropri-<br>ate values of external components. |             |              |  |  |  |  |

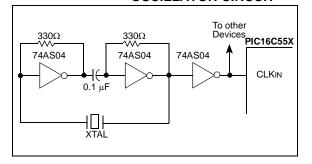

#### 6.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a pre-packaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 6-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 6-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

Figure 6-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The  $330\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 6-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

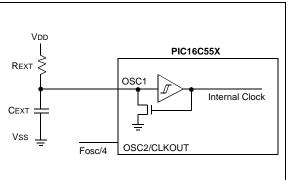

# 6.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 6-5 shows how the R/C combination is connected to the PIC16C55X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 6-5: RC OSCILLATOR MODE

| Address | Name         | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other RESETS |

|---------|--------------|-------|----------|-------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 2007h   | Config. bits | _     | Reserved | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |              |                           |

| 81h     | OPTION       | RBPU  | INTEDG   | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111    | 1111 1111                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

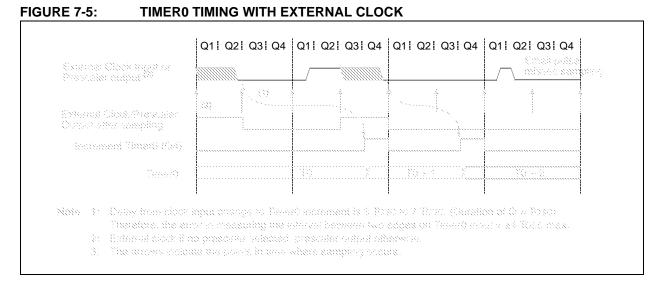

# 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

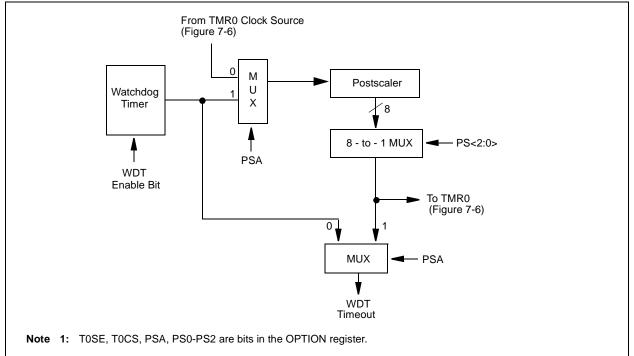

# 7.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

Note: There is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

© 1996-2013 Microchip Technology Inc.

# 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                       |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                       |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |  |  |  |  |

| Words:           | 1                                                                                                                       |  |  |  |  |

| Cycles:          | 1                                                                                                                       |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                      |  |  |  |  |

|                  | W = 0x10                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                       |  |  |  |  |

|                  | W = 0x25                                                                                                                |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |

| ANDLW            | AND Li                                  | teral wit  | h W            |          |  |

|------------------|-----------------------------------------|------------|----------------|----------|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                |            |                |          |  |

| Operands:        | $0 \le k \le 255$                       |            |                |          |  |

| Operation:       | (W) .AN                                 | ID. (k) →  | • (W)          |          |  |

| Status Affected: | Z                                       |            |                |          |  |

| Encoding:        | 11                                      | 1001       | kkkk           | kkkk     |  |

|                  | The conter<br>AND'ed wi<br>result is pl | th the eig | ht bit literal | 'k'. The |  |

| Words:           | 1                                       |            |                |          |  |

| Cycles:          | 1                                       |            |                |          |  |

| Example          | ANDLW                                   | 0x5F       |                |          |  |

|                  | Before I                                | nstructio  | on             |          |  |

|                  | W                                       | =          | 0xA3           |          |  |

|                  | After Ins                               | struction  |                |          |  |

|                  | W                                       | =          | 0x03           |          |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                         |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |  |

-

| RRF               | Rotate                                                                                                                                                                                                       | Right f                                       | throu            | igh (              | Carry      |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|--------------------|------------|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                    | RRF 1                                         | ,d               |                    |            |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                              |                                               |                  |                    |            |  |  |

| Operation:        | See description below                                                                                                                                                                                        |                                               |                  |                    |            |  |  |

| Status Affected:  | С                                                                                                                                                                                                            |                                               |                  |                    |            |  |  |

| Encoding:         | 00                                                                                                                                                                                                           | 1100                                          | dff              | f                  | ffff       |  |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                                               |                  |                    |            |  |  |

|                   |                                                                                                                                                                                                              |                                               |                  |                    |            |  |  |

|                   |                                                                                                                                                                                                              |                                               | Regist           | ter f              | ┠╼         |  |  |

| Words:            | 1                                                                                                                                                                                                            |                                               | Regist           | ter f              | ]-•        |  |  |

| Words:<br>Cycles: | 1<br>1                                                                                                                                                                                                       | ] <b>→</b> [                                  | Regist           | ter f              | <b>]</b> • |  |  |

|                   | •                                                                                                                                                                                                            |                                               |                  | ter f              | <u>}-</u>  |  |  |

| Cycles:           | 1                                                                                                                                                                                                            |                                               | REG              |                    | <u>-</u>   |  |  |

| Cycles:           | 1<br>RRF                                                                                                                                                                                                     | struction                                     | REG              | \$1,0              | 0          |  |  |

| Cycles:           | 1<br>RRF<br>Before Ins                                                                                                                                                                                       | struction                                     | REG<br>n<br>1110 | \$1,0              | .0         |  |  |

| Cycles:           | 1<br>RRF<br>Before Ins<br>REG<br>C<br>After Instr                                                                                                                                                            | struction<br>1 = 1<br>= 0<br>ruction          | REG<br>n<br>1110 | \$1,0              | 0          |  |  |

| Cycles:           | 1<br>RRF<br>Before In:<br>REG<br>C<br>After Insti<br>REG                                                                                                                                                     | struction<br>1 = 1<br>= 0<br>ruction          | REG<br>n<br>1110 | \$1,0              | -          |  |  |

| Cycles:           | 1<br>RRF<br>Before Ins<br>REG<br>C<br>After Instr                                                                                                                                                            | struction<br>1 = 1<br>= (<br>ruction<br>1 = 1 | REG<br>N<br>L110 | ;1,0<br>011<br>011 | .0         |  |  |

#### SLEEP

| Syntax:          | [ label<br>]                                                                                                                    | SLEEP                                                                                            |                                                                |                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------|

| Operands:        | None                                                                                                                            |                                                                                                  |                                                                |                     |

| Operation:       | $\begin{array}{c} 00h \rightarrow V\\ 0 \rightarrow WE\\ 1 \rightarrow \overline{TO}\\ 0 \rightarrow \overline{PD} \end{array}$ | T presca                                                                                         | ıler,                                                          |                     |

| Status Affected: | $\overline{\text{TO}}, \overline{\text{PD}}$                                                                                    |                                                                                                  |                                                                |                     |

| Encoding:        | 00                                                                                                                              | 0000                                                                                             | 0110                                                           | 0011                |

| Description:     | cleared.<br>set. Wate<br>prescaler<br>The proc<br>mode wit                                                                      | er-down st<br>Timeout st<br>hdog Time<br>are cleard<br>essor is pu<br>h the oscil<br>ion 6.8 for | atus bit, T<br>er and its<br>ed.<br>ut into SLI<br>llator stop | O is<br>EEP<br>ped. |

| Words:           | 1                                                                                                                               |                                                                                                  |                                                                |                     |

| Cycles:          | 1                                                                                                                               |                                                                                                  |                                                                |                     |

| Example:         | SLEEP                                                                                                                           |                                                                                                  |                                                                |                     |

| SUBLW               | Subtract W from Literal  |                                                                                                                                      |              |          |  |  |

|---------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|--|--|

| Syntax:             | [ <i>label</i> ] SUBLW k |                                                                                                                                      |              |          |  |  |

| Operands:           | $0 \le k \le 255$        |                                                                                                                                      |              |          |  |  |

| Operation:          | k - (W) → (              | $k - (W) \to (W)$                                                                                                                    |              |          |  |  |

| Status<br>Affected: | C, DC, Z                 | C, DC, Z                                                                                                                             |              |          |  |  |

| Encoding:           | 11                       | 110x                                                                                                                                 | kkkk         | kkkk     |  |  |

| Description:        | plement me               | The W register is subtracted (2's com-<br>plement method) from the eight bit literal<br>'k'. The result is placed in the W register. |              |          |  |  |

| Words:              | 1                        |                                                                                                                                      |              |          |  |  |

| Cycles:             | 1                        |                                                                                                                                      |              |          |  |  |

| Example 1:          | SUBLW                    | 0x02                                                                                                                                 |              |          |  |  |

|                     | Before Ins               | truction                                                                                                                             |              |          |  |  |

|                     | W                        | = 1                                                                                                                                  | l            |          |  |  |

|                     | С                        | = ?                                                                                                                                  | ?            |          |  |  |

|                     | After Instru             | uction                                                                                                                               |              |          |  |  |

|                     | W                        | = 1                                                                                                                                  | l            |          |  |  |

|                     | С                        | = 1                                                                                                                                  | l; result is | positive |  |  |

| Example 2:          | Before Ins               | truction                                                                                                                             |              |          |  |  |

|                     | W                        | = 2                                                                                                                                  | 2            |          |  |  |

|                     | С                        | = ?                                                                                                                                  | 2            |          |  |  |

|                     | After Instru             | uction                                                                                                                               |              |          |  |  |

|                     | W                        | = (                                                                                                                                  | )            |          |  |  |