Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 80 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554-04-p |

### 4.3 PCL and PCLATH

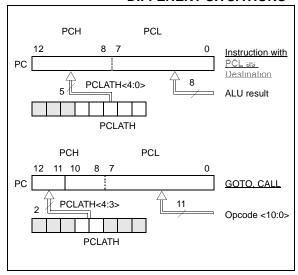

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high bits (PC<12:8>) are not directly readable or writable and come from PCLATH. On any RESET, the PC is cleared. Figure 4-6 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 4-6 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-6: LOADING OF PC IN DIFFERENT SITUATIONS

### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16C55X family has an 8-level deep x 13-bit wide hardware stack (Figure 4-1 and Figure 4-2). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or vectoring to an interrupt address.

# 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a nooperation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16C55X.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-1.

### **EXAMPLE 4-1: INDIRECT ADDRESSING**

|      | movlw | 0x20  | ;initialize pointer  |

|------|-------|-------|----------------------|

|      | movwf | FSR   | ;to RAM              |

| NEXT | clrf  | INDF  | clear INDF register; |

|      | incf  | FSR   | ;inc pointer         |

|      | btfss | FSR,4 | ;all done?           |

|      | goto  | NEXT  | ;no clear next       |

|      |       |       | yes continue;        |

|      |       |       |                      |

CONTINUE:

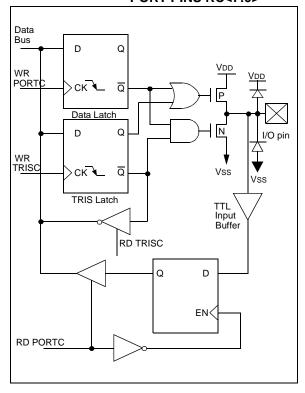

### 5.3 PORTC and TRISC Registers<sup>(1)</sup>

PORTC is a 8-bit wide latch. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISC register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISC register puts the contents of the output latch on the selected pin(s).

Reading the PORTC register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch

FIGURE 5-5: BLOCK DIAGRAM OF PORT PINS RC<7:0>

TABLE 5-5: PORTC FUNCTIONS

| Name | Bit # | Buffer Type | Function                 |

|------|-------|-------------|--------------------------|

| RC0  | Bit 0 | TTL         | Bi-directional I/O port. |

| RC1  | Bit 1 | TTL         | Bi-directional I/O port. |

| RC2  | Bit 2 | TTL         | Bi-directional I/O port. |

| RC3  | Bit 3 | TTL         | Bi-directional I/O port. |

| RC4  | Bit 4 | TTL         | Bi-directional I/O port. |

| RC5  | Bit 5 | TTL         | Bi-directional I/O port. |

| RC6  | Bit 6 | TTL         | Bi-directional I/O port. |

| RC7  | Bit 7 | TTL         | Bi-directional I/O port. |

Legend: ST = Schmitt Trigger, TTL = TTL input

TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC AND TRISC

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 07h     | PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx       | uuuu uuuu                       |

| 87h     | TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged

Note 1: PIC16C557 ONLY.

### 5.4 I/O Programming Considerations

#### 5.4.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-1 shows the effect of two sequential readmodify-write instructions (ex., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a low or high should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

# EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

```

; Initial PORT settings: PORTB<7:4> Inputs

PORTB<3:0> Outputs

PORTB<7:6> have external pull-up and are

; not connected to other circuitry

PORT latch PORT pins

BCF PORTB, 7

; 01pp pppp 11pp pppp

BCF PORTB, 6

11pp pppp

; 10pp pppp

BSF STATUS, RPO ;

BCF TRISB, 7

; 10pp pppp

11pp pppp

BCF TRISB, 6

; 10pp pppp

10pp pppp

```

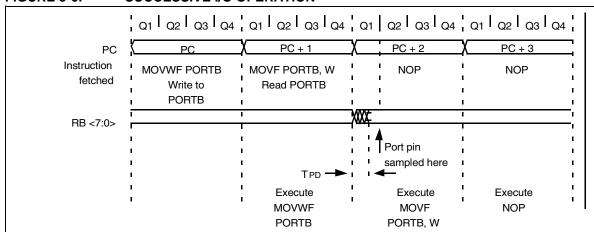

## 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle, as shown in Figure 5-6. Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

### FIGURE 5-6: SUCCESSIVE I/O OPERATION

- Note 1: This example shows write to PORTB followed by a read from PORTB.

- 2: Data setup time = (0.25 TCY TPD) where TCY = instruction cycle and TPD = propagation delay of Q1 cycle to output valid. Therefore, at higher clock frequencies, a write followed by a read may be problematic.

# 6.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST)

### 6.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.6V - 1.8V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607 "Power-up Trouble Shooting".

### 6.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) timeout on power-up only, from POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

### 6.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 6.4.4 TIMEOUT SEQUENCE

On power-up, the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired, then OST is activated. The total timeout will vary based on oscillator configuration and PWRTE bit status. For example, in RC mode with PWRTE bit erased (PWRT disabled), there will be no timeout at all. Figure 6-7, Figure 6-8 and Figure 6-9 depict timeout sequences.

Since the timeouts occur from the POR pulse, if MCLR is kept low long enough, the timeouts will expire. Then bringing MCLR high will begin execution immediately (see Figure 6-8). This is useful for testing purposes or to synchronize more than one PIC16C55X device operating in parallel.

Table 6-5 shows the RESET conditions for some special registers, while Table 6-6 shows the RESET conditions for all the registers.

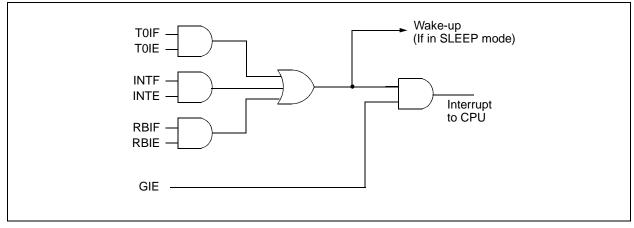

### 6.5 Interrupts

The PIC16C55X has 3 sources of interrupt:

- · External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "Return from Interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 6-12). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

FIGURE 6-11: INTERRUPT LOGIC

### 6.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 6-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 6-1:

- · Stores the W register

- Stores the STATUS register in Bank 0

- · Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

### EXAMPLE 6-1: SAVING THE STATUS AND W REGISTERS IN RAM

```

MOVWF W_TEMP

;copy W to TEMP

;register, could be in

;either bank

; swap STATUS to be

SWAPF STATUS.W

;saved into W

BCF

STATUS, RPO

; change to bank 0

;regardless of

current bank

; save STATUS to bank0

MOVWF STATUS_TEMP

;register

:

SWAPF STATUS TEMP, W; swap STATUS TEMP

;register into W, sets

; bank to original state

MOVWF STATUS

;move W into STATUS

;register

SWAPF W TEMP, F

;swap W TEMP

SWAPF W_TEMP,W

;swap W_TEMP into W

```

### 6.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT timeout generates a device RESET. If the device is in SLEEP mode, a WDT timeout causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 6.1).

### 6.7.1 WDT PERIOD

The WDT has a nominal timeout period of 18 ms, (with no prescaler). The timeout periods vary with temperature, VDD and process variations from part-to-part (see DC specs). If longer timeout periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, timeout periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer timeout.

### 6.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT timeout occurs.

### 6.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the PD bit in the STATUS register is cleared, the TO bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before SLEEP was executed (driving high, low, or himpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or Vss, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{MCLR}$  pin must be at a logic high level (VIHMC).

Note: It should be noted that a RESET gen<u>erated</u> by a WDT timeout does not drive MCLR pin low.

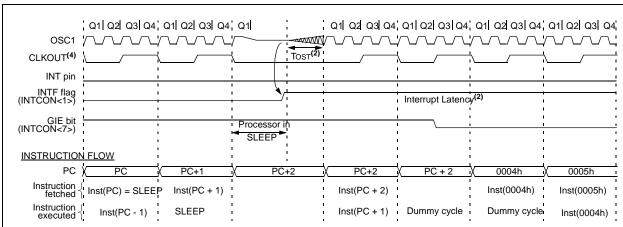

#### 6.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- External RESET input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin or RB Port change

The first event will cause a device RESET. The two latter events are considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device RESET.  $\overline{\text{PD}}$  bit, which is set on power-up is cleared when SLEEP is invoked.  $\overline{\text{TO}}$  bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

ote: If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from SLEEP. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes-up from SLEEP, regardless of the source of wake-up.

#### FIGURE 6-14: WAKE-UP FROM SLEEP THROUGH INTERRUPT

Note 1: XT, HS or LP Oscillator mode assumed.

- 2: Tost = 1024Tosc (drawing not to scale). This delay will not be there for RC osc mode.

- 3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

- 4: CLKOUT is not available in these osc modes, but shown here for timing reference.

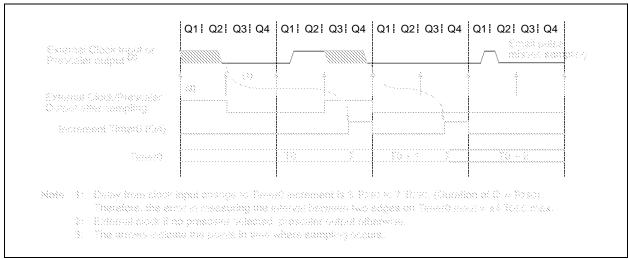

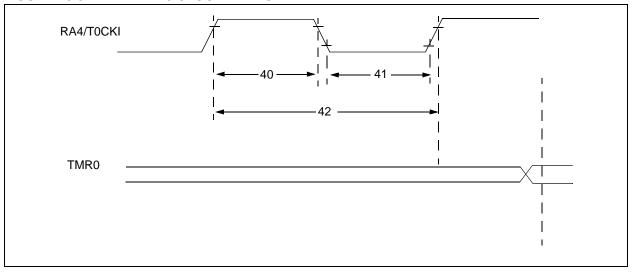

### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### 7.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

Note: There is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

NOTES:

| SUBWF               | Subtract W from f                                                                                                                                                         |  |  |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:             | [label] SUBWF f,d                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        |  |  |  |  |  |  |  |  |

| Operation:          | (f) - (W) $\rightarrow$ (dest)                                                                                                                                            |  |  |  |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Encoding:           | 00 0010 dfff ffff                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Description:        | Subtract (2's complement method) W register from register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |  |  |  |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Cycles:             | 1                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Example 1:          | SUBWF REG1,1                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                     | Before Instruction                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                     | REG1 = 3                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                     | W = 2                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | C = ?                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                     | REG1 = 1                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                     | W = 2                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Evennle 2           | C = 1; result is positive                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Example 2:          | Before Instruction                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                     | REG1 = 2<br>W = 2                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                     | C = ?                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                     | REG1 = 0                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                     | W = 2                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | C = 1; result is zero                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Example 3:          | Before Instruction                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                     | REG1 = 1                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|                     | W = 2                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | C = ?                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | After Instruction                                                                                                                                                         |  |  |  |  |  |  |  |  |

|                     | REG1 = 0xFF                                                                                                                                                               |  |  |  |  |  |  |  |  |

|                     | W = 2                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                     | C = 0; result is negative                                                                                                                                                 |  |  |  |  |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                            |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                           |  |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>),$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                    |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                         |  |  |  |  |  |  |

| Encoding:        | 00 1110 dfff ffff                                                                                                                                            |  |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0 the result is placed in W register. If 'd' is 1 the result is placed in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                            |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                            |  |  |  |  |  |  |

| Example          | SWAPF REG, 0                                                                                                                                                 |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                           |  |  |  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                  |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                            |  |  |  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                  |  |  |  |  |  |  |

|                  | W = 0x5A                                                                                                                                                     |  |  |  |  |  |  |

|                  |                                                                                                                                                              |  |  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                            |                 |        |      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|------|--|--|--|--|

| Syntax:          | [label] TRIS f                                                                                                                |                 |        |      |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                               | $5 \le f \le 7$ |        |      |  |  |  |  |

| Operation:       | $(W) \rightarrow TR$                                                                                                          | IS regis        | ter f; |      |  |  |  |  |

| Status Affected: | None                                                                                                                          |                 |        |      |  |  |  |  |

| Encoding:        | 00                                                                                                                            | 0000            | 0110   | Offf |  |  |  |  |

|                  | compatibility with the PIC16C5X products. Since TRIS registers are readable and writable, the user can directly address them. |                 |        |      |  |  |  |  |

| Words:           | 1                                                                                                                             |                 |        |      |  |  |  |  |

| Cycles:          | 1                                                                                                                             |                 |        |      |  |  |  |  |

| Example          |                                                                                                                               |                 |        |      |  |  |  |  |

|                  | To maintain upward compatibility with future PIC MCU products, do not use this instruction.                                   |                 |        |      |  |  |  |  |

NOTES:

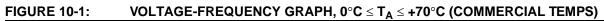

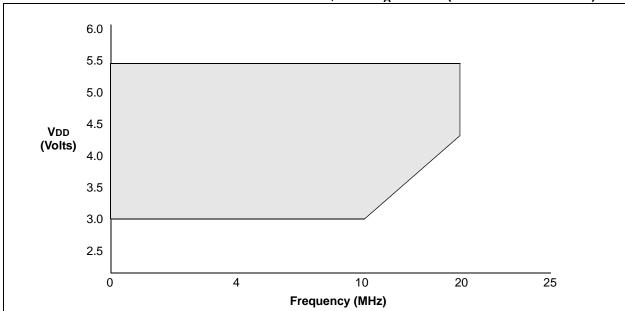

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

2: The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

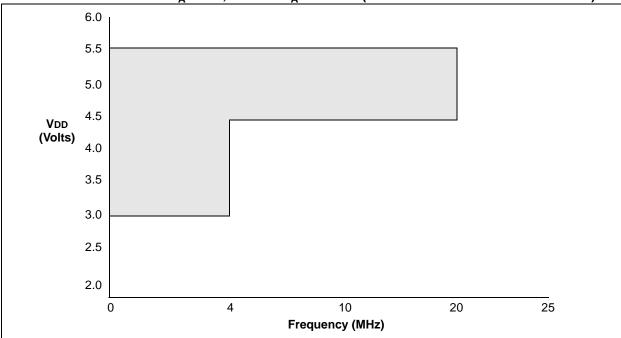

FIGURE 10-2: VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}C \leq T_{A} < 0^{\circ}C, +70^{\circ}C < T_{A} \leq +125^{\circ}C \text{ (OUTSIDE OF COMMERCIAL TEMPS)}$

Note 1: The shaded region indicates the permissible combinations of voltage and frequency.

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

**DC Characteristics**

# 10.2 DC Characteristics: PIC16C55X (Commercial, Industrial, Extended) PIC16LC55X(Commercial, Industrial, Extended)

**Standard Operating Conditions (unless otherwise stated)**

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for industrial and

$0^{\circ}C \le TA \le +70^{\circ}C$  for commercial and

-40°C  $\leq$  TA  $\leq$  +125°C for automotive

Operating voltage VDD range as described in DC spec Table 10-1

| 1             |       | T                                           |                        |      |                  |        |                                                                                                |

|---------------|-------|---------------------------------------------|------------------------|------|------------------|--------|------------------------------------------------------------------------------------------------|

| Param.<br>No. | Sym   | Characteristic                              | Min                    | Тур† | Max              | Unit   | Conditions                                                                                     |

|               | VIL   | Input Low Voltage                           |                        |      |                  |        |                                                                                                |

|               |       | I/O ports                                   |                        |      |                  |        |                                                                                                |

| D030          |       | with TTL buffer                             | Vss                    | _    | 0.8V<br>0.15 Vdd | V      | VDD = 4.5V to 5.5V otherwise                                                                   |

| D031          |       | with Schmitt Trigger input                  | Vss                    |      | 0.2 VDD          | V      |                                                                                                |

| D032          |       | MCLR, RA4/T0CKI,OSC1 (in RC mode)           | Vss                    | _    | 0.2 VDD          | V      | (Note1)                                                                                        |

| D033          |       | OSC1 (in XT* and HS)                        | Vss                    | _    | 0.3 VDD          | V      |                                                                                                |

|               |       | OSC1 (in LP*)                               | Vss                    | _    | 0.6 VDD-1.0      | V      |                                                                                                |

|               | VIH   | Input High Voltage                          |                        |      |                  |        |                                                                                                |

|               |       | I/O ports                                   |                        | _    |                  |        |                                                                                                |

| D040          |       | with TTL buffer                             | 2.0V<br>0.8 + 0.25 VDD | _    | Vdd<br>Vdd       | V<br>V | VDD = 4.5V to 5.5V otherwise                                                                   |

| D041          |       | with Schmitt Trigger input                  | 0.8V                   |      | VDD              |        |                                                                                                |

| D042          |       | MCLR RA4/T0CKI                              | 0.8 Vdd                | _    | VDD              | V      |                                                                                                |

| D043<br>D043A |       | OSC1 (XT*, HS and LP*)<br>OSC1 (in RC mode) | 0.7 VDD<br>0.9 VDD     | _    | VDD              | V      | (Note1)                                                                                        |

| D070          | IPURB | PORTB weak pull-up current                  | 50                     | 200  | 400              | μΑ     | VDD = 5.0V, VPIN = VSS                                                                         |

|               | lıL   | Input Leakage Current <sup>(2)(3)</sup>     |                        |      |                  |        |                                                                                                |

|               |       | I/O ports (Except PORTA)                    |                        |      | ±1.0             | μА     | VSS ≤ VPIN ≤ VDD, pin at himpedance                                                            |

| D060          |       | PORTA                                       | _                      | _    | ±0.5             | μΑ     | Vss ≤ VPIN ≤ VDD, pin at himpedance                                                            |

| D061          |       | RA4/T0CKI                                   | _                      | _    | ±1.0             | μΑ     | Vss ≤ VPIN ≤ VDD                                                                               |

| D063          |       | OSC1, MCLR                                  | _                      |      | ±5.0             | μΑ     | $\label{eq:VSS}  \mbox{$V$PIN$} \le \mbox{$V$DD, XT, HS and} \\ \mbox{$LP$ osc configuration}$ |

|               | Vol   | Output Low Voltage                          |                        |      |                  |        |                                                                                                |

| D080          |       | I/O ports                                   | _                      | _    | 0.6              | V      | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                                            |

|               |       |                                             | _                      | _    | 0.6              | V      | IOL=7.0 mA, VDD=4.5V, +125°C                                                                   |

| D083          |       | OSC2/CLKOUT                                 | _                      | _    | 0.6              | V      | IOL=1.6 mA, VDD=4.5V, -40° to +85°C                                                            |

|               |       | (RC only)                                   | _                      | _    | 0.6              | V      | IOL=1.2 mA, VDD=4.5V, +125°C                                                                   |

|               | Vон   | Output High Voltage <sup>(3)</sup>          |                        |      |                  |        |                                                                                                |

| D090          |       | I/O ports (Except RA4)                      | VDD-0.7                | _    | _                | V      | IOH=-3.0 mA, VDD=4.5V, -40° to +85°C                                                           |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C55X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as coming out of the pin.

TABLE 10-2: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter # | Sym      | Characteristic                                                        | Min                          | Тур†    | Max        | Units    |

|-------------|----------|-----------------------------------------------------------------------|------------------------------|---------|------------|----------|

| 10*         | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓ <sup>(1)</sup>                           |                              | 75<br>— | 200<br>400 | ns<br>ns |

| 11*         | TosH2ckH | OSC1 <sup>†</sup> to CLKOUT <sup>†</sup> (1)                          | _                            | 75<br>— | 200<br>400 | ns<br>ns |

| 12*         | TckR     | CLKOUT rise time <sup>(1)</sup>                                       | _                            | 35<br>— | 100<br>200 | ns<br>ns |

| 13*         | TckF     | CLKOUT fall time <sup>(1)</sup>                                       |                              | 35<br>— | 100<br>200 | ns<br>ns |

| 14*         | TckL2ioV | CLKOUT ↓ to Port out valid <sup>(1)</sup>                             | _                            | _       | 20         | ns       |

| 15*         | TioV2ckH | Port in valid before CLKOUT ↑ (1)                                     | Tosc +200 ns<br>Tosc +400 ns |         | _          | ns<br>ns |

| 16*         | TckH2ioI | Port in hold after CLKOUT ↑ (1)                                       | 0                            | _       | _          | ns       |

| 17*         | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid                                    |                              | 50      | 150<br>300 | ns<br>ns |

| 18*         | TosH2ioI | OSC1 <sup>†</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | 100<br>200                   | _       | _          | ns<br>ns |

| 19*         | TioV2osH | Port input valid to OSC1↑ (I/O in setup time)                         | 0                            | _       | _          | ns       |

| 20*         | TioR     | Port output rise time                                                 |                              | 10<br>— | 40<br>80   | ns<br>ns |

| 21*         | TioF     | Port output fall time                                                 | _                            | 10<br>— | 40<br>80   | ns<br>ns |

| 22*         | Tinp     | RB0/INT pin high or low time                                          | 25<br>40                     | _       | _          | ns<br>ns |

| 23*         | Trbp     | RB<7:4> change interrupt high or low time                             | Tcy                          | _       | _          | ns       |

These parameters are characterized but not tested.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 10-9: TIMERO CLOCK TIMING

TABLE 10-4: TIMERO CLOCK REQUIREMENTS

| Param<br>No. | Sym  | Characteristi          | Min            | Тур†                   | Max | Units | Conditions |                                       |

|--------------|------|------------------------|----------------|------------------------|-----|-------|------------|---------------------------------------|

| 40           | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 Tcy + 20*          | _   | -     | ns         |                                       |

|              |      |                        | With Prescaler | 10*                    | _   | _     | ns         |                                       |

| 41           | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 Tcy + 20*          | _   | _     | ns         |                                       |

|              |      |                        | With Prescaler | 10*                    | _   | _     | ns         |                                       |

| 42           | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N | _   | _     | ns         | N = prescale value<br>(1, 2, 4,, 256) |

<sup>\*</sup> These parameters are characterized but not tested.

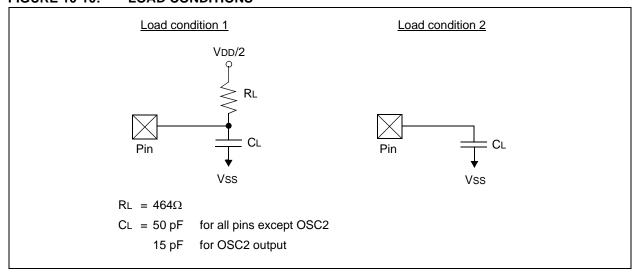

### FIGURE 10-10: LOAD CONDITIONS

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note:

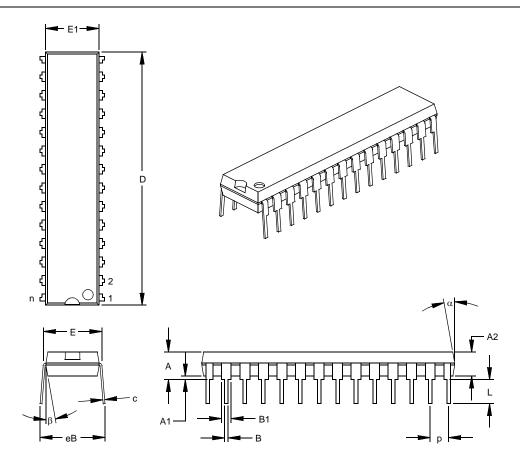

### 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units       |       | INCHES* |       | N     |       |       |

|----------------------------|-------------|-------|---------|-------|-------|-------|-------|

| Dimen                      | sion Limits | MIN   | NOM     | MAX   | MIN   | NOM   | MAX   |

| Number of Pins             | n           |       | 28      |       |       | 28    |       |

| Pitch                      | р           |       | .100    |       |       | 2.54  |       |

| Top to Seating Plane       | Α           | .140  | .150    | .160  | 3.56  | 3.81  | 4.06  |

| Molded Package Thickness   | A2          | .125  | .130    | .135  | 3.18  | 3.30  | 3.43  |

| Base to Seating Plane      | A1          | .015  |         |       | 0.38  |       |       |

| Shoulder to Shoulder Width | E           | .300  | .310    | .325  | 7.62  | 7.87  | 8.26  |

| Molded Package Width       | E1          | .275  | .285    | .295  | 6.99  | 7.24  | 7.49  |

| Overall Length             | D           | 1.345 | 1.365   | 1.385 | 34.16 | 34.67 | 35.18 |

| Tip to Seating Plane       | L           | .125  | .130    | .135  | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С           | .008  | .012    | .015  | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1          | .040  | .053    | .065  | 1.02  | 1.33  | 1.65  |

| Lower Lead Width           | В           | .016  | .019    | .022  | 0.41  | 0.48  | 0.56  |

| Overall Row Spacing        | § eB        | .320  | .350    | .430  | 8.13  | 8.89  | 10.92 |

| Mold Draft Angle Top       | α           | 5     | 10      | 15    | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β           | 5     | 10      | 15    | 5     | 10    | 15    |

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

<sup>\*</sup> Controlling Parameter § Significant Characteristic

| PICSTART Plus Entry Level Development Programmer       |    |

|--------------------------------------------------------|----|

| Port RB Interrupt                                      |    |

| PORTA                                                  |    |

| PORTB                                                  |    |

| Power Control/Status Register (PCON)                   |    |

| Power-Down Mode (SLEEP)                                |    |

| Power-On Reset (POR)                                   |    |

| Power-up Timer (PWRT)                                  |    |

| Prescaler                                              |    |

| PRO MATE II Universal Device Programmer                |    |

| Program Memory Organization                            | 13 |

| Q                                                      |    |

| Quick-Turnaround-Production (QTP) Devices              | 7  |

| Quick-Turnaround-Froduction (QTF) Devices              | 1  |

| R                                                      |    |

| RC Oscillator                                          | 34 |

| Reset                                                  |    |

| RETFIE Instruction                                     |    |

| RETLW Instruction                                      |    |

| RETURN Instruction                                     |    |

| RLF Instruction                                        |    |

| RRF Instruction                                        |    |

|                                                        |    |

| S                                                      |    |

| Serialized Quick-Turnaround-Production (SQTP) Devices. | 7  |

| SLEEP Instruction                                      | 63 |

| Software Simulator (MPLAB SIM)                         | 68 |

| Special Features of the CPU                            | 31 |

| Special Function Registers                             | 15 |

| Stack                                                  | 21 |

| Status Register                                        | 17 |

| SUBLW Instruction                                      |    |

| SUBWF Instruction                                      |    |

| SWAPF Instruction                                      | 64 |

| Т                                                      |    |

|                                                        |    |

| Timer0                                                 |    |

| TIMERO                                                 |    |

| TIMERO (TMRO) Interrupt                                |    |

| TIMER0 (TMR0) ModuleTMR0 with External Clock           |    |

| Timer1                                                 | 73 |

| Switching Prescaler Assignment                         | 51 |

| Timing Diagrams and Specifications                     |    |

| TMR0 Interrupt                                         |    |

| TRIS Instruction                                       |    |

| TRISA                                                  |    |

| TRISB                                                  |    |

| ·                                                      |    |

| W                                                      |    |

| Watchdog Timer (WDT)                                   | 43 |

| WWW, On-Line Support                                   |    |

|                                                        |    |

| X                                                      |    |

| XORLW Instruction                                      |    |

| XORWF Instruction                                      | 65 |

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: