Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

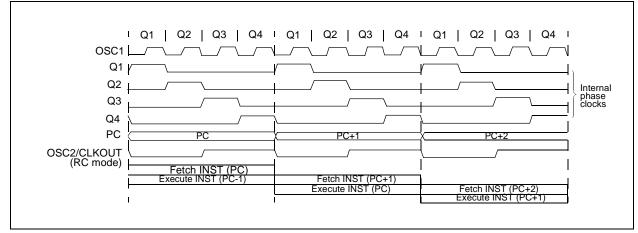

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2.

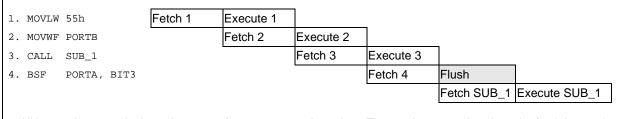

## 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle

while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

## FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

## EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Figure 4-2, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as the destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect any status bits. For other instructions, not affecting any status bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C55X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

|         | Reserved                                                                                                                                                                                                                                                                             | Reserved                                   | R/W-0   | R-1        | R-1      | R/W-x          | R/W-x       | R/W-x |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------|------------|----------|----------------|-------------|-------|--|--|

|         | IRP                                                                                                                                                                                                                                                                                  | RP1                                        | RP0     | TO         | PD       | Z              | DC          | С     |  |  |

|         | bit7                                                                                                                                                                                                                                                                                 |                                            |         |            |          |                |             | bit0  |  |  |

| bit 7   | IRP: Register Bank Select bit (used for Indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)<br>The IRP bit is reserved on the PIC16C55X, always maintain this bit clear                                                                                 |                                            |         |            |          |                |             |       |  |  |

| bit 6-5 | RP1:RP0: Register Bank Select bits (used for Direct addressing)<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes. The RP1 bit is reserved on the PIC16C55X, always maintain this bit clear. |                                            |         |            |          |                |             |       |  |  |

| bit 4   | TO: Timeout bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT timeout occurred                                                                                                                                                                        |                                            |         |            |          |                |             |       |  |  |

| bit 3   | <b>PD</b> : Power-down bit<br>1 = After power-up or by the CLRWDT instruction<br>0 = By execution of the SLEEP instruction                                                                                                                                                           |                                            |         |            |          |                |             |       |  |  |

| bit 2   | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                                                          |                                            |         |            |          |                |             |       |  |  |

| bit 1   | DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed) <ol> <li>A carry-out from the 4th low order bit of the result occurred</li> <li>No carry-out from the 4th low order bit of the result</li> </ol>                          |                                            |         |            |          |                |             |       |  |  |

| bit 0   | <b>C</b> : Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                               |                                            |         |            |          |                |             |       |  |  |

| Note 1: |                                                                                                                                                                                                                                                                                      | e polarity is reve<br>otate (RRF, RL<br>r. |         |            |          |                |             |       |  |  |

|         | Legend:                                                                                                                                                                                                                                                                              |                                            |         |            |          |                |             |       |  |  |

|         | R = Readable                                                                                                                                                                                                                                                                         | ə bit                                      | W = Wri | itable bit | U = Unim | plemented bit, | read as '0' |       |  |  |

- n = Value at POR reset

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

#### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

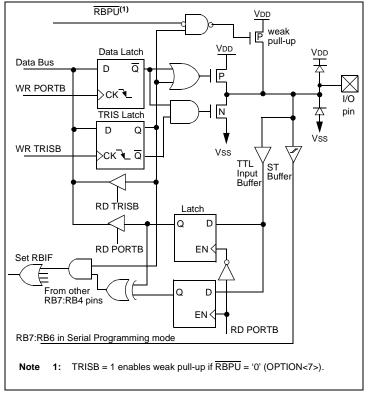

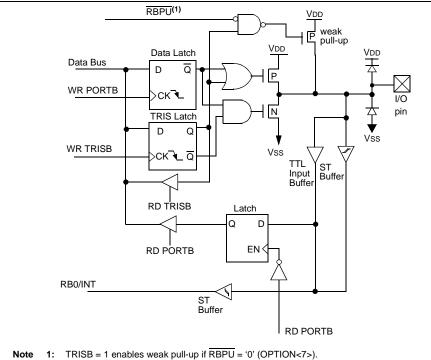

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (this will end the mismatch condition)

- Clear flag bit RBIF

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allows easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552 in the Microchip *Embedded Control Handbook*.)

**Note 1:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

### FIGURE 5-3: BLOCK DIAGRAM OF RB7:RB4 PINS

## TABLE 5-3: PORTB FUNCTIONS

| Name    | Bit # | Buffer Type           | Function                                                                                                                       |  |

|---------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| RB0/INT | Bit 0 | TTL/ST <sup>(1)</sup> | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |  |

| RB1     | Bit 1 | TTL                   | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |  |

| RB2     | Bit 2 | TTL                   | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |  |

| RB3     | Bit 3 | TTL                   | Bi-directional I/O port. Internal software programmable weak pull-up.                                                          |  |

| RB4     | Bit 4 | TTL                   | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up.                               |  |

| RB5     | Bit 5 | TTL                   | Bi-directional I/O port (with interrupt-on-change). Internal software programmabl weak pull-up.                                |  |

| RB6     | Bit 6 | TTL/ST <sup>(2)</sup> | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming clock pin. |  |

| RB7     | Bit 7 | TTL/ST <sup>(2)</sup> | Bi-directional I/O port (with interrupt-on-change). Internal software programmable weak pull-up. Serial programming data pin.  |  |

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

## TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB AND TRISB

| Address  | Name   | Bit 7  | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|----------|--------|--------|----------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h      | PORTB  | RB7    | RB6      | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx xxxx       | uuuu uuuu                       |

| 86h      | TRISB  | TRISB7 | TRISB6   | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h      | OPTION | RBPU   | INTEDG   | TOCS   | TOSE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 0BH, 8BH | INTCON | GIE    | Reserved | TOIE   | INTE   | BRIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

Legend: x = unknown, u = unchanged

Note 1: Shaded bits are not used by PORTB.

## 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

## 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

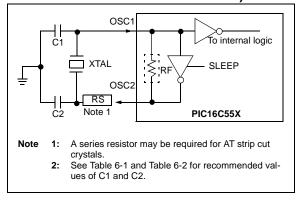

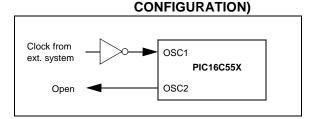

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

#### FIGURE 6-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

FIGURE 6-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

#### TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges                                                                                                                                       |                               |                                         |                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| Mode                                                                                                                                         | Freq                          | OSC1(C1)                                | OSC2(C2)                                |  |  |  |

| ХТ                                                                                                                                           | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |  |

| HS                                                                                                                                           | 8.0 MHz<br>16.0 MHz           | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |  |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design |                               |                                         |                                         |  |  |  |

| of the oscillator but also increases the    |

|---------------------------------------------|

| start-up time. These values are for design  |

| guidance only. Since each resonator has     |

| its own characteristics, the user should    |

| consult with the resonator manufacturer for |

| appropriate values of external compo-       |

| nents.                                      |

| TABLE 6-2: | <b>CAPACITOR SELECTION FOR</b> |

|------------|--------------------------------|

|            | CRYSTAL OSCILLATOR             |

|            | (PRELIMINARY)                  |

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC1(C1)                                | OSC2(C2)                                 |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------|--|--|--|

| LP      | 32 kHz<br>200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68 - 100 pF<br>15 - 30 pF               | 68 - 100 pF<br>15 - 30 pF                |  |  |  |

| XT      | 100 kHz<br>2 MHz<br>4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                              | 68 - 150 pF<br>15 - 30 pF<br>15 - 30 pF | 150 - 200 pF<br>15 - 30 pF<br>15 - 30 pF |  |  |  |

| HS      | 8 MHz<br>10 MHz<br>20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 - 30 pF<br>15 - 30 pF<br>15 - 30 pF  |                                          |  |  |  |

| Note 1: | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid over-<br>driving crystals with low-drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>with the crystal manufacturer for appropri-<br>ate values of external components. |                                         |                                          |  |  |  |

#### 6.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

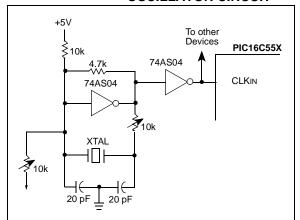

Either a pre-packaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 6-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 6-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

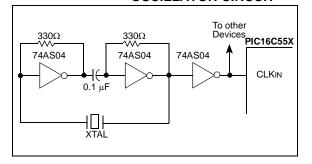

Figure 6-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The  $330\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 6-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

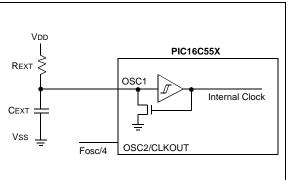

## 6.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 6-5 shows how the R/C combination is connected to the PIC16C55X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

## FIGURE 6-5: RC OSCILLATOR MODE

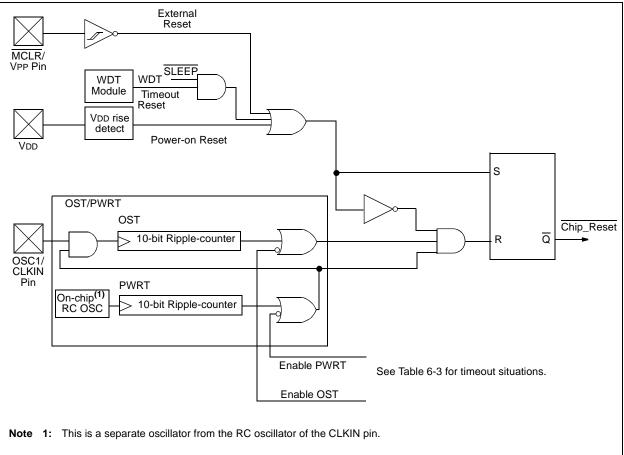

## 6.3 RESET

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers. A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

## 6.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST)

## 6.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.6V - 1.8V). To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607 "Power-up Trouble Shooting".

#### 6.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) timeout on power-up only, from POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the <u>VDD</u> to rise to an acceptable level. A configuration bit, <u>PWRTE</u> can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 6.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 6.4.4 TIMEOUT SEQUENCE

On power-up, the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired, then OST is activated. The total timeout will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no timeout at all. Figure 6-7, Figure 6-8 and Figure 6-9 depict timeout sequences.

Since the timeouts occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the timeouts will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 6-8). This is useful for testing purposes or to synchronize more than one PIC16C55X device operating in parallel.

Table 6-5 shows the RESET conditions for some special registers, while Table 6-6 shows the RESET conditions for all the registers.

## 6.9 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |

### 6.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify.

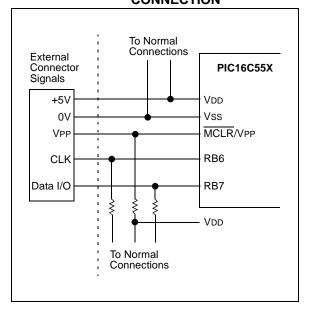

### 6.11 In-Circuit Serial Programming™

The PIC16C55X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RB6 and RB7 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After RESET, to place the device into Programming/ Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 6-15.

#### FIGURE 6-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT. Lines 5-7 are required only if the desired postscaler rate is 1:1 (PS<2:0> = 000) or 1:2 (PS<2:0> = 001).

| EXAMPLE 7-1: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (TIMER0→WDT)       |

| BCF   | STATUS, RPO          | ;Skip if already in      |

|-------|----------------------|--------------------------|

|       |                      | ;Bank 0 CLRWDT Clear WDT |

| CLRF  | TMR0                 | ;Clear TMR0 & Prescaler  |

| BSF   | STATUS, RPO          | ;Bank 1                  |

| MOVLW | '00101111 <i>'</i> b | ;These 3 lines (5, 6, 7) |

| MOVWF | OPTION               | ;Are required only if    |

|       |                      | ;Desired PS<2:0> are     |

|       |                      | ;CLRWDT 000 or 001       |

| MOVLW | '00101xxx'b          | ;Set Postscaler to       |

| MOVWF | OPTION               | ;Desired WDT rate        |

| BCF   | STATUS, RPO          | ;Return to Bank 0        |

|       |                      |                          |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        | (           | · / · ····=····     |

|--------|-------------|---------------------|

| CLRWDT |             | ;Clear WDT and      |

|        |             | ;prescaler          |

| BSF    | STATUS, RPO |                     |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| MOVWF  | OPTION      |                     |

| BCF    | STATUS, RPO |                     |

|        |             |                     |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6           | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-----------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 m | odule's registe | r     |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | Reserved        | TOIE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

| 81h     | OPTION | RBPU     | INTEDG          | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        | _               |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0',

**Note 1:** Shaded bits are not used by TMR0 module.

NOTES:

## TABLE 8-2: PIC16C55X INSTRUCTION SET

| Mnemo                          | onic,                            | Cycles                       |         | 14-Bit | Opcode | )    | Status | Neter       |       |  |  |  |

|--------------------------------|----------------------------------|------------------------------|---------|--------|--------|------|--------|-------------|-------|--|--|--|

|                                | Operands BYTE-ORIENTED FILE REGI |                              |         |        |        |      | LSb    | Affected    | Notes |  |  |  |

|                                |                                  | BYTE-ORIENTED FILE REGIS     | STER OF | PERAT  | IONS   |      |        |             |       |  |  |  |

| ADDWF                          | f, d                             | Add W and f                  | 1       | 00     | 0111   | dfff | ffff   | C,DC,Z      | 1,2   |  |  |  |

| ANDWF                          | f, d                             | AND W with f                 | 1       | 00     | 0101   | dfff | ffff   | Z           | 1,2   |  |  |  |

| CLRF                           | f                                | Clear f                      | 1       | 00     | 0001   | lfff | ffff   | Z           | 2     |  |  |  |

| CLRW                           | -                                | Clear W                      | 1       | 00     | 0001   | 0000 | 0011   | Z           |       |  |  |  |

| COMF                           | f, d                             | Complement f                 | 1       | 00     | 1001   | dfff | ffff   | Z           | 1,2   |  |  |  |

| DECF                           | f, d                             | Decrement f                  | 1       | 00     | 0011   | dfff | ffff   | Z           | 1,2   |  |  |  |

| DECFSZ                         | f, d                             | Decrement f, Skip if 0       | 1(2)    | 00     | 1011   | dfff | ffff   |             | 1,2,3 |  |  |  |

| INCF                           | f, d                             | Increment f                  | 1       | 00     | 1010   | dfff | ffff   | Z           | 1,2   |  |  |  |

| INCFSZ                         | f, d                             | Increment f, Skip if 0       | 1(2)    | 00     | 1111   | dfff | ffff   |             | 1,2,3 |  |  |  |

| IORWF                          | f, d                             | Inclusive OR W with f        | 1       | 00     | 0100   | dfff | ffff   | Z           | 1,2   |  |  |  |

| MOVF                           | f, d                             | Move f                       | 1       | 00     | 1000   | dfff | ffff   | Z           | 1,2   |  |  |  |

| MOVWF                          | f                                | Move W to f                  | 1       | 00     | 0000   | lfff | ffff   |             |       |  |  |  |

| NOP                            | -                                | No Operation                 | 1       | 00     | 0000   | 0xx0 | 0000   |             |       |  |  |  |

| RLF                            | f, d                             | Rotate Left f through Carry  | 1       | 00     | 1101   | dfff | ffff   | С           | 1,2   |  |  |  |

| RRF                            | f, d                             | Rotate Right f through Carry | 1       | 00     | 1100   | dfff | ffff   | С           | 1,2   |  |  |  |

| SUBWF                          | f, d                             | Subtract W from f            | 1       | 00     | 0010   | dfff | ffff   | C,DC,Z      | 1,2   |  |  |  |

| SWAPF                          | f, d                             | Swap nibbles in f            | 1       | 00     | 1110   | dfff | ffff   | , ,         | 1,2   |  |  |  |

| XORWF                          | f, d                             | Exclusive OR W with f        | 1       | 00     | 0110   | dfff | ffff   | Z           | 1,2   |  |  |  |

|                                |                                  | BIT-ORIENTED FILE REGIST     |         | RATION | IS     |      |        |             |       |  |  |  |

| BCF                            | f, b                             | Bit Clear f                  | 1       | 01     | 00bb   | bfff | ffff   |             | 1,2   |  |  |  |

| BSF                            | f, b                             | Bit Set f                    | 1       | 01     | 01bb   | bfff | ffff   |             | 1,2   |  |  |  |

| BTFSC                          | f, b                             | Bit Test f, Skip if Clear    | 1(2)    | 01     | 10bb   | bfff | ffff   |             | 3     |  |  |  |

| BTFSS                          | f, b                             | Bit Test f, Skip if Set      | 1(2)    | 01     | 11bb   | bfff | ffff   |             | 3     |  |  |  |

| LITERAL AND CONTROL OPERATIONS |                                  |                              |         |        |        |      |        |             |       |  |  |  |

| ADDLW                          | k                                | Add literal and W            | 1       | 11     | 111x   | kkkk | kkkk   | C,DC,Z      |       |  |  |  |

| ANDLW                          | k                                | AND literal with W           | 1       | 11     | 1001   | kkkk | kkkk   | Z           |       |  |  |  |

| CALL                           | k                                | Call subroutine              | 2       | 10     | 0kkk   | kkkk | kkkk   |             |       |  |  |  |

| CLRWDT                         | -                                | Clear Watchdog Timer         | 1       | 00     | 0000   | 0110 | 0100   | TO,PD       |       |  |  |  |

| GOTO                           | k                                | Go to address                | 2       | 10     | 1kkk   | kkkk | kkkk   |             |       |  |  |  |

| IORLW                          | k                                | Inclusive OR literal with W  | 1       | 11     | 1000   | kkkk | kkkk   | Z           |       |  |  |  |

| MOVLW                          | k                                | Move literal to W            | 1       | 11     | 00xx   | kkkk | kkkk   |             |       |  |  |  |

| RETFIE                         | -                                | Return from interrupt        | 2       | 00     | 0000   | 0000 | 1001   |             |       |  |  |  |

| RETLW                          | k                                | Return with literal in W     | 2       | 11     | 01xx   | kkkk | kkkk   |             |       |  |  |  |

| RETURN                         | -                                | Return from Subroutine       | 2       | 00     | 0000   | 0000 | 1000   |             |       |  |  |  |

| SLEEP                          | -                                | Go into Standby mode         | 1       | 00     | 0000   | 0110 | 0011   | TO,PD       |       |  |  |  |

| SUBLW                          | k                                | Subtract W from literal      | 1       | 11     |        | kkkk |        | C,DC,Z      |       |  |  |  |

| XORLW                          | k                                | Exclusive OR literal with W  | 1       | 11     |        | kkkk |        | Ζ           |       |  |  |  |

|                                |                                  |                              |         |        |        |      |        | - 44-04-1-0 |       |  |  |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

## 9.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

## 9.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

## 9.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 9.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 9.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

#### TABLE 9-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                                      | PIC12CXX | PIC14000 | PIC16C5X | PIC16C6X | PIC16CXX | PIC16F62) | AT281219   | PIC16C7X | PIC16C8X | PIC16F8X) | PIC16C9X) | X4271219 | (XTOTIOI9 | PIC18CXX | PIC18FXX) | 83CXX<br>52CXX/<br>54CXX/ | хххээн | МСКЕХХХ | MCP2510 |

|----------------------------------------------------------------------|----------|----------|----------|----------|----------|-----------|------------|----------|----------|-----------|-----------|----------|-----------|----------|-----------|---------------------------|--------|---------|---------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment             | >        | ^        | ^        | >        | ~        | >         | >          | >        | >        | >         | >         | >        | >         | >        | >         |                           |        |         |         |

| MPLAB <sup>®</sup> C17 C Compiler                                    |          |          |          |          |          |           |            |          |          |           |           | >        | ~         |          |           |                           |        |         |         |

| MPLAB <sup>®</sup> C18 C Compiler                                    |          |          |          |          |          |           |            |          |          |           |           |          |           | >        | ~         |                           |        |         |         |

| MPASM <sup>TM</sup> Assembler/<br>MPLINK <sup>TM</sup> Object Linker | >        | `        | ^        | >        | ~        | >         | >          | >        | >        | >         | >         | >        | >         | >        | >         | >                         | >      |         |         |

| MPLAB® ICE In-Circuit Emulator                                       | r <      | >        | >        | >        | >        | **`^      | >          | >        | >        | >         | >         | >        | >         | >        | >         |                           |        |         |         |

| ICEPICTM In-Circuit Emulator                                         | >        |          | >        | >        | >        |           | >          | >        | >        |           | >         |          |           |          |           |                           |        |         |         |

| eb<br>MPLAB® ICD In-Circuit<br>Debugger                              |          |          |          | *>       |          |           | *>         |          |          | >         |           |          |           |          | >         |                           |        |         |         |

| PICSTART <sup>®</sup> Plus Entry Level<br>Development Programmer     | >        | ~        | `        | `        | `        | **`       | `          | `        | ~        | `         | >         | >        | >         | >        | >         |                           |        |         |         |

| PRO MATE® II<br>Universal Device Programmer                          | >        | >        | >        | ~        | ~        | **/       | >          | >        | ^        | >         | >         | >        | >         | >        | >         | >                         | ^      |         |         |

| PICDEM <sup>TM</sup> 1 Demonstration<br>Board                        |          |          | >        |          | >        |           | + <b>-</b> |          | >        |           |           | >        |           |          |           |                           |        |         |         |

| PICDEM <sup>TM</sup> 2 Demonstration<br>Board                        |          |          |          | .↓       |          |           | ÷+         |          |          |           |           |          |           | >        | >         |                           |        |         |         |

| PICDEM <sup>TM</sup> 3 Demonstration<br>Board                        |          |          |          |          |          |           |            |          |          |           | >         |          |           |          |           |                           |        |         |         |

| PICDEM <sup>TM</sup> 14A Demonstration<br>Board                      |          | >        |          |          |          |           |            |          |          |           |           |          |           |          |           |                           |        |         |         |

| PICDEM <sup>TM</sup> 17 Demonstration<br>Board                       |          |          |          |          |          |           |            |          |          |           |           |          | >         |          |           |                           |        |         |         |

| KEELoα <sup>®</sup> Evaluation Kit                                   |          |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           | >      |         |         |

| KEELoq <sup>®</sup> Transponder Kit                                  |          |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           | >      |         |         |

| microlD <sup>TM</sup> Programmer's Kit                               |          |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           |        | ~       |         |

| 125 kHz microlD™<br>Developer's Kit                                  |          |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           |        | >       |         |

| 125 kHz Anticollision microlD™<br>Developer's Kit                    | v        |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           |        | >       |         |

| 13.56 MHz Anticollision<br>microlD <sup>TM</sup> Developer's Kit     |          |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           |        | >       |         |

| MCP2510 CAN Developer's Kit                                          |          |          |          |          |          |           |            |          |          |           |           |          |           |          |           |                           |        |         | >       |

$\ensuremath{\textcircled{}^{\circ}}$  1996-2013 Microchip Technology Inc.

NOTES:

## 10.2 DC Characteristics: PIC16C55X (Commercial, Industrial, Extended) PIC16LC55X(Commercial, Industrial, Extended)

| DC Cha        | racteris | tics                                        | Standard Ope<br>Operating tem | -      | re -40°C ≤ T<br>0°C ≤ T | A ≤ +8<br>īA ≤ +7 | <b>s otherwise stated)</b><br>5°C for industrial and<br>70°C for commercial and<br>25°C for automotive |

|---------------|----------|---------------------------------------------|-------------------------------|--------|-------------------------|-------------------|--------------------------------------------------------------------------------------------------------|

|               |          | 1                                           | Operating volt                | age Vo | D range as de           | scribed           | d in DC spec Table 10-1                                                                                |

| Param.<br>No. | Sym      | Characteristic                              | Min                           | Тур†   | Max                     | Unit              | Conditions                                                                                             |

|               | VIL      | Input Low Voltage                           |                               |        |                         |                   |                                                                                                        |

|               |          | I/O ports                                   |                               |        |                         |                   |                                                                                                        |

| D030          |          | with TTL buffer                             | Vss                           | _      | 0.8V<br>0.15 Vdd        | V                 | VDD = 4.5V to 5.5V<br>otherwise                                                                        |

| D031          |          | with Schmitt Trigger input                  | Vss                           |        | 0.2 Vdd                 | V                 |                                                                                                        |

| D032          |          | MCLR, RA4/T0CKI,OSC1 (in RC mode)           | Vss                           | _      | 0.2 VDD                 | V                 | (Note1)                                                                                                |

| D033          |          | OSC1 (in XT* and HS)                        | Vss                           | —      | 0.3 VDD                 | V                 |                                                                                                        |

|               |          | OSC1 (in LP*)                               | Vss                           | —      | 0.6 Vdd-1.0             | V                 |                                                                                                        |

|               | Vін      | Input High Voltage                          |                               |        |                         |                   |                                                                                                        |

|               |          | I/O ports                                   |                               | —      |                         |                   |                                                                                                        |

| D040          |          | with TTL buffer                             | 2.0V<br>0.8 + 0.25 VDD        | _      | Vdd<br>Vdd              | V<br>V            | VDD = 4.5V to 5.5V<br>otherwise                                                                        |

| D041          |          | with Schmitt Trigger input                  | 0.8V                          |        | Vdd                     |                   |                                                                                                        |

| D042          |          | MCLR RA4/T0CKI                              | 0.8 Vdd                       | —      | Vdd                     | V                 |                                                                                                        |

| D043<br>D043A |          | OSC1 (XT*, HS and LP*)<br>OSC1 (in RC mode) | 0.7 Vdd<br>0.9 Vdd            | —      | Vdd                     | V                 | (Note1)                                                                                                |

| D070          | Ipurb    | PORTB weak pull-up current                  | 50                            | 200    | 400                     | μΑ                | VDD = 5.0V, VPIN = VSS                                                                                 |

|               | lı∟      | Input Leakage Current <sup>(2)(3)</sup>     |                               |        |                         |                   |                                                                                                        |

|               |          | I/O ports (Except PORTA)                    |                               |        | ±1.0                    | μΑ                | $Vss \le VPIN \le VDD, \text{ pin at hi-impedance}$                                                    |

| D060          |          | PORTA                                       | —                             | —      | ±0.5                    | μA                | $Vss \le VPIN \le VDD, pin at hi-impedance$                                                            |

| D061          |          | RA4/T0CKI                                   | —                             | —      | ±1.0                    | μΑ                | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                               |

| D063          |          | OSC1, MCLR                                  | —                             | —      | ±5.0                    | μΑ                | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration                                            |

|               | Vol      | Output Low Voltage                          |                               |        |                         |                   |                                                                                                        |

| D080          |          | I/O ports                                   | —                             | —      | 0.6                     | V                 | IOL=8.5 mA, VDD=4.5V, -40° to<br>+85°C                                                                 |

|               |          |                                             | —                             | —      | 0.6                     | V                 | IOL=7.0 mA, VDD=4.5V, +125°C                                                                           |

| D083          |          | OSC2/CLKOUT                                 | _                             | —      | 0.6                     | V                 | IOL=1.6 mA, VDD=4.5V, -40° to<br>+85°C                                                                 |

|               |          | (RC only)                                   | —                             | —      | 0.6                     | V                 | IOL=1.2 mA, VDD=4.5V, +125°C                                                                           |

|               | Vон      | Output High Voltage <sup>(3)</sup>          |                               |        |                         |                   |                                                                                                        |

| D090          |          | I/O ports (Except RA4)                      | VDD-0.7                       | —      | _                       | V                 | IOH=-3.0 mA, VDD=4.5V, -40° to<br>+85°C                                                                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16C55X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

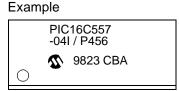

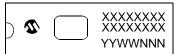

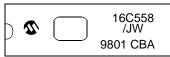

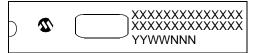

## Package Marking Information (Cont'd)

#### Example PIC16C558 -04I / S0218 S0218 9818 CDK

$\cap$

##

### 18-Lead CERDIP Windowed

#### Example

### 28-Lead CERDIP Windowed

Example

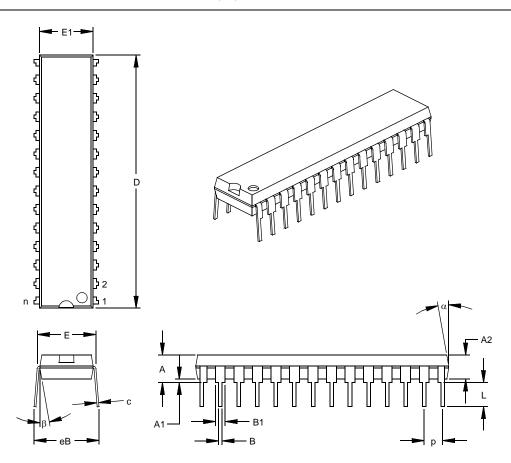

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| ision L | n  | MIN                                                                                                              | NOM                                                    | MAX                                                     | MIN                                                    | NOM                                                    | MAX                                                     |

|---------|----|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

|         |    |                                                                                                                  |                                                        |                                                         |                                                        |                                                        | INIAA                                                   |

|         | -  |                                                                                                                  | 28                                                     |                                                         |                                                        | 28                                                     |                                                         |

|         | р  |                                                                                                                  | .100                                                   |                                                         |                                                        | 2.54                                                   |                                                         |

|         | Α  | .140                                                                                                             | .150                                                   | .160                                                    | 3.56                                                   | 3.81                                                   | 4.06                                                    |

|         | A2 | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|         | A1 | .015                                                                                                             |                                                        |                                                         | 0.38                                                   |                                                        |                                                         |

|         | Е  | .300                                                                                                             | .310                                                   | .325                                                    | 7.62                                                   | 7.87                                                   | 8.26                                                    |

|         | E1 | .275                                                                                                             | .285                                                   | .295                                                    | 6.99                                                   | 7.24                                                   | 7.49                                                    |

|         | D  | 1.345                                                                                                            | 1.365                                                  | 1.385                                                   | 34.16                                                  | 34.67                                                  | 35.18                                                   |

|         | L  | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|         | С  | .008                                                                                                             | .012                                                   | .015                                                    | 0.20                                                   | 0.29                                                   | 0.38                                                    |

|         | B1 | .040                                                                                                             | .053                                                   | .065                                                    | 1.02                                                   | 1.33                                                   | 1.65                                                    |

|         | В  | .016                                                                                                             | .019                                                   | .022                                                    | 0.41                                                   | 0.48                                                   | 0.56                                                    |

| §       | eB | .320                                                                                                             | .350                                                   | .430                                                    | 8.13                                                   | 8.89                                                   | 10.92                                                   |

|         | α  | 5                                                                                                                | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

|         | β  | 5                                                                                                                | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

|         | Ş  | A           A2           A1           E           D           L           C           B1           §           α | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070