#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 80 × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

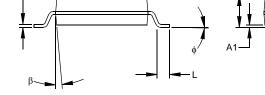

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554-04e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 4.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources.

| Note: | Interrupt flag bits get set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs regardless of the state of   |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE (INTCON<7>).                  |

| REGISTER 4-3: | INTCON REGISTER (ADDRESS 0BH OR 8BH)                                                                                                                    |                                                                                                                                       |              |              |            |            |                 |        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------|------------|-----------------|--------|

|               | R/W-0                                                                                                                                                   | Reserved                                                                                                                              | R/W-0        | R/W-0        | R/W-0      | R/W-0      | R/W-0           | R/W-x  |

|               | GIE                                                                                                                                                     | —                                                                                                                                     | T0IE         | INTE         | RBIE       | T0IF       | INTF            | RBIF   |

|               | bit7                                                                                                                                                    |                                                                                                                                       |              |              |            |            |                 | bit0   |

|               |                                                                                                                                                         |                                                                                                                                       |              |              |            |            |                 |        |

| bit 7         | GIE: Global                                                                                                                                             | Interrupt Ena                                                                                                                         | ble bit      |              |            |            |                 |        |

|               |                                                                                                                                                         | s all un-maske<br>s all interrupts                                                                                                    |              | 5            |            |            |                 |        |

| bit 6         | Reserved:                                                                                                                                               | For future use                                                                                                                        | . Always m   | aintain this | bit clear. |            |                 |        |

| bit 5         | TOIE: TMR(                                                                                                                                              | Overflow Inte                                                                                                                         | errupt Enab  | le bit       |            |            |                 |        |

|               |                                                                                                                                                         | s the TMR0 int<br>s the TMR0 in                                                                                                       |              |              |            |            |                 |        |

| bit 4         | INTE: RB0/                                                                                                                                              | INT External I                                                                                                                        | nterrupt En  | able bit     |            |            |                 |        |

|               |                                                                                                                                                         | s the RB0/INT<br>s the RB0/INT                                                                                                        |              | •            |            |            |                 |        |

| bit 3         | RBIE: RB P                                                                                                                                              | ort Change In                                                                                                                         | terrupt Ena  | ble bit      |            |            |                 |        |

|               |                                                                                                                                                         | s the RB port of s the RB port of the | 0            |              |            |            |                 |        |

| bit 2         | TOIF: TMRC                                                                                                                                              | Overflow Inte                                                                                                                         | errupt Flag  | bit          |            |            |                 |        |

|               | <ul><li>1 = TMR0 register has overflowed (must be cleared in software)</li><li>0 = TMR0 register did not overflow</li></ul>                             |                                                                                                                                       |              |              |            |            |                 |        |

| bit 1         | INTF: RB0/                                                                                                                                              | INT External li                                                                                                                       | nterrupt Fla | g bit        |            |            |                 |        |

|               | <ul> <li>1 = The RB0/INT external interrupt occurred (must be cleared in software)</li> <li>0 = The RB0/INT external interrupt did not occur</li> </ul> |                                                                                                                                       |              |              |            |            |                 |        |

| bit 0         | RBIF: RB Port Change Interrupt Flag bit                                                                                                                 |                                                                                                                                       |              |              |            |            |                 |        |

|               | 1 = When at least one of the RB7:RB4 pins changed state (must be cleared in software)                                                                   |                                                                                                                                       |              | re)          |            |            |                 |        |

|               | 0 = None of                                                                                                                                             | the RB7:RB4                                                                                                                           | pins have    | changed sta  | ate        |            |                 |        |

|               | Legend:                                                                                                                                                 |                                                                                                                                       |              |              |            |            |                 |        |

|               | R = Readat                                                                                                                                              | ole bit                                                                                                                               | W = W        | ritable bit  | U = Unir   | nplemented | bit, read as '( | )'     |

|               | - n = Value                                                                                                                                             | at POR reset                                                                                                                          | '1' = Bit    | t is set     | '0' = Bit  | is cleared | x = Bit is u    | nknown |

## REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

© 1996-2013 Microchip Technology Inc.

## 5.4 I/O Programming Considerations

### 5.4.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-1 shows the effect of two sequential read-modify-write instructions (ex.,  ${\tt BCF}$ ,  ${\tt BSF}$ , etc.) on an I/O port.

A pin actively outputting a low or high should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

## 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

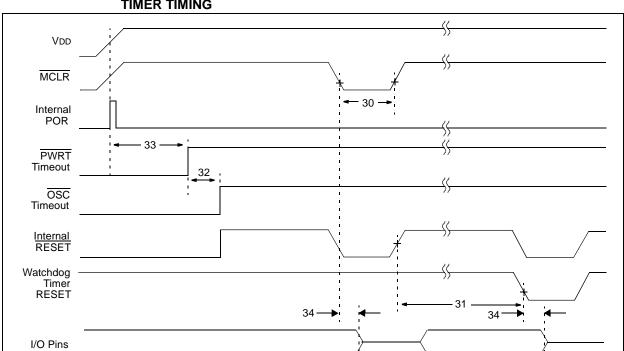

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

## 6.2 Oscillator Configurations

### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

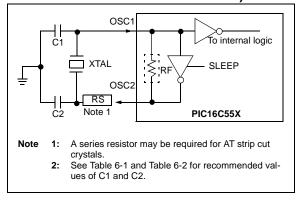

# 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

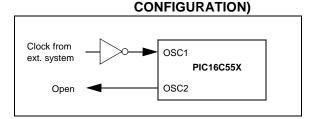

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

### FIGURE 6-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

FIGURE 6-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC

### TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges                                                                                                                                       |                               |                                         |                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------------------------------|

| Mode                                                                                                                                         | Freq                          | OSC1(C1)                                | OSC2(C2)                                |

| ХТ                                                                                                                                           | 455 kHz<br>2.0 MHz<br>4.0 MHz | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 22 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |

| HS                                                                                                                                           | 8.0 MHz<br>16.0 MHz           | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design |                               |                                         |                                         |

| of the oscillator but also increases the    |

|---------------------------------------------|

| start-up time. These values are for design  |

| guidance only. Since each resonator has     |

| its own characteristics, the user should    |

| consult with the resonator manufacturer for |

| appropriate values of external compo-       |

| nents.                                      |

| TABLE 6-2: | CAPACITOR SELECTION FOR |

|------------|-------------------------|

|            | CRYSTAL OSCILLATOR      |

|            | (PRELIMINARY)           |

| Mode    | Freq                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC1(C1)    | OSC2(C2)     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|

| LP      | 32 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 - 100 pF | 68 - 100 pF  |

|         | 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 - 30 pF  | 15 - 30 pF   |

| XT      | 100 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68 - 150 pF | 150 - 200 pF |

|         | 2 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |

|         | 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |

| HS      | 8 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15 - 30 pF  | 15 - 30 pF   |

|         | 10 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |

|         | 20 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 - 30 pF  | 15 - 30 pF   |

| Note 1: | Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Rs may be required in HS<br>mode as well as XT mode to avoid over-<br>driving crystals with low-drive level specifi-<br>cation. Since each crystal has its own<br>characteristics, the user should consult<br>with the crystal manufacturer for appropri-<br>ate values of external components. |             |              |

# **PIC16C55X**

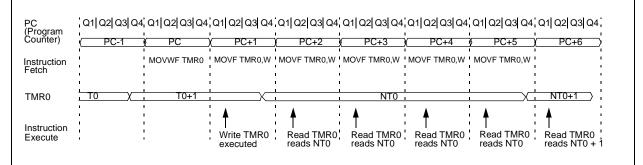

T0IF interrupt flag is sampled here (every Q1). Note 1:

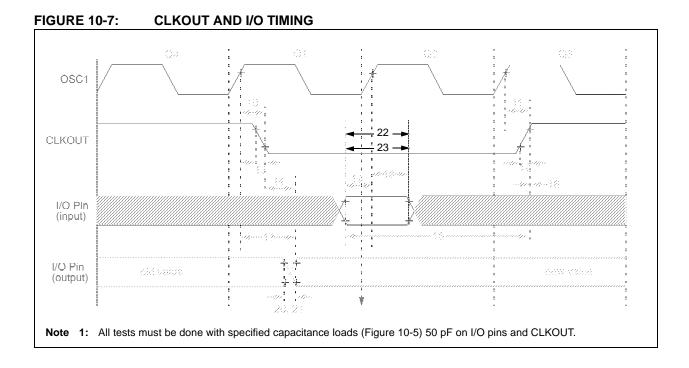

Interrupt latency = 4 Tcr, where Tcr = instruction cycle time. CLKOUT is available only in RC Oscillator mode. 2:

3:

# 8.0 INSTRUCTION SET SUMMARY

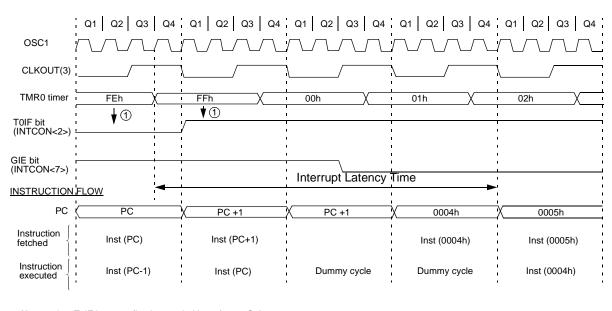

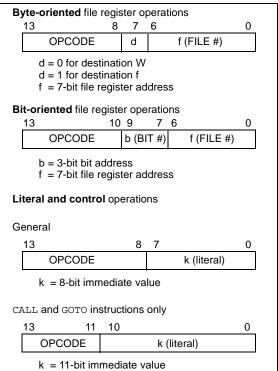

Each PIC16C55X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C55X instruction set summary in Table 8-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 8-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field         | Description                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                                              |

| x             | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It<br>is the recommended form of use for compatibil-<br>ity with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                       |

| label         | Label name                                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                                             |

| то            | Timeout bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                                          |

| [ ]           | Options                                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                                 |

| ∈             | In the set of                                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 8-1 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 8-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16C55X

| BCF              | Bit Clea                           | ar f          |            |          |

|------------------|------------------------------------|---------------|------------|----------|

| Syntax:          | [ label ]                          | BCF 1         | f,b        |          |

| Operands:        | $0 \le f \le 1$<br>$0 \le b \le 1$ |               |            |          |

| Operation:       | $0 \rightarrow (f < $              | b>)           |            |          |

| Status Affected: | None                               |               |            |          |

| Encoding:        | 01                                 | 00bb          | bfff       | ffff     |

| Description:     | Bit 'b' in re                      | gister 'f' is | s cleared. |          |

| Words:           | 1                                  |               |            |          |

| Cycles:          | 1                                  |               |            |          |

| Example          | BCF                                | FLAG_F        | REG, 7     |          |

|                  | After Inst                         | G_REG         |            | C7<br>47 |

|  | Bit | Set | f |

|--|-----|-----|---|

|--|-----|-----|---|

BSF

| Syntax:          | [ <i>label</i> ]BSF f,b                                            |               |        |      |

|------------------|--------------------------------------------------------------------|---------------|--------|------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | 7             |        |      |

| Operation:       | $1 \rightarrow (f < b;$                                            | >)            |        |      |

| Status Affected: | None                                                               |               |        |      |

| Encoding:        | 01                                                                 | 01bb          | bfff   | ffff |

| Description:     | Bit 'b' in re                                                      | gister 'f' is | s set. |      |

| Words:           | 1                                                                  |               |        |      |

| Cycles:          | 1                                                                  |               |        |      |

| Example          | BSF                                                                | FLAG_F        | REG, 7 | ,    |

|                  | Before In<br>FLA<br>After Inst                                     | G_REG         |        | 0A   |

|                  | FLAG                                                               | G_REG         | = 0x   | 8A   |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                 |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                     |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                     |  |  |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                                                                 |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                    |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                       |  |  |

| Description:     | If bit 'b' in register 'f' is '0' then the next<br>instruction is skipped. If bit 'b' is '0' then<br>the next instruction fetched during the<br>current instruction execution is dis-<br>carded, and a NOP is executed instead,<br>making this a two-cycle instruction. |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                       |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                    |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•<br>•                                                                                                                                                                                                        |  |  |

|                  | Before Instruction                                                                                                                                                                                                                                                      |  |  |

|                  | PC = address HERE                                                                                                                                                                                                                                                       |  |  |

|                  | After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1> = 1,                                                                                                                                                                                            |  |  |

|                  | PC = address FALSE                                                                                                                                                                                                                                                      |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE+1                                                                                                                                                             |  |  |  |  |  |  |  |  |

| GOTO                                                                                | Unconditional Branch                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:                                                                             | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Operands:                                                                           | $0 \le k \le 2047$                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Operation:                                                                          | $k \rightarrow PC < 10:0 >$                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|                                                                                     | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Status Affected:                                                                    | None                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| Encoding:                                                                           | 10 lkkk kkkk kkkk                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Description:                                                                        | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.                                                                              |  |  |  |  |  |  |  |  |  |

| Words:                                                                              | 1                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Cycles:                                                                             | 2                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| Example                                                                             | GOTO THERE                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|                                                                                     | After Instruction                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| INCF                                                                                | PC = Address THERE                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| _                                                                                   | Increment f                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| INCF<br>Syntax:<br>Operands:                                                        |                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Syntax:                                                                             | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                  | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest)                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Increment f[ label ] INCF f,d $0 \le f \le 127$ $d \in [0,1]$ (f) + 1 $\rightarrow$ (dest)Z001010dffffffThe contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the                                            |  |  |  |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Increment f[ label ]INCF f,d $0 \le f \le 127$ $d \in [0,1]$ $(f) + 1 \rightarrow (dest)$ Z001010dfffffffThe contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the<br>result is placed back in register 'f'. |  |  |  |  |  |  |  |  |  |

INCF CNT, 1 Before Instruction CNT = 0xFFZ = 0After Instruction CNT = 0x00Z = 1

| RRF               | Rotate Right f through Carry                                                                                                                                                                                 |                                               |                  |                    |             |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|--------------------|-------------|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                    | RRF 1                                         | ,d               |                    |             |  |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                           |                                               |                  |                    |             |  |  |  |  |  |

| Operation:        | See desc                                                                                                                                                                                                     | ription b                                     | below            |                    |             |  |  |  |  |  |

| Status Affected:  | С                                                                                                                                                                                                            |                                               |                  |                    |             |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                           | 1100                                          | dff              | f                  | ffff        |  |  |  |  |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                                               |                  |                    |             |  |  |  |  |  |

|                   | C Register f                                                                                                                                                                                                 |                                               |                  |                    |             |  |  |  |  |  |

|                   |                                                                                                                                                                                                              |                                               | Regist           | ter f              | ┠┺          |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                            |                                               | Regist           | ter f              | ]•          |  |  |  |  |  |

| Words:<br>Cycles: | 1<br>1                                                                                                                                                                                                       | ]-▶[                                          | Regist           | ter f              | <b>]•</b> ] |  |  |  |  |  |

|                   | •                                                                                                                                                                                                            | ]-•[                                          |                  | ter f              | <b>]</b> •] |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                            |                                               | REG              |                    | <u>}</u>    |  |  |  |  |  |

| Cycles:           | 1<br>RRF                                                                                                                                                                                                     | struction                                     | REG              | \$1,0              | .0          |  |  |  |  |  |

| Cycles:           | 1<br>RRF<br>Before Ins                                                                                                                                                                                       | struction                                     | REG<br>n<br>1110 | \$1,0              | .0          |  |  |  |  |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG                                                                                                                                                                                 | struction<br>1 = 1<br>= (                     | REG<br>n<br>1110 | \$1,0              | .0          |  |  |  |  |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG<br>C                                                                                                                                                                            | struction<br>1 = 1<br>= 0<br>ruction          | REG<br>n<br>1110 | \$1,0              | -           |  |  |  |  |  |

| Cycles:           | 1<br>RRF<br>Before Ins<br>REG<br>C<br>After Instr                                                                                                                                                            | struction<br>1 = 2<br>= 0<br>ruction<br>1 = 2 | REG<br>N<br>L110 | ;1,0<br>011<br>011 | .0          |  |  |  |  |  |

## SLEEP

| Syntax:          | [ <i>label</i><br>]                                                                                                                                                                                                                                       | SLEEP |      |      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|--|--|

| Operands:        | None                                                                                                                                                                                                                                                      |       |      |      |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                |       |      |      |  |  |  |  |

| Status Affected: | $\overline{\text{TO}}, \overline{\text{PD}}$                                                                                                                                                                                                              |       |      |      |  |  |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                        | 0000  | 0110 | 0011 |  |  |  |  |

| Description:     | The power-down status bit, <u>PD</u> is<br>cleared. Timeout status bit, <u>TO</u> is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 6.8 for more details |       |      |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                         |       |      |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                         |       |      |      |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                     |       |      |      |  |  |  |  |

| SUBLW               | Subtract W from Literal                       |                           |             |             |  |  |  |  |  |  |

|---------------------|-----------------------------------------------|---------------------------|-------------|-------------|--|--|--|--|--|--|

| Syntax:             | [ <i>label</i> ] SUBLW k                      |                           |             |             |  |  |  |  |  |  |

| Operands:           | $0 \leq k \leq 255$                           |                           |             |             |  |  |  |  |  |  |

| Operation:          | k - (W) → (                                   | $k - (W) \rightarrow (W)$ |             |             |  |  |  |  |  |  |

| Status<br>Affected: | C, DC, Z                                      |                           |             |             |  |  |  |  |  |  |

| Encoding:           | 11                                            | 110x                      | kkkk        | kkkk        |  |  |  |  |  |  |

| Description:        | The W regist<br>plement met<br>'k'. The resul | hod) fror                 | n the eight | bit literal |  |  |  |  |  |  |

| Words:              | 1                                             |                           |             |             |  |  |  |  |  |  |

| Cycles:             | 1                                             |                           |             |             |  |  |  |  |  |  |

| Example 1:          | SUBLW                                         | 0x02                      |             |             |  |  |  |  |  |  |

|                     | Before Inst                                   | ruction                   |             |             |  |  |  |  |  |  |

|                     | W                                             | = 1                       |             |             |  |  |  |  |  |  |

|                     | С                                             | = ?                       | <b>)</b>    |             |  |  |  |  |  |  |

|                     | After Instru                                  | ction                     |             |             |  |  |  |  |  |  |

|                     | W                                             | = 1                       |             |             |  |  |  |  |  |  |

|                     | С                                             | = 1                       | ; result is | positive    |  |  |  |  |  |  |

| Example 2:          | Before Inst                                   | ruction                   |             |             |  |  |  |  |  |  |

|                     | W                                             | = 2                       | 2           |             |  |  |  |  |  |  |

|                     | С                                             | = ?                       | )           |             |  |  |  |  |  |  |

|                     | After Instru                                  | ction                     |             |             |  |  |  |  |  |  |

|                     | W                                             | = 0                       | )           |             |  |  |  |  |  |  |

|                     | С                                             | = 1                       | ; result is | s zero      |  |  |  |  |  |  |

| Example 3:          | Before Inst                                   | ruction                   |             |             |  |  |  |  |  |  |

|                     | W                                             | = 3                       | 3           |             |  |  |  |  |  |  |

|                     | С                                             | = ?                       | )           |             |  |  |  |  |  |  |

|                     | After Instru                                  | ction                     |             |             |  |  |  |  |  |  |

|                     | W                                             |                           | )xFF        |             |  |  |  |  |  |  |

|                     | C                                             | = 0                       | ); result i | s nega-     |  |  |  |  |  |  |

tive

$\odot$  1996-2013 Microchip Technology Inc.

| XORLW            | Exclusive OR Literal with W                                                                                       |                       |      |      |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                          |                       |      |      |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 25$                                                                                                  | 5                     |      |      |  |  |  |  |  |  |

| Operation:       | (W) .XOR                                                                                                          | $k$ . k → ( $\lambda$ | N)   |      |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                 |                       |      |      |  |  |  |  |  |  |

| Encoding:        | 11                                                                                                                | 1010                  | kkkk | kkkk |  |  |  |  |  |  |

| Description:     | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. |                       |      |      |  |  |  |  |  |  |

| Words:           | 1                                                                                                                 |                       |      |      |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                 |                       |      |      |  |  |  |  |  |  |

| Example:         | XORLW                                                                                                             | 0xAF                  |      |      |  |  |  |  |  |  |

|                  | Before In:                                                                                                        | structior             | ı    |      |  |  |  |  |  |  |

|                  | W                                                                                                                 | =                     | 0xB5 |      |  |  |  |  |  |  |

|                  | After Inst                                                                                                        | ruction               |      |      |  |  |  |  |  |  |

|                  | W                                                                                                                 | =                     | 0x1A |      |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0110 dfff ffff                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Example          | XORWF REG 1                                                                                                                                                                           |  |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                  | REG = 0xAF<br>W = 0xB5                                                                                                                                                                |  |  |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                  | REG = 0x1A                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|                  | W = 0xB5                                                                                                                                                                              |  |  |  |  |  |  |  |  |

$\odot$  1996-2013 Microchip Technology Inc.

## 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Cha        | racterist |                                               |            |      | ure -4     | litions (unless otherwise stated)<br>$0^{\circ}C \le TA \le +85^{\circ}C$ for industrial and<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for commercial and<br>$0^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                                           |

|---------------|-----------|-----------------------------------------------|------------|------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Param<br>No.  | Sym       | Characteristic                                | Min        | Тур† | Max        | Units                                                                                                                                                                                                         | Conditions                                                                                |

|               | Vdd       | Supply Voltage                                |            |      |            |                                                                                                                                                                                                               |                                                                                           |

| D001          |           | 16LC55X                                       | 3.0<br>2.5 | _    | 5.5<br>5.5 | V                                                                                                                                                                                                             | XT and RC osc configuration<br>LP osc configuration                                       |

| D001<br>D001A |           | 16C55X                                        | 3.0<br>4.5 |      | 5.5<br>5.5 | V<br>V                                                                                                                                                                                                        | XT, RC and LP osc configuration<br>HS osc configuration                                   |

| D002          | Vdr       | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —          | 1.5* | —          | V                                                                                                                                                                                                             | Device in SLEEP mode                                                                      |

| D003          | VPOR      | VDD Start Voltage to<br>ensure Power-on Reset | —          | Vss  | —          | V                                                                                                                                                                                                             | See Section 6.4, Power-on Reset for details                                               |

| D004          | SVDD      | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _    | —          | V/ms                                                                                                                                                                                                          | See Section 6.4, Power-on Reset for details                                               |

|               | Idd       | Supply Current <sup>(2)</sup>                 |            |      |            |                                                                                                                                                                                                               |                                                                                           |

| D010          |           | 16LC55X                                       | _          | 1.4  | 2.5        | mA                                                                                                                                                                                                            | XT and RC osc configuration<br>Fosc = 2.0 MHz, VDD = 3.0V, WDT<br>disabled <sup>(4)</sup> |