Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |  |

|----------------------------|-----------------------------------------------------------------------------|--|

| Product Status             | Obsolete                                                                    |  |

| Core Processor             | PIC                                                                         |  |

| Core Size                  | 8-Bit                                                                       |  |

| Speed                      | 4MHz                                                                        |  |

| Connectivity               | -                                                                           |  |

| Peripherals                | POR, WDT                                                                    |  |

| Number of I/O              | 13                                                                          |  |

| Program Memory Size        | 896B (512 x 14)                                                             |  |

| Program Memory Type        | OTP                                                                         |  |

| EEPROM Size                | -                                                                           |  |

| RAM Size                   | 80 x 8                                                                      |  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |  |

| Data Converters            | •                                                                           |  |

| Oscillator Type            | External                                                                    |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |  |

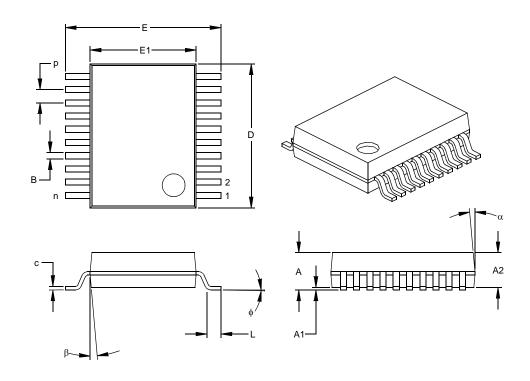

| Mounting Type              | Surface Mount                                                               |  |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |  |

| Supplier Device Package    | 20-SSOP                                                                     |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554-04e-ss |  |

#### **Special Microcontroller Features:**

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code protection

- · Power saving SLEEP mode

- · Selectable oscillator options

- Serial in-circuit programming (via two pins)

- Four user programmable ID locations

Note: For additional information on enhancements, see Appendix A

#### **CMOS Technology:**

- Low power, high speed CMOS EPROM technology

- · Fully static design

- Wide operating voltage range

- 2.5V to 5.5V

- Commercial, Industrial and Extended temperature range

- Low power consumption

- < 2.0 mA @ 5.0V, 4.0 MHz

- 15 μA typical 3.0V, 32 kHz

- < 1.0  $\mu$ A typical standby current @ 3.0V

#### **Device Differences**

| Device    | Voltage Range | Oscillator |

|-----------|---------------|------------|

| PIC16C554 | 2.5 - 5.5     | (Note 1)   |

| PIC16C557 | 2.5 - 5.5     | (Note 1)   |

| PIC16C558 | 2.5 - 5.5     | (Note 1)   |

Note 1: If you change from this device to another device, please verify oscillator characteristics in your application.

#### **Table of Contents**

| 1.0 General Description                  |     |

|------------------------------------------|-----|

| 2.0 PIC16C55X Device Varieties           | 7   |

| 3.0 Architectural Overview               | 9   |

| 4.0 Memory Organization                  |     |

| 5.0 I/O Ports                            | 23  |

| 6.0 Special Features of the CPU          | 31  |

| 7.0 Timer0 Module                        | 47  |

| 8.0 Instruction Set Summary              | 53  |

| 8.0 Instruction Set Summary              | 67  |

| 10.0 Electrical Specifications           | 73  |

| 11.0 Packaging Information               | 87  |

| Appendix A: Enhancements                 | 97  |

| Appendix B: Compatibility                | 97  |

| Index                                    | 99  |

| On-Line Support                          | 101 |

| Systems Information and Upgrade Hot Line | 101 |

| Reader Response                          | 102 |

| Product Identification System            | 103 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

### **PIC16C55X**

TABLE 1-1: PIC16C55X FAMILY OF DEVICES

|             |                                      | PIC16C554                        | PIC16C557                        | PIC16C558                 |

|-------------|--------------------------------------|----------------------------------|----------------------------------|---------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                               | 20                               | 20                        |

| Memory      | EPROM Program Memory (x14 words)     | 512                              | 2K                               | 2K                        |

|             | Data Memory (bytes)                  | 80                               | 128                              | 128                       |

| Peripherals | Timer Module(s)                      | TMR0                             | TMR0                             | TMR0                      |

|             | Interrupt Sources                    | 3                                | 3                                | 3                         |

|             | I/O Pins                             | 13                               | 22                               | 13                        |

| Features    | Voltage Range (Volts)                | 2.5-5.5                          | 2.5-5.5                          | 2.5-5.5                   |

| · oatai oo  | Brown-out Reset                      | _                                | _                                | _                         |

|             | Packages                             | 18-pin DIP, SOIC;<br>20-pin SSOP | 28-pin DIP, SOIC;<br>28-pin SSOP | 18-pin DIP, SOIC,<br>SSOP |

All PIC® Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C55X Family devices use serial programming with clock pin RB6 and data pin RB7.

TABLE 3-1: PIC16C55X PINOUT DESCRIPTION

|                    | Pin Number |      | Pin Buffer |                |                       |                                                                                                                                                                                                          |  |

|--------------------|------------|------|------------|----------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name               | PDIP       | SOIC | SSOP       | T.ma   T.ma    |                       | Description                                                                                                                                                                                              |  |

| OSC1/CLKIN         | 16         | 16   | 18         | I              | ST/CMOS               | Oscillator crystal input/external clock source output.                                                                                                                                                   |  |

| OSC2/CLKOUT        | 15         | 15   | 17         | 0              | _                     | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |

| MCLR/VPP           | 4          | 4    | 4          | I/P            | ST                    | Master clear (Reset) input/programming voltage input. This pin is an active low RESET to the device.                                                                                                     |  |

| RA0                | 17         | 17   | 19         | I/O            | ST                    | Bi-directional I/O port                                                                                                                                                                                  |  |

| RA1                | 18         | 18   | 20         | I/O            | ST                    | Bi-directional I/O port                                                                                                                                                                                  |  |

| RA2                | 1          | 1    | 1          | I/O            | ST                    | Bi-directional I/O port                                                                                                                                                                                  |  |

| RA3                | 2          | 2    | 2          | I/O            | ST                    | Bi-directional I/O port                                                                                                                                                                                  |  |

| RA4/T0CKI          | 3          | 3    | 3          | I/O            | ST                    | Bi-directional I/O port or external clock input for TMR0. Output is open drain type.                                                                                                                     |  |

| RB0/INT            | 6          | 6    | 7          | I/O            | TTL/ST <sup>(1)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. RB0/INT can also be selected as an external interrupt pin.                                                                 |  |

| RB1                | 7          | 7    | 8          | I/O            | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                            |  |

| RB2                | 8          | 8    | 9          | I/O            | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                            |  |

| RB3                | 9          | 9    | 10         | I/O            | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                            |  |

| RB4                | 10         | 10   | 11         | I/O            | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                   |  |

| RB5                | 11         | 11   | 12         | I/O            | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                   |  |

| RB6                | 12         | 12   | 13         | I/O            | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin. Serial programming clock.                                                                         |  |

| RB7                | 13         | 13   | 14         | I/O            | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin. Serial programming data.                                                                          |  |

| RC0 <sup>(3)</sup> | 18         | 18   | 18         | I/O            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC1 <sup>(3)</sup> | 19         | 19   | 19         | I/O            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC2 <sup>(3)</sup> | 20         | 20   | 20         | I/O            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC3 <sup>(3)</sup> | 21         | 21   | 21         | I/O            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC4 <sup>(3)</sup> | 22         | 22   | 22         | I/O            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC5 <sup>(3)</sup> | 23         | 23   | 23         | 1/0            |                       | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC6 <sup>(3)</sup> |            |      |            |                | TTL                   | · ·                                                                                                                                                                                                      |  |

|                    | 24         | 24   | 24         | 1/0            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| RC7 <sup>(3)</sup> | 25         | 25   | 25         | I/O            | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                    |  |

| Vss                | 5          | 5    | 5,6        | Р              | _                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |  |

| VDD                | 14         | 14   | 15,16      | P<br>O = Input | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |  |

Legend:

O = Output

I/O = Input/output

P = Power

— = Not used TTL = TTL input I = Input

ST = Schmitt Trigger input

**Note** 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

**3:** PIC16C557 only.

#### 4.2.2.2 OPTION Register

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

**Note 1:** To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

#### REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit7  |        |       |       |       |       |       | bit0  |

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

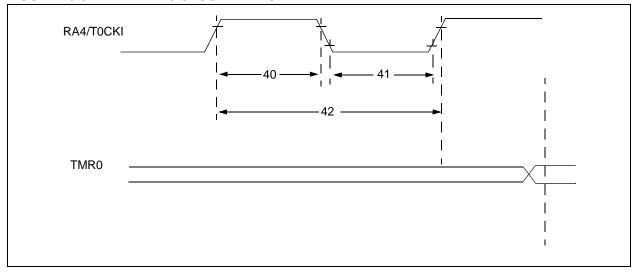

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3 **PSA**: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS2:PS0**: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1 · 256   | 1 · 128  |

| - |               |     |             |

|---|---------------|-----|-------------|

|   |               |     |             |

| ı | $\sim$        | n   | <b>۱</b> ۸۰ |

|   | $\Delta \cap$ | ıΔr | va:         |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### **CONFIGURATION WORD REGISTER 6-1:**

CP1 CP0 CP1 CP0 CP1 CP0 Reserved CP1 CP0 **PWRTE** WDTE F0SC1 F0SC0

bit 13 bit 0

CP<1:0>: Code protection bits<sup>(1)</sup> bit 13-8

11 = Program Memory code protection off 10 = 0400h - 07FFh code protected 01 = 0200h - 07FFh code protected bit 5-4

11 = 0000h - 07FFh code protected

bit 7 Unimplemented: Read as '1'

Reserved: Do not use bit 6

PWRTE: Power-up Timer Enable bit bit 3

1 = PWRT disabled 0 = PWRT enabled

bit 2 WDTE: Watchdog Timer Enable bit

> 1 = WDT enabled 0 = WDT disabled

FOSC1:FOSC0: Oscillator Selection bits bit 1-0

11 = RC oscillator

10 = HS oscillator

01 = XT oscillator

00 = LP oscillator

Note 1: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### 6.2 Oscillator Configurations

#### 6.2.1 OSCILLATOR TYPES

The PIC16C55X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

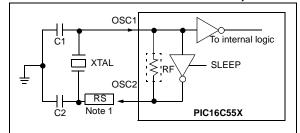

### 6.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

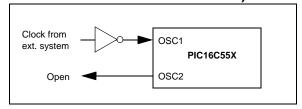

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 6-1). The PIC16C55X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 6-2).

FIGURE 6-1: CRYSTAL OPERATION

(OR CERAMIC

RESONATOR) (HS, XT OR

LP OSC

CONFIGURATION)

- Note 1: A series resistor may be required for AT strip cut crystals.

- 2: See Table 6-1 and Table 6-2 for recommended values of C1 and C2.

FIGURE 6-2: EXTERNAL CLOCK INPUT

OPERATION (HS, XT OR

LP OSC

CONFIGURATION)

TABLE 6-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS (PRELIMINARY)

| Ranges |          |             |             |

|--------|----------|-------------|-------------|

| Mode   | Freq     | OSC1(C1)    | OSC2(C2)    |

| XT     | 455 kHz  | 22 - 100 pF | 22 - 100 pF |

|        | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |

|        | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |

| HS     | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |

|        | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |

Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult with the resonator manufacturer for appropriate values of external components.

TABLE 6-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR (PRELIMINARY)

| (    |         |             |              |  |  |

|------|---------|-------------|--------------|--|--|

| Mode | Freq    | OSC1(C1)    | OSC2(C2)     |  |  |

| LP   | 32 kHz  | 68 - 100 pF | 68 - 100 pF  |  |  |

|      | 200 kHz | 15 - 30 pF  | 15 - 30 pF   |  |  |

| XT   | 100 kHz | 68 - 150 pF | 150 - 200 pF |  |  |

|      | 2 MHz   | 15 - 30 pF  | 15 - 30 pF   |  |  |

|      | 4 MHz   | 15 - 30 pF  | 15 - 30 pF   |  |  |

| HS   | 8 MHz   | 15 - 30 pF  | 15 - 30 pF   |  |  |

|      | 10 MHz  | 15 - 30 pF  | 15 - 30 pF   |  |  |

|      | 20 MHz  | 15 - 30 pF  | 15 - 30 pF   |  |  |

Note 1: Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid over-driving crystals with low-drive level specification. Since each crystal has its own characteristics, the user should consult with the crystal manufacturer for appropriate values of external components.

# 6.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST)

#### 6.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.6V - 1.8V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607 "Power-up Trouble Shooting".

#### 6.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) timeout on power-up only, from POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

### 6.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 6.4.4 TIMEOUT SEQUENCE

On power-up, the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired, then OST is activated. The total timeout will vary based on oscillator configuration and PWRTE bit status. For example, in RC mode with PWRTE bit erased (PWRT disabled), there will be no timeout at all. Figure 6-7, Figure 6-8 and Figure 6-9 depict timeout sequences.

Since the timeouts occur from the POR pulse, if MCLR is kept low long enough, the timeouts will expire. Then bringing MCLR high will begin execution immediately (see Figure 6-8). This is useful for testing purposes or to synchronize more than one PIC16C55X device operating in parallel.

Table 6-5 shows the RESET conditions for some special registers, while Table 6-6 shows the RESET conditions for all the registers.

### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT. Lines 5-7 are required only if the desired postscaler rate is 1:1 (PS<2:0> = 000) or 1:2 (PS<2:0> = 001).

### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)

| I | BCF   | STATUS, RP0 | ;Skip if already in      |

|---|-------|-------------|--------------------------|

|   |       |             | ;Bank 0 CLRWDT Clear WDT |

|   | CLRF  | TMR0        | ;Clear TMR0 & Prescaler  |

|   | BSF   | STATUS, RP0 | ;Bank 1                  |

|   | MOVLW | '00101111'b | ;These 3 lines (5, 6, 7) |

|   | MOVWF | OPTION      | ;Are required only if    |

|   |       |             | ;Desired PS<2:0> are     |

|   |       |             | ;CLRWDT 000 or 001       |

|   | MOVLW | '00101xxx'b | ;Set Postscaler to       |

|   | MOVWF | OPTION      | ;Desired WDT rate        |

|   | BCF   | STATUS, RP0 | ;Return to Bank 0        |

| ı |       |             |                          |

To change prescaler from the WDT to the TMR0 module use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT |             | ;Clear WDT and      |

|--------|-------------|---------------------|

|        |             | ;prescaler          |

| BSF    | STATUS, RP0 |                     |

| MOVLW  | b'xxxx0xxx' | ;prescale value and |

| MOVWF  | OPTION      | clock source        |

| MOVWE  | OPIION      |                     |

| BCF    | STATUS, RPO |                     |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMERO

| Address | Name   | Bit 7    | Bit 6           | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|--------|----------|-----------------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 01h     | TMR0   | Timer0 m | odule's registe | r     |        |        |        |        |        | xxxx xxxx       | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE      | Reserved        | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x       | 0000 000x                       |

| 81h     | OPTION | RBPU     | INTEDG          | T0CS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

| 85h     | TRISA  | _        | _               | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0',

Note 1: Shaded bits are not used by TMR0 module.

## PIC16C55X

| BCF              | Bit Clea                          | ar f          |          |          |  |  |

|------------------|-----------------------------------|---------------|----------|----------|--|--|

| Syntax:          | [ label ]                         | BCF f         | ,b       |          |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$ |               |          |          |  |  |

| Operation:       | $0 \rightarrow (f < l)$           | b>)           |          |          |  |  |

| Status Affected: | None                              |               |          |          |  |  |

| Encoding:        | 01                                | 00bb          | bfff     | ffff     |  |  |

| Description:     | Bit 'b' in re                     | gister 'f' is | cleared. |          |  |  |

| Words:           | 1                                 |               |          |          |  |  |

| Cycles:          | 1                                 |               |          |          |  |  |

| Example          | BCF                               | FLAG_F        | REG, 7   |          |  |  |

|                  | After Inst                        | G_REG         | = 0x     | C7<br>47 |  |  |

| BSF              | Bit Set                           | f      |      |      |  |  |

|------------------|-----------------------------------|--------|------|------|--|--|

| Syntax:          | [ label ] BSF f,b                 |        |      |      |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$ |        |      |      |  |  |

| Operation:       | $1 \rightarrow (f < b >)$         |        |      |      |  |  |

| Status Affected: | None                              |        |      |      |  |  |

| Encoding:        | 01                                | 01bb   | bfff | ffff |  |  |

| Description:     | Bit 'b' in register 'f' is set.   |        |      |      |  |  |

| Words:           | 1                                 |        |      |      |  |  |

| Cycles:          | 1                                 |        |      |      |  |  |

| Example          | BSF                               | FLAG_F | REG, | 7    |  |  |

|                  | Before Instruction                |        |      |      |  |  |

|                  | $FLAG_REG = 0x0A$                 |        |      |      |  |  |

|                  | After Instruction                 |        |      |      |  |  |

|                  | $FLAG_REG = 0x8A$                 |        |      |      |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$ $0 \le b \le 7$                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0' then the next instruction is skipped. If bit 'b' is '0' then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1 FALSE GOTO PROCESS_CODE TRUE • • •                                                                                                                                                                                                   |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                  | PC = address HERE                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | if $FLAG<1>=0$ ,                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                  | PC = address TRUE if FLAG<1> = 1,                                                                                                                                                                                                                      |  |  |  |  |  |  |

|                  | PC = address FALSE                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                           |                                                                                  |                                   |                           |  |

|------------------|---------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------|---------------------------|--|

| Syntax:          | [ label ] B                                       | TFSS f,l                                                                         | )                                 |                           |  |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                |                                                                                  |                                   |                           |  |

| Operation:       | skip if (f<                                       | b>) = 1                                                                          |                                   |                           |  |

| Status Affected: | None                                              |                                                                                  |                                   |                           |  |

| Encoding:        | 01                                                | 11bb                                                                             | bfff                              | ffff                      |  |

| Description:     | instruction If bit 'b' is ' fetched du execution, | register 'f' is is skipped 1', then the uring the cuis discardenstead, mauction. | next instrurent instrued and a No | uction<br>iction<br>OP is |  |

| Words:           | 1                                                 |                                                                                  |                                   |                           |  |

| Cycles:          | 1(2)                                              |                                                                                  |                                   |                           |  |

| Example          | HERE<br>FALSE<br>TRUE                             | BTFSS<br>GOTO<br>•                                                               | FLAG,1                            | S_CODE                    |  |

|                  | Before In                                         | struction                                                                        |                                   |                           |  |

|                  | PC                                                | = ad                                                                             | dress нег                         | RE                        |  |

|                  | PC =<br>if FL                                     | AG<1> = 0<br>= add<br>AG<1> =                                                    | ress fal                          |                           |  |

| CALL             | Call Sul                                                                                                                                                                                                                  | broutine  | )         |      |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|--|--|

| Syntax:          | [label] CALL k                                                                                                                                                                                                            |           |           |      |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                      |           |           |      |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                          |           |           |      |  |  |

| Status Affected: | None                                                                                                                                                                                                                      |           |           |      |  |  |

| Encoding:        | 10                                                                                                                                                                                                                        | 0kkk      | kkkk      | kkkk |  |  |

| Description:     | Call Subroutine. First, return address (PC+1) is pushed onto the stack. The eleven bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a two-cycle instruction. |           |           |      |  |  |

| Words:           | 1                                                                                                                                                                                                                         |           |           |      |  |  |

| Cycles:          | 2                                                                                                                                                                                                                         |           |           |      |  |  |

| Example          | HERE                                                                                                                                                                                                                      | CALL      | THERE     |      |  |  |

|                  | Before In:                                                                                                                                                                                                                | struction |           |      |  |  |

|                  | PC                                                                                                                                                                                                                        | = Add     | lress her | E    |  |  |

|                  | After Instruction                                                                                                                                                                                                         |           |           |      |  |  |

|                  | PC                                                                                                                                                                                                                        | = Add     | lress THE | RE   |  |  |

|                  | TOS                                                                                                                                                                                                                       | = Add     | lress her | E+1  |  |  |

|                  |                                                                                                                                                                                                                           |           |           |      |  |  |

| CLRF             | Clear f                                                        |        |      |      |  |  |

|------------------|----------------------------------------------------------------|--------|------|------|--|--|

| Syntax:          | [label] CLRF f                                                 |        |      |      |  |  |

| Operands:        | $0 \leq f \leq 127$                                            |        |      |      |  |  |

| Operation:       | $00h \to (f)$ $1 \to Z$                                        |        |      |      |  |  |

| Status Affected: | Z                                                              |        |      |      |  |  |

| Encoding:        | 00                                                             | 0001   | 1fff | ffff |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |        |      |      |  |  |

| Words:           | 1                                                              |        |      |      |  |  |

| Cycles:          | 1                                                              |        |      |      |  |  |

| Example          | CLRF                                                           | FLAG_F | REG  |      |  |  |

|                  | Before Instruction<br>FLAG REG=0x5A                            |        |      |      |  |  |

|                  | After Instruction                                              |        |      |      |  |  |

|                  | FLAG_REG=0x00                                                  |        |      |      |  |  |

|                  | Z                                                              | =      | 1    |      |  |  |

| Decrem                                                                                                                                                                                                                                                                                                  | nent f, S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | kip if 0                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [ label ]                                                                                                                                                                                                                                                                                               | DECFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Z f,d                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| None                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 00                                                                                                                                                                                                                                                                                                      | 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | dfff                                                                                                                                             | ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| The contents of register 'f' are decremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |