#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Program Memory Size896B (512 x 14)Program Memory TypeOTPEEPROM Size-RAM Size80 x 8                                                                                                                                                                                                                                                              | Details                    |                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

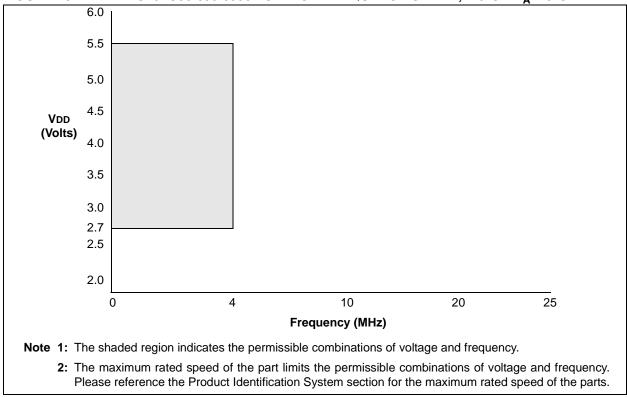

| Core Size8-BitCore Size4MHzSpeed4MHzConnectivity-PeripheralsPOR, WDTNumber of I/O13Program Memory Size896B (512 x 14)Program Memory TypeOTPEEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type18-DIP (0.300°, 7.62mm)Package / Case18-DIP | Product Status             | Active                                                                     |

| Speed4MHzConnectivity-PeripheralsPOR, WDTNumber of I/O13Program Memory Size896B (512 x 14)Program Memory TypeOTPEEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type18-DIP (0.300", 7.62mm)Package / Case18-DIP                            | Core Processor             | PIC                                                                        |

| Connectivity-PeripheralsPOR, WDTNumber of I/O13Program Memory Size896B (512 x 14)Program Memory TypeOTPEDROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Operating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)                                                       | Core Size                  | 8-Bit                                                                      |

| PeripheralsPOR, WDTNumber of I/O13Program Memory Size896B (512 x 14)Program Memory TypeOTPEEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                        | Speed                      | 4MHz                                                                       |

| Number of I/O13Program Memory Size896B (512 x 14)Program Memory TypeOTPEEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)                                                               | Connectivity               | -                                                                          |

| Program Memory Size896B (512 x 14)Program Memory TypeOTPEEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                          | Peripherals                | POR, WDT                                                                   |

| Program Memory TypeOTPEEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                  | Number of I/O              | 13                                                                         |

| EEPROM Size-RAM Size80 x 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                        | Program Memory Size        | 896B (512 x 14)                                                            |

| RAM Size80 × 8Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                                    | Program Memory Type        | OTP                                                                        |

| Voltage - Supply (Vcc/Vdd)2.5V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                                                  | EEPROM Size                | <u>.</u>                                                                   |

| Data Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                                                                                       | RAM Size                   | 80 x 8                                                                     |

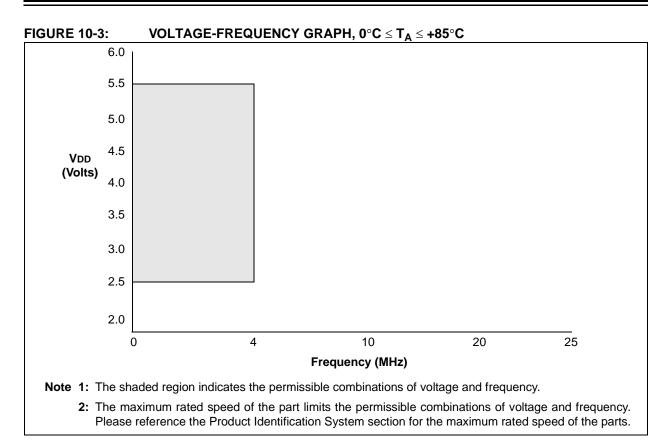

| Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                                                                                                       | Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                                                                                                                              | Data Converters            | -                                                                          |

| Mounting TypeThrough HolePackage / Case18-DIP (0.300", 7.62mm)Supplier Device Package18-PDIP                                                                                                                                                                                                                                                    | Oscillator Type            | External                                                                   |

| Package / Case     18-DIP (0.300", 7.62mm)       Supplier Device Package     18-PDIP                                                                                                                                                                                                                                                            | Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Supplier Device Package 18-PDIP                                                                                                                                                                                                                                                                                                                 | Mounting Type              | Through Hole                                                               |

|                                                                                                                                                                                                                                                                                                                                                 | Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554-04i-p                                                                                                                                                                                                                                                         | Supplier Device Package    | 18-PDIP                                                                    |

|                                                                                                                                                                                                                                                                                                                                                 | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554-04i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 4.0 MEMORY ORGANIZATION

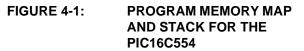

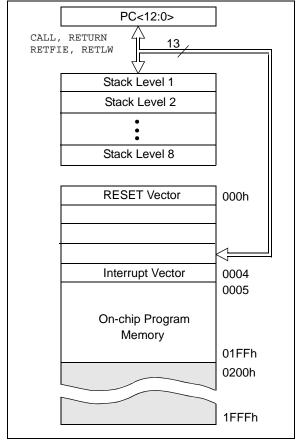

## 4.1 Program Memory Organization

The PIC16C55X has a 13-bit program counter capable of addressing an 8 K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C554 and 2K x 14 (0000h - 07FFh) for the PIC16C557 and PIC16C558 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 spaces in the PIC16C554, or 2K x 14 space of the PIC16C558 and PIC16C557. The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2).

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C557 AND PIC16C558

## 4.2 Data Memory Organization

The data memory (Figure 4-3 through Figure 4-5) is partitioned into two banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bank 0 is selected when the RP0 bit (STATUS <5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-6Fh (Bank 0) on the PIC16C554 and 20-7Fh (Bank 0) and A0-BFh (Bank 1) on the PIC16C558 and PIC16C557 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $80 \times 8$  in the PIC16C554 and 128 x 8 in the PIC16C557 and PIC16C558. Each can be accessed either directly or indirectly through the File Select Register, FSR (Section 4.4).

## FIGURE 4-3:

## DATA MEMORY MAP FOR THE PIC16C554

| File<br>Address | 3                                                 |                     | File<br>Address |  |  |  |  |  |

|-----------------|---------------------------------------------------|---------------------|-----------------|--|--|--|--|--|

| 00h             | INDF <sup>(1)</sup>                               | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |

| 01h             | TMR0                                              | OPTION              | 81h             |  |  |  |  |  |

| 02h             | PCL                                               | PCL                 | 82h             |  |  |  |  |  |

| 03h             | STATUS                                            | STATUS              | 83h             |  |  |  |  |  |

| 04h             | FSR                                               | FSR                 | 84h             |  |  |  |  |  |

| 05h             | PORTA                                             | TRISA               | 85h             |  |  |  |  |  |

| 06h             | PORTB                                             | TRISB               | 86h             |  |  |  |  |  |

| 07h             | 1 OILIB                                           | THE                 | 87h             |  |  |  |  |  |

| 08h             |                                                   |                     | 88h             |  |  |  |  |  |

| 09h             |                                                   |                     | 89h             |  |  |  |  |  |

| 0Ah             | PCLATH                                            | PCLATH              | 8Ah             |  |  |  |  |  |

| 0Bh             | INTCON                                            | INTCON              | 8Bh             |  |  |  |  |  |

| 0Ch             |                                                   |                     | 8Ch             |  |  |  |  |  |

| 0Dh             |                                                   |                     | 8Dh             |  |  |  |  |  |

| 0Eh             |                                                   | PCON                | 8Eh             |  |  |  |  |  |

| 0Eh             |                                                   | 10011               | 8Fh             |  |  |  |  |  |

| 10h             |                                                   |                     | 90h             |  |  |  |  |  |

| 11h             |                                                   |                     | 91h             |  |  |  |  |  |

| 12h             |                                                   |                     | 92h             |  |  |  |  |  |

| 13h             |                                                   |                     | 93h             |  |  |  |  |  |

| 14h             |                                                   |                     | 94h             |  |  |  |  |  |

| 15h             |                                                   |                     | 95h             |  |  |  |  |  |

| 16h             |                                                   |                     | 96h             |  |  |  |  |  |

| 17h             |                                                   |                     | 97h             |  |  |  |  |  |

| 18h             |                                                   |                     | 98h             |  |  |  |  |  |

| 19h             |                                                   |                     | 99h             |  |  |  |  |  |

| 1Ah             |                                                   |                     | 9Ah             |  |  |  |  |  |

| 1Bh             |                                                   |                     | 9Bh             |  |  |  |  |  |

| 1Ch             |                                                   |                     | 9Ch             |  |  |  |  |  |

| 1Dh             |                                                   |                     | 9Dh             |  |  |  |  |  |

| 1Eh             |                                                   |                     | 9Eh             |  |  |  |  |  |

| 1Fh             |                                                   |                     | 9Fh             |  |  |  |  |  |

| 20h             |                                                   |                     | A0h             |  |  |  |  |  |

| -               | General                                           |                     | 7.011           |  |  |  |  |  |

|                 | Purpose<br>Register                               |                     |                 |  |  |  |  |  |

| 6Fh             | regiotor                                          |                     |                 |  |  |  |  |  |

| 70h             |                                                   |                     |                 |  |  |  |  |  |

|                 |                                                   |                     |                 |  |  |  |  |  |

| ſ               |                                                   |                     |                 |  |  |  |  |  |

|                 |                                                   |                     |                 |  |  |  |  |  |

| 7Fh             |                                                   |                     | FFh             |  |  |  |  |  |

| ,,,,,           | Bank 0                                            | Bank 1              |                 |  |  |  |  |  |

| Unim            | Unimplemented data memory locations, read as '0'. |                     |                 |  |  |  |  |  |

| Note 1:         | Not a physical regi                               |                     |                 |  |  |  |  |  |

|                 |                                                   |                     |                 |  |  |  |  |  |

#### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16C557

|                                                                                              | IHE                 | PIC16C557           |                 |  |  |  |  |

|----------------------------------------------------------------------------------------------|---------------------|---------------------|-----------------|--|--|--|--|

| File<br>Address                                                                              | 8                   |                     | File<br>Address |  |  |  |  |

| 00h                                                                                          | INDF <sup>(1)</sup> | INDF <sup>(1)</sup> | 80h             |  |  |  |  |

| 01h                                                                                          | TMR0                | OPTION              | 81h             |  |  |  |  |

| 02h                                                                                          | PCL                 | PCL                 | 82h             |  |  |  |  |

| 03h                                                                                          | STATUS              | STATUS              | 83h             |  |  |  |  |

| 04h                                                                                          | FSR                 | FSR                 | 84h             |  |  |  |  |

| 05h                                                                                          | PORTA               | TRISA               | 85h             |  |  |  |  |

| 06h                                                                                          | PORTB               | TRISB               | 86h             |  |  |  |  |

| 07h                                                                                          | PORTC               | TRISC               | 87h             |  |  |  |  |

| 08h                                                                                          |                     |                     | 88h             |  |  |  |  |

| 09h                                                                                          |                     |                     | 89h             |  |  |  |  |

| 0Ah                                                                                          | PCLATH              | PCLATH              | 8Ah             |  |  |  |  |

| 0Bh                                                                                          | INTCON              | INTCON              | 8Bh             |  |  |  |  |

| 0Ch                                                                                          |                     |                     | 8Ch             |  |  |  |  |

| 0Dh                                                                                          |                     |                     | 8Dh             |  |  |  |  |

| 0Eh                                                                                          |                     | PCON                | 8Eh             |  |  |  |  |

| 0Fh                                                                                          |                     |                     | 8Fh             |  |  |  |  |

| 10h                                                                                          |                     |                     | 90h             |  |  |  |  |

| 11h                                                                                          |                     |                     | 91h             |  |  |  |  |

| 12h                                                                                          |                     |                     | 92h             |  |  |  |  |

| 13h                                                                                          |                     |                     | 93h             |  |  |  |  |

| 14h                                                                                          |                     |                     | 94h             |  |  |  |  |

| 15h                                                                                          |                     |                     | 95h             |  |  |  |  |

| 16h                                                                                          |                     |                     | 96h             |  |  |  |  |

| 17h                                                                                          |                     |                     | 97h             |  |  |  |  |

| 18h                                                                                          |                     |                     | 98h             |  |  |  |  |

| 19h                                                                                          |                     |                     | 99h             |  |  |  |  |

| 1Ah                                                                                          |                     |                     | 9Ah             |  |  |  |  |

| 1Bh                                                                                          |                     |                     | 9Bh             |  |  |  |  |

| 1Ch                                                                                          |                     |                     | 9Ch             |  |  |  |  |

| 1Dh                                                                                          |                     |                     | 9Dh             |  |  |  |  |

| 1Eh                                                                                          |                     |                     | 9Eh             |  |  |  |  |

| 1Fh                                                                                          |                     |                     | 9Fh             |  |  |  |  |

| 20h                                                                                          |                     |                     | A0h             |  |  |  |  |

|                                                                                              | General             | General             |                 |  |  |  |  |

|                                                                                              | Purpose<br>Register | Purpose<br>Register |                 |  |  |  |  |

|                                                                                              |                     |                     | BFh             |  |  |  |  |

|                                                                                              |                     |                     | C0h             |  |  |  |  |

|                                                                                              |                     |                     |                 |  |  |  |  |

|                                                                                              |                     |                     |                 |  |  |  |  |

|                                                                                              |                     |                     |                 |  |  |  |  |

| 7Fh                                                                                          |                     |                     | FFh             |  |  |  |  |

| ,,,,,                                                                                        | Bank 0 Bank 1       |                     |                 |  |  |  |  |

| Unimplemented data memory locations, read as '0'.<br><b>Note 1:</b> Not a physical register. |                     |                     |                 |  |  |  |  |

## TABLE 5-1: PORTA FUNCTIONS

| Name      | Bit # | Buffer<br>Type | Function                                                                             |

|-----------|-------|----------------|--------------------------------------------------------------------------------------|

| RA0       | Bit 0 | ST             | Bi-directional I/O port.                                                             |

| RA1       | Bit 1 | ST             | Bi-directional I/O port.                                                             |

| RA2       | Bit 2 | ST             | Bi-directional I/O port.                                                             |

| RA3       | Bit 3 | ST             | Bi-directional I/O port.                                                             |

| RA4/T0CKI | Bit 4 | ST             | Bi-directional I/O port or external clock input for TMR0. Output is open drain type. |

Legend: ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 05h     | PORTA | —     | _     |       | RA4    | RA3    | RA2    | RA1    | RA0    | x xxxx          | u uuuu                          |

| 85h     | TRISA | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111          | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged

**Note 1:** Shaded bits are not used by PORTA.

## 6.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a pre-packaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

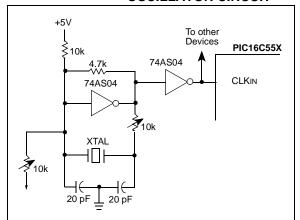

Figure 6-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 6-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

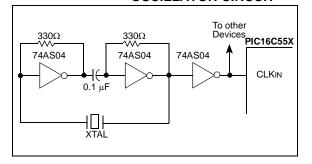

Figure 6-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The  $330\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 6-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

# 6.2.4 RC OSCILLATOR

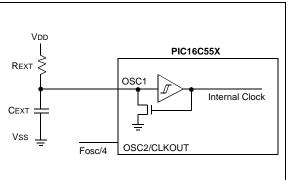

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 6-5 shows how the R/C combination is connected to the PIC16C55X. For REXT values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high REXT values (e.g., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep REXT between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (CEXT = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 6-5: RC OSCILLATOR MODE

## 6.3 RESET

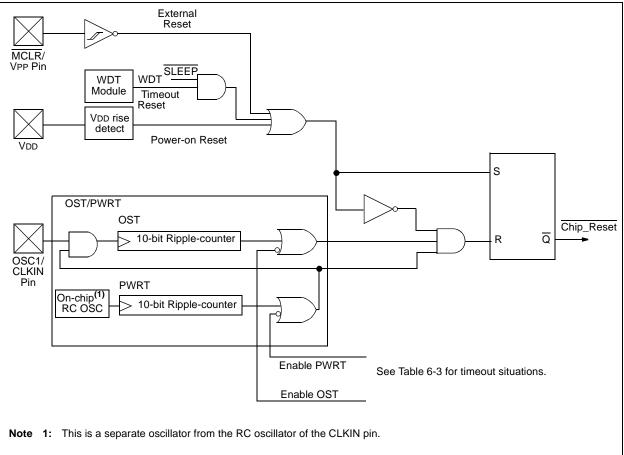

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

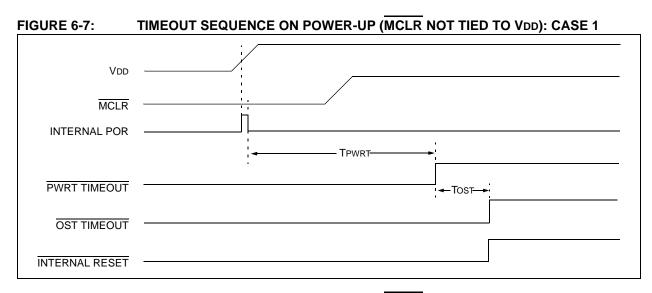

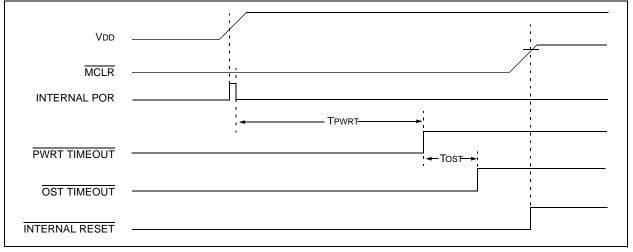

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers. A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

# 6.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 6-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 6-1:

- Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- Restores the W register

#### EXAMPLE 6-1: SAVING THE STATUS AND W REGISTERS IN RAM

|       | 117            |                                           |

|-------|----------------|-------------------------------------------|

| MOVWF | W_TEMP         | ;copy W to TEMP<br>;register, could be in |

|       |                | -                                         |

|       |                | ;either bank                              |

| SWAPF | STATUS,W       | ;swap STATUS to be                        |

|       |                | ;saved into W                             |

| BCF   | STATUS, RPO    | ;change to bank0                          |

|       |                | ;regardless of                            |

|       |                | ;current bank                             |

| MOVWF | STATUS_TEMP    | ;save STATUS to bank0                     |

|       |                | ;register                                 |

| :     |                |                                           |

| :     |                |                                           |

| :     |                |                                           |

| SWAPF | STATUS_TEMP, W | 1;swap STATUS_TEMP                        |

|       |                | ;register into W, sets                    |

|       |                | ;bank to original state                   |

| MOVWF | STATUS         | ;move W into STATUS                       |

|       |                | ;register                                 |

| SWAPF | W_TEMP,F       | ;swap W_TEMP                              |

| SWAPF | W_TEMP,W       | ;swap W_TEMP into W                       |

# 6.7 Watchdog Timer (WDT)

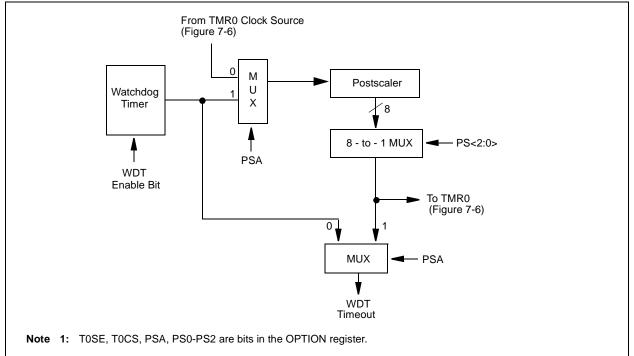

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT timeout generates a device RESET. If the device is in SLEEP mode, a WDT timeout causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 6.1).

## 6.7.1 WDT PERIOD

The WDT has a nominal timeout period of 18 ms, (with no prescaler). The timeout periods vary with temperature, VDD and process variations from part-to-part (see DC specs). If longer timeout periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, timeout periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer timeout.

## 6.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT timeout occurs.

| Address | Name         | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other RESETS |

|---------|--------------|-------|----------|-------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 2007h   | Config. bits | _     | Reserved | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |              |                           |

| 81h     | OPTION       | RBPU  | INTEDG   | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111    | 1111 1111                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

## TABLE 8-2: PIC16C55X INSTRUCTION SET

| Mnemonic, Description |                                        | Cycles                       |        | 14-Bit | Opcode | Status | Neter |             |       |  |  |

|-----------------------|----------------------------------------|------------------------------|--------|--------|--------|--------|-------|-------------|-------|--|--|

| Opera                 |                                        | Description                  |        | MSb    |        |        | LSb   | Affected    | Notes |  |  |

|                       | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |        |        |        |        |       |             |       |  |  |

| ADDWF                 | f, d                                   | Add W and f                  | 1      | 00     | 0111   | dfff   | ffff  | C,DC,Z      | 1,2   |  |  |

| ANDWF                 | f, d                                   | AND W with f                 | 1      | 00     | 0101   | dfff   | ffff  | Z           | 1,2   |  |  |

| CLRF                  | f                                      | Clear f                      | 1      | 00     | 0001   | lfff   | ffff  | Z           | 2     |  |  |

| CLRW                  | -                                      | Clear W                      | 1      | 00     | 0001   | 0000   | 0011  | Z           |       |  |  |

| COMF                  | f, d                                   | Complement f                 | 1      | 00     | 1001   | dfff   | ffff  | Z           | 1,2   |  |  |

| DECF                  | f, d                                   | Decrement f                  | 1      | 00     | 0011   | dfff   | ffff  | Z           | 1,2   |  |  |

| DECFSZ                | f, d                                   | Decrement f, Skip if 0       | 1(2)   | 00     | 1011   | dfff   | ffff  |             | 1,2,3 |  |  |

| INCF                  | f, d                                   | Increment f                  | 1      | 00     | 1010   | dfff   | ffff  | Z           | 1,2   |  |  |

| INCFSZ                | f, d                                   | Increment f, Skip if 0       | 1(2)   | 00     | 1111   | dfff   | ffff  |             | 1,2,3 |  |  |

| IORWF                 | f, d                                   | Inclusive OR W with f        | 1      | 00     | 0100   | dfff   | ffff  | Z           | 1,2   |  |  |

| MOVF                  | f, d                                   | Move f                       | 1      | 00     | 1000   |        | ffff  | z           | 1,2   |  |  |

| MOVWF                 | f                                      | Move W to f                  | 1      | 00     | 0000   |        | ffff  | _           | - ,=  |  |  |

| NOP                   | -                                      | No Operation                 | 1      | 00     | 0000   | 0xx0   | 0000  |             |       |  |  |

| RLF                   | f, d                                   | Rotate Left f through Carry  | 1      | 00     |        | dfff   |       | С           | 1,2   |  |  |

| RRF                   | f, d                                   | Rotate Right f through Carry | 1      | 00     | 1100   | dfff   |       | Č           | 1,2   |  |  |

| SUBWF                 | f, d                                   | Subtract W from f            | 1      | 00     | 0010   | dfff   |       | C,DC,Z      | 1,2   |  |  |

| SWAPF                 | f, d                                   | Swap nibbles in f            | 1      | 00     | 1110   |        | ffff  | 0,20,2      | 1,2   |  |  |

| XORWF                 | f, d                                   | Exclusive OR W with f        | 1      | 00     | 0110   |        | ffff  | Z           | 1,2   |  |  |

|                       |                                        | BIT-ORIENTED FILE REGIST     |        | RATION | IS     |        |       |             |       |  |  |

| BCF                   | f, b                                   | Bit Clear f                  | 1      | 01     | 00bb   | bfff   | ffff  |             | 1,2   |  |  |

| BSF                   | f, b                                   | Bit Set f                    | 1      | 01     | 01bb   | bfff   | ffff  |             | 1,2   |  |  |

| BTFSC                 | f, b                                   | Bit Test f, Skip if Clear    | 1(2)   | 01     | 10bb   | bfff   | ffff  |             | 3     |  |  |

| BTFSS                 | f, b                                   | Bit Test f, Skip if Set      | 1(2)   | 01     | 11bb   | bfff   | ffff  |             | 3     |  |  |

|                       |                                        | LITERAL AND CONTROL          | OPERAT | IONS   |        |        |       |             |       |  |  |

| ADDLW                 | k                                      | Add literal and W            | 1      | 11     | 111x   | kkkk   | kkkk  | C,DC,Z      |       |  |  |

| ANDLW                 | k                                      | AND literal with W           | 1      | 11     | 1001   | kkkk   | kkkk  | Z           |       |  |  |

| CALL                  | k                                      | Call subroutine              | 2      | 10     | 0kkk   | kkkk   | kkkk  |             |       |  |  |

| CLRWDT                | -                                      | Clear Watchdog Timer         | 1      | 00     | 0000   | 0110   | 0100  | TO,PD       |       |  |  |

| GOTO                  | k                                      | Go to address                | 2      | 10     | 1kkk   | kkkk   | kkkk  | ,           |       |  |  |

| IORLW                 | k                                      | Inclusive OR literal with W  | 1      | 11     | 1000   | kkkk   | kkkk  | Z           |       |  |  |

| MOVLW                 | k                                      | Move literal to W            | 1      | 11     |        | kkkk   |       |             |       |  |  |

| RETFIE                | -                                      | Return from interrupt        | 2      | 00     | 0000   | 0000   | 1001  |             |       |  |  |

| RETLW                 | k                                      | Return with literal in W     | 2      | 11     |        | kkkk   |       |             |       |  |  |

| RETURN                | -                                      | Return from Subroutine       | 2      | 00     | 0000   | 0000   | 1000  |             |       |  |  |

| SLEEP                 | -                                      | Go into Standby mode         | 1      | 00     | 0000   | 0110   | 0011  | TO,PD       |       |  |  |

| SUBLW                 | k                                      | Subtract W from literal      | 1      | 11     |        | kkkk   |       | C,DC,Z      |       |  |  |

| XORLW                 | k                                      | Exclusive OR literal with W  | 1      | 11     |        | kkkk   |       | 0,00,2<br>Z |       |  |  |

|                       |                                        |                              | -      |        |        |        |       | <u>ک</u>    |       |  |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                       |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                       |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |  |  |  |  |

| Words:           | 1                                                                                                                       |  |  |  |  |

| Cycles:          | 1                                                                                                                       |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                              |  |  |  |  |

|                  | Before Instruction                                                                                                      |  |  |  |  |

|                  | W = 0x10                                                                                                                |  |  |  |  |

|                  | After Instruction                                                                                                       |  |  |  |  |

|                  | W = 0x25                                                                                                                |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |  |

| ANDLW            | AND Li                                  | teral wit  | h W            |          |  |  |  |

|------------------|-----------------------------------------|------------|----------------|----------|--|--|--|

| Syntax:          | [ label ]                               | ANDLW      | / k            |          |  |  |  |

| Operands:        | $0 \le k \le 2$                         | 255        |                |          |  |  |  |

| Operation:       | (W) .AN                                 | ID. (k) →  | • (W)          |          |  |  |  |

| Status Affected: | Z                                       |            |                |          |  |  |  |

| Encoding:        | 11                                      | 1001       | kkkk           | kkkk     |  |  |  |

|                  | The conter<br>AND'ed wi<br>result is pl | th the eig | ht bit literal | 'k'. The |  |  |  |

| Words:           | 1                                       |            |                |          |  |  |  |

| Cycles:          | 1                                       |            |                |          |  |  |  |

| Example          | ANDLW                                   | 0x5F       |                |          |  |  |  |

|                  | Before I                                | nstructio  | on             |          |  |  |  |

|                  | W                                       | =          | 0xA3           |          |  |  |  |

|                  | After Instruction                       |            |                |          |  |  |  |

|                  | W                                       | =          | 0x03           |          |  |  |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                         |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |  |  |

-

# PIC16C55X

| MOVF             | Move f                                                                                      |                                                                  |                                                                         |                                                    |  |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------|--|

| Syntax:          | [ label ]                                                                                   | MOVF                                                             | f,d                                                                     |                                                    |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in \left[0,1\right] \end{array}$                      |                                                                  |                                                                         |                                                    |  |

| Operation:       | $(f) \rightarrow (des$                                                                      | st)                                                              |                                                                         |                                                    |  |

| Status Affected: | Z                                                                                           |                                                                  |                                                                         |                                                    |  |

| Encoding:        | 00                                                                                          | 1000                                                             | dfff                                                                    | ffff                                               |  |

| Description:     | The conte<br>moved to<br>upon the<br>tination is<br>destination<br>= 1 is use<br>since stat | a destina<br>status of<br>W regis<br>on is file r<br>oful to tes | ation dep<br>f d. If d =<br>ter. If d =<br>register f i<br>st a file re | endant<br>0, des-<br>1, the<br>tself. d<br>egister |  |

| Words:           | 1                                                                                           |                                                                  |                                                                         |                                                    |  |

| Cycles:          | 1                                                                                           |                                                                  |                                                                         |                                                    |  |

| Example          | MOVF                                                                                        | FSR,                                                             | 0                                                                       |                                                    |  |

|                  | After Inst<br>W<br>Z                                                                        |                                                                  | e in FSR I                                                              | register                                           |  |

| NOP              | No Operation |      |      |      |  |

|------------------|--------------|------|------|------|--|

| Syntax:          | [ label ]    |      |      |      |  |

| Operands:        | None         |      |      |      |  |

| Operation:       | No operation |      |      |      |  |

| Status Affected: | None         |      |      |      |  |

| Encoding:        | 00           | 0000 | 0xx0 | 0000 |  |

| Description:     | No operat    | ion. |      |      |  |

| Words:           | 1            |      |      |      |  |

| Cycles:          | 1            |      |      |      |  |

| Example          | NOP          |      |      |      |  |

| MOVWF            | Move W to f                                |  |  |  |  |

|------------------|--------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVWF f                            |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                        |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                      |  |  |  |  |

| Status Affected: | None                                       |  |  |  |  |

| Encoding:        | 00 0000 1fff ffff                          |  |  |  |  |

| Description:     | Move data from W register to register 'f'. |  |  |  |  |

| Words:           | 1                                          |  |  |  |  |

| Cycles:          | 1                                          |  |  |  |  |

| Example          | MOVWF OPTION                               |  |  |  |  |

|                  | Before Instruction                         |  |  |  |  |

|                  | OPTION = 0xFF                              |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |

|                  | After Instruction                          |  |  |  |  |

|                  | OPTION = 0x4F                              |  |  |  |  |

|                  | W = 0x4F                                   |  |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                             |        |      |      |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                        | OPTION | N    |      |  |

| Operands:        | None                                                                                                                                                                                                                                             |        |      |      |  |

| Operation:       | $(W) \rightarrow O$                                                                                                                                                                                                                              | PTION  |      |      |  |

| Status Affected: | None                                                                                                                                                                                                                                             |        |      |      |  |

| Encoding:        | 00                                                                                                                                                                                                                                               | 0000   | 0110 | 0010 |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it. |        |      |      |  |

| Words:           | 1                                                                                                                                                                                                                                                |        |      |      |  |

| Cycles:          | 1                                                                                                                                                                                                                                                |        |      |      |  |

| Example          |                                                                                                                                                                                                                                                  |        |      |      |  |

|                  | To maintain upward compatibility<br>with future PIC MCU products, do<br>not use this instruction.                                                                                                                                                |        |      |      |  |

|                  |                                                                                                                                                                                                                                                  |        |      |      |  |

$\odot$  1996-2013 Microchip Technology Inc.

# **PIC16C55X**

| SUBWF               | Subtract W from f                                                                                                                                                                  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ label ] SUBWF f,d                                                                                                                                                                |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                 |

| Operation:          | (f) - (W) $\rightarrow$ (dest)                                                                                                                                                     |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                           |

| Encoding:           | 00 0010 dfff ffff                                                                                                                                                                  |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is 1<br>the result is stored back in register 'f'. |

| Words:              | 1                                                                                                                                                                                  |

| Cycles:             | 1                                                                                                                                                                                  |

| Example 1:          | SUBWF REG1,1                                                                                                                                                                       |

|                     | Before Instruction                                                                                                                                                                 |

|                     | REG1 = 3                                                                                                                                                                           |

|                     | W = 2                                                                                                                                                                              |

|                     | C = ?                                                                                                                                                                              |

|                     | After Instruction                                                                                                                                                                  |

|                     | REG1 = 1                                                                                                                                                                           |

|                     | W = 2                                                                                                                                                                              |

|                     | C = 1; result is positive                                                                                                                                                          |

| Example 2:          | Before Instruction                                                                                                                                                                 |

|                     | REG1 = 2                                                                                                                                                                           |

|                     | W = 2 $C = ?$                                                                                                                                                                      |

|                     | After Instruction                                                                                                                                                                  |

|                     |                                                                                                                                                                                    |

|                     | REG1 = 0<br>W = 2                                                                                                                                                                  |

|                     | C = 1; result is zero                                                                                                                                                              |

| Example 3:          | Before Instruction                                                                                                                                                                 |

|                     | REG1 = 1                                                                                                                                                                           |

|                     | W = 2                                                                                                                                                                              |

|                     | C = ?                                                                                                                                                                              |

|                     | After Instruction                                                                                                                                                                  |

|                     | REG1 = 0xFF                                                                                                                                                                        |

|                     | W = 2                                                                                                                                                                              |

|                     | C = 0; result is negative                                                                                                                                                          |

| SWAPF            | Swap Nibbles in f                                                                                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                               |  |  |  |  |  |

|                  | d ∈ [0,1]                                                                                                                                                                       |  |  |  |  |  |

| Operation:       | (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                                                                                                               |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                            |  |  |  |  |  |

| Encoding:        | 00 1110 dfff ffff                                                                                                                                                               |  |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0<br>the result is placed in W register. If 'd'<br>is 1 the result is placed in register 'f'.           |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                               |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                               |  |  |  |  |  |

| Example          | SWAPF REG, 0                                                                                                                                                                    |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                              |  |  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                                     |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                               |  |  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                                     |  |  |  |  |  |

|                  | W = 0x5A                                                                                                                                                                        |  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                              |  |  |  |  |  |

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                              |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                            |  |  |  |  |  |

| Encoding:        | 00 0000 0110 Offf                                                                                                                                                               |  |  |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X<br>products. Since TRIS registers are<br>readable and writable, the user can<br>directly address them. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                               |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                               |  |  |  |  |  |

| Example          |                                                                                                                                                                                 |  |  |  |  |  |