Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 896B (512 x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 80 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554t-04e-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

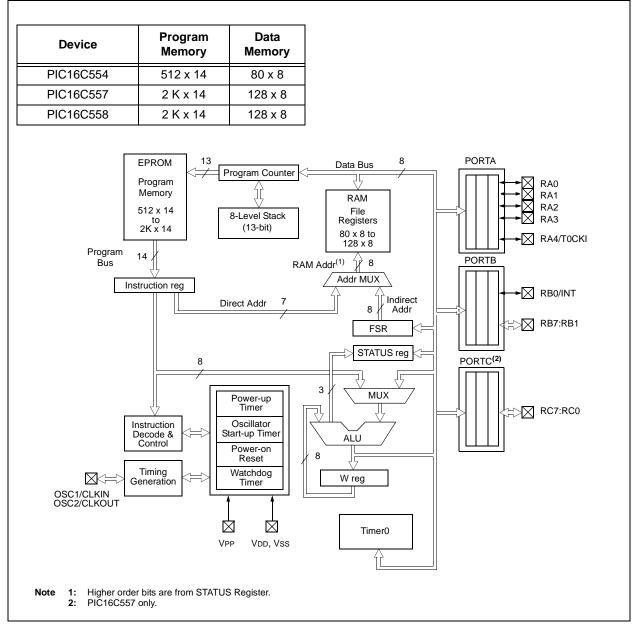

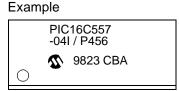

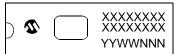

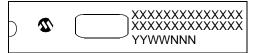

### 2.0 PIC16C55X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C55X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

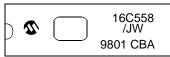

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PROMATE<sup>®</sup> programmers both support programming of the PIC16C55X.

#### 2.2 One-Time Programmable (OTP) Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 Quick-Turnaround Production (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium-to-high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices, but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

#### 2.4 Serialized Quick-Turnaround Production (SQTP<sup>™</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry code, password or ID number.

# PIC16C55X

#### FIGURE 3-1: BLOCK DIAGRAM

| TABLE 3-1:         | PIC16C55X PINOUT DESC |                        |       |                         |                       |                                                                                                                                                                                                                   |  |  |

|--------------------|-----------------------|------------------------|-------|-------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name               | PDIP SOIC SSOP        |                        |       | Pin Buffer<br>Type Type |                       | Description                                                                                                                                                                                                       |  |  |

| 00000000000        |                       |                        |       |                         |                       | •                                                                                                                                                                                                                 |  |  |

| OSC1/CLKIN         | 16                    | 16                     | 18    |                         | ST/CMOS               | Oscillator crystal input/external clock source output.                                                                                                                                                            |  |  |

| OSC2/CLKOUT        | 15                    | 15                     | 17    | 0                       | _                     | Oscillator crystal output. Connects to crystal or resonator<br>in Crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |  |  |

| MCLR/VPP           | 4                     | 4                      | 4     | I/P                     | ST                    | Master clear (Reset) input/programming voltage input.<br>This pin is an active low RESET to the device.                                                                                                           |  |  |

| RA0                | 17                    | 17                     | 19    | I/O                     | ST                    | Bi-directional I/O port                                                                                                                                                                                           |  |  |

| RA1                | 18                    | 18                     | 20    | I/O                     | ST                    | Bi-directional I/O port                                                                                                                                                                                           |  |  |

| RA2                | 1                     | 1                      | 1     | I/O                     | ST                    | Bi-directional I/O port                                                                                                                                                                                           |  |  |

| RA3                | 2                     | 2                      | 2     | I/O                     | ST                    | Bi-directional I/O port                                                                                                                                                                                           |  |  |

| RA4/T0CKI          | 3                     | 3                      | 3     | I/O                     | ST                    | Bi-directional I/O port or external clock input for TMR0.<br>Output is open drain type.                                                                                                                           |  |  |

| RB0/INT            | 6                     | 6                      | 7     | I/O                     | TTL/ST <sup>(1)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. RB0/INT can also be selected as an external interrupt pin.                                                                          |  |  |

| RB1                | 7                     | 7                      | 8     | I/O                     | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |  |  |

| RB2                | 8                     | 8                      | 9     | I/O                     | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |  |  |

| RB3                | 9                     | 9                      | 10    | I/O                     | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up.                                                                                                                                     |  |  |

| RB4                | 10                    | 10                     | 11    | I/O                     | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                            |  |  |

| RB5                | 11                    | 11                     | 12    | I/O                     | TTL                   | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin.                                                                                                            |  |  |

| RB6                | 12                    | 12                     | 13    | I/O                     | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for<br>internal weak pull-up. Interrupt-on-change pin. Serial pro-<br>gramming clock.                                                                          |  |  |

| RB7                | 13                    | 13                     | 14    | I/O                     | TTL/ST <sup>(2)</sup> | Bi-directional I/O port can be software programmed for internal weak pull-up. Interrupt-on-change pin. Serial pro-<br>gramming data.                                                                              |  |  |

| RC0 <sup>(3)</sup> | 18                    | 18                     | 18    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| RC1 <sup>(3)</sup> | 19                    | 19                     | 19    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| RC2 <sup>(3)</sup> | 20                    | 20                     | 20    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| RC3 <sup>(3)</sup> | 21                    | 21                     | 21    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| RC4 <sup>(3)</sup> | 22                    | 22                     | 22    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| RC5 <sup>(3)</sup> | 22                    | 22                     | 22    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

|                    |                       |                        |       |                         |                       |                                                                                                                                                                                                                   |  |  |

| RC6 <sup>(3)</sup> | 24                    | 24                     | 24    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| RC7 <sup>(3)</sup> | 25                    | 25                     | 25    | I/O                     | TTL                   | Bi-directional I/O port input buffer.                                                                                                                                                                             |  |  |

| Vss                | 5                     | 5                      | 5,6   | P                       |                       | Ground reference for logic and I/O pins.                                                                                                                                                                          |  |  |

| VDD                | 14                    | 14                     | 15,16 | P                       |                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |  |  |

| Legend:            |                       | = Output<br>= Not used |       | /O = Input<br>= Input   | output                | P = Power<br>ST = Schmitt Trigger input                                                                                                                                                                           |  |  |

|                    |                       | L = TTL inp            |       | – input                 |                       |                                                                                                                                                                                                                   |  |  |

TABLE 3-1: PIC16C55X PINOUT DESCRIPTION

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

3: PIC16C557 only.

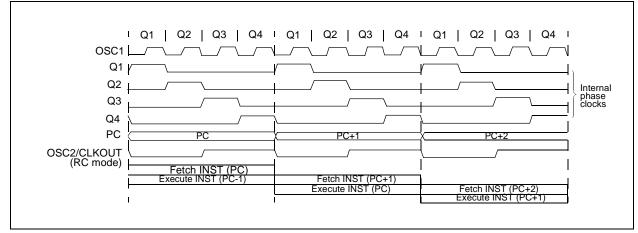

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-2.

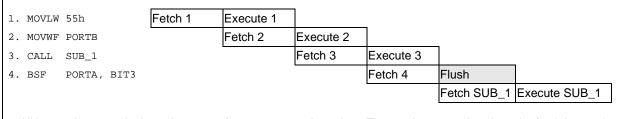

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle

while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

## 5.3 PORTC and TRISC Registers<sup>(1)</sup>

PORTC is a 8-bit wide latch. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISC register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISC register puts the contents of the output latch on the selected pin(s).

Reading the PORTC register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch

FIGURE 5-5: BLOCK DIAGRAM OF

#### PORT PINS RC<7:0> Data Bus D Q Vdd WR PORT ск 🔪 Q P Data Latch Q Ν D I/O pin WR T<u>RISC</u> Q ∘ск҇∢\_ Vss Vss TRIS Latch TTL Input Buffer RD TRISC Q D FN. **RD PORTC**

| Name | Bit # | Buffer Type | Function                 |

|------|-------|-------------|--------------------------|

| RC0  | Bit 0 | TTL         | Bi-directional I/O port. |

| RC1  | Bit 1 | TTL         | Bi-directional I/O port. |

| RC2  | Bit 2 | TTL         | Bi-directional I/O port. |

| RC3  | Bit 3 | TTL         | Bi-directional I/O port. |

| RC4  | Bit 4 | TTL         | Bi-directional I/O port. |

| RC5  | Bit 5 | TTL         | Bi-directional I/O port. |

| RC6  | Bit 6 | TTL         | Bi-directional I/O port. |

| RC7  | Bit 7 | TTL         | Bi-directional I/O port. |

Legend: ST = Schmitt Trigger, TTL = TTL input

#### TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC AND TRISC

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 07h     | PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx       | uuuu uuuu                       |

| 87h     | TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged Note 1: PIC16C557 ONLY.

#### 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

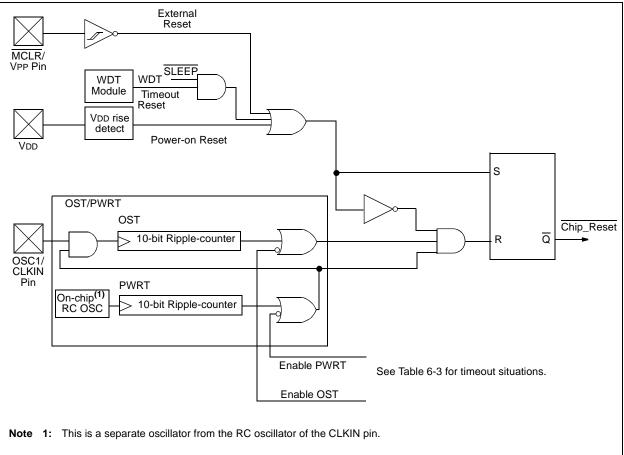

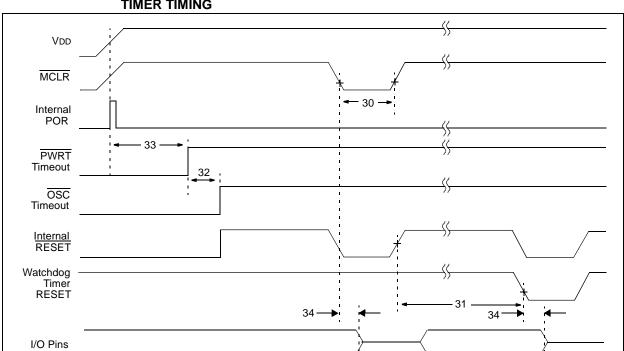

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### 6.3 RESET

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers. A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

#### 8.0 INSTRUCTION SET SUMMARY

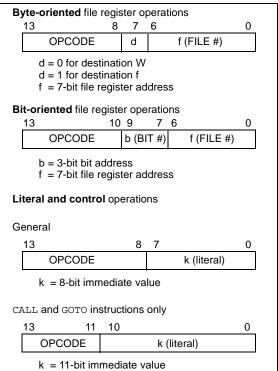

Each PIC16C55X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C55X instruction set summary in Table 8-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 8-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field         | Description                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                                              |

| x             | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It<br>is the recommended form of use for compatibil-<br>ity with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                       |

| label         | Label name                                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                                             |

| то            | Timeout bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                                          |

| [ ]           | Options                                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                                 |

| ∈             | In the set of                                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 8-1 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 8-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16C55X

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                       | IORWF                             | Inclusive OR W with f                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                  | Syntax:                           | [ <i>label</i> ] IORWF f,d                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                           | Operands:                         | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                             |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                             | Operation:                        | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                         | Status Affected:                  | Z                                                                                                                                                                       |

| Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                            | Encoding:                         | 00 0100 dfff ffff                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. | Description:<br>Words:<br>Cycles: | Inclusive OR the W register with<br>register 'f'. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>1 |

| Words:           | 1                                                                                                                                                                                                                                                                                                                            | Example                           | IORWF RESULT, 0                                                                                                                                                         |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                         |                                   | Before Instruction<br>RESULT = 0x13                                                                                                                                     |

| Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                                      |                                   | W = 0x91<br>After Instruction<br>RESULT = 0x13<br>W = 0x93                                                                                                              |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if $CNT = 0$ ,<br>PC = address CONTINUE<br>if $CNT \neq 0$ ,<br>PC = address HERE + 1                                                                                                                                                       |                                   | Z = 1                                                                                                                                                                   |

| IORLW            | Inclusiv                     | ve OR I           | Literal wit                                    | h W      |  |  |  |  |  |

|------------------|------------------------------|-------------------|------------------------------------------------|----------|--|--|--|--|--|

| Syntax:          | [ label ]                    | IORLV             | / k                                            |          |  |  |  |  |  |

| Operands:        | $0 \le k \le 2$              | $0 \le k \le 255$ |                                                |          |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W) |                   |                                                |          |  |  |  |  |  |

| Status Affected: | Z                            |                   |                                                |          |  |  |  |  |  |

| Encoding:        | 11                           | 1000              | kkkk                                           | kkkk     |  |  |  |  |  |

| Description:     | OR'ed with                   | n the eig         | e W register<br>ht bit literal<br>the W regist | 'k'. The |  |  |  |  |  |

| Words:           | 1                            |                   |                                                |          |  |  |  |  |  |

| Cycles:          | 1                            |                   |                                                |          |  |  |  |  |  |

| Example          | IORLW                        | 0x35              |                                                |          |  |  |  |  |  |

|                  | Before In                    | structio          | n                                              |          |  |  |  |  |  |

|                  | W                            | =                 | 0x9A                                           |          |  |  |  |  |  |

|                  | After Inst                   | ruction           |                                                |          |  |  |  |  |  |

|                  | W                            | =                 | 0xBF                                           |          |  |  |  |  |  |

|                  | Z                            | =                 | 1                                              |          |  |  |  |  |  |

| MOVLW            | Move L                                                                                     | iteral to | w    |      |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|-----------|------|------|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |           |      |      |  |  |  |

| Operands:        | $0 \le k \le 2\xi$                                                                         | 55        |      |      |  |  |  |

| Operation:       | $k \to (W)$                                                                                |           |      |      |  |  |  |

| Status Affected: | None                                                                                       |           |      |      |  |  |  |

| Encoding:        | 11                                                                                         | 00xx      | kkkk | kkkk |  |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |           |      |      |  |  |  |

| Words:           | 1                                                                                          |           |      |      |  |  |  |

| Cycles:          | 1                                                                                          |           |      |      |  |  |  |

| Example          | MOVLW                                                                                      | 0x5A      |      |      |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                              |           |      |      |  |  |  |

# PIC16C55X

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                            |  |  |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                  |              |      |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                               | RETUR        | N    |      |  |  |  |

| Operands:        | None                                                                                                                                                    |              |      |      |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                    |              |      |      |  |  |  |

| Status Affected: | None                                                                                                                                                    |              |      |      |  |  |  |

| Encoding:        | 00                                                                                                                                                      | 0000         | 0000 | 1000 |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two-cycle instruction. |              |      |      |  |  |  |

| Words:           | 1                                                                                                                                                       |              |      |      |  |  |  |

| Cycles:          | 2                                                                                                                                                       |              |      |      |  |  |  |

| Example          | RETURN                                                                                                                                                  |              |      |      |  |  |  |

|                  | After Inte<br>PC                                                                                                                                        | rrupt<br>= T | OS   |      |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            | F             |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            | Sy            |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   | O             |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                        | O             |  |  |  |

| Status Affected: | None                                                                                                                                                                                | St            |  |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   | Er            |  |  |  |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |               |  |  |  |

| Words:           | 1                                                                                                                                                                                   |               |  |  |  |

| Cycles:          | 2                                                                                                                                                                                   |               |  |  |  |

| Example          | CALL TABLE;W contains table<br>;offset value<br>;W now has table<br>value                                                                                                           | W<br>Cy<br>Ex |  |  |  |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>RETLW kn ; End of table<br>Before Instruction                                                              |               |  |  |  |

|                  | W = 0x07                                                                                                                                                                            |               |  |  |  |

|                  | After Instruction                                                                                                                                                                   |               |  |  |  |

|                  | W = value of k8                                                                                                                                                                     |               |  |  |  |

| RLF             | Rotate Left f through Carry                                                                                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| yntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                    |

| )perands:       | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                           |

| peration:       | See description below                                                                                                                                                                                       |

| tatus Affected: | С                                                                                                                                                                                                           |

| ncoding:        | 00 1101 dfff ffff                                                                                                                                                                                           |

| escription:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |

| Vords:          | 1                                                                                                                                                                                                           |

| ycles:          | 1                                                                                                                                                                                                           |

| xample          | RLF REG1,0                                                                                                                                                                                                  |

|                 | Before Instruction                                                                                                                                                                                          |

|                 | $\begin{array}{rcl} REG1 &= 1110 & 0110 \\ C &= 0 \end{array}$                                                                                                                                              |

|                 | After Instruction                                                                                                                                                                                           |

|                 | <b>REG1</b> = 1110 0110                                                                                                                                                                                     |

|                 | W = 1100 1100                                                                                                                                                                                               |

|                 | C = 1                                                                                                                                                                                                       |

| RRF               | Rotate                                                                                                                                                                                                       | Right f                                       | throu            | igh (              | Carry       |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|--------------------|-------------|--|

| Syntax:           | [ label ]                                                                                                                                                                                                    | RRF 1                                         | ,d               |                    |             |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$                                                                                                                                               | 7                                             |                  |                    |             |  |

| Operation:        | See desc                                                                                                                                                                                                     | ription b                                     | below            |                    |             |  |

| Status Affected:  | С                                                                                                                                                                                                            |                                               |                  |                    |             |  |

| Encoding:         | 00                                                                                                                                                                                                           | 1100                                          | dff              | f                  | ffff        |  |

| Description:      | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'. |                                               |                  |                    |             |  |

|                   |                                                                                                                                                                                                              |                                               |                  |                    |             |  |

|                   |                                                                                                                                                                                                              |                                               | Regist           | ter f              | ┠┺          |  |

| Words:            | 1                                                                                                                                                                                                            |                                               | Regist           | ter f              | ]•          |  |

| Words:<br>Cycles: | 1<br>1                                                                                                                                                                                                       | ]-▶[                                          | Regist           | ter f              | <b>]•</b> ] |  |

|                   | •                                                                                                                                                                                                            | ]-•[                                          |                  | ter f              | <b>]</b> •] |  |

| Cycles:           | 1                                                                                                                                                                                                            |                                               | REG              |                    | <u>}</u>    |  |

| Cycles:           | 1<br>RRF                                                                                                                                                                                                     | struction                                     | REG              | \$1,0              | .0          |  |

| Cycles:           | 1<br>RRF<br>Before Ins                                                                                                                                                                                       | struction                                     | REG<br>n<br>1110 | \$1,0              | .0          |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG                                                                                                                                                                                 | struction<br>1 = 1<br>= (                     | REG<br>n<br>1110 | \$1,0              | .0          |  |

| Cycles:           | 1<br>RRF<br>Before In<br>REG<br>C                                                                                                                                                                            | struction<br>1 = 1<br>= 0<br>ruction          | REG<br>n<br>1110 | \$1,0              | -           |  |

| Cycles:           | 1<br>RRF<br>Before Ins<br>REG<br>C<br>After Instr                                                                                                                                                            | struction<br>1 = 2<br>= 0<br>ruction<br>1 = 2 | REG<br>N<br>L110 | ;1,0<br>011<br>011 | .0          |  |

#### SLEEP

| Syntax:          | [ <i>label</i><br>]                                                                                                                                                                                                                                        | SLEEP |      |      |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|--|

| Operands:        | None                                                                                                                                                                                                                                                       |       |      |      |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ \text{prescaler}, \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$                                                                                  |       |      |      |  |  |

| Status Affected: | $\overline{\text{TO}}, \overline{\text{PD}}$                                                                                                                                                                                                               |       |      |      |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                         | 0000  | 0110 | 0011 |  |  |

| Description:     | The power-down status bit, <u>PD</u> is<br>cleared. Timeout status bit, <u>TO</u> is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 6.8 for more details. |       |      |      |  |  |

| Words:           | 1                                                                                                                                                                                                                                                          |       |      |      |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                          |       |      |      |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                      |       |      |      |  |  |

| SUBLW               | Subtract          | W from                                                                                                                               | n Literal   |          |  |  |  |  |

|---------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|--|--|--|--|

| Syntax:             | [label] S         | UBLW                                                                                                                                 | k           |          |  |  |  |  |

| Operands:           | $0 \le k \le 255$ | $0 \le k \le 255$                                                                                                                    |             |          |  |  |  |  |

| Operation:          | $k - (W) \to (W)$ |                                                                                                                                      |             |          |  |  |  |  |

| Status<br>Affected: | C, DC, Z          |                                                                                                                                      |             |          |  |  |  |  |

| Encoding:           | 11                | 110x                                                                                                                                 | kkkk        | kkkk     |  |  |  |  |

| Description:        | plement met       | The W register is subtracted (2's com-<br>plement method) from the eight bit literal<br>'k'. The result is placed in the W register. |             |          |  |  |  |  |

| Words:              | 1                 |                                                                                                                                      |             |          |  |  |  |  |

| Cycles:             | 1                 |                                                                                                                                      |             |          |  |  |  |  |

| Example 1:          | SUBLW             | 0x02                                                                                                                                 |             |          |  |  |  |  |

|                     | Before Inst       | ruction                                                                                                                              |             |          |  |  |  |  |

|                     | W                 | = 1                                                                                                                                  |             |          |  |  |  |  |

|                     | С                 | = ?                                                                                                                                  | <b>)</b>    |          |  |  |  |  |

|                     | After Instru      | ction                                                                                                                                |             |          |  |  |  |  |

|                     | W                 | = 1                                                                                                                                  |             |          |  |  |  |  |

|                     | С                 | = 1                                                                                                                                  | ; result is | positive |  |  |  |  |

| Example 2:          | Before Inst       | ruction                                                                                                                              |             |          |  |  |  |  |

|                     | W                 | = 2                                                                                                                                  | 2           |          |  |  |  |  |

|                     | С                 | = ?                                                                                                                                  | )           |          |  |  |  |  |

|                     | After Instru      | ction                                                                                                                                |             |          |  |  |  |  |

|                     | W                 | = 0                                                                                                                                  | )           |          |  |  |  |  |

|                     | С                 | = 1                                                                                                                                  | ; result is | s zero   |  |  |  |  |

| Example 3:          | Before Inst       | ruction                                                                                                                              |             |          |  |  |  |  |

|                     | W                 | = 3                                                                                                                                  | 3           |          |  |  |  |  |

|                     | С                 | = ?                                                                                                                                  | )           |          |  |  |  |  |

|                     | After Instru      | ction                                                                                                                                |             |          |  |  |  |  |

|                     | W                 |                                                                                                                                      | )xFF        |          |  |  |  |  |

|                     | C                 | = 0                                                                                                                                  | ); result i | s nega-  |  |  |  |  |

tive

$\odot$  1996-2013 Microchip Technology Inc.

## 9.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 9.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

#### 9.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

#### 9.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 10.0 ELECTRICAL SPECIFICATIONS

| Absolute Maximum Ratings †                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature under bias40° to +125°C                                                                                                      |

| Storage Temperature                                                                                                                              |

| Voltage on any pin with respect to Vss (except VDD and MCLR)0.6V to VDD +0.6V                                                                    |

| Voltage on VDD with respect to Vss 0 to +7.5V                                                                                                    |

| Voltage on MCLR with respect to Vss0 to +14V                                                                                                     |

| Total power Dissipation (Note 1)1.0W                                                                                                             |

| Maximum Current out of Vss pin                                                                                                                   |

| Maximum Current into VDD pin250 mA                                                                                                               |

| Input Clamp Current, Iικ (VI < 0 or VI > VDD)±20 mA                                                                                              |

| Output Clamp Current, IOK (V0 < 0 or V0 > VDD)±20 mA                                                                                             |

| Maximum Output Current sunk by any I/O pin25 mA                                                                                                  |

| Maximum Output Current sourced by any I/O pin25 mA                                                                                               |

| Maximum Current sunk by PORTA, PORTB and PORTC                                                                                                   |

| Maximum Current sourced by PORTA, PORTB and PORTC                                                                                                |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD-VOH) x IOH} + $\Sigma$ (VOI x IOL) |

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Characteristics |      |                                               |            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |            |        |                                                                                           |  |

|--------------------|------|-----------------------------------------------|------------|------------------------------------------------------|------------|--------|-------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym  | Characteristic                                | Min        | Тур†                                                 | Max        | Units  | Conditions                                                                                |  |

|                    | Vdd  | Supply Voltage                                |            |                                                      |            |        |                                                                                           |  |