Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 896B (512 x 14)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 80 × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc554t-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5.3 PORTC and TRISC Registers<sup>(1)</sup>

PORTC is a 8-bit wide latch. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISC register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISC register puts the contents of the output latch on the selected pin(s).

Reading the PORTC register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch

FIGURE 5-5: BLOCK DIAGRAM OF

#### PORT PINS RC<7:0> Data Bus D Q Vdd WR PORT ск 🔪 Q P Data Latch Q Ν D I/O pin WR T<u>RISC</u> Q ∘ск҇∢\_ Vss Vss TRIS Latch TTL Input Buffer RD TRISC Q D FN4 **RD PORTC**

| Name | Bit # | Buffer Type | Function                 |

|------|-------|-------------|--------------------------|

| RC0  | Bit 0 | TTL         | Bi-directional I/O port. |

| RC1  | Bit 1 | TTL         | Bi-directional I/O port. |

| RC2  | Bit 2 | TTL         | Bi-directional I/O port. |

| RC3  | Bit 3 | TTL         | Bi-directional I/O port. |

| RC4  | Bit 4 | TTL         | Bi-directional I/O port. |

| RC5  | Bit 5 | TTL         | Bi-directional I/O port. |

| RC6  | Bit 6 | TTL         | Bi-directional I/O port. |

| RC7  | Bit 7 | TTL         | Bi-directional I/O port. |

Legend: ST = Schmitt Trigger, TTL = TTL input

#### TABLE 5-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC AND TRISC

| Address | Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 07h     | PORTC | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx xxxx       | uuuu uuuu                       |

| 87h     | TRISC | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111       | 1111 1111                       |

Legend: x = unknown, u = unchanged Note 1: PIC16C557 ONLY.

#### **REGISTER 6-1: CONFIGURATION WORD**

|          | CP1                | CP0                                                                                                                                                    | CP1        | CP0         | CP1     | CP0 | — | Reserved | CP1 | CP0 | PWRTE | WDTE | F0SC1 | F0SC0 |

|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|---------|-----|---|----------|-----|-----|-------|------|-------|-------|

|          | bit 13             |                                                                                                                                                        |            |             |         |     |   |          |     |     |       |      |       | bit 0 |

|          |                    |                                                                                                                                                        |            | (4)         |         |     |   |          |     |     |       |      |       |       |

| bit 13-8 |                    |                                                                                                                                                        | protection |             | ion off |     |   |          |     |     |       |      |       |       |

| bit 5-4  | 10 = 04<br>01 = 02 | 11 = Program Memory code protection off<br>10 = 0400h - 07FFh code protected<br>01 = 0200h - 07FFh code protected<br>11 = 0000h - 07FFh code protected |            |             |         |     |   |          |     |     |       |      |       |       |

| bit 7    | Unimpl             | emented                                                                                                                                                | I: Read as | s '1'       |         |     |   |          |     |     |       |      |       |       |

| bit 6    | Reserv             | ed: Do no                                                                                                                                              | ot use     |             |         |     |   |          |     |     |       |      |       |       |

| bit 3    | 1 = PW             | <b>PWRTE</b> : Power-up Timer Enable bit         1 = PWRT disabled         0 = PWRT enabled                                                            |            |             |         |     |   |          |     |     |       |      |       |       |

| bit 2    | WDTE:              | Watchdo                                                                                                                                                | g Timer E  | nable bit   |         |     |   |          |     |     |       |      |       |       |

|          |                    | 1 = WDT enabled<br>0 = WDT disabled                                                                                                                    |            |             |         |     |   |          |     |     |       |      |       |       |

| bit 1-0  | FOSC1              | :FOSC0:                                                                                                                                                | Oscillator | r Selectior | n bits  |     |   |          |     |     |       |      |       |       |

|          |                    | C oscillato                                                                                                                                            |            |             |         |     |   |          |     |     |       |      |       |       |

|          |                    | 10 = HS oscillator<br>01 = XT oscillator                                                                                                               |            |             |         |     |   |          |     |     |       |      |       |       |

|          | 00 = LF            | 00 = LP oscillator                                                                                                                                     |            |             |         |     |   |          |     |     |       |      |       |       |

|          | Note               | Note 1: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.                                          |            |             |         |     |   |          |     |     |       |      |       |       |

|          |                    |                                                                                                                                                        |            |             |         |     |   |          |     |     |       |      |       |       |

|          | Legend             | 1:                                                                                                                                                     |            |             |         |     |   |          |     |     |       |      |       |       |

| Legend:                  |                  |                               |                    |

|--------------------------|------------------|-------------------------------|--------------------|

| R = Readable bit         | W = Writable bit | U = Unimplemented bit, read a | s '0'              |

| - n = Value at POR reset | '1' = Bit is set | '0' = Bit is cleared          | x = Bit is unknown |

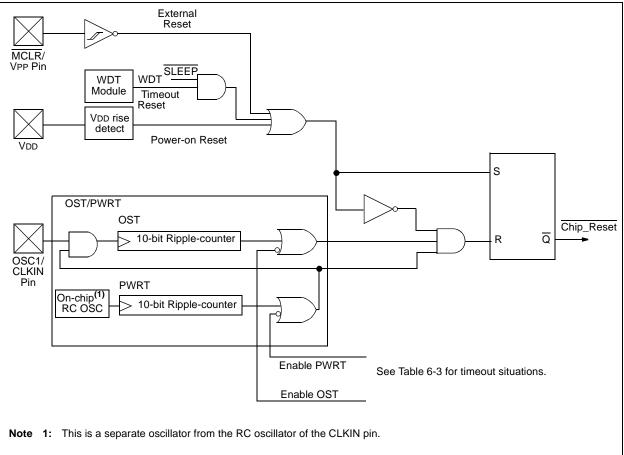

#### 6.3 RESET

The PIC16C55X differentiates between various kinds of RESET:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during SLEEP

- WDT Reset (normal operation)

- WDT wake-up (SLEEP)

Some registers are not affected in any RESET condition; their status is unknown on POR and unchanged in any other RESET. Most other registers are reset to a "RESET state" on Power-on Reset, on MCLR or WDT Reset and on MCLR Reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different RESET situations as indicated in Table 6-4. These bits are used in software to determine the nature of the RESET. See Table 6-6 for a full description of RESET states of all registers. A simplified block diagram of the on-chip RESET circuit is shown in Figure 6-6.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 10-3 for pulse width specification.

#### 6.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST)

#### 6.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.6V - 1.8V). To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details.

The POR circuit does not produce internal RESET when VDD declines.

When the device starts normal operation (exits the RESET condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in RESET until the operating conditions are met.

For additional information, refer to Application Note AN607 "Power-up Trouble Shooting".

#### 6.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) timeout on power-up only, from POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as PWRT is active. The PWRT delay allows the <u>VDD</u> to rise to an acceptable level. A configuration bit, <u>PWRTE</u> can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-Up Time delay will vary from chip to chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 6.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST timeout is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

#### 6.4.4 TIMEOUT SEQUENCE

On power-up, the timeout sequence is as follows: First PWRT timeout is invoked after POR has expired, then OST is activated. The total timeout will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no timeout at all. Figure 6-7, Figure 6-8 and Figure 6-9 depict timeout sequences.

Since the timeouts occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the timeouts will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 6-8). This is useful for testing purposes or to synchronize more than one PIC16C55X device operating in parallel.

Table 6-5 shows the RESET conditions for some special registers, while Table 6-6 shows the RESET conditions for all the registers.

#### TABLE 6-5:INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-               |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-               |

| MCLR Reset during SLEEP            | 000h                  | 0001 0uuu          | u-               |

| WDT Reset                          | 000h                  | 0000 uuuu          | u-               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | u-               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition. **Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

| Register             | Address | Power-on Reset | MCLR Reset during normal<br>operation<br>MCLR Reset during SLEEP<br>WDT Reset | Wake-up from SLEEP<br>through interrupt<br>Wake-up from SLEEP<br>through WDT timeout |

|----------------------|---------|----------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| W                    | —       | XXXX XXXX      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| INDF                 | 00h     | _              | _                                                                             | _                                                                                    |

| TMR0                 | 01h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PCL                  | 02h     | 0000 0000      | 0000 0000                                                                     | PC + 1 <sup>(2)</sup>                                                                |

| STATUS               | 03h     | 0001 1xxx      | 000q quuu <sup>(3)</sup>                                                      | uuuq quuu <sup>(3)</sup>                                                             |

| FSR                  | 04h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PORTA                | 05h     | x xxxx         | u uuuu                                                                        | u uuuu                                                                               |

| PORTB                | 06h     | xxxx xxxx      | uuuu uuuu                                                                     | uuuu uuuu                                                                            |

| PORTC <sup>(4)</sup> | 06h     | xxxx xxxx      | uuuu uuuu                                                                     | սսսս սսսս                                                                            |

| PCLATH               | 0Ah     | 0 0000         | 0 0000                                                                        | u uuuu                                                                               |

| INTCON               | 0Bh     | 0000 000x      | 0000 000u                                                                     | uuuu uuuu <sup>(1)</sup>                                                             |

| OPTION               | 81h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| TRISA                | 85h     | 1 1111         | 1 1111                                                                        | u uuuu                                                                               |

| TRISB                | 86h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| TRISC <sup>(4)</sup> | 86h     | 1111 1111      | 1111 1111                                                                     | uuuu uuuu                                                                            |

| PCON                 | 8Eh     | 0-             | u-                                                                            | u-                                                                                   |

#### TABLE 6-6: INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: One or more bits in INTCON will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

**3:** See Table 6-5 for RESET value for specific condition.

4: PIC16C557 only.

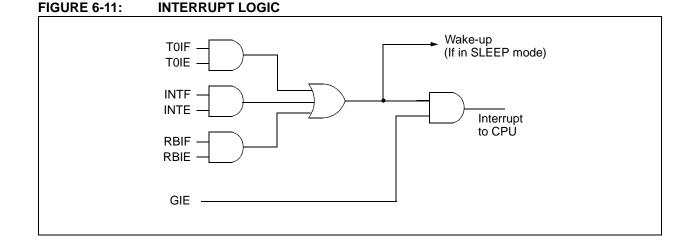

#### 6.5 Interrupts

The PIC16C55X has 3 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "Return from Interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 6-12). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

© 1996-2013 Microchip Technology Inc.

#### 6.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This will have to be implemented in software.

Example 6-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 6-1:

- Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- Restores the W register

#### EXAMPLE 6-1: SAVING THE STATUS AND W REGISTERS IN RAM

|       | 117            |                                           |

|-------|----------------|-------------------------------------------|

| MOVWF | W_TEMP         | ;copy W to TEMP<br>;register, could be in |

|       |                | -                                         |

|       |                | ;either bank                              |

| SWAPF | STATUS,W       | ;swap STATUS to be                        |

|       |                | ;saved into W                             |

| BCF   | STATUS, RPO    | ;change to bank0                          |

|       |                | ;regardless of                            |

|       |                | ;current bank                             |

| MOVWF | STATUS_TEMP    | ;save STATUS to bank0                     |

|       |                | ;register                                 |

| :     |                |                                           |

| :     |                |                                           |

| :     |                |                                           |

| SWAPF | STATUS_TEMP, W | 1;swap STATUS_TEMP                        |

|       |                | ;register into W, sets                    |

|       |                | ;bank to original state                   |

| MOVWF | STATUS         | ;move W into STATUS                       |

|       |                | ;register                                 |

| SWAPF | W_TEMP,F       | ;swap W_TEMP                              |

| SWAPF | W_TEMP,W       | ;swap W_TEMP into W                       |

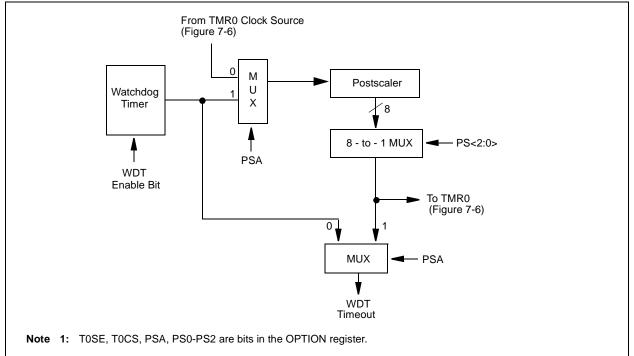

#### 6.7 Watchdog Timer (WDT)

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT timeout generates a device RESET. If the device is in SLEEP mode, a WDT timeout causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 6.1).

#### 6.7.1 WDT PERIOD

The WDT has a nominal timeout period of 18 ms, (with no prescaler). The timeout periods vary with temperature, VDD and process variations from part-to-part (see DC specs). If longer timeout periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, timeout periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer timeout.

#### 6.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler) it may take several seconds before a WDT timeout occurs.

| Address | Name         | Bit 7 | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on POR | Value on all other RESETS |

|---------|--------------|-------|----------|-------|-------|-------|-------|-------|-------|--------------|---------------------------|

| 2007h   | Config. bits | _     | Reserved | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |              |                           |

| 81h     | OPTION       | RBPU  | INTEDG   | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111    | 1111 1111                 |

Legend: x = unknown, u = unchanged, q = value depends on condition, — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

## 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

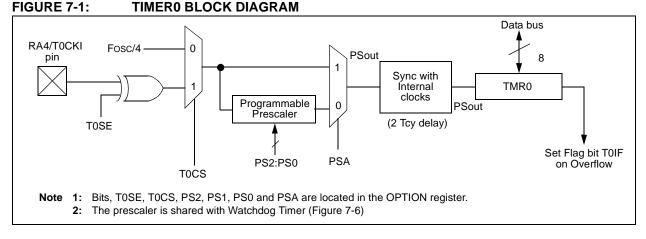

Figure 7-1 is a simplified block diagram of the Timer0 module.

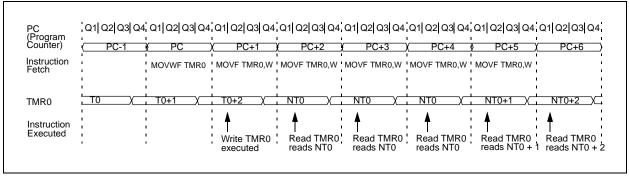

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 TIMER0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before reenabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

#### 7.2 Using Timer0 with External Clock

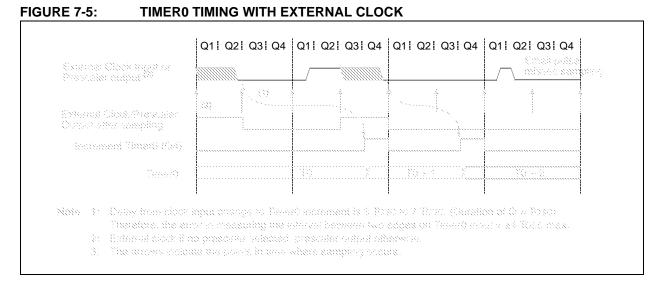

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### 7.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

Note: There is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

© 1996-2013 Microchip Technology Inc.

## 8.0 INSTRUCTION SET SUMMARY

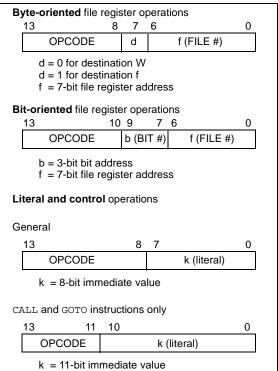

Each PIC16C55X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16C55X instruction set summary in Table 8-2 lists **byte-oriented**, **bitoriented**, and **literal and control** operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 8-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field         | Description                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                                              |

| x             | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It<br>is the recommended form of use for compatibil-<br>ity with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                       |

| label         | Label name                                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                                             |

| то            | Timeout bit                                                                                                                                                                        |

| PD            | Power-down bit                                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                                          |

| [ ]           | Options                                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                                 |

| ∈             | In the set of                                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 8-1 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

Figure 8-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16C55X

| CLRW             | Clear W                              | V        |              |        |

|------------------|--------------------------------------|----------|--------------|--------|

| Syntax:          | [ label ]                            | CLRW     |              |        |

| Operands:        | None                                 |          |              |        |

| Operation:       | $00h \rightarrow (V 1 \rightarrow Z$ | V)       |              |        |

| Status Affected: | Z                                    |          |              |        |

| Encoding:        | 00                                   | 0001     | 0000         | 0011   |

| Description:     | W register set.                      | is clear | ed. Zero bit | (Z) is |

| Words:           | 1                                    |          |              |        |

| Cycles:          | 1                                    |          |              |        |

| Example          | CLRW                                 |          |              |        |

|                  | Before In                            | structio | n            |        |

|                  | W                                    | =        | 0x5A         |        |

|                  | After Instruction                    |          |              |        |

|                  | W                                    | =        | 0x00         |        |

|                  | Z                                    | =        | 1            |        |

| COMF             | Comple                                                         | ement f                            |                              |      |  |  |  |

|------------------|----------------------------------------------------------------|------------------------------------|------------------------------|------|--|--|--|

| Syntax:          | [ label ]                                                      | [label] COMF f,d                   |                              |      |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in [0,1] \end{array}$ | $0 \le f \le 127$<br>$d \in [0,1]$ |                              |      |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (des$                              | st)                                |                              |      |  |  |  |

| Status Affected: | Z                                                              |                                    |                              |      |  |  |  |

| Encoding:        | 00                                                             | 1001                               | dfff                         | ffff |  |  |  |

| Description:     | The conter<br>compleme<br>stored in V<br>stored bac            | nted. If 'd<br>V. If 'd' is        | ' is 0 the re<br>1 the resul |      |  |  |  |

| Words:           | 1                                                              |                                    |                              |      |  |  |  |

| Cycles:          | 1                                                              |                                    |                              |      |  |  |  |

| Example          | COMF                                                           | REG1,0                             | )                            |      |  |  |  |

|                  | Before Instruction                                             |                                    |                              |      |  |  |  |

|                  | REG                                                            | 1 =                                | 0x13                         |      |  |  |  |

|                  | After Instruction                                              |                                    |                              |      |  |  |  |

|                  | REG                                                            | 1 =                                | 0x13                         |      |  |  |  |

|                  | W                                                              | =                                  | 0xEC                         |      |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                          |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] CLRWDT                                                                                                                                                |  |

| Operands:        | None                                                                                                                                                          |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$      |  |

| Status Affected: | TO, PD                                                                                                                                                        |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                             |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. |  |

| Words:           | 1                                                                                                                                                             |  |

| Cycles:          | 1                                                                                                                                                             |  |

| Example          | CLRWDT                                                                                                                                                        |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction                                                                                                    |  |

|                  | WDT counter = $0x00$                                                                                                                                          |  |

|                  | $\underline{WDT}$ prescaler = 0                                                                                                                               |  |

|                  | $\overline{TO} = 1$                                                                                                                                           |  |

|                  | PD = 1                                                                                                                                                        |  |

....

| DECF             | Decrement f                                                                                                                                 |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                           |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |  |  |  |  |

| Status Affected: | Z                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                           |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                           |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                                 |  |  |  |  |

|                  | Before Instruction                                                                                                                          |  |  |  |  |

|                  | CNT = 0x01                                                                                                                                  |  |  |  |  |

|                  | Z = 0                                                                                                                                       |  |  |  |  |

|                  | After Instruction                                                                                                                           |  |  |  |  |

|                  | CNT = 0x00                                                                                                                                  |  |  |  |  |

|                  | Z = 1                                                                                                                                       |  |  |  |  |

|                  |                                                                                                                                             |  |  |  |  |

## 9.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC<sup>™</sup> In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup>1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

#### 9.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup>-based application that contains:

- · An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- · A project manager

- Customizable toolbar and key mapping

- · A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the costeffective simulator to a full-featured emulator with minimal retraining.

#### 9.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PIC MCUs.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

#### 9.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 9.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

#### 9.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

#### 9.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 9.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

#### 9.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

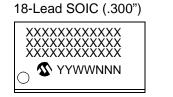

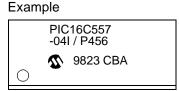

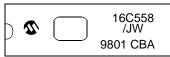

#### Package Marking Information (Cont'd)

#### Example PIC16C558 -04I / S0218 S0218 9818 CDK

$\cap$

####

#### 18-Lead CERDIP Windowed

#### Example

#### 28-Lead CERDIP Windowed

Example

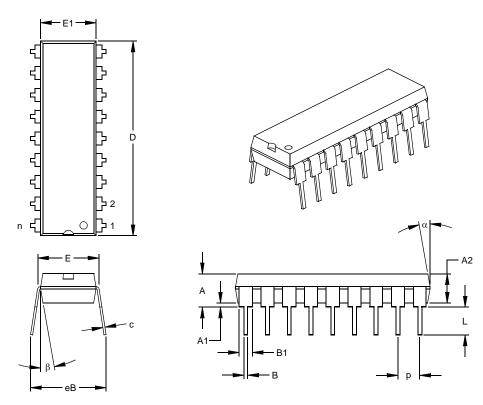

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                            | Units    | INCHES* |      |      | MILLIMETERS |       |       |

|----------------------------|----------|---------|------|------|-------------|-------|-------|

| Dimensio                   | n Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n        |         | 18   |      |             | 18    |       |

| Pitch                      | р        |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | А        | .140    | .155 | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2       | .115    | .130 | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1       | .015    |      |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е        | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1       | .240    | .250 | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D        | .890    | .898 | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L        | .125    | .130 | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С        | .008    | .012 | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1       | .045    | .058 | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В        | .014    | .018 | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing §      | eB       | .310    | .370 | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α        | 5       | 10   | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β        | 5       | 10   | 15   | 5           | 10    | 15    |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-007

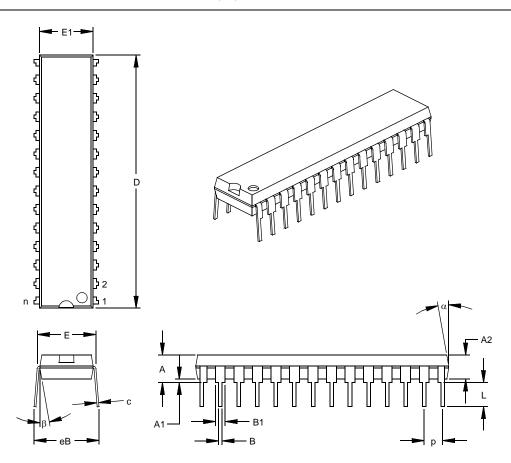

## 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| ision L | imits<br>n<br>p | MIN                                                                                                              | NOM                                                    | MAX                                                     | MIN                                                    | NOM                                                    | MAX                                                     |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

|         |                 |                                                                                                                  |                                                        |                                                         |                                                        |                                                        | 100 01                                                  |

|         | n               |                                                                                                                  | 28                                                     |                                                         |                                                        | 28                                                     |                                                         |

|         | Р               |                                                                                                                  | .100                                                   |                                                         |                                                        | 2.54                                                   |                                                         |

|         | Α               | .140                                                                                                             | .150                                                   | .160                                                    | 3.56                                                   | 3.81                                                   | 4.06                                                    |

|         | A2              | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|         | A1              | .015                                                                                                             |                                                        |                                                         | 0.38                                                   |                                                        |                                                         |

|         | Е               | .300                                                                                                             | .310                                                   | .325                                                    | 7.62                                                   | 7.87                                                   | 8.26                                                    |

|         | E1              | .275                                                                                                             | .285                                                   | .295                                                    | 6.99                                                   | 7.24                                                   | 7.49                                                    |

|         | D               | 1.345                                                                                                            | 1.365                                                  | 1.385                                                   | 34.16                                                  | 34.67                                                  | 35.18                                                   |

|         | L               | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|         | С               | .008                                                                                                             | .012                                                   | .015                                                    | 0.20                                                   | 0.29                                                   | 0.38                                                    |

|         | B1              | .040                                                                                                             | .053                                                   | .065                                                    | 1.02                                                   | 1.33                                                   | 1.65                                                    |

|         | В               | .016                                                                                                             | .019                                                   | .022                                                    | 0.41                                                   | 0.48                                                   | 0.56                                                    |

| §       | eB              | .320                                                                                                             | .350                                                   | .430                                                    | 8.13                                                   | 8.89                                                   | 10.92                                                   |

|         | α               | 5                                                                                                                | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

|         | β               | 5                                                                                                                | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

|         | §               | A           A2           A1           E           D           L           C           B1           §           α | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

## INDEX

#### A

| ADDLW Instruction      |    |

|------------------------|----|

| ADDWF Instruction      |    |

| ANDLW Instruction      |    |

| ANDWF Instruction      |    |

| Architectural Overview | 9  |

| Assembler              |    |

| MPASM Assembler        | 67 |

|                        |    |

## В

| BCF Instruction    |    |

|--------------------|----|

| Block Diagram      |    |

| TIMER0             | 47 |

| TMR0/WDT PRESCALER | 50 |

| BSF Instruction    |    |

| BTFSC Instruction  |    |

| BTFSS Instruction  | 57 |

|                    |    |

## С

| CALL Instruction                  | 57 |

|-----------------------------------|----|

| Clocking Scheme/Instruction Cycle |    |

| CLRF Instruction                  | 57 |

| CLRW Instruction                  |    |

| CLRWDT Instruction                |    |

| Code Protection                   |    |

| COMF Instruction                  |    |

| Configuration Bits                | 31 |

|                                   |    |

## D

| Data Memory Organization |    |

|--------------------------|----|

| DECF Instruction         | 58 |

| DECFSZ Instruction       | 59 |

| Development Support      | 67 |

## Ε

| Errata3                             |  |

|-------------------------------------|--|

| External Crystal Oscillator Circuit |  |

## G

| General purpose Register File13 |  |

|---------------------------------|--|

| GOTO Instruction                |  |

## I

|                                             | ~~ |

|---------------------------------------------|----|

| I/O Ports                                   |    |

| I/O Programming Considerations              | 28 |

| ICEPIC In-Circuit Emulator                  |    |

| ID Locations                                | 46 |

| INCF Instruction                            |    |

| INCFSZ Instruction                          |    |

| In-Circuit Serial Programming               | 46 |

| Indirect Addressing, INDF and FSR Registers | 21 |

| Instruction Flow/Pipelining                 | 12 |

| Instruction Set                             |    |

| ADDLW                                       | 55 |

| ADDWF                                       | 55 |

| ANDLW                                       | 55 |

| ANDWF                                       | 55 |

| BCF                                         | 56 |

| BSF                                         | 56 |

| BTFSC                                       | 56 |

| BTFSS                                       | 67 |

| B1F33                                       | 57 |

| CALL                                        |    |

| CLRW                    | 58 |

|-------------------------|----|

| CLRWDT                  | 58 |

| COMF                    | 58 |

| DECF                    | 58 |

| DECFSZ                  | 59 |

| GOTO                    | 59 |

| INCF                    | 59 |

| INCFSZ                  | 60 |

| IORLW                   | 60 |

| IORWF                   | 60 |

| MOVF                    | 61 |

| MOVLW                   | 60 |

| MOVWF                   | 61 |

| NOP                     | 61 |

| OPTION                  | 61 |

| RETFIE                  | 62 |

| RETLW                   | 62 |

| RETURN                  | 62 |

| RLF                     | 62 |

| RRF                     | 63 |

| SLEEP                   | 63 |

| SUBLW                   | 63 |

| SUBWF                   | 64 |

| SWAPF                   | 64 |

| TRIS                    | 64 |

| XORLW                   | 65 |

| XORWF                   | 65 |

| Instruction Set Summary | 53 |

| INT Interrupt           | 42 |

| INTCON Register         | 19 |

| Interrupts              | 41 |

| IORLW Instruction       | 60 |

| IORWF Instruction       | 60 |

|                         |    |

## Κ

## М

| MOVF Instruction                                         |

|----------------------------------------------------------|

| MOVLW Instruction                                        |

| MOVWF Instruction                                        |

| MPLAB C17 and MPLAB C18 C Compilers 67                   |

| MPLAB ICD In-Circuit Debugger 69                         |

| MPLAB ICE High Performance Universal In-Circuit Emulator |

| with MPLAB IDE 68                                        |

| MPLAB Integrated Development Environment Software 67     |

| MPLINK Object Linker/MPLIB Object Librarian 68           |

## Ν

| NOP Instruction | 61 |

|-----------------|----|

|                 | 01 |

#### 0

| One-Time-Programmable (OTP) Devices | 7  |

|-------------------------------------|----|

| OPTION Instruction                  | 61 |

| OPTION Register                     |    |

| Oscillator Configurations           | 33 |

| Oscillator Start-up Timer (OST)     | 36 |

## Ρ

| ) |

|---|

| ) |

| ) |

| ) |

| ) |

|   |

NOTES:

## Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Fax: 45-4485-2829

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12