Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc558-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 MEMORY ORGANIZATION

## 4.1 Program Memory Organization

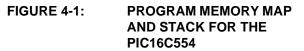

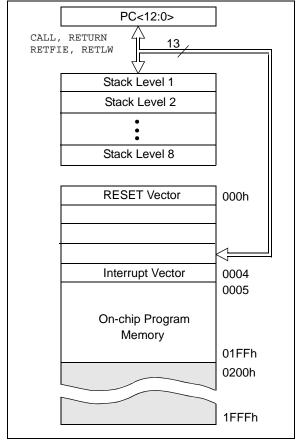

The PIC16C55X has a 13-bit program counter capable of addressing an 8 K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16C554 and 2K x 14 (0000h - 07FFh) for the PIC16C557 and PIC16C558 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 spaces in the PIC16C554, or 2K x 14 space of the PIC16C558 and PIC16C557. The RESET vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2).

#### FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC16C557 AND PIC16C558

## 4.2 Data Memory Organization

The data memory (Figure 4-3 through Figure 4-5) is partitioned into two banks which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). Bank 0 is selected when the RP0 bit (STATUS <5>) is cleared. Bank 1 is selected when the RP0 bit is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-6Fh (Bank 0) on the PIC16C554 and 20-7Fh (Bank 0) and A0-BFh (Bank 1) on the PIC16C558 and PIC16C557 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $80 \times 8$  in the PIC16C554 and 128 x 8 in the PIC16C557 and PIC16C558. Each can be accessed either directly or indirectly through the File Select Register, FSR (Section 4.4).

#### 4.2.2.1 STATUS Register

The STATUS register, shown in Figure 4-2, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as the destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the STATUS register because these instructions do not affect any status bits. For other instructions, not affecting any status bits, see the "Instruction Set Summary".

- Note 1: The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16C55X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

|         | Reserved                                                                                                                                                                                                                                                                      | Reserved                                        | R/W-0   | R-1           | R-1      | R/W-x          | R/W-x       | R/W-x |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------|---------------|----------|----------------|-------------|-------|

|         | IRP                                                                                                                                                                                                                                                                           | RP1                                             | RP0     | TO            | PD       | Z              | DC          | С     |

|         | bit7                                                                                                                                                                                                                                                                          |                                                 |         |               |          |                |             | bit0  |

| bit 7   | IRP: Register Bank Select bit (used for Indirect addressing)<br>1 = Bank 2, 3 (100h - 1FFh)<br>0 = Bank 0, 1 (00h - FFh)<br>The IRP bit is reserved on the PIC16C55X, always maintain this bit clear                                                                          |                                                 |         |               |          |                |             |       |

| bit 6-5 | <b>RP1:RP0</b> : Register Bank Select bits (used for Direct addressing) 11 = Bank 3 (180h - 1FFh) 10 = Bank 2 (100h - 17Fh) 01 = Bank 1 (80h - FFh) 00 = Bank 0 (00h - 7Fh) Each bank is 128 bytes. The RP1 bit is reserved on the PIC16C55X, always maintain this bit clear. |                                                 |         |               |          |                |             | ear.  |

| bit 4   |                                                                                                                                                                                                                                                                               | bit<br>/er-up, CLRWDT<br>meout occurred         |         | or sleep inst | truction |                |             |       |

| bit 3   | •                                                                                                                                                                                                                                                                             | own bit<br>/er-up or by the<br>tion of the SLE: |         |               |          |                |             |       |

| bit 2   | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                                                   |                                                 |         |               |          |                |             |       |

| bit 1   | DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed) <ol> <li>A carry-out from the 4th low order bit of the result occurred</li> <li>No carry-out from the 4th low order bit of the result</li> </ol>                   |                                                 |         |               |          |                |             |       |

| bit 0   | C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                |                                                 |         |               |          |                |             |       |

| Note 1: |                                                                                                                                                                                                                                                                               | e polarity is reve<br>otate (RRF, RL<br>r.      |         |               |          |                |             |       |

|         | Legend:                                                                                                                                                                                                                                                                       |                                                 |         |               |          |                |             |       |

|         | R = Readable                                                                                                                                                                                                                                                                  | ə bit                                           | W = Wri | itable bit    | U = Unim | plemented bit, | read as '0' |       |

- n = Value at POR reset

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

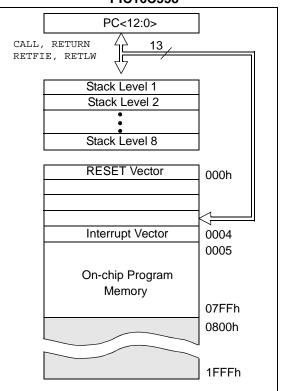

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB7:RB4, have an interrupt-onchange feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (this will end the mismatch condition)

- Clear flag bit RBIF

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

The interrupt on mismatch feature, together with software configurable pull-ups on these four pins, allows easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552 in the Microchip *Embedded Control Handbook*.)

**Note 1:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

## FIGURE 5-3: BLOCK DIAGRAM OF RB7:RB4 PINS

NOTES:

## 6.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16C55X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. RESET

- 3. Power-on Reset (POR)

- 4. Power-up Timer (PWRT)

- 5. Oscillator Start-Up Timer (OST)

- 6. Interrupts

- 7. Watchdog Timer (WDT)

- 8. SLEEP

- 9. Code protection

- 10. ID Locations

- 11. In-circuit serial programming<sup>™</sup>

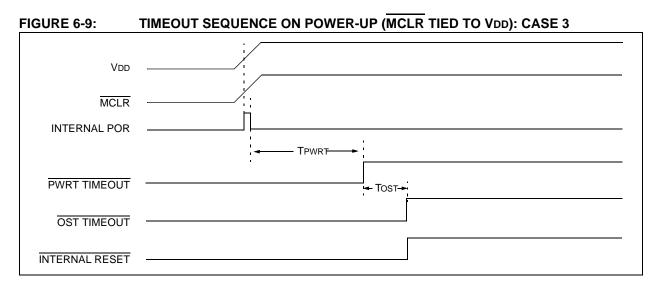

The PIC16C55X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), which is intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two functions onchip, most applications need no external RESET circuitry.

The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through external RESET, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 6.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

# PIC16C55X

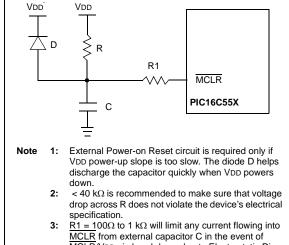

### FIGURE 6-10: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

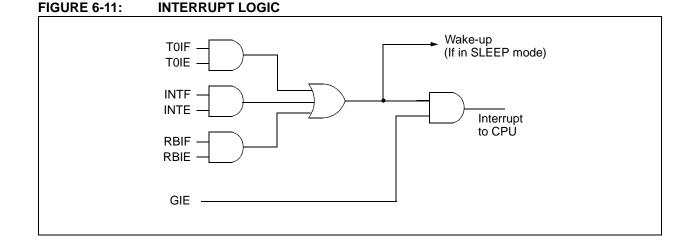

## 6.5 Interrupts

The PIC16C55X has 3 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "Return from Interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

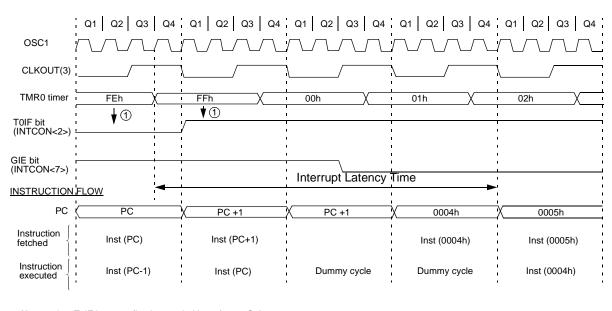

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 6-12). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

© 1996-2013 Microchip Technology Inc.

# **PIC16C55X**

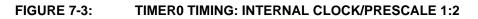

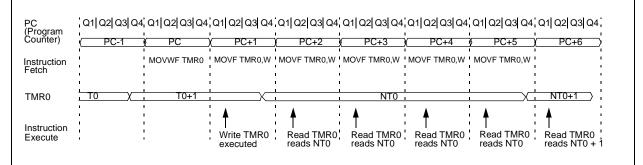

T0IF interrupt flag is sampled here (every Q1). Note 1:

Interrupt latency = 4 Tcr, where Tcr = instruction cycle time. CLKOUT is available only in RC Oscillator mode. 2:

3:

NOTES:

# 8.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                       |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                       |  |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                       |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                |  |  |  |  |  |  |

| Encoding:        | 11 111x kkkk kkkk                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                       |  |  |  |  |  |  |

| Example          | ADDLW 0x15                                                                                                              |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                      |  |  |  |  |  |  |

|                  | W = 0x10                                                                                                                |  |  |  |  |  |  |

|                  | After Instruction                                                                                                       |  |  |  |  |  |  |

|                  | W = 0x25                                                                                                                |  |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                                         |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                                             |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                    |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                  |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                              |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |  |

|                  | W = 0xD9                                                                                                                                                                  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                                |  |  |  |  |  |

| ANDLW            | AND Literal with W                                                                                                  |           |       |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|-----------|-------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                           | ANDLW     | / k   |      |  |  |  |

| Operands:        | $0 \le k \le 2$                                                                                                     | 255       |       |      |  |  |  |

| Operation:       | (W) .AN                                                                                                             | ID. (k) → | • (W) |      |  |  |  |

| Status Affected: | Z                                                                                                                   |           |       |      |  |  |  |

| Encoding:        | 11                                                                                                                  | 1001      | kkkk  | kkkk |  |  |  |

|                  | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |           |       |      |  |  |  |

| Words:           | 1                                                                                                                   |           |       |      |  |  |  |

| Cycles:          | 1                                                                                                                   |           |       |      |  |  |  |

| Example          | ANDLW 0x5F                                                                                                          |           |       |      |  |  |  |

|                  | Before Instruction                                                                                                  |           |       |      |  |  |  |

|                  | W = 0xA3                                                                                                            |           |       |      |  |  |  |

|                  | After Instruction                                                                                                   |           |       |      |  |  |  |

|                  | W                                                                                                                   | =         | 0x03  |      |  |  |  |

| ANDWF            | AND W with f                                                                                                                                              |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                                                                                         |  |  |  |  |  |  |

|                  | $d \in [0,1]$                                                                                                                                             |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                         |  |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |  |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                         |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                         |  |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                              |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                        |  |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |  |

|                  | FSR = 0xC2                                                                                                                                                |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                         |  |  |  |  |  |  |

|                  | W = 0x17                                                                                                                                                  |  |  |  |  |  |  |

|                  | FSR = 0x02                                                                                                                                                |  |  |  |  |  |  |

-

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•<br>•                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE+1                                                                                                                                        |  |  |  |  |  |

| GOTO                                                                                | Unconditional Branch                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                             | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Operands:                                                                           | $0 \le k \le 2047$                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Operation:                                                                          | $k \rightarrow PC < 10:0 >$                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                                                                     | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Status Affected:                                                                    | None                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:                                                                           | 10 lkkk kkkk kkkk                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:                                                                        | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.                                                                              |  |  |  |  |  |  |

| Words:                                                                              | 1                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Cycles:                                                                             | 2                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Example                                                                             | GOTO THERE                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                                                                     | After Instruction                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| INCF                                                                                | PC = Address THERE                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| _                                                                                   | Increment f                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| INCF<br>Syntax:<br>Operands:                                                        |                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Syntax:                                                                             | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$                                                                                                                                                                                                              |  |  |  |  |  |  |

| Syntax:<br>Operands:                                                                | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                             |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                  | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest)                                                                                                                                                             |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                        |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Increment f[ label ] INCF f,d $0 \le f \le 127$ $d \in [0,1]$ (f) + 1 $\rightarrow$ (dest)Z001010dffffffThe contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the                                            |  |  |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Increment f[ label ]INCF f,d $0 \le f \le 127$ $d \in [0,1]$ $(f) + 1 \rightarrow (dest)$ Z001010dfffffffThe contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the<br>result is placed back in register 'f'. |  |  |  |  |  |  |

INCF CNT, 1 Before Instruction CNT = 0xFFZ = 0After Instruction CNT = 0x00Z = 1

| XORLW            | Exclusive OR Literal with W                                                                                             |                       |      |      |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                |                       |      |      |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                       |                       |      |      |  |  |

| Operation:       | (W) .XOR                                                                                                                | $k$ . k → ( $\lambda$ | N)   |      |  |  |

| Status Affected: | Z                                                                                                                       |                       |      |      |  |  |

| Encoding:        | 11                                                                                                                      | 1010                  | kkkk | kkkk |  |  |

| Description:     | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W register. |                       |      |      |  |  |

| Words:           | 1                                                                                                                       |                       |      |      |  |  |

| Cycles:          | 1                                                                                                                       |                       |      |      |  |  |

| Example:         | XORLW 0xAF                                                                                                              |                       |      |      |  |  |

|                  | Before Instruction                                                                                                      |                       |      |      |  |  |

|                  | W                                                                                                                       | =                     | 0xB5 |      |  |  |

|                  | After Instruction                                                                                                       |                       |      |      |  |  |

|                  | W                                                                                                                       | =                     | 0x1A |      |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                     |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                           |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |  |  |

| Encoding:        | 00 0110 dfff ffff                                                                                                                                                         |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                         |  |  |  |  |  |

| Example          | XORWF REG 1                                                                                                                                                               |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                        |  |  |  |  |  |

|                  | REG = 0xAF<br>W = 0xB5                                                                                                                                                    |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                         |  |  |  |  |  |

|                  | REG = 0x1A                                                                                                                                                                |  |  |  |  |  |

|                  | W = 0xB5                                                                                                                                                                  |  |  |  |  |  |

$\odot$  1996-2013 Microchip Technology Inc.

## 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

| DC Characteristics |      |                                               |            | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial and} \\ & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for commercial and} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |            |        |                                                                                           |

|--------------------|------|-----------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                                | Min        | Тур†                                                                                                                                                                                                                                                                                                                                | Max        | Units  | Conditions                                                                                |

|                    | Vdd  | Supply Voltage                                |            |                                                                                                                                                                                                                                                                                                                                     |            |        |                                                                                           |

| D001               |      | 16LC55X                                       | 3.0<br>2.5 | _                                                                                                                                                                                                                                                                                                                                   | 5.5<br>5.5 | V      | XT and RC osc configuration<br>LP osc configuration                                       |

| D001<br>D001A      |      | 16C55X                                        | 3.0<br>4.5 |                                                                                                                                                                                                                                                                                                                                     | 5.5<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration                                   |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>  | —          | 1.5*                                                                                                                                                                                                                                                                                                                                | —          | V      | Device in SLEEP mode                                                                      |

| D003               | VPOR | VDD Start Voltage to<br>ensure Power-on Reset | —          | Vss                                                                                                                                                                                                                                                                                                                                 | —          | V      | See Section 6.4, Power-on Reset for details                                               |

| D004               | SVDD | VDD Rise Rate to ensure<br>Power-on Reset     | 0.05*      | _                                                                                                                                                                                                                                                                                                                                   | —          | V/ms   | See Section 6.4, Power-on Reset for details                                               |

|                    | Idd  | Supply Current <sup>(2)</sup>                 |            |                                                                                                                                                                                                                                                                                                                                     |            |        |                                                                                           |

| D010               |      | 16LC55X                                       | _          | 1.4                                                                                                                                                                                                                                                                                                                                 | 2.5        | mA     | XT and RC osc configuration<br>Fosc = 2.0 MHz, VDD = 3.0V, WDT<br>disabled <sup>(4)</sup> |

| D010A              |      |                                               | _          | 26                                                                                                                                                                                                                                                                                                                                  | 53         | μA     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT<br>disabled                        |

| D010               |      | 16C55X                                        | _          | 1.8                                                                                                                                                                                                                                                                                                                                 | 3.3        | mA     | XT and RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V,<br>WDT disabled <sup>(4)</sup>   |

| D010A              |      |                                               | _          | 35                                                                                                                                                                                                                                                                                                                                  | 70         | μΑ     | LP osc configuration,<br>PIC16C55X-04 only<br>Fosc = 32 kHz, VDD = 4.0V,<br>WDT disabled  |

| D013               |      |                                               | —          | 9.0                                                                                                                                                                                                                                                                                                                                 | 20         | mA     | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V,<br>WDT disabled                        |

These parameters are characterized but not tested.

† Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

<u>OSC1</u> = external square wave, from rail to rail; all I/O pins configured as input, pulled to VDD, MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as input and tied to VDD or Vss.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# 10.3 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

#### 1. TppS2ppS

2. TppS

| т      |                                               |    |              |  |  |  |  |

|--------|-----------------------------------------------|----|--------------|--|--|--|--|

| F      | Frequency                                     | Т  | Time         |  |  |  |  |

| Lowerc | Lowercase subscripts (pp) and their meanings: |    |              |  |  |  |  |

| рр     |                                               |    |              |  |  |  |  |

| ck     | CLKOUT                                        | OS | OSC1         |  |  |  |  |

| io     | I/O port                                      | t0 | TOCKI        |  |  |  |  |

| mc     | MCLR                                          |    |              |  |  |  |  |

| Upperc | Uppercase letters and their meanings:         |    |              |  |  |  |  |

| S      |                                               |    |              |  |  |  |  |

| F      | Fall                                          | Р  | Period       |  |  |  |  |

| Н      | High                                          | R  | Rise         |  |  |  |  |

| I      | Invalid (Hi-impedance)                        | V  | Valid        |  |  |  |  |

| L      | Low                                           | Z  | Hi-impedance |  |  |  |  |

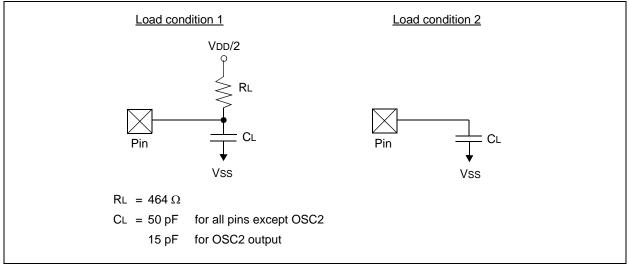

## FIGURE 10-5: LOAD CONDITIONS

| Parameter # | Sym        | Characteristic                                             | Min          | Typ† | Max | Units |  |  |

|-------------|------------|------------------------------------------------------------|--------------|------|-----|-------|--|--|

| 10*         | TosH2ckL   | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                            | _            | 75   | 200 | ns    |  |  |

|             |            |                                                            | —            |      | 400 | ns    |  |  |

| 11*         | TosH2ckH   | OSC1↑ to CLKOUT↑ <sup>(1)</sup>                            | _            | 75   | 200 | ns    |  |  |

|             |            |                                                            | —            | —    | 400 | ns    |  |  |

| 12*         | TckR       | CLKOUT rise time <sup>(1)</sup>                            | —            | 35   | 100 | ns    |  |  |

|             |            |                                                            | _            | —    | 200 | ns    |  |  |

| 13*         | TckF       | CLKOUT fall time <sup>(1)</sup>                            | —            | 35   | 100 | ns    |  |  |

|             |            |                                                            | _            | —    | 200 | ns    |  |  |

| 14*         | TckL2ioV   | CLKOUT ↓ to Port out valid <sup>(1)</sup>                  | —            | —    | 20  | ns    |  |  |

| 15*         | TioV2ckH   | Port in valid before CLKOUT $\uparrow$ <sup>(1)</sup>      | Tosc +200 ns | _    | _   | ns    |  |  |

|             |            |                                                            | Tosc +400 ns | —    |     | ns    |  |  |

| 16*         | TckH2iol   | Port in hold after CLKOUT $\uparrow$ <sup>(1)</sup>        | 0            | _    | —   | ns    |  |  |

| 17*         | TosH2ioV   | OSC1↑ (Q1 cycle) to Port out valid                         | —            | 50   | 150 | ns    |  |  |

|             |            |                                                            | _            |      | 300 | ns    |  |  |

| 18*         | TosH2iol   | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in | 100          | —    | —   | ns    |  |  |

|             |            | hold time)                                                 | 200          | —    |     | ns    |  |  |

| 19*         | TioV2osH   | Port input valid to OSC1 <sup>↑</sup> (I/O in setup time)  | 0            | —    | —   | ns    |  |  |

| 20*         | TioR       | Port output rise time                                      | _            | 10   | 40  | ns    |  |  |

|             |            |                                                            |              | —    | 80  | ns    |  |  |

| 21*         | TioF       | Port output fall time                                      |              | 10   | 40  | ns    |  |  |

|             |            |                                                            |              | —    | 80  | ns    |  |  |

| 22*         | Tinp       | RB0/INT pin high or low time                               | 25           | _    | _   | ns    |  |  |

|             |            |                                                            | 40           | —    |     | ns    |  |  |

| 23*         | Trbp       | RB<7:4> change interrupt high or low time                  | Тсу          | _    | _   | ns    |  |  |

| * These     | parameters | are characterized but not tested.                          | •            |      |     |       |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

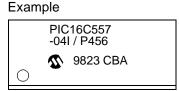

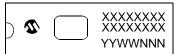

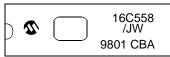

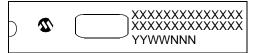

## Package Marking Information (Cont'd)

#### Example PIC16C558 -04I / S0218 S0218 9818 CDK

$\cap$

##

## 18-Lead CERDIP Windowed

#### Example

## 28-Lead CERDIP Windowed

Example

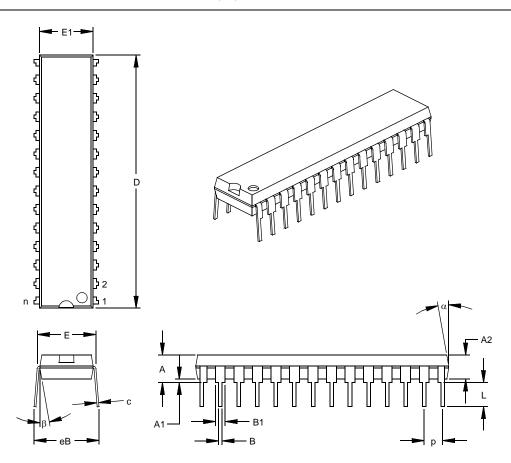

# 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| ision L                   | n  | MIN                                                                                                              | NOM                                                    | MAX                                                     | MIN                                                    | NOM                                                    | MAX                                                     |

|---------------------------|----|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|

|                           |    |                                                                                                                  |                                                        |                                                         |                                                        |                                                        | IVIAA                                                   |

|                           | -  |                                                                                                                  | 28                                                     |                                                         |                                                        | 28                                                     |                                                         |

|                           | р  |                                                                                                                  | .100                                                   |                                                         |                                                        | 2.54                                                   |                                                         |

|                           | Α  | .140                                                                                                             | .150                                                   | .160                                                    | 3.56                                                   | 3.81                                                   | 4.06                                                    |

|                           | A2 | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|                           | A1 | .015                                                                                                             |                                                        |                                                         | 0.38                                                   |                                                        |                                                         |

|                           | Е  | .300                                                                                                             | .310                                                   | .325                                                    | 7.62                                                   | 7.87                                                   | 8.26                                                    |

|                           | E1 | .275                                                                                                             | .285                                                   | .295                                                    | 6.99                                                   | 7.24                                                   | 7.49                                                    |

|                           | D  | 1.345                                                                                                            | 1.365                                                  | 1.385                                                   | 34.16                                                  | 34.67                                                  | 35.18                                                   |

|                           | L  | .125                                                                                                             | .130                                                   | .135                                                    | 3.18                                                   | 3.30                                                   | 3.43                                                    |

|                           | С  | .008                                                                                                             | .012                                                   | .015                                                    | 0.20                                                   | 0.29                                                   | 0.38                                                    |

|                           | B1 | .040                                                                                                             | .053                                                   | .065                                                    | 1.02                                                   | 1.33                                                   | 1.65                                                    |

|                           | В  | .016                                                                                                             | .019                                                   | .022                                                    | 0.41                                                   | 0.48                                                   | 0.56                                                    |

| §                         | eB | .320                                                                                                             | .350                                                   | .430                                                    | 8.13                                                   | 8.89                                                   | 10.92                                                   |

|                           | α  | 5                                                                                                                | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

| Mold Draft Angle Bottom β |    |                                                                                                                  | 10                                                     | 15                                                      | 5                                                      | 10                                                     | 15                                                      |

|                           | Ş  | A           A2           A1           E           D           L           C           B1           §           α | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $ |

\* Controlling Parameter § Significant Characteristic

Notes:

Dimension D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MO-095

Drawing No. C04-070

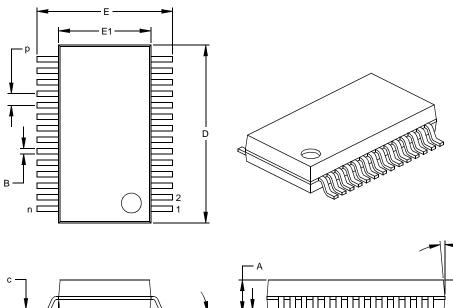

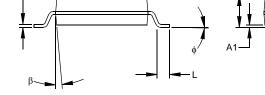

### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      | INCHES |      |      | MILLIMETERS* |        |        |

|--------------------------|------------|--------|------|------|--------------|--------|--------|

| Dimens                   | ion Limits | MIN    | NOM  | MAX  | MIN          | NOM    | MAX    |

| Number of Pins           | n          |        | 28   |      |              | 28     |        |

| Pitch                    | р          |        | .026 |      |              | 0.65   |        |

| Overall Height           | А          | .068   | .073 | .078 | 1.73         | 1.85   | 1.98   |

| Molded Package Thickness | A2         | .064   | .068 | .072 | 1.63         | 1.73   | 1.83   |

| Standoff §               | A1         | .002   | .006 | .010 | 0.05         | 0.15   | 0.25   |

| Overall Width            | E          | .299   | .309 | .319 | 7.59         | 7.85   | 8.10   |

| Molded Package Width     | E1         | .201   | .207 | .212 | 5.11         | 5.25   | 5.38   |

| Overall Length           | D          | .396   | .402 | .407 | 10.06        | 10.20  | 10.34  |

| Foot Length              | L          | .022   | .030 | .037 | 0.56         | 0.75   | 0.94   |

| Lead Thickness           | С          | .004   | .007 | .010 | 0.10         | 0.18   | 0.25   |

| Foot Angle               | φ          | 0      | 4    | 8    | 0.00         | 101.60 | 203.20 |

| Lead Width               | В          | .010   | .013 | .015 | 0.25         | 0.32   | 0.38   |

| Mold Draft Angle Top     | α          | 0      | 5    | 10   | 0            | 5      | 10     |

| Mold Draft Angle Bottom  | β          | 0      | 5    | 10   | 0            | 5      | 10     |

**Controlling Parameter** § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

A2

## APPENDIX A: ENHANCEMENTS

The following are the list of enhancements over the PIC16C5X microcontroller family:

- Instruction word length is increased to 14 bits. This allows larger page sizes both in program memory (4K now as opposed to 512 before) and register file (up to 128 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. PA2, PA1, PA0 bits are removed from STATUS register.

- 3. Data memory paging is slightly redefined. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW.

Two instructions TRIS and OPTION are being phased out although they are kept for compatibility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. RESET vector is changed to 0000h.

- RESET of all registers is revised. Three different RESET (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake-up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt-onchange feature.

- 13. Timer0 clock input, T0CKI pin is also a port pin (RA4/T0CKI) and has a TRIS bit.

- 14. FSR is made a full 8-bit register.

- 15. "In-circuit programming" is made possible. The user can program PIC16C55X devices using only five pins: VDD, VSS, VPP, RB6 (clock) and RB7 (data in/out).

- 16. PCON status register is added with a Power-on Reset (POR) status bit.

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- 18. PORTA inputs are now Schmitt Trigger inputs.

## APPENDIX B: COMPATIBILITY