Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc558t-04e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

|                                          | _   |

|------------------------------------------|-----|

| .0 General Description                   | . 5 |

| .0 PIC16C55X Device Varieties            | . 7 |

| .0       General Description             | . 9 |

| .0 Memory Organization                   | 13  |

|                                          |     |

| 0.0 Special Features of the CPU          | 31  |

| .0 Timer0 Module                         |     |

| 0 Instruction Set Summary                | 53  |

| .0 Development Support                   | 67  |

| 0.0 Electrical Specifications            | 73  |

| 1.0 Packaging Information                | 87  |

| vppendix A: Enhancements                 | 97  |

| ppendix B: Compatibility                 | 97  |

| ndex                                     | 99  |

| Dn-Line Support 1                        | 01  |

| Systems Information and Upgrade Hot Line | 01  |

| Dn-Line Support                          | 02  |

| Product Identification System            | 03  |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

• Your local Microchip sales office (see last page)

• The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16C55X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16C55X uses a Harvard architecture in which program and data are accessed from separate memories using separate busses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently from 8-bit wide data words. Instruction opcodes are 14-bit wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a singlecycle (200 ns @ 20 MHz) except for program branches. The table below lists the memory (EPROM and RAM).

| Device    | Program<br>Memory<br>(EPROM) | Data<br>Memor<br>(RAM) |  |

|-----------|------------------------------|------------------------|--|

| PIC16C554 | 512                          | 80                     |  |

| PIC16C557 | 2 K                          | 128                    |  |

| PIC16C558 | 2 K                          | 128                    |  |

The PIC16C554 addresses 512 x 14 on-chip program memory. The PIC16C557 and PIC16C558 addresses 2 K x 14 program memory. All program memory is internal.

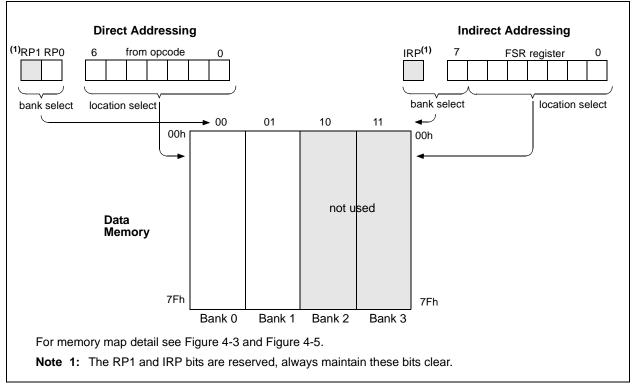

The PIC16C55X can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped into the data memory. The PIC16C55X has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any Addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16C55X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16C55X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

#### 4.2.2.4 PCON Register

The PCON register contains a flag bit to differentiate between a Power-on Reset, an external MCLR Reset or WDT Reset. See Section 6.3 and Section 6.4 for detailed RESET operation.

#### **REGISTER 4-4:** PCON REGISTER (ADDRESS 8Eh) U-0 U-0 U-0 R/W-0 U-0 U-0 U-0 U-0 POR bit7 bit 7-2 Unimplemented: Read as '0' bit 1 POR: Power-on Reset status bit 1 = No Power-on Reset occurred 0 = Power-on Reset occurred bit 0 Unimplemented: Read as '0' Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit0

# 5.0 I/O PORTS

The PIC16C554 and PIC16C558 have two ports, PORTA and PORTB. The PIC16C557 has three ports, PORTA, PORTB and PORTC.

### 5.1 PORTA and TRISA Registers

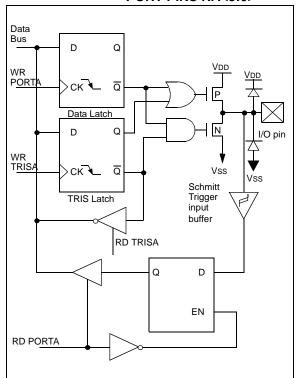

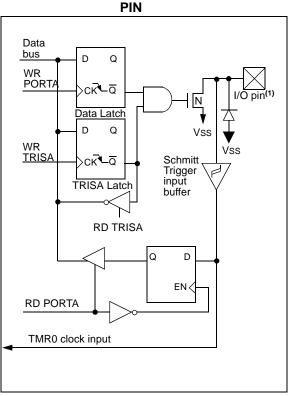

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open-drain output. Port RA4 is multiplexed with the T0CKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a Hi-impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

**Note 1:** On RESET, the TRISA register is set to all inputs.

FIGURE 5-1: BLOCK DIAGRAM OF PORT PINS RA<3:0>

#### FIGURE 5-2: BL

BLOCK DIAGRAM OF RA4

#### 6.4.5 POWER CONTROL/STATUS REGISTER (PCON)

Bit1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent RESET if POR is '0', it will indicate that a Poweron Reset must have occurred (VDD may have gone too low).

### TABLE 6-3: TIMEOUT IN VARIOUS SITUATIONS

| Oscillator    | Powe              | Wake-up from |           |

|---------------|-------------------|--------------|-----------|

| Configuration | PWRTE = 0         | PWRTE = 1    | SLEEP     |

| XT, HS, LP    | 72 ms + 1024 Tosc | 1024 Tosc    | 1024 Tosc |

| RC            | 72 ms             | _            | —         |

#### TABLE 6-4: STATUS BITS AND THEIR SIGNIFICANCE

| POR | то | PD |                                    |

|-----|----|----|------------------------------------|

| 0   | 1  | 1  | Power-on Reset                     |

| 0   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0  | u  | WDT Reset                          |

| 1   | 0  | 0  | WDT Wake-up                        |

| 1   | u  | u  | MCLR Reset during normal operation |

| 1   | 1  | 0  | MCLR Reset during SLEEP            |

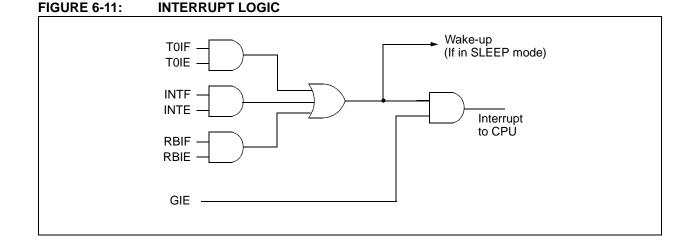

#### 6.5 Interrupts

The PIC16C55X has 3 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PORTB change interrupts (pins RB7:RB4)

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on RESET.

The "Return from Interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts. For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 6-12). The latency is the same for one or two cycle instructions. Once in the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note 1: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

© 1996-2013 Microchip Technology Inc.

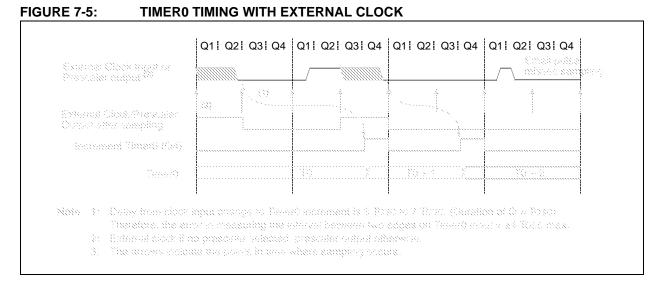

#### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### 7.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

Note: There is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa. The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

© 1996-2013 Microchip Technology Inc.

# PIC16C55X

| CLRW             | Clear W                                                               | V |  |  |  |

|------------------|-----------------------------------------------------------------------|---|--|--|--|

| Syntax:          | [label] CLRW                                                          |   |  |  |  |

| Operands:        | None                                                                  |   |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |   |  |  |  |

| Status Affected: | Z                                                                     |   |  |  |  |

| Encoding:        | 00 0001 0000 0011                                                     |   |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |   |  |  |  |

| Words:           | 1                                                                     |   |  |  |  |

| Cycles:          | 1                                                                     |   |  |  |  |

| Example          | CLRW                                                                  |   |  |  |  |

|                  | Before Instruction                                                    |   |  |  |  |

|                  | W = 0x5A                                                              |   |  |  |  |

|                  | After Instruction                                                     |   |  |  |  |

|                  | W = 0x00                                                              |   |  |  |  |

|                  | Z = 1                                                                 |   |  |  |  |

| COMF             | Complement f                                                                                                                                          |      |      |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|

| Syntax:          | [label] COMF f,d                                                                                                                                      |      |      |      |  |

| Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                              |      |      |      |  |

| Operation:       | $(\overline{f}) \rightarrow (des$                                                                                                                     | st)  |      |      |  |

| Status Affected: | Z                                                                                                                                                     |      |      |      |  |

| Encoding:        | 00                                                                                                                                                    | 1001 | dfff | ffff |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0 the result is<br>stored in W. If 'd' is 1 the result is<br>stored back in register 'f'. |      |      |      |  |

| Words:           | 1                                                                                                                                                     |      |      |      |  |

| Cycles:          | 1                                                                                                                                                     |      |      |      |  |

| Example          | COMF REG1,0                                                                                                                                           |      |      |      |  |

|                  | Before Instruction                                                                                                                                    |      |      |      |  |

|                  | REG1 = 0x13                                                                                                                                           |      |      |      |  |

|                  | After Instruction                                                                                                                                     |      |      |      |  |

|                  | REG1 = 0x13                                                                                                                                           |      |      |      |  |

|                  | W = 0xEC                                                                                                                                              |      |      |      |  |

| Clear Watchdog Timer                                                                                                              |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| [label] CLRWDT                                                                                                                    |  |  |  |  |

| None                                                                                                                              |  |  |  |  |

| $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow PD$            |  |  |  |  |

| TO, PD                                                                                                                            |  |  |  |  |

| 00 0000 0110 0100                                                                                                                 |  |  |  |  |

| CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT. Status bits TO<br>and PD are set.    |  |  |  |  |

| 1                                                                                                                                 |  |  |  |  |

| 1                                                                                                                                 |  |  |  |  |

| CLRWDT                                                                                                                            |  |  |  |  |

| Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = $1$<br>PD = $1$ |  |  |  |  |

|                                                                                                                                   |  |  |  |  |

.....

| DECF             | Decrement f                                                                                                                                 |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECF f,d                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                           |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest)                                                                                                                |  |  |  |  |

| Status Affected: | Z                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 0011 dfff ffff                                                                                                                           |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                           |  |  |  |  |

| Example          | DECF CNT, 1                                                                                                                                 |  |  |  |  |

|                  | Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                       |  |  |  |  |

|                  |                                                                                                                                             |  |  |  |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in$ [0,1]                                                                                                                                                                                                                                                                      |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0 the result is placed in the W register. If 'd' is 1 the result is placed back in register 'f'. If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                      |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT - 1<br>if CNT = 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE+1                                                                                                                                        |  |  |  |  |

| GOTO                                                                                | Unconditional Branch                                                                                                                                                                                                                                                       |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                                             | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                                    |  |  |  |  |

| Operands:                                                                           | $0 \le k \le 2047$                                                                                                                                                                                                                                                         |  |  |  |  |

| Operation:                                                                          | $k \rightarrow PC < 10:0 >$                                                                                                                                                                                                                                                |  |  |  |  |

|                                                                                     | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                                                                                        |  |  |  |  |

| Status Affected:                                                                    | None                                                                                                                                                                                                                                                                       |  |  |  |  |

| Encoding:                                                                           | 10 lkkk kkkk kkkk                                                                                                                                                                                                                                                          |  |  |  |  |

| Description:                                                                        | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.                                                                              |  |  |  |  |

| Words:                                                                              | 1                                                                                                                                                                                                                                                                          |  |  |  |  |

| Cycles:                                                                             | 2                                                                                                                                                                                                                                                                          |  |  |  |  |

| Example                                                                             | GOTO THERE                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                                                                     | After Instruction                                                                                                                                                                                                                                                          |  |  |  |  |

| INCF                                                                                | PC = Address THERE                                                                                                                                                                                                                                                         |  |  |  |  |

| _                                                                                   | Increment f                                                                                                                                                                                                                                                                |  |  |  |  |

| INCF<br>Syntax:<br>Operands:                                                        |                                                                                                                                                                                                                                                                            |  |  |  |  |

| Syntax:                                                                             | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$                                                                                                                                                                                                              |  |  |  |  |

| Syntax:<br>Operands:                                                                | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                             |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:                                                  | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest)                                                                                                                                                             |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:                              | Increment f<br>[ <i>label</i> ] INCF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest)<br>Z                                                                                                                                                        |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:                 | Increment f[ label ] INCF f,d $0 \le f \le 127$ $d \in [0,1]$ (f) + 1 $\rightarrow$ (dest)Z001010dffffffThe contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the                                            |  |  |  |  |

| Syntax:<br>Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description: | Increment f[ label ]INCF f,d $0 \le f \le 127$ $d \in [0,1]$ $(f) + 1 \rightarrow (dest)$ Z001010dfffffffThe contents of register 'f' are<br>incremented. If 'd' is 0 the result is<br>placed in the W register. If 'd' is 1 the<br>result is placed back in register 'f'. |  |  |  |  |

INCF CNT, 1 Before Instruction CNT = 0xFFZ = 0After Instruction CNT = 0x00Z = 1

| XORLW            | Exclusive OR Literal with W          |                        |               |         |

|------------------|--------------------------------------|------------------------|---------------|---------|

| Syntax:          | [ <i>label</i> ] XORLW k             |                        |               |         |

| Operands:        | $0 \le k \le 255$                    |                        |               |         |

| Operation:       | (W) .XOF                             | R. $k \rightarrow (N)$ | N)            |         |

| Status Affected: | Z                                    |                        |               |         |

| Encoding:        | 11                                   | 1010                   | kkkk          | kkkk    |

| Description:     | The conter<br>XOR'ed with the result | ith the eig            | ght bit liter | al 'k'. |

| Words:           | 1                                    |                        |               |         |

| Cycles:          | 1                                    |                        |               |         |

| Example:         | XORLW                                | 0xAF                   |               |         |

|                  | Before In                            | structior              | ı             |         |

|                  | W                                    | =                      | 0xB5          |         |

|                  | After Instruction                    |                        |               |         |

|                  | W                                    | =                      | 0x1A          |         |

| XORWF            | Exclusive OR W with f                                                                                                                                                                 |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in \left[0,1\right] \end{array}$                                                                                                                |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                     |  |  |  |  |

| Encoding:        | 00 0110 dfff ffff                                                                                                                                                                     |  |  |  |  |

| Description:     | Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                     |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                     |  |  |  |  |

| Example          | XORWF REG 1                                                                                                                                                                           |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                    |  |  |  |  |

|                  | REG = 0xAF                                                                                                                                                                            |  |  |  |  |

|                  | W = 0xB5                                                                                                                                                                              |  |  |  |  |

|                  | After Instruction                                                                                                                                                                     |  |  |  |  |

|                  | REG = 0x1A                                                                                                                                                                            |  |  |  |  |

|                  | W = 0xB5                                                                                                                                                                              |  |  |  |  |

© 1996-2013 Microchip Technology Inc.

### 9.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PIC MCUs and can be used to develop for this and other PIC microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>TM</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time.

#### 9.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in Stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In Stand-alone mode, the PRO MATE II device programmer can read, verify, or program PIC devices. It can also set code protection in this mode.

### 9.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PIC devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

#### 9.11 PICDEM 1 Low Cost PIC MCU Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A). PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

### 9.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the  $I^2C^{TM}$  bus and separate headers for connection to an LCD module and a keypad.

### 10.1 DC Characteristics: PIC16C55X-04 (Commercial, Industrial, Extended) PIC16C55X-20 (Commercial, Industrial, Extended) HCS1365-04 (Commercial, Industrial, Extended)

|              |                |                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |            |          |                                               |

|--------------|----------------|-----------------------------------|------------------------------------------------------|-----|------------|----------|-----------------------------------------------|

| Param<br>No. | Sym            | Characteristic                    | Min Typ† Max Units Conditions                        |     | Conditions |          |                                               |

| D020         | IPD            | Power-Down Current <sup>(3)</sup> |                                                      |     |            |          |                                               |

|              |                | 16LC55X                           | _                                                    | 0.7 | 2          | μΑ       | VDD = 3.0V, WDT disabled                      |

|              |                | 16C55X                            | —                                                    | 1.0 | 2.5<br>15  | μΑ<br>μΑ | VDD = 4.0V, WDT disabled<br>(+85°C to +125°C) |

|              | $\Delta I$ WDT | WDT Current <sup>(5)</sup>        |                                                      |     |            |          |                                               |

|              |                | 16LC55X                           | _                                                    | 6.0 | 15         | μΑ       | VDD = 3.0V                                    |

|              |                | 16C55X                            | _                                                    | 6.0 | 20         | μA       | VDD = 4.0V<br>(+85°C to +125°C)               |

\* These parameters are characterized but not tested.

**†** Data is "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active Operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins configured as input, pulled to VDD,

- $\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as input and tied to VDD or VSS.

- 4: For RC osc configuration, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

NOTES:

### Package Marking Information (Cont'd)

#### Example PIC16C558 -04I / S0218 S0218 9818 CDK

$\cap$

####

#### 18-Lead CERDIP Windowed

#### Example

#### 28-Lead CERDIP Windowed

Example

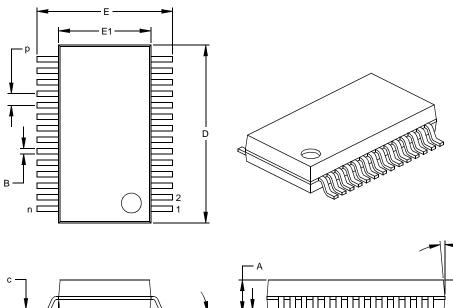

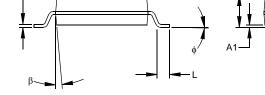

#### 28-Lead Plastic Shrink Small Outline (SS) - 209 mil, 5.30 mm (SSOP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units      | INCHES |      | MILLIMETERS* |       |        |        |

|--------------------------|------------|--------|------|--------------|-------|--------|--------|

| Dimens                   | ion Limits | MIN    | NOM  | MAX          | MIN   | NOM    | MAX    |

| Number of Pins           | n          |        | 28   |              |       | 28     |        |

| Pitch                    | р          |        | .026 |              |       | 0.65   |        |

| Overall Height           | Α          | .068   | .073 | .078         | 1.73  | 1.85   | 1.98   |

| Molded Package Thickness | A2         | .064   | .068 | .072         | 1.63  | 1.73   | 1.83   |

| Standoff §               | A1         | .002   | .006 | .010         | 0.05  | 0.15   | 0.25   |

| Overall Width            | Е          | .299   | .309 | .319         | 7.59  | 7.85   | 8.10   |

| Molded Package Width     | E1         | .201   | .207 | .212         | 5.11  | 5.25   | 5.38   |

| Overall Length           | D          | .396   | .402 | .407         | 10.06 | 10.20  | 10.34  |

| Foot Length              | L          | .022   | .030 | .037         | 0.56  | 0.75   | 0.94   |

| Lead Thickness           | С          | .004   | .007 | .010         | 0.10  | 0.18   | 0.25   |

| Foot Angle               | φ          | 0      | 4    | 8            | 0.00  | 101.60 | 203.20 |

| Lead Width               | В          | .010   | .013 | .015         | 0.25  | 0.32   | 0.38   |

| Mold Draft Angle Top     | α          | 0      | 5    | 10           | 0     | 5      | 10     |

| Mold Draft Angle Bottom  | β          | 0      | 5    | 10           | 0     | 5      | 10     |

**Controlling Parameter** § Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-150

Drawing No. C04-073

A2

NOTES:

# PIC16C55X

| PICSTART Plus Entry Level Development Programmer 69 |

|-----------------------------------------------------|

| Port RB Interrupt                                   |

| PORTA                                               |

| PORTB                                               |

| Power Control/Status Register (PCON)                |

| Power-Down Mode (SLEEP)45                           |

| Power-On Reset (POR)                                |

| Power-up Timer (PWRT)                               |

| Prescaler                                           |

| PRO MATE II Universal Device Programmer             |

| Program Memory Organization                         |

# Q

# R

| RC Oscillator      |    |

|--------------------|----|

| Reset              |    |

| RETFIE Instruction | 62 |

| RETLW Instruction  | 62 |

| RETURN Instruction | 62 |

| RLF Instruction    | 62 |

| RRF Instruction    | 63 |

# S

| Serialized Quick-Turnaround-Production (SQTP) Devices | 7    |

|-------------------------------------------------------|------|

| SLEEP Instruction                                     | . 63 |

| Software Simulator (MPLAB SIM)                        | . 68 |

| Special Features of the CPU                           | . 31 |

| Special Function Registers                            | . 15 |

| Stack                                                 | . 21 |

| Status Register                                       | . 17 |

| SUBLW Instruction                                     | . 63 |

| SUBWF Instruction                                     | . 64 |

| SWAPF Instruction                                     | . 64 |

# т

| Timer0                             |        |

|------------------------------------|--------|

| TIMER0                             | 47     |

| TIMER0 (TMR0) Interrupt            | 47     |

| TIMER0 (TMR0) Module               |        |

| TMR0 with External Clock           |        |

| Timer1                             |        |

| Switching Prescaler Assignment     | 51     |

| Timing Diagrams and Specifications | 81     |

| TMR0 Interrupt                     |        |

| TRIS Instruction                   | 64     |

| TRISA                              | 23     |

| TRISB                              | 25, 27 |

| W                                  |        |

| Watchdog Timer (WDT)               | 43     |

| WWW, On-Line Support               |        |

| x                                  |        |

| XORLW Instruction                  | 65     |

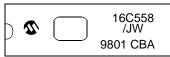

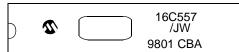

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | x <u>/xx xxx</u>                                                                                                              | Examples:                                                                                                                                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device            | Temperature Package Pattern<br>Range                                                                                          | a) PIC17C756–16L Commercial Temp.,<br>PLCC package, 16 MHz,<br>normal VDD limits                                                                         |

| Device            | PIC17C756: Standard VDD range<br>PIC17C756T: (Tape and Reel)<br>PIC17LC756: Extended VDD range                                | <ul> <li>b) PIC17LC756–08/PT Commercial Temp.,<br/>TQFP package, 8MHz,<br/>extended VDD limits</li> <li>c) PIC17C756–33I/PT Industrial Temp.,</li> </ul> |

| Temperature Range | $\begin{array}{rcl} - & = & 0^{\circ}C \text{ to } +70^{\circ}C \\ I & = & -40^{\circ}C \text{ to } +85^{\circ}C \end{array}$ | TQFP package, 33 MHz,<br>normal VDD limits                                                                                                               |

| Package           | CL = Windowed LCC<br>PT = TQFP<br>L = PLCC                                                                                    |                                                                                                                                                          |

| Pattern           | QTP, SQTP, ROM Code (factory specified) or<br>Special Requirements. Blank for OTP and<br>Windowed devices.                    |                                                                                                                                                          |

|                   |                                                                                                                               |                                                                                                                                                          |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)

NOTES: