Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | M8C                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 24MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 8KB (8K x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                 |

| Data Converters            | A/D 1x8b, 1x11b, 1x12b; D/A 1x9b                                           |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c26233-24pvi |

|                            |                                                                            |

## 1.0 Functional Overview

The CPU heart of this next generation family of microcontrollers is a high performance, 8-bit, M8C Harvard architecture microprocessor. Separate program and memory busses allow for faster overall throughput. Processor clock speeds to 24 MHz are available. The processor may also be run at lower clock speeds for powersensitive applications. A rich instruction set allows for efficient low-level language support.

All devices in this family include both analog and digital configurable peripherals (PSoC blocks). These blocks enable the user to define unique functions during configuration of the device. Included are twelve analog PSoC blocks and eight digital PSoC blocks. Potential applications for the digital PSoC blocks are timers, counters, UARTs, CRC generators, PWMs, and other functions. The analog PSoC blocks can be used for SAR ADCs, Multi-slope ADCs, programmable gain amplifiers, programmable filters, DACs, and other functions. Higher order User Modules such as modems, complex motor controllers, and complete sensor signal chains can be created from these building blocks. This allows for an unprecedented level of flexibility and integration in microcontroller-based systems.

A Multiplier/Accumulator (MAC) is available on all devices in this family. The MAC is implemented on this device as a peripheral that is mapped into the register space. When an instruction writes to the MAC input registers, the result of an 8x8 multiply and a 32-bit accumulate are available to be read from the output registers on the next instruction cycle.

The number of general purpose I/Os available in this family of parts range from 6 to 44. Each of these I/O pins has a variety of programmable options. In the output

mode, the user can select the drive strength desired. Any pin can serve as an interrupt source, and can be selected to trigger on positive edges, negative edges, or any change. Digital signal sources can be routed directly from a pin to the digital PSoC blocks. Some pins have additional capability to route analog signals to the analog PSoC blocks.

Multiple oscillator options are available for use in clocking the CPU, analog PSoC blocks and digital PSoC blocks. These options include an internal main oscillator running at 48/24 MHz, an external crystal oscillator for use with a 32.768 kHz watch crystal, and an internal low-speed oscillator for use in clocking the PSoC blocks and the Watchdog/Sleep timer. User selectable clock divisors allow for optimizing code execution speed and power trade-offs.

The different device types in this family provide various amounts of code and data memory. The code space ranges in size from 4K to 16K bytes of user programmable Flash memory. This memory can be programmed serially in either a programming Pod or on the user board. The endurance on the Flash memory is 50,000 erase/write cycles. The data space is 256 bytes of user SRAM.

A powerful and flexible protection model secures the user's sensitive information. This model allows the user to selectively lock blocks of memory for read and write protection. This allows partial code updates without exposing proprietary information.

Devices in this family range from 8 pins through 48 pins in PDIP, SOIC and SSOP packages.

# 1.1 Key Features

Table 1: Device Family Key Features

|                           | CY8C25122       | CY8C26233       | CY8C26443       | CY8C26643       |

|---------------------------|-----------------|-----------------|-----------------|-----------------|

| Operating Frequency       | 93.7kHz - 24MHz | 93.7kHz - 24MHz | 93.7kHz - 24MHz | 93.7kHz - 24MHz |

| Operating Voltage         | 3.0 - 5.25V     | 3.0 - 5.25V     | 3.0 - 5.25V     | 3.0 - 5.25V     |

| Program Memory (KBytes)   | 4               | 8               | 16              | 16              |

| Data Memory (Bytes)       | 256             | 256             | 256             | 256             |

| Digital PSoC Blocks       | 8               | 8               | 8               | 8               |

| Analog PSoC Blocks        | 12              | 12              | 12              | 12              |

| I/O Pins                  | 6               | 16              | 24              | 40/44           |

| External Switch Mode Pump | No              | Yes             | Yes             | Yes             |

| Available Packages        | 8 PDIP          | 20 PDIP         | 28 PDIP         | 48 PDIP         |

|                           |                 | 20 SOIC         | 28 SOIC         | 48 SSOP         |

|                           |                 | 20 SSOP         | 28 SSOP         | 44 TQFP         |

# 2.4 Instruction Set Summary

Table 23: Instruction Set Summary (Sorted by Mnemonic)

| Opcode Hex | Cycles | Bytes | Instruction Format        | Flags                                                                                                                                               | Opcode Hex | Cycles | Bytes | Instruction Format   | Flags | Opcode Hex | Cycles | Bytes | Instruction Format    | Flags |

|------------|--------|-------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|-------|----------------------|-------|------------|--------|-------|-----------------------|-------|

|            |        |       |                           |                                                                                                                                                     |            |        |       |                      |       |            |        |       |                       |       |

| 09         | 4      |       | ADC A, expr               | C, Z                                                                                                                                                | 76         | 7      | 2     |                      | C, Z  | 20         | 5      | 1     |                       |       |

| 0A         | 6      |       | ADC A, [expr]             | C, Z                                                                                                                                                | 77         | 8      | 2     |                      | C, Z  | 18         | 5      | 1     |                       | Z     |

| 0B         | 7      | 2     | ADC A, [X+expr]           | C, Z                                                                                                                                                | Fx         | 13     | 2     |                      | Z     | 10         | 4      | 1     |                       |       |

| 00         | 7      |       | ADC [expr], A             | C, Z                                                                                                                                                | Ex         | 7      | 2     |                      |       | 08         | 4      | 1     |                       |       |

| 0D         | 8      | 2     |                           | C, Z                                                                                                                                                | Сх         | 5      | 2     | JC                   |       | 7E         | 10     | 1     |                       | C, Z  |

| 0E         | 9      |       | ADC [expr], expr          | C, Z                                                                                                                                                | 8x         | 5      | 2     | JMP                  |       | 7F         | 8      | 1     |                       |       |

| 0F         | 10     |       | ADC [X+expr], expr        | C, Z                                                                                                                                                | Dx         | 5      | 2     | JNC                  |       | 6A         | 4      | 1     |                       | C, Z  |

| 01         | 4      |       | ADD A, expr               | C, Z                                                                                                                                                | Вх         | 5      | 2     | JNZ                  |       | 6B         | 7      | 2     |                       | C, Z  |

| 02         | 6      |       | ADD A, [expr]             | C, Z                                                                                                                                                | Ax         | 5      | 2     | JZ                   |       | 6C         | 8      | 2     |                       | C, Z  |

| 03         | 7      |       | ADD A, [X+expr]           | C, Z                                                                                                                                                | 7C         | 13     | 3     | LCALL                |       | 28         | 11     | 1     |                       | Z     |

| 04         | 7      | 2     | ADD [expr], A             | C, Z                                                                                                                                                | 7D         | 7      | 3     | LJMP                 |       | 6D         | 4      | 1     | RRC A                 | C, Z  |

| 05         | 8      |       | ADD [X+expr], A           | C, Z                                                                                                                                                | 4F         | 4      | 1     | MOV X, SP            | _     | 6E         | 7      | 2     |                       | C, Z  |

| 06         | 9      |       | ADD [expr], expr          | C, Z                                                                                                                                                | 50         | 4      | 2     | MOV A, expr          | Z     | 6F         | 8      | 2     |                       | C, Z  |

| 07         | 10     |       | ADD [X+expr], expr        | C, Z                                                                                                                                                | 51         | 5      | 2     | MOV A, [expr]        | Z     | 19         | 4      | 2     |                       | C, Z  |

| 38         | 5      | 2     |                           | _                                                                                                                                                   | 52         | 6      | 2     | MOV A, [X+expr]      | Z     | 1A         | 6      | 2     |                       | C, Z  |

| 21         | 4      |       | AND A, expr               | Z                                                                                                                                                   | 53         | 5      | 2     | MOV [expr], A        |       | 1B         | 7      | 2     |                       | C, Z  |

| 22         | 6      | 2     |                           | Z                                                                                                                                                   | 54         | 6      | 2     | MOV [X+expr], A      |       | 1C         | 7      | 2     |                       | C, Z  |

| 23         | 7      |       | AND A, [X+expr]           | Z                                                                                                                                                   | 55         | 8      | 3     | MOV [expr], expr     |       | 1D         | 8      | 2     |                       | C, Z  |

| 24         | 7      |       | AND [expr], A             | Z                                                                                                                                                   | 56         | 9      | 3     |                      |       | 1E         | 9      | 3     |                       | C, Z  |

| 25         | 8      |       | AND [X+expr], A           | Z                                                                                                                                                   | 57         | 4      | 2     | MOV X, expr          |       | 1F         | 10     | 3     |                       | C, Z  |

| 26         | 9      |       | AND [expr], expr          | Z                                                                                                                                                   | 58         | 6      | 2     |                      |       | 00         | 15     | 1     | SSC                   |       |

| 27         | 10     |       | AND [X+expr], expr        | Z                                                                                                                                                   | 59         | 7      | 2     |                      |       | 11         | 4      | 2     |                       | C, Z  |

| 70         | 4      |       | AND F, expr               | C, Z                                                                                                                                                | 5A         | 5      | 2     |                      |       | 12         | 6      | 2     |                       | C, Z  |

| 41         | 9      |       | AND reg[expr], expr       | Z                                                                                                                                                   | 5B         | 4      | 1     | MOV A, X             | Z     | 13         | 7      | 2     |                       | C, Z  |

| 42         | 10     | 3     | 5                         | Z                                                                                                                                                   | 5C         | 4      | 1     | MOV X, A             |       | 14         | 7      | 2     |                       | C, Z  |

| 64         | 4      | 1     |                           | C, Z                                                                                                                                                | 5D         | 6      | 2     | MOV A, reg[expr]     | Z     | 15         | 8      | 2     |                       | C, Z  |

| 65         | 7      | 2     |                           | C, Z                                                                                                                                                | 5E         | 7      | 2     | MOV A, reg[X+expr]   | Z     | 16         | 9      | 3     |                       | C, Z  |

| 66         | 8      | 2     |                           | C, Z                                                                                                                                                | 5F         | 10     | 3     | MOV [expr], [expr]   |       | 17         | 10     | 3     |                       | C, Z  |

| 67         | 4      | 1     |                           | C, Z                                                                                                                                                | 60         | 5      | 2     | MOV reg[expr], A     |       | 4B         | 5      | 1     |                       | Z     |

| 68         | 7      | 2     |                           | C, Z                                                                                                                                                | 61         | 6      | 2     | MOV reg[X+expr], A   |       | 4C         | 7      | 2     |                       | Z     |

| 69         | 8      | 2     |                           | C, Z                                                                                                                                                | 62         | 8      | 3     | MOV reg[expr], expr  |       | 4D         | 7      | 2     |                       |       |

| 9x         | 11     | 2     |                           |                                                                                                                                                     | 63         | 9      | 3     |                      |       | 4E         | 5      | 1     |                       | Z     |

| 39         | 5      | 2     |                           | if (A=B) Z=1                                                                                                                                        | 3E         | 10     | 2     |                      | Z     | 47         | 8      | 3     |                       | Z     |

| 3A         | 7      | 2     |                           | if (A <b) c="1&lt;/td"><td>3F</td><td>10</td><td>2</td><td>MVI [ [expr]++ ], A</td><td></td><td>48</td><td>9</td><td>3</td><td></td><td>Z</td></b)> | 3F         | 10     | 2     | MVI [ [expr]++ ], A  |       | 48         | 9      | 3     |                       | Z     |

| 3B         | 8      | 2     |                           |                                                                                                                                                     | 40         | 4      | 1     | NOP                  |       | 49         | 9      | 3     |                       | Z     |

| 3C         | 8      | 3     |                           |                                                                                                                                                     | 29         | 4      | 2     | OR A, expr           | Z     | 4A         | 10     | 3     |                       | Z     |

| 3D         | 9      | 3     |                           |                                                                                                                                                     | 2A         | 6      | 2     | OR A, [expr]         | Z     | 72         | 4      | 2     |                       | C, Z  |

| 73         | 4      | 1     | CPL A                     | Z                                                                                                                                                   | 2B         | 7      | 2     | OR A, [X+expr]       | Z     | 31         | 4      | 2     | ' '                   | Z     |

| 78         | 4      | 1     |                           | C, Z                                                                                                                                                | 2C         | 7      | 2     | OR [expr], A         | Z     | 32         | 6      | 2     |                       | Z     |

| 79         | 4      | 1     | DEC X                     | C, Z                                                                                                                                                | 2D         | 8      | 2     | OR [X+expr], A       | Z     | 33         | 7      | 2     |                       | Z     |

| 7A         | 7      | 2     |                           | C, Z                                                                                                                                                | 2E         | 9      | 3     | OR [expr], expr      | Z     | 34         | 7      |       | XOR [expr], A         | Z     |

| 7B         | 8      | 2     |                           | C, Z                                                                                                                                                | 2F         | 10     | 3     | OR [X+expr], expr    | Z     | 35         | 8      | 2     |                       | Z     |

| 30         | 9      | 1     | HALT                      |                                                                                                                                                     | 43         | 9      | 3     | OR reg[expr], expr   | Z     | 36         | 9      | 3     |                       | Z     |

| 74         | 4      | 1     | INC A                     | C, Z                                                                                                                                                | 44         | 10     | 3     | OR reg[X+expr], expr | Z     | 37         | 10     | 3     |                       | Z     |

| 75         | 4      | 1     | INC X                     | C, Z                                                                                                                                                | 71         | 4      | 2     | OR F, expr           | C, Z  | 45         | 9      | 3     | XOR reg[expr], expr   | Z     |

| Note       | e: Int | erru  | pt acknowledge to Interru | ıpt Vector table                                                                                                                                    | = 13       | cycl   | es.   |                      |       | 46         | 10     | 3     | XOR reg[X+expr], expr | Z     |

# 7.2.2 24V1/24V2 Frequency Selection

24V1 and 24V2 based on the value written to the OSC\_CR1 register.

The following table shows the resulting frequencies for

Table 42: 24V1/24V2 Frequency Selection

| Reg.<br>Value | 24V1<br>MHz    | 24V2 kHz           | Reg.<br>Value | 24V1<br>MHz  | 24V2 kHz          | Reg.<br>Value | 24V1<br>MHz  | 24V2 kHz         | Reg.<br>Value | 24V1<br>MHz  | 24V2 kHz         |

|---------------|----------------|--------------------|---------------|--------------|-------------------|---------------|--------------|------------------|---------------|--------------|------------------|

| 00            | 24.00          | 24000.00           | 40            | 4.80         | 4800.00           | 80            | 2.67         | 2666.67          | C0            | 1.85         | 1846.15          |

| 01            | 24.00          | 12000.00           | 41            | 4.80         | 2400.00           | 81            | 2.67         | 1333.33          | C1            | 1.85         | 923.08           |

| 02            | 24.00          | 8000.00            | 42            | 4.80         | 1600.00           | 82            | 2.67         | 888.89           | C2            | 1.85         | 615.38           |

| 03<br>04      | 24.00<br>24.00 | 6000.00<br>4800.00 | 43<br>44      | 4.80<br>4.80 | 1200.00<br>960.00 | 83<br>84      | 2.67<br>2.67 | 666.67<br>533.33 | C3<br>C4      | 1.85<br>1.85 | 461.54<br>369.23 |

| 05            | 24.00          | 4000.00            | 44            | 4.80         | 800.00            | 85            | 2.67         | 444.44           | C5            | 1.85         | 307.69           |

| 06            | 24.00          | 3428.57            | 46            | 4.80         | 685.71            | 86            | 2.67         | 380.95           | C6            | 1.85         | 263.74           |

| 07            | 24.00          | 3000.00            | 47            | 4.80         | 600.00            | 87            | 2.67         | 333.33           | C7            | 1.85         | 230.77           |

| 08            | 24.00          | 2666.67            | 48            | 4.80         | 533.33            | 88            | 2.67         | 296.30           | C8            | 1.85         | 205.13           |

| 09            | 24.00          | 2400.00            | 49            | 4.80         | 480.00            | 89            | 2.67         | 266.67           | C9            | 1.85         | 184.62           |

| 0A            | 24.00          | 2181.82            | 4A            | 4.80         | 436.36            | 8A            | 2.67         | 242.42           | CA            | 1.85         | 167.83           |

| 0B            | 24.00          | 2000.00            | 4B            | 4.80         | 400.00            | 8B            | 2.67         | 222.22           | CB            | 1.85         | 153.85           |

| 0C<br>0D      | 24.00          | 1846.15<br>1714.29 | 4C<br>4D      | 4.80         | 369.23            | 8C<br>8D      | 2.67         | 205.13           | CC<br>CD      | 1.85<br>1.85 | 142.01<br>131.87 |

| 0E            | 24.00<br>24.00 | 1600.00            | 4D<br>4E      | 4.80<br>4.80 | 342.86<br>320.00  | 8E            | 2.67<br>2.67 | 190.48<br>177.78 | CE            | 1.85         | 123.08           |

| 0F            | 24.00          | 1500.00            | 4F            | 4.80         | 300.00            | 8F            | 2.67         | 166.67           | CF            | 1.85         | 115.38           |

| 10            | 12.00          | 12000.00           | 50            | 4.00         | 4000.00           | 90            | 2.40         | 2400.00          | D0            | 1.71         | 1714.29          |

| 11            | 12.00          | 6000.00            | 51            | 4.00         | 2000.00           | 91            | 2.40         | 1200.00          | D1            | 1.71         | 857.14           |

| 12            | 12.00          | 4000.00            | 52            | 4.00         | 1333.33           | 92            | 2.40         | 800.00           | D2            | 1.71         | 571.43           |

| 13            | 12.00          | 3000.00            | 53            | 4.00         | 1000.00           | 93            | 2.40         | 600.00           | D3            | 1.71         | 428.57           |

| 14            | 12.00          | 2400.00            | 54            | 4.00         | 800.00            | 94            | 2.40         | 480.00           | D4            | 1.71         | 342.86           |

| 15            | 12.00          | 2000.00            | 55            | 4.00         | 666.67            | 95            | 2.40         | 400.00           | D5            | 1.71         | 285.71           |

| 16            | 12.00          | 1714.29            | 56            | 4.00         | 571.43            | 96            | 2.40         | 342.86           | D6            | 1.71         | 244.90           |

| 17<br>18      | 12.00<br>12.00 | 1500.00<br>1333.33 | 57<br>58      | 4.00<br>4.00 | 500.00<br>444.44  | 97<br>98      | 2.40<br>2.40 | 300.00<br>266.67 | D7<br>D8      | 1.71<br>1.71 | 214.29<br>190.48 |

| 19            | 12.00          | 1200.00            | 50<br>59      | 4.00         | 400.00            | 99            | 2.40         | 240.00           | D0            | 1.71         | 171.43           |

| 1A            | 12.00          | 1090.91            | 5A            | 4.00         | 363.64            | 9A            | 2.40         | 218.18           | DA            | 1.71         | 155.84           |

| 1B            | 12.00          | 1000.00            | 5B            | 4.00         | 333.33            | 9B            | 2.40         | 200.00           | DB            | 1.71         | 142.86           |

| 1C            | 12.00          | 923.08             | 5C            | 4.00         | 307.69            | 9C            | 2.40         | 184.62           | DC            | 1.71         | 131.87           |

| 1D            | 12.00          | 857.14             | 5D            | 4.00         | 285.71            | 9D            | 2.40         | 171.43           | DD            | 1.71         | 122.45           |

| 1E            | 12.00          | 800.00             | 5E            | 4.00         | 266.67            | 9E            | 2.40         | 160.00           | DE            | 1.71         | 114.29           |

| 1F            | 12.00          | 750.00             | 5F            | 4.00         | 250.00            | 9F            | 2.40         | 150.00           | DF            | 1.71         | 107.14           |

| 20            | 8.00           | 8000.00            | 60            | 3.43         | 3428.57           | A0            | 2.18         | 2181.82          | E0            | 1.60         | 1600.00          |

| 21<br>22      | 8.00<br>8.00   | 4000.00            | 61            | 3.43         | 1714.29           | A1<br>A2      | 2.18         | 1090.91          | E1            | 1.60<br>1.60 | 800.00           |

| 23            | 8.00           | 2666.67<br>2000.00 | 62<br>63      | 3.43<br>3.43 | 1142.86<br>857.14 | A2<br>A3      | 2.18<br>2.18 | 727.27<br>545.45 | E2<br>E3      | 1.60         | 533.33<br>400.00 |

| 24            | 8.00           | 1600.00            | 64            | 3.43         | 685.71            | A4            | 2.18         | 436.36           | E4            | 1.60         | 320.00           |

| 25            | 8.00           | 1333.33            | 65            | 3.43         | 571.43            | A5            | 2.18         | 363.64           | E5            | 1.60         | 266.67           |

| 26            | 8.00           | 1142.86            | 66            | 3.43         | 489.80            | A6            | 2.18         | 311.69           | E6            | 1.60         | 228.57           |

| 27            | 8.00           | 1000.00            | 67            | 3.43         | 428.57            | A7            | 2.18         | 272.73           | E7            | 1.60         | 200.00           |

| 28            | 8.00           | 888.89             | 68            | 3.43         | 380.95            | A8            | 2.18         | 242.42           | E8            | 1.60         | 177.78           |

| 29            | 8.00           | 800.00             | 69            | 3.43         | 342.86            | A9            | 2.18         | 218.18           | E9            | 1.60         | 160.00           |

| 2A            | 8.00           | 727.27             | 6A            | 3.43         | 311.69            | AA            | 2.18         | 198.35           | EA            | 1.60         | 145.45           |

| 2B<br>2C      | 8.00<br>8.00   | 666.67<br>615.38   | 6B<br>6C      | 3.43<br>3.43 | 285.71<br>263.74  | AB<br>AC      | 2.18<br>2.18 | 181.82           | EB<br>EC      | 1.60<br>1.60 | 133.33<br>123.08 |

| 2C<br>2D      | 8.00           | 571.43             | 6D            | 3.43         | 244.90            | AC            | 2.18         | 167.83<br>155.84 | ED            | 1.60         | 123.08           |

| 2E            | 8.00           | 533.33             | 6E            | 3.43         | 228.57            | AE            | 2.18         | 145.45           | EE            | 1.60         | 106.67           |

| 2F            | 8.00           | 500.00             | 6F            | 3.43         | 214.29            | AF            | 2.18         | 136.36           | EF            | 1.60         | 100.00           |

| 30            | 6.00           | 6000.00            | 70            | 3.00         | 3000.00           | В0            | 2.00         | 2000.00          | F0            | 1.50         | 1500.00          |

| 31            | 6.00           | 3000.00            | 71            | 3.00         | 1500.00           | B1            | 2.00         | 1000.00          | F1            | 1.50         | 750.00           |

| 32            | 6.00           | 2000.00            | 72            | 3.00         | 1000.00           | B2            | 2.00         | 666.67           | F2            | 1.50         | 500.00           |

| 33            | 6.00           | 1500.00            | 73            | 3.00         | 750.00            | B3            | 2.00         | 500.00           | F3            | 1.50         | 375.00           |

| 34            | 6.00           | 1200.00            | 74            | 3.00         | 600.00            | B4            | 2.00         | 400.00           | F4            | 1.50         | 300.00           |

| 35            | 6.00           | 1000.00            | 75            | 3.00         | 500.00            | B5            | 2.00         | 333.33           | F5            | 1.50         | 250.00           |

| 36<br>37      | 6.00<br>6.00   | 857.14<br>750.00   | 76<br>77      | 3.00<br>3.00 | 428.57<br>375.00  | B6<br>B7      | 2.00<br>2.00 | 285.71<br>250.00 | F6<br>F7      | 1.50<br>1.50 | 214.29<br>187.50 |

| 38            | 6.00           | 666.67             | 78            | 3.00         | 333.33            | B8            | 2.00         | 222.22           | F8            | 1.50         | 166.67           |

| 39            | 6.00           | 600.00             | 78<br>79      | 3.00         | 300.00            | B9            | 2.00         | 200.00           | F9            | 1.50         | 150.00           |

| 3A            | 6.00           | 545.45             | 7A            | 3.00         | 272.73            | BA            | 2.00         | 181.82           | FA            | 1.50         | 136.36           |

| 3B            | 6.00           | 500.00             | 7B            | 3.00         | 250.00            | BB            | 2.00         | 166.67           | FB            | 1.50         | 125.00           |

| 3C            | 6.00           | 461.54             | 7C            | 3.00         | 230.77            | BC            | 2.00         | 153.85           | FC            | 1.50         | 115.38           |

| 3D            | 6.00           | 428.57             | 7D            | 3.00         | 214.29            | BD            | 2.00         | 142.86           | FD            | 1.50         | 107.14           |

| 3E            | 6.00           | 400.00             | 7E            | 3.00         | 200.00            | BE            | 2.00         | 133.33           | FE            | 1.50         | 100.00           |

| 3F            | 6.00           | 375.00             | 7F            | 3.00         | 187.5             | BF            | 2.00         | 125.00           | FF            | 1.50         | 93.75            |

# 8.4 Interrupt Masks

Table 44: General Interrupt Mask Register

| Bit #          | 7        | 6     | 5    | 4        | 3        | 2        | 1        | 0               |

|----------------|----------|-------|------|----------|----------|----------|----------|-----------------|

| POR            | 0        | 0     | 0    | 0        | 0        | 0        | 0        | 0               |

| Read/<br>Write | RW       | RW    | RW   | RW       | RW       | RW       | RW       | RW              |

| Bit Name       | Reserved | Sleep | GPIO | Acolumn3 | Acolumn2 | Acolumn1 | Acolumn0 | Voltage Monitor |

#### Bit 7: Reserved

# Bit 6: Sleep Interrupt Enable Bit (see 11.4)

0 = Disabled

1 = Enabled

# Bit 5: GPIO Interrupt Enable Bit (see 8.6)

0 = Disabled

1 = Enabled

# Bit [4]: Acolumn 3 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

# Bit [3]: Acolumn 2 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

# Bit [2]: Acolumn 1 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

# Bit [1]: Acolumn 0 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

# Bit 0: Voltage Monitor Interrupt Enable Bit (see 11.5)

0 = Disabled

1 = Enabled

General Interrupt Mask Register (INT\_MSK0, Address = Bank 0, E0h)

# 9.0 Digital PSoC Blocks

## 9.1 Introduction

PSoC blocks are user configurable system resources. On-chip digital PSoC blocks reduce the need for many MCU part types and external peripheral components. Digital PSoC blocks can be configured to provide a wide variety of peripheral functions. PSoC Designer Software Integrated Development Environment provides automated configuration of PSoC blocks by simply selecting the desired functions. PSoC Designer then generates the proper configuration information and can print a device data sheet unique to that configuration.

Digital PSoC blocks provide up to eight, 8-bit multipurpose timers/counters supporting multiple event timers, real-time clocks, Pulse Width Modulators (PWM), and CRCs. In addition to all PSoC block functions, communication PSoC blocks support full-duplex UARTs and SPI master or slave functions.

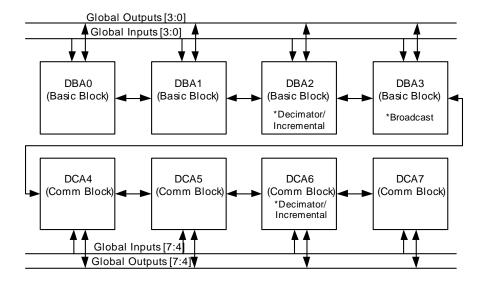

As shown in Figure 12:, there are a total of eight 8-bit digital PSoC blocks in this device family configured as a linear array. Four of these are the Digital Basic Type A blocks and four are the Digital Communications Type A blocks. Each of these digital PSoC blocks can be configured independently, or used in combination.

Each digital PSoC block has a unique Interrupt Vector and Interrupt Enable bit. Functions can be stopped or started with a user-accessible Enable bit.

The Timer/Counter/CRC/PRS/Deadband functions are available on the Digital Basic Type A blocks and also the Digital Communications Type A blocks. The UART and SPI communications functions are only available on the Digital Communications Type A blocks.

There are three configuration registers: the Function Register (DBA00FN-DCA07FN) to select the block function and mode, the Input Register (DBA00IN-DCA07IN) to select data input and clock selection, and the Output Register (DBA00OU-DCA07OU) to select and enable function outputs.

The three data registers are designated Data 0 (DBA00DR0-DCA07DR0), Data 1 (DBA00DR1-DCA07DR1), and Data 2 (DBA00DR2-DCA07DR2). The function of these registers and their bit mapping is

dependent on the overall block function selected by the user.

The one Control Register (DBA00CR0-DCA07CR0) is designated Control 0. The function of this register and its bit mapping is dependent on the overall block function selected by the user.

If the CPU frequency is 24 MHz and a PSoC timer/counter of 24-bits or longer is operating at 48 MHz, a write to the block Control Register to enable it (for example, a call to Timer\_1\_Start) may not start the block properly. In the failure case, the first count will typically be indeterminate as the upper bytes fail to make the first count correctly. However, on the first terminal count, the correct period will be loaded and counted thereafter.

Figure 12: Digital Basic and Digital Communications PSoC Blocks

\*Three of the digital blocks have special functions. DBA3 is a Broadcast block, with output directly available to all digital blocks as a clock or data input. Blocks DBA2 and DCA6 have selectable connections to support Delta Sigma and Incremental A/D converters.

# 9.2 Digital PSoC Block Bank 1 Registers

# 9.2.1 Digital Basic Type A / Communications Type A Block xx Function Register

The Digital Basic Type A/ Communications Type A Block xx Function Register (DBA00FN-DCA07FN) consists of 3 bits [2:0] to select the block function, 2 bits [4:3] to select mode of operation, and 1 bit [5] to indicate the last block in a group of chained blocks.

divided into distinct bit fields. Some bit fields set the PSoC block's resistor ratios or capacitor values. Others configure switches and multiplexers that form connections between internal block nodes. Additionally, a block may be connected via local interconnection resources to neighboring analog PSoC blocks, reference voltage sources, input multiplexers and output busses. Specific advantages and applications of each type are treated separately below.

#### 10.6.1 Local Interconnect

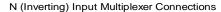

Analog continuous-time PSoC blocks occupy the top row, (row 0) of the analog array. Designated ACA for analog continuous-time subtype "A," each connects to its

neighbors by means of three multiplexers. (Note that unlike the switched capacitor blocks, the continuous time blocks in the current family of parts only have one subtype.) The three are the non-inverting input multiplexer, "PMux," the inverting input multiplexer, "NMux," and the "RBotMux" which controls the node at the bottom of the resistor string. The bit fields, which control these multiplexers, are named PMux, NMux, and RBotMux, respectively. The following diagrams show how each multiplexer connects its ACA block connect to its neighbors. Each arrow points from an input source, either a PSoC block, bus or reference voltage to the block where it is used. Each arrow is labeled with the value to which the bit-field must be set to select that input source.

#### 10.6.1.1 NMux

**Figure 18: NMux Connections**

## 10.7.2.3 Analog Continuous Time Type A Block xx Control 2 Register

CPhase controls which internal clock phase the comparator data is latched on.

can be obtained if the amplifier is being used as a comparator.

CLatch controls whether the latch is active or if it is always transparent.

TestMux – selects block bypass mode for testing and characterization purposes.

CompCap controls whether the compensation capacitor is switched in or not in the op-amp. By not switching in the compensation capacitance, a much faster response Power – encoding for selecting 1 of 4 power levels. The blocks always power up in the off state.

Table 68: Analog Continuous Time Type A Block xx Control 2 Register

| Bit #          | 7      | 6      | 5       | 4          | 3          | 2          | 1        | 0        |

|----------------|--------|--------|---------|------------|------------|------------|----------|----------|

| POR            | 0      | 0      | 0       | 0          | 0          | 0          | 0        | 0        |

| Read/<br>Write | RW     | RW     | RW      | RW         | RW         | RW         | RW       | RW       |

| Bit Name       | CPhase | CLatch | CompCap | TestMux[2] | TestMux[1] | TestMux[0] | Power[1] | Power[0] |

#### Bit 7: CPhase

- 0 = Comparator Control latch transparent on PHI1

- 1 = Comparator Control latch transparent on PHI2

## Bit 6: CLatch

- 0 = Comparator Control latch is always transparent

- 1 = Comparator Control latch is active

# Bit 5: CompCap

- 0 = Comparator Mode

- 1 = Op-amp Mode

#### Bit [4:2]: TestMux [2:0] Select block bypass mode for testing and characterization purposes

|                           | <u>ACA00</u> | <u>ACA01</u> | <u>ACA02</u> | <u>ACA03</u> |

|---------------------------|--------------|--------------|--------------|--------------|

| 1 0 0 = Positive Input to | .ABUS0       | ABUS1        | ABUS2        | ABUS3        |

| 1 0 1 = AGND to           | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

| 1 1 0 = REFLO to          | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

| 1 1 1 = REFHI to          | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

|                           |              |              |              |              |

$0 \times x = All Paths Off$

#### Bit [1:0]: Power [1:0] Encoding for selecting 1 of 4 power levels

0.0 = Off

$0.1 = Low (60 \mu A)$

$1.0 = Med (150 \mu A)$

$1.1 = High (500 \mu A)$

Analog Continuous Time Block 00 Control 2 Register (ACA00CR2, Address = Bank 0/1, 73h)

Analog Continuous Time Block 01 Control 2 Register (ACA01CR2, Address = Bank 0/1, 77h)

Analog Continuous Time Block 02 Control 2 Register (ACA02CR2, Address = Bank 0/1, 7Bh)

Analog Continuous Time Block 03 Control 2 Register (ACA03CR2, Address = Bank 0/1, 7Fh)

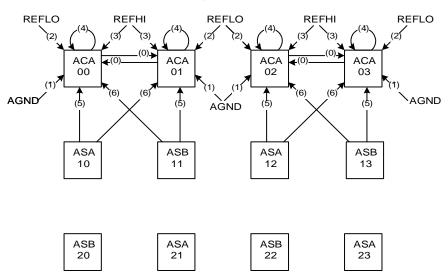

Figure 26: Analog Switch Cap Type B PSoC Blocks

# 10.9.2 Registers

# 10.9.2.1 Analog Switch Cap Type B Block xx Control 0 Register

FCap controls the size of the switched feedback capacitor in the integrator.

ClockPhase controls the internal clock phasing relative to the input clock phasing. ClockPhase affects the output of the analog column bus which is controlled by the AnalogBus bit in Control 2 Register (ASB11CR2, ASB13CR2, ASB20CR2, ASB22CR2).

ASign controls the switch phasing of the switches on the bottom plate of the A capacitor. The bottom plate samples the input or the reference.

The ACap bits set the value of the capacitor in the A path.

Table 73: Analog Switch Cap Type B Block xx Control 0 Register

| Bit #          | 7    | 6          | 5     | 4       | 3       | 2       | 1       | 0       |

|----------------|------|------------|-------|---------|---------|---------|---------|---------|

| POR            | 0    | 0          | 0     | 0       | 0       | 0       | 0       | 0       |

| Read/<br>Write | RW   | RW         | RW    | RW      | RW      | RW      | RW      | RW      |

| Bit Name       | FCap | ClockPhase | ASign | ACap[4] | ACap[3] | ACap[2] | ACap[1] | ACap[0] |

Table 75: Analog Switch Cap Type B Block xx Control 2 Register

| Bit #          | 7         | 6       | 5        | 4       | 3       | 2       | 1       | 0       |

|----------------|-----------|---------|----------|---------|---------|---------|---------|---------|

| POR            | 0         | 0       | 0        | 0       | 0       | 0       | 0       | 0       |

| Read/<br>Write | RW        | RW      | RW       | RW      | RW      | RW      | RW      | RW      |

| Bit Name       | AnalogBus | CompBus | AutoZero | CCap[4] | CCap[3] | CCap[2] | CCap[1] | CCap[0] |

#### Bit 7: AnalogBus Enable output to the analog bus

- 0 = Disable output to analog column bus

- 1 = Enable output to analog column bus

(The output on the analog column bus is affected by the state of the ClockPhase bit in Control 0 Register (ASB11CR0, ASB13CR0, ASB20CR0, ASB22CR0). If AnalogBus is set to 0, the output to the analog column bus is tri-stated. If AnalogBus is set to 1, the ClockPhase bit selects the signal that is output to the analog column bus. If the ClockPhase bit is 0, the block output is gated by sampling clock on last part of PHI2. If the ClockPhase bit is 1, the block output continuously drives the analog column bus)

## Bit 6: CompBus Enable output to the comparator bus

- 0 = Disable output to comparator bus

- 1 = Enable output to comparator bus

### Bit 5: AutoZero Bit for controlling gated switches

- 0 = Shorting switch is not active. Input cap branches shorted to op-amp input

- 1 = Shorting switch is enabled during internal PHI1. Input cap branches shorted to analog ground during internal PHI1 and to op-amp input during internal PHI2.

#### Bit [4:0]: CCap [4:0] Binary encoding for 32 possible capacitor sizes for C Capacitor:

| 00000 00 11 11 1                             | 10000 100 '' '' '                       |

|----------------------------------------------|-----------------------------------------|

| $0\ 0\ 0\ 0\ 0 = 0$ Capacitor units in array | 10000 = 16 Capacitor units in array     |

| 0 0 0 0 1 = 1 Capacitor units in array       | 1 0 0 0 1 = 17 Capacitor units in array |

| 0 0 0 1 0 = 2 Capacitor units in array       | 1 0 0 1 0 = 18 Capacitor units in array |

| 0 0 0 1 1 = 3 Capacitor units in array       | 1 0 0 1 1 = 19 Capacitor units in array |

| 0 0 1 0 0 = 4 Capacitor units in array       | 10100 = 20 Capacitor units in array     |

| 0 0 1 0 1 = 5 Capacitor units in array       | 1 0 1 0 1 = 21 Capacitor units in array |

| 0 0 1 1 0 = 6 Capacitor units in array       | 1 0 1 1 0 = 22 Capacitor units in array |

| 0 0 1 1 1 = 7 Capacitor units in array       | 1 0 1 1 1 = 23 Capacitor units in array |

| 0 1 0 0 0 = 8 Capacitor units in array       | 1 1 0 0 0 = 24 Capacitor units in array |

| 0 1 0 0 1 = 9 Capacitor units in array       | 1 1 0 0 1 = 25 Capacitor units in array |

| 0 1 0 1 0 = 10 Capacitor units in array      | 1 1 0 1 0 = 26 Capacitor units in array |

| 0 1 0 1 1 = 11 Capacitor units in array      | 1 1 0 1 1 = 27 Capacitor units in array |

| 0 1 1 0 0 = 12 Capacitor units in array      | 1 1 1 0 0 = 28 Capacitor units in array |

| 0 1 1 0 1 = 13 Capacitor units in array      | 1 1 1 0 1 = 29 Capacitor units in array |

| 0 1 1 1 0 = 14 Capacitor units in array      | 1 1 1 1 0 = 30 Capacitor units in array |

| 0 1 1 1 1 = 15 Capacitor units in array      | 1 1 1 1 1 = 31 Capacitor units in array |

Analog Switch Cap Type B Block 11 Control 2 Register (ASB11CR2, Address = Bank 0/1, 86h)

Analog Switch Cap Type B Block 13 Control 2 Register (ASB13CR2, Address = Bank 0/1, 8Eh)

Analog Switch Cap Type B Block 20 Control 2 Register (ASB20CR2, Address = Bank 0/1, 92h)

Analog Switch Cap Type B Block 22 Control 2 Register (ASB22CR2, Address = Bank 0/1, 9Ah)

#### 10.9.2.4 Analog Switch Cap Type B Block xx Control 3 Register

ARefMux selects the reference input of the A capacitor branch.

FSW1 is used to control a switch in the integrator capacitor path. It connects the output of the op-amp to the integrating cap. The state of the switch is affected by the state of the AutoZero bit in Control 2 Register (ASB11CR2, ASB13CR2, ASB20CR2, ASB22CR2). If the FSW1 bit is set to 0, the switch is always disabled. If the FSW1 bit is set to 1, the AutoZero bit determines the state of the switch. If the AutoZero bit is 0, the switch is enabled at all times. If the AutoZero bit is 1, the switch is enabled only when the internal PHI2 is high.

FSW0 is used to control a switch in the integrator capacitor path. It connects the output of the op-amp to analog ground.

BSW is used to control switching in the B branch. If disabled, the B capacitor branch is a continuous time branch like the C branch of the SC A Block. If enabled, then on internal PHI1, both ends of the cap are switched to analog ground. On internal PHI2, one end is switched to the B input and the other end is switched to the summing node.

BMuxSCB controls muxing to the input of the B capacitor branch. The B branch can be switched or unswitched.

Table 76: Analog Switch Cap Type B Block xx Control 3 Register

| Bit #          | 7          | 6          | 5      | 4      | 3   | 2       | 1        | 0        |

|----------------|------------|------------|--------|--------|-----|---------|----------|----------|

| POR            | 0          | 0          | 0      | 0      | 0   | 0       | 0        | 0        |

| Read/<br>Write | RW         | RW         | RW     | RW     | RW  | RW      | RW       | RW       |

| Bit Name       | ARefMux[1] | ARefMux[0] | FSW[1] | FSW[0] | BSW | BMuxSCB | Power[1] | Power[0] |

# Bit [7:6]: ARefMux [1:0] Encoding for selecting reference input

- 0 0 = Analog ground is selected

- 0 1 = REFHI input selected (This is usually the high reference)

- 1 0 = REFLO input selected (This is usually the low reference)

- 1 1 = Reference selection is driven by the comparator (When output comparator node is set high, the input is set to REFHI. When set low, the input is set to REFLO)

#### Bit 5: FSW1 Bit for controlling gated switches

0 = Switch is disabled

FSW1 bit is set to 1; the state of the switch is determined by the AutoZero bit. If the AutoZero bit is 0, the switch is enabled at all times. If the AutoZero bit is 1, the switch is enabled only when the internal PHI2 is high

#### Bit 4: FSW0 Bits for controlling gated switches

- 0 = Switch is disabled

- 1 = Switch is enabled when PHI1 is high

#### Bit 3: BSW Enable switching in branch

- 0 = B branch is a continuous time path

- 1 = B branch is switched with internal PHI2 sampling

# Bit 2: <u>BMuxSCB</u> Encoding for selecting B inputs. (Note that the available mux inputs vary by individual PSoC block) <u>ASB11 ASB13 ASB20 ASB22</u>

- 0 = ACA00 ACA02 ASB11 ASB13

- 1 = ACA01 ACA03 ASA10 ASA12

#### Bit [1:0]: Power [1:0] Encoding for selecting 1 of 4 power levels

- 0.0 = Off

- $0.1 = 10 \mu A$ , typical

- $1.0 = 50 \mu A$ , typical

- 1 1 = 200  $\mu$ A, typical

```

Analog Switch Cap Type B Block 11 Control 3 Register (ASB11CR3, Address = Bank 0/1, 87h) Analog Switch Cap Type B Block 13 Control 3 Register (ASB13CR3, Address = Bank 0/1, 8Fh) Analog Switch Cap Type B Block 20 Control 3 Register (ASB20CR3, Address = Bank 0/1, 93h) Analog Switch Cap Type B Block 22 Control 3 Register (ASB22CR3, Address = Bank 0/1, 98h)

```

## 10.12.4 Analog Output Buffer Control Register

Table 81: Analog Output Buffer Control Register

| Bit #          | 7        | 6        | 5       | 4       | 3       | 2       | 1        | 0   |

|----------------|----------|----------|---------|---------|---------|---------|----------|-----|

| POR            | 0        | 0        | 0       | 0       | 0       | 0       | 0        | 0   |

| Read/<br>Write | W        | W        | W       | W       | W       | W       |          | W   |

| Bit Name       | ACol1Mux | ACol2Mux | ABUF1EN | ABUF2EN | ABUF0EN | ABUF3EN | Reserved | PWR |

#### Bit 7: ACol1Mux

0 = Set column 1 input to column 1 input mux output

1 = Set column 1 input to column 0 input mux output

#### Bit 6: ACol2Mux

0 = Set column 2 input to column 2 input mux output

1 = Set column 2 input to column 3 input mux output

Bit 5: ABUF1EN Enables the analog output buffer for Analog Column 1 (Pin P0[5])

0 = Disable analog output buffer

1 = Enable analog output buffer

Bit 4: ABUF2EN Enables the analog output buffer for Analog Column 2 (Pin P0[4])

0 = Disable analog output buffer

1 = Enable analog output buffer

Bit 3: ABUF0EN Enables the analog output buffer for Analog Column 0 (Pin P0[3])

0 = Disable analog output buffer

1 = Enable analog output buffer

Bit 2: ABUF3EN Enables the analog output buffer for Analog Column 3 (Pin P0[2])

0 = Disable analog output buffer

1 = Enable analog output buffer

Bit [1]: Reserved Must be left as 0

Bit [0]: PWR Determines power level of all output buffers

0 = Low output power

1 = High output power

Analog Output Buffer Control Register (ABF\_CR, Address = Bank 1, 62h)

# 10.13 Analog Modulator

The user has the capability to use the Analog Switch Cap Type A PSoC Blocks in Columns 0 and 2 as amplitude modulators. The Analog Modulator Control Register (AMD\_CR) allows the user to select the appropriate modulating signal. When the modulating signal is low, the polarity follows the setting of the ASign bit set in the Analog Switch Cap Type A Control 0 Register (ASAxxCR0). When this signal is high, the normal gain polarity of the PSoC block is inverted.

interrupt will wake the part from sleep. The Stop bit in the Status and Control Register (CPU\_SCR) must be cleared for a part to resume out of sleep.

Any digital PSoC block that is clocked by a System Clock other than the **32K** system-clocking signal or external pins will be stopped, as these clocks do not run in sleep mode.

The Internal Main Oscillator restarts immediately on exiting either the Full Sleep or CPU Sleep modes. Analog functions must be re-enabled by firmware. If the External Crystal Oscillator is used and the internal PLL is enabled, the PLL will take many cycles to change from its initial 2.5% accuracy to track that of the External Crystal Oscillator. If the PLL is enabled, there will be a  $30\mu s$  (one full 32K cycle) delay hold-off time for the CPU to let the VCO and PLL stabilize. If the PLL is not enabled, the hold-off time is one half of the 32K cycle. For further details on PLL, see 7.0.

The Sleep interrupt allows the microcontroller to wake up periodically and poll system components while maintaining very low average power consumption. The sleep interrupt may also be used to provide periodic interrupts during non-sleep modes.

In System Sleep State, GPIO Pins P2[4] and P2[6] should be held to a logic low or a false Low Voltage Detect interrupt may be triggered. The cause is in the System Sleep State, the internal Bandgap reference generator is turned off and the reference voltage is maintained on a capacitor.

The circumstances are that during sleep, the reference voltage on the capacitor is refreshed periodically at the sleep system duty cycle. Between refresh cycles, this voltage may leak slightly to either the positive supply or ground. If pins P2[4] or P2[6] are in a high state, the leakage to the positive supply is accelerated (especially at high temperature). Since the reference voltage is compared to the supply to detect a low voltage condition, this accelerated leakage to the positive supply voltage will cause that voltage to appear lower than it actually is, leading to the generation of a false Low Voltage Detect interrupt.

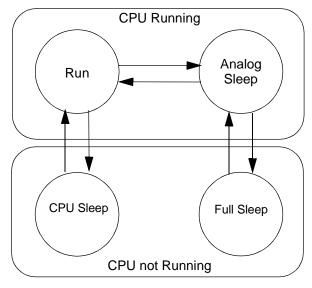

Figure 32: Three Sleep States

# 11.5 Supply Voltage Monitor

The Supply Voltage Monitor detector generates an interrupt whenever Vcc drops below a pre-programmed value. There are eight voltage trip points that are selectable by setting the VM [2:0] bit in the Voltage Monitor

Control Register (VLT\_CR). These bits also select the Switch Mode Pump trip points. The Supply Voltage Monitor will remain active when the device enters sleep mode.

Table 96: Voltage Monitor Control Register

| Bit #          | 7   | 6        | 5        | 4        | 3        | 2      | 1      | 0      |

|----------------|-----|----------|----------|----------|----------|--------|--------|--------|

| POR            | 0   | 0        | 0        | 0        | 0        | 0      | 0      | 0      |

| Read/<br>Write | W   |          |          |          |          | W      | W      | W      |

| Bit Name       | SMP | Reserved | Reserved | Reserved | Reserved | VM [2] | VM [1] | VM [0] |

Bit 7: SMP Disables SMP function

0 = Switch Mode Pump enabled, default

1 = Switch Mode Pump disabled

Bit 6: Reserved

Bit 5: Reserved

Bit 4: Reserved

Bit 3: Reserved

## Bit [2:0]: VM [2:0]

1 0 1 = 4.48 Trip Voltage 1 0 1 = 4.64 Trip Voltage 1 1 0 = 4.65 Trip Voltage 1 1 0 = 4.82 Trip Voltage

1 1 0 = 4.56 Trip Voltage 1 1 0 = 4.82 Trip Voltage 1 1 1 = 4.64 Trip Voltage 1 1 1 = 5.00 Trip Voltage

Voltage Monitor Control Register (VLT\_CR, Address = Bank 1, E3h)

<sup>1.</sup> Voltages are ideal typical values. Tolerances are in Table 104 on page 129.

# 12.0 Development Tools

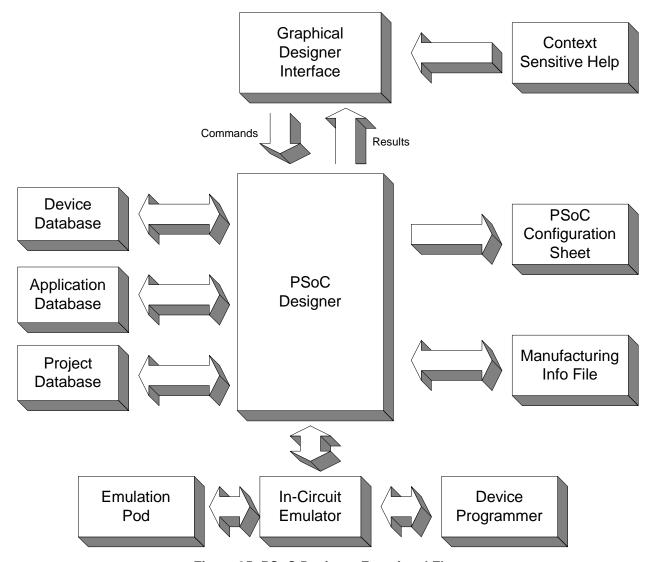

Figure 35: PSoC Designer Functional Flow

## 12.1 Overview

The Cypress MicroSystems PSoC Designer is a Microsoft® Windows-based, integrated development environment for the Programmable System-on-Chip (PSoC) devices. The PSoC Designer runs on Windows 98, Windows NT 4.0, Windows 2000, Windows Millennium (Me), or Windows XP.

PSoC Designer helps the customer to select an operating configuration for the microcontroller, write application code that uses the microcontroller, and debug the application. This system provides design database management by project, an integrated debugger with In-Circuit

Emulator, in-system programming support, and the CYASM macro assembler for the CPUs.

PSoC Designer also supports a high-level C language compiler developed specifically for the devices in the family.

125

## 13.2.1 DC Operational Amplifier Specifications

#### 13.2.1.1 5V Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges, 5V + /-5% and  $-40^{\circ}C <= T_A <= 85^{\circ}C$ . The Operational Amplifier is a component of both the Analog Continuous Time PSoC blocks and the Analog Switch Cap

PSoC blocks. The guaranteed specifications are measured in the Analog Continuous Time PSoC block. Typical parameters apply to 5V at 25°C and are for design guidance only. For 3.3V operation, see Table 106 on page 131.

Table 105: 5V DC Operational Amplifier Specifications

| Symbol | 5V DC Operational Amplifier Specifications                                                | Minimum                                                     | Typical           | Maximum               | Unit           |

|--------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------|-----------------------|----------------|

|        | Input Offset Voltage (Absolute Value)                                                     | -                                                           | 7                 | 30                    | mV             |

|        | Average Input Offset Voltage Drift                                                        | -                                                           | +24               | -                     | μV/°C          |

|        | Input Leakage Current <sup>1</sup>                                                        | -                                                           | 3                 | 1000                  | nA             |

|        | Input Capacitance <sup>2</sup>                                                            | .30                                                         | .34               | .40                   | pF             |

|        | Common Mode Voltage Range <sup>3</sup>                                                    | .5                                                          | -                 | V <sub>CC</sub> - 1.0 | VDC            |

|        | Common Mode Rejection Ratio                                                               | 80                                                          | -                 | -                     | dB             |

|        | Open Loop Gain                                                                            | 80                                                          | -                 | -                     | dB             |

|        | High Output Voltage Swing (Worst Case Internal Load) Bias = Low Bias = Medium Bias = High | V <sub>cc</sub> 4<br>V <sub>cc</sub> 4<br>V <sub>cc</sub> 4 | -<br>-<br>-       | -<br>-<br>-           | V<br>V<br>V    |

|        | Low Output Voltage Swing (Worst Case Internal Load) Bias = Low Bias = Medium Bias = High  | -<br>-<br>-                                                 | -<br>-<br>-       | 0.1<br>0.1<br>0.1     | V<br>V<br>V    |

|        | Supply Current (Including Associated AGND Buffer) Bias = Low Bias = Medium Bias = High    | -<br>-<br>-                                                 | 125<br>280<br>760 | 300<br>600<br>1500    | μΑ<br>μΑ<br>μΑ |

|        | Supply Voltage Rejection Ratio                                                            | 60                                                          | -                 | -                     | dB             |

<sup>1.</sup> The leakage current includes the Analog Continuous Time PSoC block mux and the analog input mux. The leakage related to the General Purpose I/O pins is not included here.

<sup>2.</sup> The Input Capacitance includes the Analog Continuous Time PSoC block mux and the analog input mux. The capacitance of the General Purpose I/O pins is not included here.

<sup>3.</sup> The common-mode input voltage range is measured through an analog output buffer. The specification includes the limitations imposed by the characteristics of the analog output buffer.

## 13.2.1.2 3.3V Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges, 3.3V +/- 10% and -40°C <=  $T_A$  <= 85°C. The Operational Amplifier is a component of both the Analog Continuous Time PSoC blocks and the Analog Switch

Cap PSoC blocks. The guaranteed specifications are measured in the Analog Continuous Time PSoC block. Typical parameters apply to 5V at 25°C and are for design guidance only. For 5V operation, see Table 105 on page 130.

Table 106: 3.3V DC Operational Amplifier Specifications

| Symbol | 3.3V DC Operational Amplifier Specifications                                              | Minimum                                                     | Typical          | Maximum               | Unit           |

|--------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|-----------------------|----------------|

|        | Input Offset Voltage (Absolute Value)                                                     | -                                                           | 7                | 30                    | mV             |

|        | Average Input Offset Voltage Drift                                                        | -                                                           | +24              | -                     | μV/°C          |

|        | Input Leakage Current <sup>1</sup>                                                        | -                                                           | 2                | 700                   | nA             |

|        | Input Capacitance <sup>2</sup>                                                            | .32                                                         | .36              | .42                   | pF             |

|        | Common Mode Voltage Range <sup>3</sup>                                                    | .5                                                          | -                | V <sub>cc</sub> - 1.0 | VDC            |

|        | Common Mode Rejection Ratio                                                               | 80                                                          | -                | -                     | dB             |

|        | Open Loop Gain                                                                            | 80                                                          | -                | -                     | dB             |

|        | High Output Voltage Swing (Worst Case Internal Load) Bias = Low Bias = Medium Bias = High | V <sub>cc</sub> 4<br>V <sub>cc</sub> 4<br>V <sub>cc</sub> 4 | -<br>-<br>-      | -<br>-<br>-           | V<br>V<br>V    |

|        | Low Output Voltage Swing (Worst Case Internal Load) Bias = Low Bias = Medium Bias = High  | -                                                           | -                | 0.1<br>0.1<br>0.1     | V<br>V<br>V    |

|        | Supply Current (Including Associated AGND Buffer) Bias = Low Bias = Medium Bias = High    | -                                                           | 80<br>112<br>320 | 200<br>300<br>800     | μΑ<br>μΑ<br>μΑ |

|        | Supply Voltage Rejection Ratio                                                            | 60                                                          | -                | -                     | dB             |

<sup>1.</sup> The leakage current includes the Analog Continuous Time PSoC block mux and the analog input mux. The leakage related to the General Purpose I/O pins is not included here.

<sup>2.</sup> The Input Capacitance includes the Analog Continuous Time PSoC block mux and the analog input mux. The capacitance of the General Purpose I/O pins is not included here.

<sup>3.</sup> The common-mode input voltage range is measured through an analog output buffer. The specification includes the limitations imposed by the characteristics of the analog output buffer

Table 120: 3.3V AC Analog Output Buffer Specifications

| Symbol | 3.3V AC Analog Output Buffer Specifications                                                  | Minimum    | Typical | Maximum    | Unit         |

|--------|----------------------------------------------------------------------------------------------|------------|---------|------------|--------------|

|        | Rising Settling Time to 0.1%, 1V Step, 100pF Load Bias = Low Bias = High                     | -          | -       | 3.2<br>3.2 | µs<br>µs     |

|        | Falling Settling Time to 0.1%, 1V Step, 100pF Load Bias = Low Bias = High                    | -          | -       | 2.6<br>2.6 | µs<br>µs     |

|        | Rising Slew Rate (20% to 80%), 1V Step, 100pF Load Bias = Low Bias = High                    | .5<br>.5   | -       | -          | V/µs<br>V/µs |

|        | Falling Slew Rate (80% to 20%), 1V Step, 100pF Load Bias = Low Bias = High                   | .5<br>.5   | -       | -          | V/µs<br>V/µs |

|        | Small Signal Bandwidth, 20mV <sub>pp</sub> , 3dB BW, 100pF Load<br>Bias = Low<br>Bias = High | 1.3<br>1.3 | -       | -          | MHz<br>MHz   |

|        | Large Signal Bandwidth, 1V <sub>pp</sub> , 3dB BW, 100pF Load<br>Bias = Low<br>Bias = High   | 360<br>360 | -       | -          | kHz<br>kHz   |

# 13.3.3 AC Programming Specifications

**Table 121: AC Programming Specifications**

| Symbol              | AC Programming Specifications           | Minimum | Typical | Maximum | Unit |

|---------------------|-----------------------------------------|---------|---------|---------|------|

| T <sub>rsclk</sub>  | Rise Time of SCLK                       | 1       | -       | 20      | ns   |

| T <sub>fsclk</sub>  | Fall Time of SCLK                       | 1       | -       | 20      | ns   |

| T <sub>ssclk</sub>  | Data Set up Time to Rising Edge of SCLK | 25      | -       | -       | ns   |

| T <sub>hsclk</sub>  | Data Hold Time from Rising Edge of SCLK | 25      | -       | -       | ns   |

| F <sub>sclk</sub>   | Frequency of SCLK                       | 2       | -       | 20      | MHz  |

| T <sub>eraseb</sub> | Flash Erase Time (Block)                | -       | 10      | -       | ms   |

| T <sub>erasef</sub> | Flash Erase Time (Full)                 | -       | 40      | -       | ms   |

| T <sub>write</sub>  | Flash Block Write Time                  | 2       | 10      | 20      | ms   |

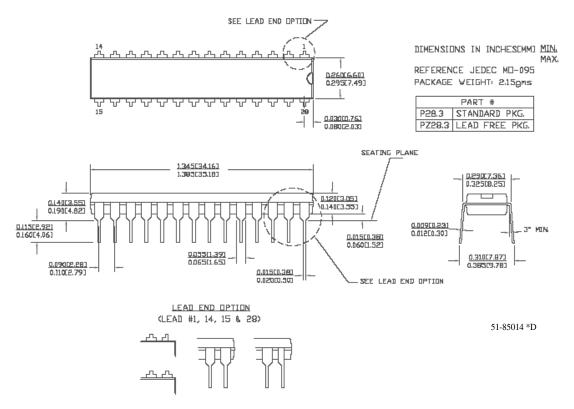

# 14.0 Packaging Information

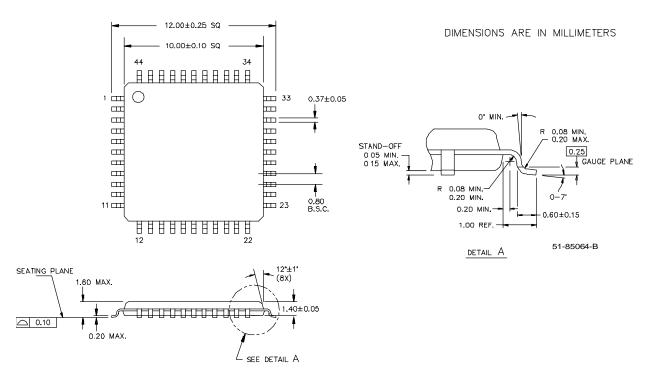

Figure 37: 44-Lead Thin Plastic Quad Flat Pack A44

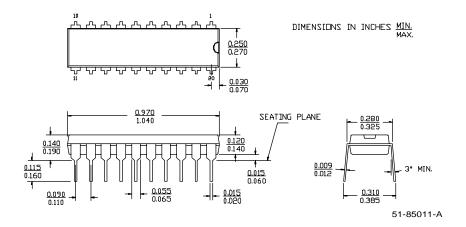

Figure 41: 20-Lead (300-Mil) Molded DIP P5

Figure 42: 28-Lead (300-Mil) Molded DIP P21

146 Document #: 38-12010 CY Rev. \*C