Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorM8CCore Size8-BitSpeed24MHzConnectivitySPI, UART/USARTPeripheralsLVD, POR, PWM, WDTNumber of I/O24Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type28-SSOP (0.209°, 5.30mm Width)Supplier Device Package28-SSOPPurchase URLhttps://www.e-xfl.com/product-detail/infineon-technologies/cy8c26443-24pvi | Details                    |                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

| Core Size8-BitSpeed24MHzConnectivitySPI, UART/USARTPeripheralsLVD, POR, PWM, WDTNumber of I/O24Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device PackageESSOP                                                                                                     | Product Status             | Obsolete                                                                   |

| Speed24MHzConnectivitySPI, UART/USARTPeripheralsLVD, POR, PWM, WDTNumber of I/O24Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                 | Core Processor             | M8C                                                                        |

| ConnectivitySPI, UART/USARTPeripheralsLVD, POR, PWM, WDTNumber of I/O24Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)                                                                                                                                                         | Core Size                  | 8-Bit                                                                      |

| PeripheralsLVD, POR, PWM, WDTNumber of I/O24Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Suppler Device Package28-SSOP                                                                                                                                                       | Speed                      | 24MHz                                                                      |

| Number of I/O24Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)                                                                                                                                                                                                                 | Connectivity               | SPI, UART/USART                                                            |

| Program Memory Size16KB (16K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                  | Peripherals                | LVD, POR, PWM, WDT                                                         |

| Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                   | Number of I/O              | 24                                                                         |

| EEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                           | Program Memory Size        | 16KB (16K x 8)                                                             |

| RAM Size256 x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                                       | Program Memory Type        | FLASH                                                                      |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.25VData ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                                                      | EEPROM Size                | -                                                                          |

| Data ConvertersA/D 1x8b, 1x11b, 1x12b; D/A 1x9bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                                                                                          | RAM Size                   | 256 x 8                                                                    |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                                                                                                                                         | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                 |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                                                                                                                                                                | Data Converters            | A/D 1x8b, 1x11b, 1x12b; D/A 1x9b                                           |

| Mounting TypeSurface MountPackage / Case28-SSOP (0.209", 5.30mm Width)Supplier Device Package28-SSOP                                                                                                                                                                                                                                                                                                                                                                                                                                      | Oscillator Type            | Internal                                                                   |

| Package / Case     28-SSOP (0.209", 5.30mm Width)       Supplier Device Package     28-SSOP                                                                                                                                                                                                                                                                                                                                                                                                                                               | Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Supplier Device Package 28-SSOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Mounting Type              | Surface Mount                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/cy8c26443-24pvi                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | 28-SSOP                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c26443-24pvi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Tables

| Table 1: Device Family Key Features                    |    |

|--------------------------------------------------------|----|

| Table 2: Pin-out 8 Pin                                 | 15 |

| Table 3: Pin-out 20 Pin                                | 15 |

| Table 4: Pin-out 28 Pin                                | 16 |

| Table 5: Pin-out 44 Pin                                | 16 |

| Table 6: Pin-out 48 Pin                                |    |

| Table 7: CPU Registers and Mnemonics                   |    |

| Table 8: Flags Register                                | 20 |

| Table 9: Accumulator Register (CPU_A)                  |    |

| Table 10: Index Register (CPU_X)                       | 21 |

| Table 11: Stack Pointer Register (CPU_SP)              |    |

| Table 12: Program Counter Register (CPU_PC)            |    |

| Table 13: Source Immediate                             |    |

| Table 14: Source Direct                                |    |

| Table 15: Source Indexed                               |    |

| Table 16: Destination Direct                           |    |

| Table 17: Destination Indexed                          |    |

| Table 18: Destination Direct Immediate                 |    |

| Table 19: Destination Indexed Immediate                |    |

| Table 20: Destination Direct Direct                    |    |

| Table 21: Source Indirect Post Increment               |    |

| Table 22: Destination Indirect Post Increment          |    |

| Table 23: Instruction Set Summary (Sorted by Mnemonic) |    |

| Table 24: Flash Program Memory Map                     |    |

| Table 25: RAM Data Memory Map                          |    |

| Table 26: Bank 0                                       |    |

| Table 27: Bank 1                                       |    |

| Table 28: Port Data Registers                          |    |

| Table 29: Port Interrupt Enable Registers              |    |

| Table 30: Port Global Select Registers                 |    |

| Table 31: Port Drive Mode 0 Registers                  |    |

| Table 32: Port Drive Mode 1 Registers                  |    |

| Table 33: Port Interrupt Control 0 Registers           |    |

| Table 34: Port Interrupt Control 1 Registers           |    |

| Table 35: Internal Main Oscillator Trim Register       |    |

| Table 36: Internal Low Speed Oscillator Trim Register  |    |

| Table 37: External Crystal Oscillator Trim Register    |    |

| Table 38: Typical Package Capacitances                 |    |

| Table 39: System Clocking Signals and Definitions      |    |

| Table 40: Oscillator Control 0 Register                |    |

| Table 41: Oscillator Control 1 Register                |    |

| Table 42: 24V1/24V2 Frequency Selection                |    |

| Table 43: Interrupt Vector Table                       |    |

| Table 44: General Interrupt Mask Register              |    |

| Table 45: Digital PSoC Block Interrupt Mask Register   | 46 |

# List of Figures

| Figure 1: Block Diagram                                         | 13  |

|-----------------------------------------------------------------|-----|

| Figure 2: CY8C25122                                             | 15  |

| Figure 3: CY8C26233                                             | 15  |

| Figure 4: 26443 PDIP/SOIC/SSOP                                  | 16  |

| Figure 5: 26643 TQFP                                            |     |

| Figure 6: 26643 PDIP/SSOP                                       | 18  |

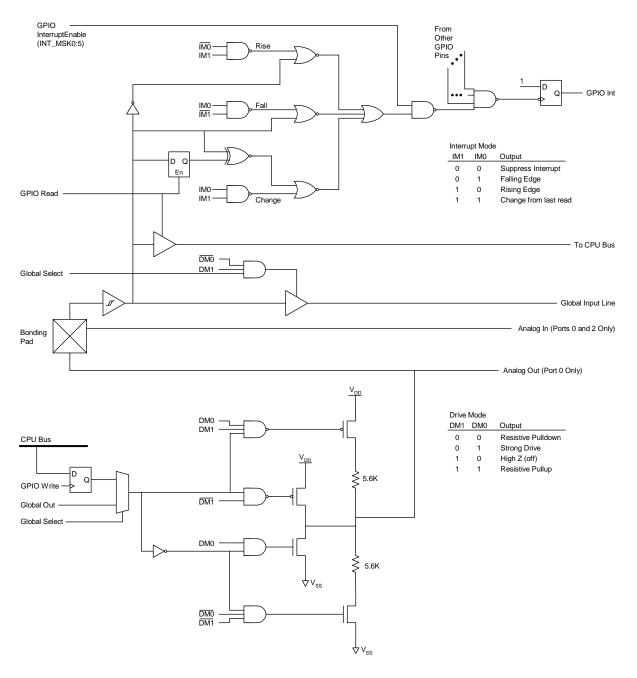

| Figure 7: General Purpose I/O Pins                              |     |

| Figure 8: External Crystal Oscillator Connections               | 37  |

| Figure 9: PSoC MCU Clock Tree of Signals                        | .39 |

| Figure 10: Interrupts Overview                                  | .43 |

| Figure 11: GPIO Interrupt Enable Diagram                        |     |

| Figure 12: Digital Basic and Digital Communications PSoC Blocks | .49 |

| Figure 13: Polynomial LFSR                                      | .65 |

| Figure 14: Polynomial PRS                                       | .65 |

| Figure 15: SPI Waveforms                                        | 68  |

| Figure 16: Array of Analog PSoC Blocks                          | 72  |

| Figure 17: Analog Reference Control Schematic                   | 73  |

| Figure 18: NMux Connections                                     |     |

| Figure 19: PMux Connections                                     | 79  |

| Figure 20: RBotMux Connections                                  | 79  |

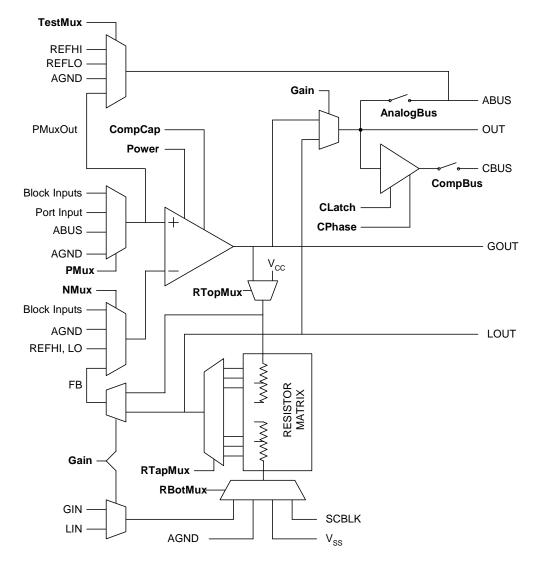

| Figure 21: Analog Continuous Time PSoC Blocks                   | 81  |

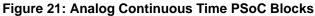

| Figure 22: Analog Switch Cap Type A PSoC Blocks                 | 86  |

| Figure 23: AMux Connections                                     | 87  |

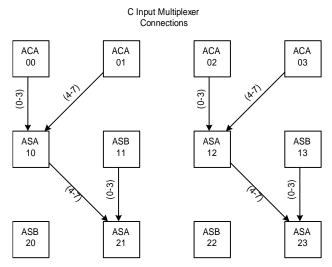

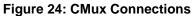

| Figure 24: CMux Connections                                     | 87  |

| Figure 25: BMuxSCA/SCB Connections                              | 88  |

| Figure 26: Analog Switch Cap Type B PSoC Blocks                 | 95  |

| Figure 27: Analog Input Muxing                                  |     |

| Figure 28: Analog Output Buffers                                | 105 |

| Figure 29: Multiply/Accumulate Block Diagram                    |     |

| Figure 30: Decimator Coefficients                               | 112 |

| Figure 31: Execution Reset                                      | 115 |

| Figure 32: Three Sleep States                                   |     |

| Figure 33: Switch Mode Pump                                     | 119 |

| Figure 34: Programming Wave Forms                               | 124 |

| Figure 35: PSoC Designer Functional Flow                        |     |

| Figure 36: CY8C25xxx/CY8C26xxx Voltage Frequency Graph          | 127 |

| Figure 37: 44-Lead Thin Plastic Quad Flat Pack A44              | 143 |

| Figure 38: 20-Pin Shrunk Small Outline Package O20              |     |

| Figure 39: 28-Lead (210-Mil) Shrunk Small Outline Package O28   | 145 |

| Figure 40: 48-Lead Shrunk Small Outline Package O48             | 145 |

| Figure 41: 20-Lead (300-Mil) Molded DIP P5                      | 146 |

| Figure 42: 28-Lead (300-Mil) Molded DIP P21                     | 146 |

| Figure 43: 48-Lead (600-Mil) Molded DIP P25                     | 147 |

| Figure 44: 20-Lead (300-Mil) Molded SOIC S5                     |     |

| Figure 45: 28-Lead (300-Mil) Molded SOIC S21                    | 148 |

# 3.0 Memory Organization

# 3.1 Flash Program Memory Organization

### Table 24: Flash Program Memory Map

| Address | Description                                 |

|---------|---------------------------------------------|

| 0x0000  | Reset Vector                                |

| 0x0004  | Supply Monitor Interrupt Vector             |

| 0x0008  | DBA 00 PSoC Block Interrupt Vector          |

| 0x000C  | DBA 01 PSoC Block Interrupt Vector          |

| 0x0010  | DBA 02 PSoC Block Interrupt Vector          |

| 0x0014  | DBA 03 PSoC Block Interrupt Vector          |

| 0x0018  | DCA 04 PSoC Block Interrupt Vector          |

| 0x001C  | DCA 05 PSoC Block Interrupt Vector          |

| 0x0020  | DCA 06 PSoC Block Interrupt Vector          |

| 0x0024  | DCA 07 PSoC Block Interrupt Vector          |

| 0x0028  | Analog Column 0 Interrupt Vector            |

| 0x002C  | Analog Column 1 Interrupt Vector            |

| 0x0030  | Analog Column 2 Interrupt Vector            |

| 0x0034  | Analog Column 3 Interrupt Vector            |

| 0x0038  | GPIO Interrupt Vector                       |

| 0x003C  | Sleep Timer Interrupt Vector                |

| 0x0040  | On-Chip User Program Memory Starts<br>Here  |

|         | ***                                         |

|         | ***                                         |

|         | ***                                         |

| 0x3FFF  | 16K Flash Maximum Depending on Ver-<br>sion |

# 3.2 RAM Data Memory Organization

The stack on this device grows from low addresses to high addresses. The Linker function within PSoC Designer locates the bottom of the stack after the end of Global Variables. This allows the stack to grow from just after the Global Variables until 0xFF. The stack will wrap back to 0x00 on an overflow condition.

| Address | Description                                    |

|---------|------------------------------------------------|

| 0x00    | First General Purpose RAM Location             |

| 0xXX    | General Purpose RAM                            |

| 0xXY    | General Purpose RAM                            |

| 0xXZ    | Last General Purpose RAM Location              |

| 0xYX    | Bottom of Hardware Stack                       |

| 0xYY    | $\Downarrow$ Stack Grows This Way $\Downarrow$ |

| 0xFF    | Top of Hardware Stack                          |

Table 25: RAM Data Memory Map

# 4.0 Register Organization

# 4.1 Introduction

There are two register banks implemented on these devices. Each bank contains 256 addresses. The purpose of these register banks is to personalize and parameterize the on-chip resources as well as read and write data values.

The user selects between the two banks by setting the XIO bit in the CPU\_F Flag Register.

In some cases, the same register is available on either bank, for convenience. These registers (71h to 9fh) can be accessed from either bank.

Note: All register addresses not shown are reserved and should never be written. In addition, unused or reserved bits in any register should always be written to 0.

Figure 7: General Purpose I/O Pins

# 6.3 Port Global Select Registers

| Bit #      | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|

| POR        | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Read/Write | W       | W       | W       | W       | W       | W       | W       | W       |

| Bit Name   | GlobSel |

|            | [7]     | [6]     | [5]     | [4]     | [3]     | [2]     | [1]     | [0]     |

#### Table 30: Port Global Select Registers

Bit [7:0]: <u>Global Select [7:0]</u> When written determines whether a pin is connected to the Global Input Bus and Global Output Bus

0 = Not Connected

1 = Connected

Drive Mode xx = Global Select Register 0 = Standard CPU controlled port (Default) Drive Mode 1 0 (High Z) = Global Select Register 1 = Direct Drive of associated Global Input line Drive Mode 0 0, 0 1, 1 1 = Global Select Register 1 = Direct Receive from associated Global Output line

Port 0 Global Select Register (PRT0GS, Address = Bank 0, 02h) Port 1 Global Select Register (PRT1GS, Address = Bank 0, 06h) Port 2 Global Select Register (PRT2GS, Address = Bank 0, 0Ah) Port 3 Global Select Register (PRT3GS, Address = Bank 0, 0Eh) Port 4 Global Select Register (PRT4GS, Address = Bank 0, 12h) Port 5 Global Select Register (PRT5GS, Address = Bank 0, 16h) Note: If implemented, Port 5 is 4-bits wide

#### 6.3.1 Port Drive Mode 0 Registers

#### Table 31: Port Drive Mode 0 Registers

| Bit #      | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|

| POR        | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Read/Write | W       | W       | W       | W       | W       | W       | W       | W       |

| Bit Name   | DM0 [7] | DM0 [6] | DM0 [5] | DM0 [4] | DM0 [3] | DM0 [2] | DM0 [1] | DM0 [0] |

**Bit** [7:0]: <u>DM0 [7:0]</u> The two Drive Mode bits that control a particular port pin are treated as a pair and are decoded as follows:

| Port Data Register Bit 0 = Drive Mode 0 0 = 0 Resistive (Defau |

|----------------------------------------------------------------|

| Port Data Register Bit 0 = Drive Mode 0 1 = 0 Strong           |

| Port Data Register Bit 0 = Drive Mode 1 0 = High Z             |

| Port Data Register Bit 0 = Drive Mode 1 1 = 0 Strong           |

| Port Data Register Bit 1 = Drive Mode 0 0 = 1 Strong           |

| Port Data Register Bit 1 = Drive Mode 0 1 = 1 Strong           |

| Port Data Register Bit 1 = Drive Mode 1 0 = High Z             |

| Port Data Register Bit 1 = Drive Mode 1 1 = 1 Resistive        |

| ~                                                              |

Port 0 Drive Mode 0 Register (PRT0DM0, Address = Bank 1, 00h) Port 1 Drive Mode 0 Register (PRT1DM0, Address = Bank 1, 04h) Port 2 Drive Mode 0 Register (PRT2DM0, Address = Bank 1, 08h) Port 3 Drive Mode 0 Register (PRT3DM0, Address = Bank 1, 0Ch) Port 4 Drive Mode 0 Register (PRT4DM0, Address = Bank 1, 10h) Port 5 Drive Mode 0 Register (PRT5DM0, Address = Bank 1, 14h) **Note**: Port 5 is 4-bits wide

## 6.3.2 Port Drive Mode 1 Registers

| Table 32: | Port Drive Mode 1 Registers |

|-----------|-----------------------------|

|-----------|-----------------------------|

| Bit #                                                                       | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|-----------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| POR                                                                         | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Read/Write                                                                  | W       | W       | W       | W       | W       | W       | W       | W       |

| Bit Name                                                                    | DM1 [7] | DM1 [6] | DM1 [5] | DM1 [4] | DM1 [3] | DM1 [2] | DM1 [1] | DM1 [0] |

| Bit [7:0]: DM1 [7:0] See truth table for Port Drive Mode 0 Registers, above |         |         |         |         |         |         |         |         |

Port 0 Drive Mode 1 Register (PRT0DM1, Address = Bank 1, 01h) Port 1 Drive Mode 1 Register (PRT1DM1, Address = Bank 1, 05h) Port 2 Drive Mode 1 Register (PRT2DM1, Address = Bank 1, 09h) Port 3 Drive Mode 1 Register (PRT3DM1, Address = Bank 1, 0Dh) Port 4 Drive Mode 1 Register (PRT4DM1, Address = Bank 1, 11h) Port 5 Drive Mode 1 Register (PRT5DM1, Address = Bank 1, 15h) **Note**: Port 5 is 4-bits wide

### 6.3.3 Port Interrupt Control 0 Registers

#### Table 33: Port Interrupt Control 0 Registers

| Bit #      | 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0       |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|

| POR        | 0       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| Read/Write | W       | W       | W       | W       | W       | W       | W       | W       |

| Bit Name   | IC0 [7] | IC0 [6] | IC0 [5] | IC0 [4] | IC0 [3] | IC0 [2] | IC0 [1] | IC0 [0] |

Bit [7:0]: <u>IC0 [7:0]</u> The two Interrupt Control bits that control a particular port pin are treated as a pair and are decoded as follows:

IC1 [x], IC0 [x] = 0.0 = Disabled (Default)

IC1 [x], IC0 [x] = 0 1 = Falling Edge (-)

IC1 [x], IC0 [x] = 1.0 = Rising Edge(+)

IC1 [x], IC0 [x] = 1 1 = Change from Last Direct Read

Port 0 Interrupt Control 0 Register (PRT0IC0, Address = Bank 1, 02h) Port 1 Interrupt Control 0 Register (PRT1IC0, Address = Bank 1, 06h) Port 2 Interrupt Control 0 Register (PRT2IC0, Address = Bank 1, 0Ah) Port 3 Interrupt Control 0 Register (PRT3IC0, Address = Bank 1, 0Eh) Port 4 Interrupt Control 0 Register (PRT4IC0, Address = Bank 1, 12h) Port 5 Interrupt Control 0 Register (PRT5IC0, Address = Bank 1, 16h) **Note**: Port 5 is 4-bits wide

# 9.0 Digital PSoC Blocks

# 9.1 Introduction

PSoC blocks are user configurable system resources. On-chip digital PSoC blocks reduce the need for many MCU part types and external peripheral components. Digital PSoC blocks can be configured to provide a wide variety of peripheral functions. PSoC Designer Software Integrated Development Environment provides automated configuration of PSoC blocks by simply selecting the desired functions. PSoC Designer then generates the proper configuration information and can print a device data sheet unique to that configuration.

Digital PSoC blocks provide up to eight, 8-bit multipurpose timers/counters supporting multiple event timers, real-time clocks, Pulse Width Modulators (PWM), and CRCs. In addition to all PSoC block functions, communication PSoC blocks support full-duplex UARTs and SPI master or slave functions.

As shown in Figure 12:, there are a total of eight 8-bit digital PSoC blocks in this device family configured as a linear array. Four of these are the Digital Basic Type A blocks and four are the Digital Communications Type A blocks. Each of these digital PSoC blocks can be configured independently, or used in combination.

Each digital PSoC block has a unique Interrupt Vector and Interrupt Enable bit. Functions can be stopped or started with a user-accessible Enable bit.

The Timer/Counter/CRC/PRS/Deadband functions are available on the Digital Basic Type A blocks and also the Digital Communications Type A blocks. The UART and SPI communications functions are only available on the Digital Communications Type A blocks.

There are three configuration registers: the Function Register (DBA00FN-DCA07FN) to select the block function and mode, the Input Register (DBA00IN-DCA07IN) to select data input and clock selection, and the Output Register (DBA00OU-DCA07OU) to select and enable function outputs.

The three data registers are designated Data 0 (DBA00DR0-DCA07DR0), Data 1 (DBA00DR1-DCA07DR1), and Data 2 (DBA00DR2-DCA07DR2). The function of these registers and their bit mapping is

dependent on the overall block function selected by the user.

The one Control Register (DBA00CR0-DCA07CR0) is designated Control 0. The function of this register and its bit mapping is dependent on the overall block function selected by the user.

If the CPU frequency is 24 MHz and a PSoC timer/ counter of 24-bits or longer is operating at 48 MHz, a write to the block Control Register to enable it (for example, a call to Timer\_1\_Start) may not start the block properly. In the failure case, the first count will typically be indeterminate as the upper bytes fail to make the first count correctly. However, on the first terminal count, the correct period will be loaded and counted thereafter. Digital Communications Type A Block 05 Function Register Digital Communications Type A Block 06 Function Register Digital Communications Type A Block 07 Function Register (DCA05FN, Address = Bank 1, 34h) (DCA06FN, Address = Bank 1, 38h) (DCA07FN, Address = Bank 1, 3Ch)

# 9.2.2 Digital Basic Type A / Communications Type A Block xx Input Register

The Digital Basic Type A / Communications Type A Block xx Input Register (DBA00IN-DCA07IN) consists of 4 bits [3:0] to select the block input clock and 4 bits [7:4] to

select the primary data/enable input. The actual usage of the input data/enable is function dependent.

| Bit #                                        | 7                 | 6                | 5                      | 4            | 3                                 | 2                                        | 1          | 0         |

|----------------------------------------------|-------------------|------------------|------------------------|--------------|-----------------------------------|------------------------------------------|------------|-----------|

| POR                                          | 0                 | 0                | 0                      | 0            | 0                                 | 0                                        | 0          | 0         |

| Read/Write                                   | RW                | RW               | RW                     | RW           | RW                                | RW                                       | RW         | RW        |

| Bit Name                                     | Data [3]          | Data [2]         | Data [1]               | Data [0]     | Clock [3]                         | Clock [2]                                | Clock [1]  | Clock [0] |

|                                              |                   |                  | -14                    |              |                                   |                                          |            |           |

| Bit [7:4]: <u>Data  </u><br>0 0 0 0 = Data = |                   | able Source S    | elect                  |              |                                   |                                          |            |           |

| 0 0 0 1 = Data =                             |                   |                  |                        |              |                                   |                                          |            |           |

| 0 0 1 0 = Digital                            | Block 03          |                  |                        |              |                                   |                                          |            |           |

| 0 0 1 1 = Chain                              |                   |                  |                        |              |                                   |                                          |            |           |

| 0.100 = Analog                               |                   |                  |                        |              |                                   |                                          |            |           |

| 101 = Analog                                 |                   |                  |                        |              |                                   |                                          |            |           |

| 0 1 1 0 = Analog<br>0 1 1 1 = Analog         | 0                 | •                |                        |              |                                   |                                          |            |           |

|                                              | •                 | •                | ; 00 to 03) <b>o</b> i | r Global Out | put[4] (for Did                   | gital Blocks 04 to                       | 07)        |           |

|                                              |                   |                  |                        |              |                                   | gital Blocks 04 to                       |            |           |

| 1 0 1 0 = Globa                              | I Output[2] (for  | Digital Blocks   | 00 to 03) o            | r Global Out | put[6] (for Dig                   | gital Blocks 04 to                       | 07)        |           |

|                                              |                   | 0                | ,                      |              |                                   | gital Blocks 04 to                       | ,          |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)<br>Blocks 04 to 07)     |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              | 1 - 1 - 1 ( -     | 3                | , .                    |              | . I ( <sup>1</sup> J <sup>1</sup> | · · · · · · · ,                          |            |           |

| Bit [3:0]: <u>Clock</u>                      |                   | Source Select    |                        |              |                                   |                                          |            |           |

| $0 \ 0 \ 0 \ 0 = \text{Clock}$               |                   |                  |                        |              |                                   |                                          |            |           |

|                                              |                   |                  | 6 00 to 03) <b>o</b> i | r Global Out | put[0] (for Dig                   | gital Blocks 04 to                       | 07)        |           |

| 0 0 1 0 = Digital<br>0 0 1 1 = Previo        |                   |                  | arv Output)            |              |                                   |                                          |            |           |

| 0 1 0 0 = 48M                                | Nus Digital 1 Oc  |                  | ary Output)            |              |                                   |                                          |            |           |

| 0 1 0 1 = 24V1                               |                   |                  |                        |              |                                   |                                          |            |           |

| 0 1 1 0 = 24V2                               |                   |                  |                        |              |                                   |                                          |            |           |

| 0 1 1 1 = 32k                                |                   |                  |                        |              |                                   |                                          |            |           |

|                                              |                   | 0                | ,                      |              |                                   | gital Blocks 04 to                       | ,          |           |

|                                              |                   | 0                | ,                      |              |                                   | gital Blocks 04 to<br>gital Blocks 04 to | ,          |           |

|                                              |                   |                  |                        |              |                                   | gital Blocks 04 to                       |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

| 1 1 1 1 = Globa                              | I Input[3] (for E | Digital Blocks ( | 00 to 03) <b>or</b> 0  | Global Input | [7] (for Digital                  | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   |                                          |            |           |

| igital Basic Ty                              | ne A Block (      | 00 Input Red     | ister                  |              | (DBA00IN                          | I, Address = Ba                          | ank 1 21h) |           |

| Digital Basic Type A Block 00 Input Register          | (DBA00IN, Address = Bank 1, 21h) |

|-------------------------------------------------------|----------------------------------|

| Digital Basic Type A Block 01 Input Register          | (DBA01IN, Address = Bank 1, 25h) |

| Digital Basic Type A Block 02 Input Register          | (DBA02IN, Address = Bank 1, 29h) |

| Digital Basic Type A Block 03 Input Register          | (DBA03IN, Address = Bank 1, 2Dh) |

| Digital Communications Type A Block 04 Input Register | (DCA04IN, Address = Bank 1, 31h) |

| Digital Communications Type A Block 05 Input Register | (DCA05IN, Address = Bank 1, 35h) |

### 10.7.2 Registers

### 10.7.2.1 Analog Continuous Time Block xx Control 0 Register

The RTopMux and RBotMux bits control the connection of the two ends of the resistor string. The RTopMux bit controls the top end of the resistor string, which can either be connected to Vcc or to the op-amp output. The RBotMux bits control the connection of the bottom end of the resistor string. The RTapMux bits control the center tap of the resistor string. Note that only relative weighting of units is given in the table.

The Gain and Loss columns correspond to the gain or loss obtained if the RTopMux and Gain bits are set so that the overall amplifier provides gain or loss.

The Gain bit controls whether the resistor string is connected around the op-amp as for gain (center tap to

# 10.7.2.2 Analog Continuous Time Block xx Control 1 Register

The PMux bits control the multiplexing of inputs to the non-inverting input of the op-amp. There are physically only 7 inputs.

The 8<sup>th</sup> code (111) will leave the input floating. This is not desirable, and should be avoided.

The NMux bits control the multiplexing of inputs to the inverting input of the op-amp. There are physically only 7 inputs.

CompBus controls a tri-state buffer that drives the comparator logic. If no PSoC block in the analog column is driving the comparator bus, it will be driven low externally to the blocks.

AnalogBus controls the analog output bus. A CMOS switch connects the op-amp output to the analog bus.

| Table 67: | Analog Continuous Time Block xx Control 1 Register |  |

|-----------|----------------------------------------------------|--|

|-----------|----------------------------------------------------|--|

| Bit #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                     | 6                                                                            | 5                                                                                     | 4                                                                                     | 3     | 2     | 1     | 0     |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

| POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                     | 0                                                                            | 0                                                                                     | 0                                                                                     | 0     | 0     | 0     | 0     |  |  |  |

| Read/<br>Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RW                                                                                    | RW                                                                           | RW                                                                                    | RW                                                                                    | RW    | RW    | RW    | RW    |  |  |  |

| Bit Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AnalogBus                                                                             | CompBus                                                                      | NMux2                                                                                 | NMux1                                                                                 | NMux0 | PMux2 | PMux1 | PMux0 |  |  |  |

| <ul> <li>Bit 7: <u>AnalogBus</u> Enable output to the analog bus</li> <li>0 = Disable analog bus driven by this block</li> <li>1 = Enable analog bus driven by this block</li> <li>Bit 6: <u>CompBus</u> Enable output to the comparator bus</li> <li>0 = Disable comparator bus driven by this block</li> <li>1 = Enable comparator bus driven by this block</li> <li>1 = Enable comparator bus driven by this block</li> <li>Bit [5:3]: NMux [2:0] Encoding for negative input select</li> </ul> |                                                                                       |                                                                              |                                                                                       |                                                                                       |       |       |       |       |  |  |  |

| ыт [э:э]. м                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                       |                                                                              |                                                                                       |                                                                                       |       |       |       |       |  |  |  |

| $0 \ 0 \ 1 = \\ 0 \ 1 \ 0 = \\ 0 \ 1 \ 1 = \\ 1 \ 0 \ 0^{1} = \\ 1 \ 0 \ 1 = \\ 1 \ 0 \ 1 = \\ 1 \ 0 \ 1 = \\ 1 \ 0 = $                                                                                                                                                                                                                                                                                                                                                                            | ACA00<br>ACA01<br>AGND<br>REFLO<br>REFHI<br>ACA00<br>ASA10<br>ASB11<br>Reserved       | ACA00<br>AGND<br>REFLO<br>REFHI<br>ACA01<br>ASB11<br>ASA10<br>Reserved       | ACA02<br>ACA03<br>AGND<br>REFLO<br>REFHI<br>ACA02<br>ASA12<br>ASB13<br>Reserved       | ACA03<br>ACA02<br>AGND<br>REFLO<br>REFHI<br>ACA03<br>ASB13<br>ASA12<br>Reserved       |       |       |       |       |  |  |  |

| Bit [2:0]: PM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Mux [2:0] End                                                                         | coding for pos                                                               | sitive input se                                                                       | lect                                                                                  |       |       |       |       |  |  |  |

| 0 0 1 =<br>0 1 0 =<br>0 1 1 =<br>1 0 0 =<br>1 0 1 =<br>1 1 0 =                                                                                                                                                                                                                                                                                                                                                                                                                                     | ACA00<br>REFLO<br>Port Inputs<br>ACA01<br>AGND<br>ASA10<br>ASB11<br>ABUS0<br>Reserved | ACA02<br>Port Inputs<br>ACA00<br>AGND<br>ASB11<br>ASA10<br>ABUS1<br>Reserved | ACA02<br>ACA01<br>Port Inputs<br>ACA03<br>AGND<br>ASA12<br>ASB13<br>ABUS2<br>Reserved | ACA03<br>REFLO<br>Port Inputs<br>ACA02<br>AGND<br>ASB13<br>ASA12<br>ABUS3<br>Reserved |       |       |       |       |  |  |  |

1. This in fact is the feedback input of the MUX.

Analog Continuous Time Block 00 Control 1 Register (ACA00CR1, Address = Bank 0/1, 72h) Analog Continuous Time Block 01 Control 1 Register (ACA01CR1, Address = Bank 0/1, 76h) Analog Continuous Time Block 02 Control 1 Register (ACA02CR1, Address = Bank 0/1, 7Ah) Analog Continuous Time Block 03 Control 1 Register (ACA03CR1, Address = Bank 0/1, 7Eh)

## 10.8.2 Local Interconnect

# 10.8.2.1 AMux

Figure 23: AMux Connections

| Bit #          | 7         | 6       | 5        | 4       | 3       | 2       | 1       | 0       |

|----------------|-----------|---------|----------|---------|---------|---------|---------|---------|

| POR            | 0         | 0       | 0        | 0       | 0       | 0       | 0       | 0       |

| Read/<br>Write | RW        | RW      | RW       | RW      | RW      | RW      | RW      | RW      |

| Bit Name       | AnalogBus | CompBus | AutoZero | CCap[4] | CCap[3] | CCap[2] | CCap[1] | CCap[0] |

| Table 71: | Analog Switch Cap Type A Block xx Control 2 Register |

|-----------|------------------------------------------------------|

|-----------|------------------------------------------------------|

Bit 7: AnalogBus Enable output to the analog bus

0 = Disable output to analog column bus

1 = Enable output to analog column bus

(The output on the analog column bus is affected by the state of the ClockPhase bit in Control 0 Register (ASA10CR0, ASA12CR0, ASA21CR0, ASA23CR0). If AnalogBus is set to 0, the output to the analog column bus is tri-stated. If AnalogBus is set to 1, the signal that is output to the analog column bus is selected by the ClockPhase bit. If the ClockPhase bit is 0, the block output is gated by sampling clock on last part of PHI2. If the ClockPhase bit is 1, the block output continuously drives the analog column bus.)

Bit 6: <u>CompBus</u> Enable output to the comparator bus

0 = Disable output to comparator bus

1 = Enable output to comparator bus

Bit 5: AutoZero Bit for controlling gated switches

0 = Shorting switch is not active. Input cap branches shorted to op-amp input

1 = Shorting switch is enabled during internal PHI1. Input cap branches shorted to analog ground during internal PHI1 and to op-amp input during internal PHI2.

Bit [4:0]: CCap [4:0] Binary encoding for 32 possible capacitor sizes for C Capacitor:

| 0 0 0 0 0 = 0 Capacitor units in array $1 0 0 0 0 = 10$ Capacitor units in array $0 0 0 0 1 = 1$ Capacitor units in array $1 0 0 0 1 = 17$ Capacitor units in array $0 0 0 1 0 = 2$ Capacitor units in array $1 0 0 1 0 = 18$ Capacitor units in array $0 0 0 1 1 = 3$ Capacitor units in array $1 0 0 1 0 = 18$ Capacitor units in array $0 0 1 0 = 4$ Capacitor units in array $1 0 0 1 0 = 20$ Capacitor units in array $0 0 1 0 = 4$ Capacitor units in array $1 0 1 0 0 = 20$ Capacitor units in array $0 0 1 0 = 4$ Capacitor units in array $1 0 1 0 0 = 20$ Capacitor units in array $0 0 1 0 = 4$ Capacitor units in array $1 0 1 0 1 = 21$ Capacitor units in array $0 0 1 1 0 = 6$ Capacitor units in array $1 0 1 1 0 = 22$ Capacitor units in array $0 0 1 1 1 = 7$ Capacitor units in array $1 0 1 1 1 = 23$ Capacitor units in array $0 1 0 0 = 8$ Capacitor units in array $1 0 0 0 = 24$ Capacitor units in array $0 1 0 0 = 8$ Capacitor units in array $1 0 0 0 = 24$ Capacitor units in array $0 1 0 0 = 8$ Capacitor units in array $1 0 0 0 = 24$ Capacitor units in array $0 1 0 0 = 8$ Capacitor units in array $1 0 0 0 = 24$ Capacitor units in array $0 1 0 1 = 9$ Capacitor units in array $1 1 0 0 = 28$ Capacitor units in array $0 1 0 1 = 13$ Capacitor units in array $1 1 1 0 1 = 29$ Capacitor units in array $0 1 1 1 0 = 14$ Capacitor units in array $1 1 1 0 1 = 30$ Capacitor units in array $0 1 1 1 1 = 15$ Capacitor units in array $1 1 1 1 = 31$ Capacitor units in array $0 1 1 1 1 = 15$ Capacitor units in array $1 1 1 1 = 31$ Capacitor units in array <th><math>0\ 0\ 0\ 0\ 0 = 0</math> Capacitor units in array</th> <th>10000 = 16 Capacitor units in array</th> | $0\ 0\ 0\ 0\ 0 = 0$ Capacitor units in array | 10000 = 16 Capacitor units in array           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|

| $0 \ 0 \ 0 \ 1 \ 0 = 2$ Capacitor units in array $1 \ 0 \ 0 \ 1 \ 0 = 18$ Capacitor units in array $0 \ 0 \ 1 \ 1 = 3$ Capacitor units in array $1 \ 0 \ 0 \ 1 \ 1 = 19$ Capacitor units in array $0 \ 0 \ 1 \ 0 = 4$ Capacitor units in array $1 \ 0 \ 0 \ 1 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 = 4$ Capacitor units in array $1 \ 0 \ 1 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 = 4$ Capacitor units in array $1 \ 0 \ 1 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 = 5$ Capacitor units in array $1 \ 0 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 = 6$ Capacitor units in array $1 \ 0 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 = 7$ Capacitor units in array $1 \ 0 \ 1 \ 1 = 23$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 0 = 26$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 11$ Capacitor units in array $1 \ 0 \ 0 = 26$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 12$ Capacitor units in array $1 \ 1 \ 0 \ 1 = 27$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 13$ Capacitor units in array $1 \ 1 \ 0 \ 0 = 28$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 14$ Capacitor units in array $1 \ 1 \ 0 \ 0 = 28$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ $                                                                                                                                                                                                                                                                        |                                              | , , ,                                         |

| $0 \ 0 \ 0 \ 1 \ 1 = 3$ Capacitor units in array $1 \ 0 \ 0 \ 1 \ 1 = 19$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 4$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 5$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 5$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 5$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 0 = 20$ Capacitor units in array $0 \ 1 \ 0 \ 1 \ 0 = 6$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ 0 = 6$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                              |                                               |

| 0 0 1 0 0 = 4 Capacitor units in array $1 0 1 0 0 = 20$ Capacitor units in array $0 0 1 0 1 = 5$ Capacitor units in array $1 0 1 0 1 = 21$ Capacitor units in array $0 0 1 1 0 = 6$ Capacitor units in array $1 0 1 0 1 = 21$ Capacitor units in array $0 0 1 1 0 = 6$ Capacitor units in array $1 0 1 1 0 = 22$ Capacitor units in array $0 0 1 1 1 = 7$ Capacitor units in array $1 0 1 1 1 = 23$ Capacitor units in array $0 0 1 0 0 = 8$ Capacitor units in array $1 0 0 0 = 24$ Capacitor units in array $0 1 0 0 0 = 8$ Capacitor units in array $1 1 0 0 0 = 24$ Capacitor units in array $0 1 0 0 1 = 9$ Capacitor units in array $1 1 0 0 1 = 25$ Capacitor units in array $0 1 0 1 0 = 10$ Capacitor units in array $1 1 0 1 0 = 26$ Capacitor units in array $0 1 0 1 1 = 11$ Capacitor units in array $1 1 0 1 0 = 28$ Capacitor units in array $0 1 1 0 0 = 12$ Capacitor units in array $1 1 1 0 0 = 28$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 1 0 1 = 29$ Capacitor units in array $0 1 1 0 = 14$ Capacitor units in array $1 1 1 0 = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $0\ 0\ 0\ 1\ 0 = 2$ Capacitor units in array | 1 0 0 1 0 = 18 Capacitor units in array       |

| $0 \ 0 \ 1 \ 0 \ 1 = 5$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 1 = 21$ Capacitor units in array $0 \ 0 \ 1 \ 1 \ 0 = 6$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 \ 1 = 7$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 \ 1 = 7$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 9$ Capacitor units in array $1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $0\ 0\ 0\ 1\ 1 = 3$ Capacitor units in array | $1\ 0\ 0\ 1\ 1 = 19$ Capacitor units in array |

| $0 \ 0 \ 1 \ 1 \ 0 = 6$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 \ 1 = 7$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 1 \ 0 = 7$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 0 = 22$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 0 = 9$ Capacitor units in array $1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 1 = 9$ Capacitor units in array $1 \ 0 \ 0 \ 1 = 25$ Capacitor units in array $0 \ 1 \ 0 \ 1 \ 0 = 10$ Capacitor units in array $1 \ 0 \ 0 \ 1 = 26$ Capacitor units in array $0 \ 1 \ 0 \ 1 \ 0 = 12$ Capacitor units in array $1 \ 0 \ 1 \ 0 \ 0 \ 0 \ 28$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 2$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ 0 \ 28$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 1 \ 2$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ 28$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 1 \ 2$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ 28$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ 1 \ 0 \ 0 \ 1 \ 20$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ 28$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ 1 \ 1 \ 0 \ 0 \ 1 \ 0 \ 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $0\ 0\ 1\ 0\ 0 = 4$ Capacitor units in array | 1 0 1 0 0 = 20 Capacitor units in array       |

| $0 \ 0 \ 1 \ 1 \ 1 = 7$ Capacitor units in array $1 \ 0 \ 1 \ 1 \ 1 = 23$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 8$ Capacitor units in array $1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 0 = 9$ Capacitor units in array $1 \ 0 \ 0 \ 0 = 24$ Capacitor units in array $0 \ 1 \ 0 \ 1 = 9$ Capacitor units in array $1 \ 0 \ 0 \ 1 = 25$ Capacitor units in array $0 \ 1 \ 0 \ 1 \ 0 = 10$ Capacitor units in array $1 \ 0 \ 0 \ 1 = 25$ Capacitor units in array $0 \ 1 \ 0 \ 1 \ 0 = 10$ Capacitor units in array $1 \ 0 \ 1 \ 0 = 26$ Capacitor units in array $0 \ 1 \ 0 \ 1 \ 0 = 12$ Capacitor units in array $1 \ 1 \ 0 \ 1 \ 0 \ 0 \ 28$ Capacitor units in array $0 \ 1 \ 0 \ 0 \ = 12$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ = 28$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ = 13$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ = 20$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ = 14$ Capacitor units in array $1 \ 1 \ 0 \ 0 \ = 20$ Capacitor units in array $0 \ 1 \ 1 \ 0 \ = 14$ Capacitor units in array $1 \ 1 \ 0 \ = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $0\ 0\ 1\ 0\ 1 = 5$ Capacitor units in array | 1 0 1 0 1 = 21 Capacitor units in array       |

| 0 1 0 0 0 = 8 Capacitor units in array $1 1 0 0 0 = 24$ Capacitor units in array $0 1 0 0 1 = 9$ Capacitor units in array $1 0 0 1 = 25$ Capacitor units in array $0 1 0 1 0 = 10$ Capacitor units in array $1 0 0 1 = 25$ Capacitor units in array $0 1 0 1 0 = 10$ Capacitor units in array $1 1 0 1 0 = 26$ Capacitor units in array $0 1 0 1 1 = 11$ Capacitor units in array $1 1 0 1 1 = 27$ Capacitor units in array $0 1 1 0 0 = 12$ Capacitor units in array $1 1 0 0 = 28$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 1 0 1 = 29$ Capacitor units in array $0 1 1 1 0 = 14$ Capacitor units in array $1 1 1 0 = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $0\ 0\ 1\ 1\ 0 = 6$ Capacitor units in array | 1 0 1 1 0 = 22 Capacitor units in array       |

| 0 1 0 0 1 = 9 Capacitor units in array $1 1 0 0 1 = 25$ Capacitor units in array $0 1 0 1 0 = 10$ Capacitor units in array $1 1 0 1 0 = 26$ Capacitor units in array $0 1 0 1 1 = 11$ Capacitor units in array $1 1 0 1 0 = 26$ Capacitor units in array $0 1 1 0 0 = 12$ Capacitor units in array $1 1 0 1 1 = 27$ Capacitor units in array $0 1 1 0 0 = 12$ Capacitor units in array $1 1 0 0 = 28$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 1 0 1 = 29$ Capacitor units in array $0 1 1 1 0 = 14$ Capacitor units in array $1 1 1 0 = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 0 1 1 1 = 7 Capacitor units in array       | 1 0 1 1 1 = 23 Capacitor units in array       |

| 0 1 0 1 0 = 10 Capacitor units in array $1 1 0 1 0 = 26$ Capacitor units in array $0 1 0 1 1 = 11$ Capacitor units in array $1 1 0 1 1 = 27$ Capacitor units in array $0 1 1 0 0 = 12$ Capacitor units in array $1 1 0 1 1 = 27$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 0 0 = 28$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 0 1 = 29$ Capacitor units in array $0 1 1 1 0 = 14$ Capacitor units in array $1 1 1 0 = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 1 0 0 0 = 8 Capacitor units in array       | 1 1 0 0 0 = 24 Capacitor units in array       |

| 0 1 0 1 1 = 11 Capacitor units in array $1 1 0 1 1 = 27$ Capacitor units in array $0 1 1 0 0 = 12$ Capacitor units in array $1 1 0 1 0 = 28$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 1 0 1 = 29$ Capacitor units in array $0 1 1 0 = 14$ Capacitor units in array $1 1 1 0 = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 1 0 0 1 = 9 Capacitor units in array       | 1 1 0 0 1 = 25 Capacitor units in array       |

| 0 1 1 0 0 = 12 Capacitor units in array $1 1 1 0 0 = 28$ Capacitor units in array $0 1 1 0 1 = 13$ Capacitor units in array $1 1 1 0 1 = 29$ Capacitor units in array $0 1 1 1 0 = 14$ Capacitor units in array $1 1 1 0 = 30$ Capacitor units in array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 1 0 1 0 = 10 Capacitor units in array      | 1 1 0 1 0 = 26 Capacitor units in array       |