Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 24MHz                                                                      |

| Connectivity               | SPI, UART/USART                                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                 |

| Data Converters            | A/D 1x8b, 1x11b, 1x12b; D/A 1x9b                                           |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

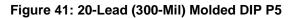

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c26443-24sxi |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 40: Interrupt Visitor Deviator                                                | 40  |

|-------------------------------------------------------------------------------------|-----|

| Table 46: Interrupt Vector Register                                                 |     |

| Table 47: Digital Basic Type A/ Communications Type A Block xx Function Register    |     |

| Table 48: Digital Basic Type A / Communications Type A Block xx Input Register      |     |

| Table 49: Digital Function Data Input Definitions                                   |     |

| Table 50: Digital Basic Type A / Communications Type A Block xx Output Register     |     |

| Table 51: Digital Function Outputs                                                  |     |

| Table 52: Digital Basic Type A / Communications Type A Block xx Data Register 0,1,2 |     |

| Table 53: R/W Variations per User Module Selection                                  |     |

| Table 54: Digital Basic Type A / Communications Type A Block xx Control Register 0  |     |

| Table 55: Digital Basic Type A/Communications Type A Block xx Control Register 0    |     |

| Table 56: Digital Communications Type A Block xx Control Register 0                 |     |

| Table 57: Digital Communications Type A Block xx Control Register 0                 |     |

| Table 58: Digital Communications Type A Block xx Control Register 0                 |     |

| Table 59: Global Input Assignments                                                  |     |

| Table 60: Global Output Assignments                                                 |     |

| Table 61: Analog System Clocking Signals                                            |     |

| Table 62: AGND, RefHI, RefLO Operating Parameters                                   |     |

| Table 63: Analog Reference Control Register                                         |     |

| Table 64: Analog Column Clock Select Register                                       |     |

| Table 65: Analog Clock Select Register                                              |     |

| Table 66: Analog Continuous Time Block xx Control 0 Register                        |     |

| Table 67: Analog Continuous Time Block xx Control 1 Register                        |     |

| Table 68: Analog Continuous Time Type A Block xx Control 2 Register                 |     |

| Table 69: Analog Switch Cap Type A Block xx Control 0 Register                      | 88  |

| Table 70: Analog Switch Cap Type A Block xx Control 1 Register                      | 90  |

| Table 71: Analog Switch Cap Type A Block xx Control 2 Register                      | 92  |

| Table 72: Analog Switch Cap Type A Block xx Control 3 Register                      | 93  |

| Table 73: Analog Switch Cap Type B Block xx Control 0 Register                      | 95  |

| Table 74: Analog Switch Cap Type B Block xx Control 1 Register                      | 97  |

| Table 75: Analog Switch Cap Type B Block xx Control 2 Register                      | 99  |

| Table 76: Analog Switch Cap Type B Block xx Control 3 Register                      |     |

| Table 77: Analog Comparator Control Register                                        |     |

| Table 78: Analog Frequency Relationships                                            |     |

| Table 79: Analog Synchronization Control Register                                   |     |

| Table 80: Analog Input Select Register                                              |     |

| Table 81: Analog Output Buffer Control Register                                     |     |

| Table 82: Analog Modulator Control Register                                         |     |

| Table 83: Multiply Input X Register                                                 |     |

| Table 84: Multiply Input Y Register                                                 |     |

| Table 85: Multiply Result High Register                                             |     |

| Table 86: Multiply Result Low Register                                              |     |

| Table 87: Accumulator Result 1 / Multiply/Accumulator Input X Register              |     |

| Table 88: Accumulator Result 0 / Multiply/Accumulator Input Y Register              |     |

| Table 89: Accumulator Result 3 / Multiply/Accumulator Clear 0 Register              |     |

| Table 90: Accumulator Result 2 / Multiply/Accumulator Clear 1 Register              |     |

| Table 91: Decimator/Incremental Control Register                                    |     |

| Table 92: Decimator Data High Register                                              |     |

| Table 93: Decimator Data Low Register                                               |     |

| Table 94: Processor Status and Control Register                                     | 114 |

| Table 95: Reset WDT Register                                                        |     |

| Table 96: Voltage Monitor Control Register                                          |     |

| Table 97: Bandgap Trim Register                                                     |     |

| Table 98: CY8C25122, CY8C26233, CY8C26443, CY8C26643 (256 Bytes of SRAM)            |     |

| Table 99: Table Read for Supervisory Call Functions                                 |     |

| rable ve. rable read for oupervisory can r unchoria                                 | 122 |

# 1.2 Pin-out Descriptions

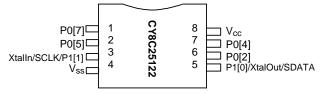

#### Table 2:Pin-out 8 Pin

| Name  | I/O   | Pin | Description                     |

|-------|-------|-----|---------------------------------|

| P0[7] | I/O   | 1   | Port 0[7] (Analog Input)        |

| P0[5] | I/O   | 2   | Port 0[5] (Analog Input/Output) |

| P1[1] | I/O   | 3   | Port 1[1] / Xtalln / SCLK       |

| Vss   | Power | 4   | Ground                          |

| P1[0] | I/O   | 5   | Port 1[0] / XtalOut / SDATA     |

| P0[2] | I/O   | 6   | Port 0[2] (Analog Input/Output) |

| P0[4] | I/O   | 7   | Port 0[4] (Analog Input/Output) |

| Vcc   | Power | 8   | Supply Voltage                  |

Figure 2: CY8C25122

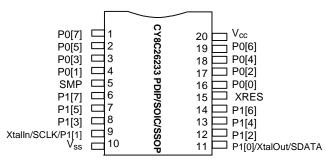

| Name  | I/O                                | Pin | Description                     |  |  |

|-------|------------------------------------|-----|---------------------------------|--|--|

| P0[7] | I/O                                | 1   | Port 0[7] (Analog Input)        |  |  |

| P0[5] | [5] I/O 2 Port 0[5] (Analog Input/ |     |                                 |  |  |

| P0[3] | I/O                                | 3   | Port 0[3] (Analog Input/Output) |  |  |

| P0[1] | I/O                                | 4   | Port 0[1] (Analog Input)        |  |  |

| SMP   | 0                                  | 5   | Switch Mode Pump                |  |  |

| P1[7] | I/O                                | 6   | Port 1[7]                       |  |  |

| P1[5] | I/O                                | 7   | Port 1[5]                       |  |  |

| P1[3] | 3] I/O 8 Port 1[3]                 |     |                                 |  |  |

| P1[1] | P1[1] I/O                          |     | Port 1[1] / Xtalln / SCLK       |  |  |

| Vss   | Power                              | 10  | Ground                          |  |  |

| P1[0] | I/O                                | 11  | Port 1[0] / XtalOut / SDATA     |  |  |

| P1[2] | I/O                                | 12  | Port 1[2]                       |  |  |

| P1[4] | I/O                                | 13  | Port 1[4]                       |  |  |

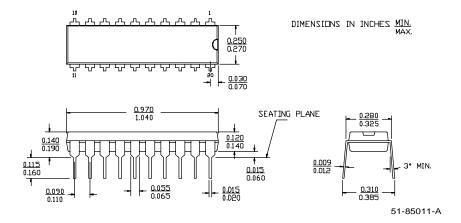

Pin-out 20 Pin

Table 3:

P1[6]

XRES

P0[0]

P0[2]

P0[4]

P0[6]

Vcc

I/O

I/O

I/O

I/O

I/O

Power

L

14

15

16

17

18

19

20

Port 1[6]

**External Reset**

Supply Voltage

Port 0[0] (Analog Input)

Port 0[6] (Analog Input)

Port 0[2] (Analog Input/Output)

Port 0[4] (Analog Input/Output)

Figure 3: CY8C26233

#### Examples:

| ADD | A, | 7 | ;In this case, the immediate<br>;value of 7 is added with the<br>;Accumulator, and the result<br>;is placed in the<br>;Accumulator.        |

|-----|----|---|--------------------------------------------------------------------------------------------------------------------------------------------|

| MOV | X, | 8 | ;In this case, the immediate<br>;value of 8 is moved to the X<br>;register.                                                                |

| AND | F, | 9 | ;In this case, the immediate<br>;value of 9 is logically<br>;ANDed with the F register<br>;and the result is placed in<br>;the F register. |

#### 2.3.2 Source Direct

The result of an instruction using this addressing mode is placed in either the A register or the X register, which is specified as part of the instruction opcode. Operand 1 is an address that points to a location in either the RAM memory space or the register space that is the source for the instruction. Arithmetic instructions require two sources, the second source is the A register or X register specified in the opcode. Instructions using this addressing mode are two bytes in length.

#### Table 14: Source Direct

| Opcode      | Operand 1      |

|-------------|----------------|

| Instruction | Source Address |

Examples:

| ADD | Α, | [7]     | ;In this case, the<br>;value in the RAM<br>;memory location at<br>;address 7 is added<br>;with the Accumulator,<br>;and the result is<br>;placed in the<br>;Accumulator. |

|-----|----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV | X, | REG [8] | ;In this case, the<br>;value in the register<br>;space at address 8 is<br>;moved to the X<br>;register.                                                                  |

#### 2.3.3 Source Indexed

The result of an instruction using this addressing mode is placed in either the A register or the X register, which is specified as part of the instruction opcode. Operand 1 is added to the X register forming an address that points to a location in either the RAM memory space or the register space that is the source for the instruction. Arithmetic instructions require two sources, the second source is the A register or X register specified in the opcode. Instructions using this addressing mode are two bytes.

#### Table 15: Source Indexed

| Opcode      | Operand 1    |

|-------------|--------------|

| Instruction | Source Index |

Examples:

| ADD | A, | [X+7]     | ;In this case, the<br>;value in the memory<br>;location at address<br>;X + 7 is added with<br>;the Accumulator, and<br>;the result is placed<br>;in the Accumulator. |

|-----|----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV | Х, | REG [X+8] | ;In this case, the<br>;value in the<br>;register space at<br>;address X + 8 is<br>;moved to the X<br>;register.                                                      |

#### 2.3.4 Destination Direct

The result of an instruction using this addressing mode is placed within either the RAM memory space or the register space. Operand 1 is an address that points to the location of the result. The source for the instruction is either the A register or the X register, which is specified as part of the instruction opcode. Arithmetic instructions require two sources, the second source is the location specified by Operand 1. Instructions using this addressing mode are two bytes in length.

| Opcode      | Operand 1           |

|-------------|---------------------|

| Instruction | Destination Address |

# 4.2 Register Bank 0 Map

### Table 26: Bank 0

| Register<br>Name     | Address    | Data Sheet<br>Page | Access  | Register<br>Name     | Address     | Data Sheet<br>Page | Access   | Register<br>Name     | Address    | Data Sheet<br>Page | Access   | Register<br>Name               | Address    | Data Sheet<br>Page | Access   |

|----------------------|------------|--------------------|---------|----------------------|-------------|--------------------|----------|----------------------|------------|--------------------|----------|--------------------------------|------------|--------------------|----------|

|                      |            |                    | -       |                      |             | et                 |          |                      | -          |                    | RW       | 7                              | C0h        | et                 |          |

| PRT0DR<br>PRT0IE     | 00h<br>01h | 31<br>31           | RW<br>W |                      | 40h<br>41h  |                    |          | ASA10CR0<br>ASA10CR1 | 81h        | 88<br>90           | RW       |                                | C0n<br>C1h |                    |          |

| PRTOGS               | 02h        | 32                 | Ŵ       |                      | 42h         |                    |          | ASA10CR2             | 82h        | 92                 | RW       |                                | C2h        |                    |          |

| Reserved             | 03h        |                    |         |                      | 43h         |                    |          | ASA10CR3             |            | 93                 | RW       |                                | C3h        |                    |          |

| PRT1DR               | 04h        | 31                 | RW      |                      | 44h         |                    |          |                      | 84h        | 95                 | RW       |                                | C4h        |                    |          |

| PRT1IE<br>PRT1GS     | 05h<br>06h | 31<br>32           | W<br>W  |                      | 45h<br>46h  |                    |          | ASB11CR1<br>ASB11CR2 | 85h<br>86h | 97<br>99           | RW<br>RW |                                | C5h<br>C6h |                    |          |

|                      | 07h        | 32                 | VV      |                      | 4011<br>47h |                    |          |                      | 87h        | 100                | RW       |                                | Con<br>C7h |                    |          |

| PRT2DR               | 08h        | 31                 | RW      |                      | 48h         |                    |          |                      | 88h        | 88                 | RW       |                                | C8h        |                    |          |

| PRT2IE               | 09h        | 31                 | W       |                      | 49h         |                    |          |                      | 89h        | 90                 | RW       |                                | C9h        |                    |          |

| PRT2GS               | 0Ah        | 32                 | W       |                      | 4Ah         |                    |          | ASA12CR2             | 8Ah        | 92                 | RW       |                                | CAh        |                    |          |

|                      | 0Bh<br>0Ch | 21                 | RW      |                      | 4Bh<br>4Ch  |                    |          |                      | 8Bh<br>8Ch | 93<br>95           | RW<br>RW |                                | CBh<br>CCh |                    |          |

| PRT3IE               | 0Dh        |                    | W       |                      | 40h         |                    |          |                      | 8Dh        | 95<br>97           | RW       |                                | CDh        |                    |          |

| PRT3GS               | 0Eh        |                    | Ŵ       | ম                    | 4Eh         |                    |          | ASB13CR2             |            | 99                 | RW       | 7                              | CEh        |                    |          |

|                      | 0Fh        | _                  |         | Reserved             | 4Fh         |                    |          | ASB13CR3             |            | 100                | RW       | Reserved                       | CFh        |                    |          |

| PRT4DR               | 10h        | 31                 | RW      | erv.                 | 50h         |                    |          | ASB20CR0             |            | 95                 | RW       | erv.                           | D0h        |                    |          |

| PRT4IE               | 11h        | 31                 | W       | ed                   | 51h         |                    |          | ASB20CR1             | 91h        | 97                 | RW       | e d                            | D1h        |                    |          |

| PRT4GS<br>Reserved   | 12h<br>13h | 32                 | W       |                      | 52h<br>53h  |                    |          | ASB20CR2<br>ASB20CR3 | 92h<br>03h | 99<br>100          | RW<br>RW |                                | D2h<br>D3h |                    |          |

| PRT5DR               | 14h        | 31                 | RW      |                      | 54h         |                    |          |                      | 94h        | 88                 | RW       |                                | D4h        |                    |          |

| PRT5IE               | 15h        | 31                 | W       |                      | 55h         |                    |          | ASA21CR1             | 95h        | 90                 | RW       |                                | D5h        |                    |          |

| PRT5GS               | 16h        | 32                 | W       |                      | 56h         |                    |          | ASA21CR2             | 96h        | 92                 | RW       |                                | D6h        |                    |          |

|                      | 17h        |                    |         |                      | 57h         |                    |          | ASA21CR3             | 97h        | 93                 | RW       |                                | D7h        |                    |          |

| -                    | 18h<br>19h |                    |         |                      | 58h<br>59h  |                    |          | ASB22CR0<br>ASB22CR1 | 98h<br>99h | 95<br>97           | RW<br>RW |                                | D8h<br>D9h |                    |          |

| Re .                 | 1Ah        |                    |         |                      | 5Ah         |                    |          | ASB22CR1             |            | 99                 | RW       | -                              | DAh        |                    |          |

| se .                 | 1Bh        |                    |         |                      | 5Bh         |                    |          | ASB22CR3             | 9Bh        | 100                | RW       |                                | DBh        |                    |          |

| Reserved             | 1Ch        |                    |         |                      | 5Ch         |                    |          | ASA23CR0             |            | 88                 | RW       |                                | DCh        |                    |          |

| ă                    | 1Dh        |                    |         |                      | 5Dh         |                    |          | ASA23CR1             | 9Dh        | 90                 | RW       |                                | DDh        |                    |          |

|                      | 1Eh        |                    |         |                      | 5Eh         |                    |          | ASA23CR2             | 9Eh        | 92                 | RW       |                                | DEh        |                    |          |

| DBA00DR0             | 1Fh<br>20h | 54                 | 1       | AMX_IN               | 5Fh<br>60h  | 104                | RW       | ASA23CR3             | 9Fh<br>A0h | 93                 | RW       | INT_MSK0                       | DFh<br>E0h | 45                 | RW       |

|                      | 21h        | 54                 | 1       |                      | 61h         | 104                | 1        |                      | A1h        |                    | -        | INT_MSK1                       | E1h        | 46                 | RW       |

| DBA00DR2             | 22h        | 54                 | 1       | Reserved             | 62h         |                    |          |                      | A2h        |                    |          | INT_VC                         | E2h        | 46                 | RW       |

|                      | 23h        | 55                 | 1       | ARF_CR               | 63h         | 73                 | RW       |                      | A3h        |                    |          | RES_WDT                        | E3h        | 116                | RW       |

|                      | 24h        | 54                 | 1       | CMP_CR               | 64h         | 101                | 1        |                      | A4h        |                    |          | DEC_DH/DEC_CL                  | E4h        | 113                | RW       |

|                      | 25h<br>26h | 54<br>54           | 1       | ASY_CR               | 65h<br>66h  | 102                | 1        |                      | A5h<br>A6h |                    | -        | DEC_DL<br>DEC_CR               | E5h<br>E6h | 113<br>113         | R<br>RW  |

|                      | 27h        | 55                 | 1       |                      | 67h         |                    |          |                      | A7h        |                    | -        | Reserved                       | E7h        | 115                | 1        |

|                      | 28h        | 54                 | 1       |                      | 68h         |                    |          |                      | A8h        |                    |          | MUL_X                          | E8h        | 110                | W        |

|                      | 29h        | 54                 | 1       | ਸ਼                   | 69h         |                    |          |                      | A9h        |                    |          | MUL_Y                          | E9h        | 110                | W        |

|                      | 2Ah        | 54                 | 1       | les                  | 6Ah         |                    |          |                      | AAh        |                    |          | MUL_DH                         | EAh        | 111                | R        |

| DBA02CR0             |            | 55                 | 1       | ez                   | 6Bh         |                    |          |                      | ABh        |                    | _        | MUL_DL                         | EBh        | 111                | R        |

| DBA03DR0<br>DBA03DR1 | 2Ch<br>2Dh |                    | 1       | Reserved             | 6Ch<br>6Dh  |                    | _        |                      | ACh<br>ADh |                    | -        | ACC_DR1/MAC_X<br>ACC_DR0/MAC_Y | ECh<br>EDh | 111<br>111         | RW<br>RW |

| DBA03DR2             |            |                    | 1       |                      | 6Eh         |                    |          | 72                   | AEh        |                    | -        | ACC_DR3/MAC_CL0                |            |                    | RW       |

| DBA03CR0             | 2Fh        | 55                 | 1       |                      | 6Fh         |                    |          | eserved              | AFh        |                    |          | ACC_DR2/MAC_CL1                |            |                    | RW       |

| DCA04DR0             |            |                    | 1       |                      | 70h         |                    |          | Ne Ve                | B0h        |                    |          |                                | F0h        |                    |          |

| DCA04DR1             |            |                    | 1       | ACA00CR0             |             |                    | RW       | ed                   | B1h        |                    | L        |                                | F1h        |                    |          |

| DCA04DR2<br>DCA04CR0 |            |                    | 1       | ACA00CR1<br>ACA00CR2 |             |                    | RW<br>RW |                      | B2h<br>B3h |                    |          |                                | F2h<br>F3h |                    |          |

| DCA04CR0<br>DCA05DR0 |            |                    | 1       | Reserved             | 73n<br>74h  | 04                 | NVV      |                      | B4h        |                    | -        |                                | F3n<br>F4h |                    |          |

| DCA05DR1             |            |                    | 1       | ACA01CR0             |             | 82                 | RW       |                      | B5h        |                    |          |                                | F5h        |                    |          |

| DCA05DR2             | 36h        | 54                 | 1       | ACA01CR1             | 76h         | 83                 | RW       |                      | B6h        |                    |          | Reserved                       | F6h        |                    |          |

| DCA05CR0             |            |                    | 1       | ACA01CR2             | 77h         | 84                 | RW       |                      | B7h        |                    |          | , er                           | F7h        |                    |          |

| DCA06DR0             |            |                    | 1       | Reserved             | 78h         | 02                 | DIA      |                      | B8h        |                    |          | vec                            | F8h        |                    |          |

| DCA06DR1<br>DCA06DR2 |            |                    | 1       | ACA02CR0<br>ACA02CR1 |             |                    | RW<br>RW |                      | B9h<br>BAh |                    | -        | <u> </u>                       | F9h<br>FAh |                    |          |

| DCA06DR2<br>DCA06CR0 |            |                    | 1       | ACA02CR1             |             |                    | RW       |                      | BBh        |                    | -        |                                | FBh        |                    |          |

| DCA07DR0             |            |                    | 1       | Reserved             | 7Ch         |                    |          |                      | BCh        |                    |          |                                | FCh        |                    |          |

| DCA07DR1             | 3Dh        | 54                 | 1       | ACA03CR0             |             | 82                 | RW       |                      | BDh        |                    |          |                                | FDh        |                    |          |

| DCA07DR2             | 3Eh        | 54                 | 1       | ACA03CR1             |             |                    | RW       |                      | BEh        |                    |          |                                | FEh        |                    |          |

| DCA07CR0             | 3Fh        | 55                 | 1       | ACA03CR2             | /Fh         | 84                 | RW       |                      | BFh        |                    |          | CPU_SCR                        | FFh        | 114                | 1        |

# 4.3 Register Bank 1 Map

## Table 27: Bank 1

| Register<br>Name    | Address     | Page     | Access   | Register<br>Name     | Address     | Data Sheet<br>Page | Access   | Register<br>Name     | Address    | Data Sheet<br>Page | Access   | Register<br>Name   | Address     | Data Sheet<br>Page | Access   |

|---------------------|-------------|----------|----------|----------------------|-------------|--------------------|----------|----------------------|------------|--------------------|----------|--------------------|-------------|--------------------|----------|

| le                  | SS          | e        | SS       | le                   | SS          | e<br>e             | SS       | ēfer                 | SS         | e                  | SS       | eter               | SS          | e                  | SS       |

| PRT0DM0             | 00h         | 32       | W        |                      | 40h         |                    |          | ASA10CR0             | 80h        | 88                 | RW       |                    | C0h         | -                  |          |

| PRT0DM1             | 01h         | 33       | W        |                      | 41h         |                    |          | ASA10CR1             | 81h        | 90                 | RW       | ]                  | C1h         |                    |          |

| PRTOIC0             | 02h         | 33       | W        | -                    | 42h         |                    |          | ASA10CR2             | 82h        | 92                 | RW       |                    | C2h         |                    |          |

| PRT0IC1<br>PRT1DM0  | 03h<br>04h  | 34<br>32 | W        | -                    | 43h<br>44h  |                    |          | ASA10CR3<br>ASB11CR0 | 83h<br>84h | 93<br>95           | RW<br>RW |                    | C3h<br>C4h  |                    |          |

| PRT1DM0             | 0411<br>05h | 33       | W        | -                    | 4411<br>45h |                    |          | ASB11CR1             | 85h        | 97                 | RW       |                    | C5h         |                    |          |

| PRT1IC0             | 06h         | 33       | Ŵ        | -                    | 46h         |                    |          | ASB11CR2             | 86h        | 99                 | RW       |                    | C6h         |                    | $\vdash$ |

| PRT1IC1             | 07h         | 34       | Ŵ        |                      | 47h         |                    |          | ASB11CR3             | 87h        | 100                | RW       |                    | C7h         |                    |          |

| PRT2DM0             | 08h         | 32       | W        |                      | 48h         |                    |          | ASA12CR0             | 88h        | 88                 | RW       |                    | C8h         |                    |          |

| PRT2DM1             | 09h         | 33       | W        | ]                    | 49h         |                    |          | ASA12CR1             | 89h        | 90                 | RW       |                    | C9h         |                    |          |

| PRT2IC0             | 0Ah         | 33       | W        |                      | 4Ah         |                    |          | ASA12CR2             | 8Ah        | 92                 | RW       |                    | CAh         |                    |          |

| PRT2IC1             | 0Bh         | 34       | W        | -                    | 4Bh         |                    |          | ASA12CR3             | 8Bh        | 93                 | RW       |                    | CBh         |                    |          |

| PRT3DM0<br>PRT3DM1  | 0Ch<br>0Dh  | 32<br>33 | W        | -                    | 4Ch<br>4Dh  |                    |          | ASB13CR0<br>ASB13CR1 | 8Ch<br>8Dh | 95<br>97           | RW<br>RW |                    | CCh<br>CDh  |                    |          |

| PRT3IC0             | 0Eh         | 33       | W        | 7                    | 4Eh         |                    |          | ASB13CR2             | 8Eh        | 99                 | RW       | 7                  | CEh         |                    |          |

| PRT3IC1             | 0Fh         | 34       | Ŵ        | Reserved             | 4Fh         |                    |          | ASB13CR3             | 8Fh        | 100                | RW       | Reserved           | CFh         |                    | $\vdash$ |

| PRT4DM0             | 10h         | 32       | Ŵ        | er                   | 50h         |                    |          | ASB20CR0             | 90h        | 95                 | RW       | er                 | D0h         |                    |          |

| PRT4DM1             | 11h         | 33       | W        | è                    | 51h         |                    |          | ASB20CR1             | 91h        | 97                 | RW       | è                  | D1h         |                    |          |

| PRT4IC0             | 12h         | 33       | W        |                      | 52h         |                    |          | ASB20CR2             | 92h        | 99                 | RW       |                    | D2h         |                    |          |

| PRT4IC1             | 13h         | 34       | W        |                      | 53h         |                    |          | ASB20CR3             | 93h        | 100                | RW       |                    | D3h         |                    |          |

| PRT5DM0             | 14h         | 32       | W        |                      | 54h         |                    |          | ASA21CR0             | 94h        | 88                 | RW       |                    | D4h         |                    |          |

| PRT5DM1             | 15h         | 33<br>33 | W        |                      | 55h         |                    |          | ASA21CR1             | 95h        | 90<br>92           | RW<br>RW |                    | D5h         |                    |          |

| PRT5IC0<br>PRT5IC1  | 16h<br>17h  | 33       | W        | -                    | 56h<br>57h  |                    |          | ASA21CR2<br>ASA21CR3 | 96h<br>97h | 92                 | RW       |                    | D6h<br>D7h  |                    |          |

|                     | 18h         | 54       |          | 1                    | 58h         |                    |          | ASB22CR0             | 98h        | 95                 | RW       |                    | D8h         |                    | $\vdash$ |

|                     | 19h         |          | -        |                      | 59h         |                    |          | ASB22CR1             | 99h        | 97                 | RW       | -                  | D9h         |                    |          |

| 7                   | 1Ah         |          |          |                      | 5Ah         |                    |          | ASB22CR2             | 9Ah        | 99                 | RW       |                    | DAh         |                    |          |

| ese                 | 1Bh         |          |          | 1                    | 5Bh         |                    |          | ASB22CR3             | 9Bh        | 100                | RW       |                    | DBh         |                    |          |

| Reserved            | 1Ch         |          |          |                      | 5Ch         |                    |          | ASA23CR0             | 9Ch        | 88                 | RW       | ]                  | DCh         |                    |          |

| ed                  | 1Dh         |          |          | -                    | 5Dh         |                    |          | ASA23CR1             | 9Dh        | 90                 | RW       |                    | DDh         |                    |          |

|                     | 1Eh<br>1Fh  |          | -        | -                    | 5Eh<br>5Fh  |                    |          | ASA23CR2<br>ASA23CR3 | 9Eh<br>9Fh | 92<br>93           | RW<br>RW |                    | DEh<br>DFh  |                    |          |

| DBA00FN             | 20h         | 50       | RW       | CLK_CR0              | 60h         | 76                 | RW       | ASAZSURS             | A0h        | 93                 | RVV      | OSC_CR0            | E0h         | 40                 | RW       |

| DBA00IN             | 21h         | 51       | RW       | CLK_CR1              | 61h         | 77                 | RW       | -                    | A1h        |                    |          | OSC_CR1            | E1h         | 40                 | RW       |

| DBA00OU             | 22h         | 53       | RW       | ABF_CR               | 62h         | 106                | W        | -                    | A2h        |                    |          | Reserved           | E2h         | 10                 | <u> </u> |

| Reserved            | 23h         |          |          | AMD_CR               | 63h         | 107                | RW       | 1                    | A3h        |                    |          | VLT_CR             | E3h         | 118                | RW       |

| DBA01FN             | 24h         | 50       | RW       |                      | 64h         |                    |          |                      | A4h        |                    |          | Reserved           | E4h         |                    |          |

| DBA01IN             | 25h         | 51       | RW       |                      | 65h         |                    |          |                      | A5h        |                    |          | Reserved           | E5h         |                    |          |

| DBA01OU             | 26h         | 53       | RW       | -                    | 66h         |                    |          | -                    | A6h        |                    |          | Reserved           | E6h         |                    |          |

| Reserved<br>DBA02FN | 27h<br>28h  | 50       | RW       | -                    | 67h<br>68h  |                    |          | -                    | A7h<br>A8h |                    |          | Reserved<br>IMO_TR | E7h<br>E8h  | 35                 | w        |

| DBA02IN             | 2011<br>29h | 51       | RW       | Re                   | 69h         |                    |          | -                    | A9h        |                    |          | ILO_TR             | E9h         | 36                 | W        |

| DBA02OU             | 2Ah         | 53       | RW       | - ise                | 6Ah         |                    |          | -                    | AAh        |                    |          | BDG TR             | EAh         | 120                | Ŵ        |

| Reserved            | 2Bh         |          |          | Reserved             | 6Bh         |                    |          |                      | ABh        |                    |          | ECO_TR             | EBh         | 37                 | Ŵ        |

| DBA03FN             | 2Ch         | 50       | RW       | ď                    | 6Ch         |                    |          | -                    | ACh        |                    |          |                    | ECh         |                    |          |

| DBA03IN             | 2Dh         | 51       | RW       |                      | 6Dh         |                    |          |                      | ADh        |                    |          |                    | EDh         |                    |          |

| DBA03OU             | 2Eh         | 53       | RW       |                      | 6Eh         |                    |          | Re                   | AEh        |                    |          |                    | EEh         |                    |          |

| Reserved            | 2Fh         | 50       | DIA/     | -                    | 6Fh         |                    |          | Reserved             | AFh        |                    |          |                    | EFh         |                    |          |

| DCA04FN<br>DCA04IN  | 30h<br>31h  | 50<br>51 | RW<br>RW | ACA00CR0             | 70h<br>71h  | 82                 | RW       | IV€                  | B0h<br>B1h |                    |          |                    | F0h<br>F1h  |                    |          |

| DCA04IN<br>DCA04OU  | 32h         | 53       | RW       | ACA00CR0             | 72h         | o∠<br>83           | RW       | d d                  | B2h        |                    |          |                    | F111<br>F2h |                    |          |

| Reserved            | 33h         | 00       |          | ACA00CR2             | 73h         | 84                 | RW       | -                    | B3h        |                    |          | _                  | F3h         |                    |          |

| DCA05FN             | 34h         | 50       | RW       | Reserved             | 74h         |                    |          |                      | B4h        |                    |          | Reserved           | F4h         |                    |          |

| DCA05IN             | 35h         | 51       | RW       | ACA01CR0             | 75h         | 82                 | RW       |                      | B5h        |                    |          | sei                | F5h         |                    |          |

| DCA05OU             | 36h         | 53       | RW       | ACA01CR1             | 76h         | 83                 | RW       |                      | B6h        |                    |          | rve                | F6h         |                    |          |

| Reserved            | 37h         |          | DUU      | ACA01CR2             | 77h         | 84                 | RW       |                      | B7h        |                    |          | ä                  | F7h         |                    |          |

| DCA06FN             | 38h         | 50       | RW       | Reserved             | 78h         | 00                 |          |                      | B8h        |                    |          |                    | F8h         |                    |          |

| DCA06IN             | 39h         | 51       | RW       | ACA02CR0             | 79h         | 82                 | RW       | -                    | B9h        |                    |          |                    | F9h         |                    |          |

| DCA06OU<br>Reserved | 3Ah<br>3Bh  | 53       | RW       | ACA02CR1<br>ACA02CR2 | 7Ah<br>7Bh  | 83<br>84           | RW<br>RW | -                    | BAh<br>BBh |                    |          |                    | FAh<br>FBh  |                    |          |

| DCA07FN             | 3Ch         | 50       | RW       | Reserved             | 7Ch         | 04                 | IX V V   | -                    | BCh        |                    |          |                    | FCh         |                    |          |

| DCA07FN<br>DCA07IN  | 3Dh         | 50       | RW       | ACA03CR0             | 7Dh         | 82                 | RW       |                      | BDh        |                    |          |                    | FDh         |                    |          |

| DCA070U             | 3Eh         | 53       | RW       | ACA03CR1             | 7Eh         | 83                 | RW       |                      | BEh        |                    |          |                    | FEh         |                    |          |

| Reserved            | 3Fh         |          |          | ACA03CR2             | 7Fh         | 84                 | RW       |                      | BFh        |                    |          | CPU SCR            | FFh         | 114                | 1        |

|                     | L           |          |          |                      |             |                    |          |                      |            |                    |          |                    |             |                    |          |

1. Read/Write access is bit-specific or varies by function. See register.

| Bit #                                                                                                                                                                                                                                                       | 7                                                                                                                                                                                            | 6                                                                                                                                                           | 5                                                                                 | 4                                                        | 3                                | 2                  | 1                 | 0            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--------------------|-------------------|--------------|

| POR                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                            | 0                                                                                                                                                           | 0                                                                                 | 0                                                        | 0                                | 0                  | 0                 | 0            |

| Read/Write                                                                                                                                                                                                                                                  | RW                                                                                                                                                                                           | RW                                                                                                                                                          | RW                                                                                | RW                                                       | RW                               | RW                 | RW                | RW           |

| Bit Name                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                                                     | Reserved                                                                                                                                                    | End                                                                               | Mode 1                                                   | Mode 0                           | Function [2]       | Function [1]      | Function [0] |

| <b>Bit 7: Reserved</b><br><b>Bit 6: Reserved</b><br><b>Bit 5: End</b><br>0 = PSoC block i<br>1 = PSoC block i                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                             |                                                                                   | •                                                        |                                  | ) in block DCA07)  |                   |              |

| <b>Bit 4</b> : <u>Mode 1</u> Th<br>Timer: The Mode<br>0 = Less Than of<br>1 = Less Than<br>Counter: The Mode<br>0 = Less Than<br>CRC/PRS: The Mode<br>0 = Transmit: Inte<br>1 = Transmit: Inte<br>SPI: The Mode[1<br>0 = Master: Inter<br>1 = Master: Inter | ne definition of t<br>e [1] bit signifies<br>r Equal<br>ode [1] bit signifi<br>r Equal<br>Mode [1] bit is u<br>Mode [1] bit is u<br>e[1] bit signifies<br>errupt on TX_R<br>errupt on TX Reg | he Mode [1] b<br>the Compare<br>tes the Compare<br>nused in this<br>nused in this<br>the Interrupt<br>eg Empty<br>omplete<br>e Interrupt Ty<br>Empty, Slave | bit depe<br>Type<br>are Typ<br>function<br>function<br>Type (T<br>pe<br>e: Interr | ends on the b<br>e<br>n<br>Transmitter of<br>upt on RX R | lock function<br>nly)<br>eg Full |                    |                   |              |

| Bit 3: Mode 0 Th<br>Timer: The Mode<br>0 = Terminal Cou<br>1 = Compare Tru<br>Counter: The Mod<br>0 = Terminal Cou<br>1 = Compare Tru<br>CRC/PRS: The Mode<br>0 = Receive<br>1 = Transmit<br>SPI: The Mode [1<br>0 = Master<br>1 = Slave                    | e [0] bit signifies<br>unt<br>de<br>ode [0] bit signifi<br>unt<br>Mode [0] bit is u<br>Mode [0] bit is u<br>e [0] bit signifies                                                              | Interrupt Typ<br>ies Interrupt T<br>nused in this<br>inused in this<br>the Direction                                                                        | e<br>ype<br>function<br>functio                                                   | n                                                        | lock function                    | selected           |                   |              |

| <b>Bit [2:0]</b> : <u>Functi</u><br>0 0 0 = Timer (cf<br>0 1 = Counter<br>0 1 0 = CRC/PR<br>0 1 1 = Reserved<br>1 0 0 = Deadban<br>1 0 1 = UART (fu<br>1 1 0 = SPI (func<br>1 1 1 = Reserved                                                                | nainable)<br>(chainable)<br>S (Cyclical Red<br>d<br>for Pulse Wid<br>Inction only ava<br>tion only availa                                                                                    | undancy Che<br>Ith Modulator<br>illable on DCA                                                                                                              | cker or<br>A type b                                                               | Pseudo Ran<br>blocks)                                    |                                  | n determines the b | oasic hardware co | nfiguration  |

| Table 47: | Digital Basic Type A/ Communications Type A Block xx Function Register |

|-----------|------------------------------------------------------------------------|

|-----------|------------------------------------------------------------------------|

Digital Basic Type A Block 00 Function Register(DBA00FN, Address = Bank 1, 20h)Digital Basic Type A Block 01 Function Register(DBA01FN, Address = Bank 1, 24h)Digital Basic Type A Block 02 Function Register(DBA02FN, Address = Bank 1, 24h)Digital Basic Type A Block 03 Function Register(DBA03FN, Address = Bank 1, 28h)Digital Communications Type A Block 04 Function Register(DCA04FN, Address = Bank 1, 30h)

Digital Communications Type A Block 05 Function Register Digital Communications Type A Block 06 Function Register Digital Communications Type A Block 07 Function Register (DCA05FN, Address = Bank 1, 34h) (DCA06FN, Address = Bank 1, 38h) (DCA07FN, Address = Bank 1, 3Ch)

## 9.2.2 Digital Basic Type A / Communications Type A Block xx Input Register

The Digital Basic Type A / Communications Type A Block xx Input Register (DBA00IN-DCA07IN) consists of 4 bits [3:0] to select the block input clock and 4 bits [7:4] to

select the primary data/enable input. The actual usage of the input data/enable is function dependent.

| Bit #                                        | 7                 | 6                | 5                      | 4            | 3                                 | 2                                        | 1          | 0         |

|----------------------------------------------|-------------------|------------------|------------------------|--------------|-----------------------------------|------------------------------------------|------------|-----------|

| POR                                          | 0                 | 0                | 0                      | 0            | 0                                 | 0                                        | 0          | 0         |

| Read/Write                                   | RW                | RW               | RW                     | RW           | RW                                | RW                                       | RW         | RW        |

| Bit Name                                     | Data [3]          | Data [2]         | Data [1]               | Data [0]     | Clock [3]                         | Clock [2]                                | Clock [1]  | Clock [0] |

|                                              |                   |                  | -14                    |              |                                   |                                          |            |           |

| Bit [7:4]: <u>Data  </u><br>0 0 0 0 = Data = |                   | able Source S    | elect                  |              |                                   |                                          |            |           |

| 0 0 0 1 = Data =                             |                   |                  |                        |              |                                   |                                          |            |           |

| 0 0 1 0 = Digital                            | Block 03          |                  |                        |              |                                   |                                          |            |           |

| 0 0 1 1 = Chain                              |                   |                  |                        |              |                                   |                                          |            |           |

| 0.100 = Analog                               |                   |                  |                        |              |                                   |                                          |            |           |

| 101 = Analog                                 |                   |                  |                        |              |                                   |                                          |            |           |

| 0 1 1 0 = Analog<br>0 1 1 1 = Analog         | 0                 | •                |                        |              |                                   |                                          |            |           |

|                                              | •                 | •                | ; 00 to 03) <b>o</b> i | r Global Out | put[4] (for Did                   | gital Blocks 04 to                       | 07)        |           |

|                                              |                   |                  |                        |              |                                   | gital Blocks 04 to                       |            |           |

| 1 0 1 0 = Globa                              | I Output[2] (for  | Digital Blocks   | 00 to 03) o            | r Global Out | put[6] (for Dig                   | gital Blocks 04 to                       | 07)        |           |

|                                              |                   | 0                | ,                      |              |                                   | gital Blocks 04 to                       | ,          |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)<br>Blocks 04 to 07)     |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              | 1 - 1 - 1 ( -     | 3                | , .                    |              | . I ( <sup>1</sup> J <sup>1</sup> | · · · · · · · ,                          |            |           |

| Bit [3:0]: <u>Clock</u>                      |                   | Source Select    |                        |              |                                   |                                          |            |           |

| $0 \ 0 \ 0 \ 0 = \text{Clock}$               |                   |                  |                        |              |                                   |                                          |            |           |

|                                              |                   |                  | 6 00 to 03) <b>o</b> i | r Global Out | put[0] (for Dig                   | gital Blocks 04 to                       | 07)        |           |

| 0 0 1 0 = Digital<br>0 0 1 1 = Previo        |                   |                  | arv Output)            |              |                                   |                                          |            |           |

| 0 1 0 0 = 48M                                | Nus Digitai i Oc  |                  | ary Output)            |              |                                   |                                          |            |           |

| 0 1 0 1 = 24V1                               |                   |                  |                        |              |                                   |                                          |            |           |

| 0 1 1 0 = 24V2                               |                   |                  |                        |              |                                   |                                          |            |           |

| 0 1 1 1 = 32k                                |                   |                  |                        |              |                                   |                                          |            |           |

|                                              |                   | 0                | ,                      |              |                                   | gital Blocks 04 to                       | ,          |           |

|                                              |                   | 0                | ,                      |              |                                   | gital Blocks 04 to<br>gital Blocks 04 to | ,          |           |

|                                              |                   |                  |                        |              |                                   | gital Blocks 04 to                       |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   | Blocks 04 to 07)                         |            |           |

| 1 1 1 1 = Globa                              | I Input[3] (for E | Digital Blocks ( | 00 to 03) <b>or</b> 0  | Global Input | [7] (for Digital                  | Blocks 04 to 07)                         |            |           |

|                                              |                   |                  |                        |              |                                   |                                          |            |           |

| igital Basic Ty                              | ne A Block (      | 00 Input Red     | ister                  |              | (DBA00IN                          | I, Address = Ba                          | ank 1 21h) |           |

| Digital Basic Type A Block 00 Input Register          | (DBA00IN, Address = Bank 1, 21h) |

|-------------------------------------------------------|----------------------------------|

| Digital Basic Type A Block 01 Input Register          | (DBA01IN, Address = Bank 1, 25h) |

| Digital Basic Type A Block 02 Input Register          | (DBA02IN, Address = Bank 1, 29h) |

| Digital Basic Type A Block 03 Input Register          | (DBA03IN, Address = Bank 1, 2Dh) |

| Digital Communications Type A Block 04 Input Register | (DCA04IN, Address = Bank 1, 31h) |

| Digital Communications Type A Block 05 Input Register | (DCA05IN, Address = Bank 1, 35h) |

Digital Communications Type A Block 06 Input Register Digital Communications Type A Block 07 Input Register

The Data/Enable source select [3:0] bits select between multiple inputs to the Digital PSoC Blocks. These inputs serve as Clock Enables or Data Input depending on the Digital PSoC Block's programmed function. If "Chain Function to Previous" data input is selected for Data/ Enable then the selected Digital PSoC block receives its Data, Enable, Zero Detect, and all chaining information from the previous digital PSoC block. The data inputs that are selected from the GPIO pins (through the Global Input Bus) are synchronized to the 24 MHz clock. The following table shows the function dependent meaning of the data input.

| Table 49: | Digital Function Data Input Definitions |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Function   | Data Input                 |

|------------|----------------------------|

| Timer      | Positive Edge Capture      |

| Counter    | Count Enable (Active High) |

| CRC        | Data Input                 |

| PRS        | N/A                        |

| Deadband   | Kill Signal (Active High)  |

| TX UART    | N/A                        |

| RX UART    | RX Data In                 |

| SPI Master | MISO (Master In/Slave Out) |

| SPI Slave  | MOSI (Master Out/Slave In) |

(DCA06IN, Address = Bank 1, 39h) (DCA07IN, Address = Bank 1, 3Dh)

The Clock[3:0] bits select multiple sources for the clock for each digital PSoC block. The sources for each digital PSoC block clock are selected from the Global Input Bus, System Clocks, and other neighboring digital PSoC blocks. As shown in the table, Digital PSoC Blocks 0-3 can interface to Global I/Os 00-03, and Digital PSoC block 04-07 can interface to Global I/Os 4-7. It is important to note that clock inputs selected from the GPIO pins (through the Global Input Bus) are not synchronized. This may cause indeterminate results if the CPU reads a block register as it is changing in response to an external clock. CPU reads must be manually synchronized, either through the block interrupt, or through a multiple read and voting scheme.

#### 9.2.3 Digital Basic Type A / Communications Type A Block xx Output Register

The digital PSoC block's outputs can be selected to drive associated Global Output Bus signals via the Output Select bits. In addition, the output drive can be selectively enabled in this register. The SPI Slave has an auxiliary input which is also controlled by selections in this register.

|     | AGND               |                    | Ref                  | HI                 | Ref                  | LO                 | Notes                        |

|-----|--------------------|--------------------|----------------------|--------------------|----------------------|--------------------|------------------------------|

|     | Source             | Voltage            | Source               | Voltage            | Source               | Voltage            |                              |

| 000 | V <sub>cc</sub> /2 | 2.5 V<br>1.65 V    | V <sub>cc</sub> +Vbg | 3.8 V<br>2.95 V    | V <sub>cc</sub> -Vbg | 1.2 V<br>0.35 V    | 5.0 V System<br>3.3 V System |

| 001 | P2[4]              | 2.2 V <sup>1</sup> | P2[4]+P2[6]          | 3.2 V <sup>1</sup> | P2[4]-P2[6]          | 1.2 V <sup>1</sup> | User Adjustable              |

| 010 | Vcc/2              | 2.5 V<br>1.65 V    | Vcc                  | 5.0 V<br>3.3 V     | Vss                  | 0.0 V<br>0.0 V     | 5.0 V System<br>3.3 V System |

| 011 | 2*Vbg              | 2.6 V              | 2*Vbg+Vbg            | 3.9 V              | 2*Vbg-Vbg            | 1.3 V              | Not for 3.3 V Systems        |

| 100 | 2*Vbg              | 2.6 V              | 2*Vbg+P2[6]          | 3.6 V <sup>1</sup> | 2*Vbg-P2[6]          | 1.6 V <sup>1</sup> | Not for 3.3 V Systems        |

| 101 | P2[4]              | 2.2 V <sup>1</sup> | P2[4]+Vbg            | 3.5 V <sup>1</sup> | P2[4]-Vbg            | 0.9 V <sup>1</sup> | User Adjustable              |

| 110 | Reserved           |                    | •                    |                    |                      |                    | •                            |

| 111 | Reserved           |                    |                      |                    |                      |                    |                              |

| Table 62: | AGND, RefHI, RefLO Operating Parameters |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

1. Example shown for AGND P2[4] = 2.2 V and Ref P2[6] = 1.0 V

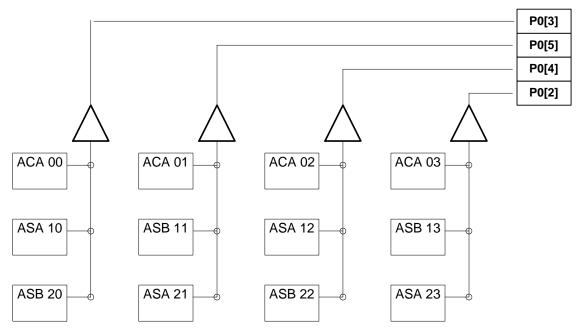

#### 10.4.4 Analog Array Power Control

PWR Sets Analog Array Power Control. Analog array power is controlled through the bias circuits in the Continuous Time blocks and separate bias circuits in the Switched Capacitor blocks. Continuous Time blocks (ACAxx) can be operated to make low power comparators independent of Switched Capacitor (ASAxx and ASBxx) blocks, without their power consumption.

The reference array supplies voltage to all blocks and current to the Switched Capacitor blocks. At higher block clock rates, there is increased reference current demand; the reference power should be set equal to the highest power level of the analog blocks used.

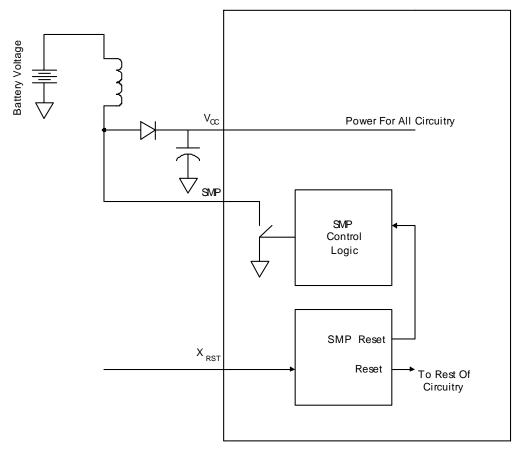

# 10.5 Analog PSoC Block Clocking Options

All analog PSoC blocks in a particular Analog Column share the same clock signal. Choosing the clocking for an analog PSoC block is a two-step process.

First, if the user wants to use the ACLK0 and ACLK1 system-clocking signals, the digital PSoC blocks that serve as the source for these signals must be selected. This selection is made in the Analog Clock Select Register (CLK\_CR1).

#### 10.5.1 Analog Column Clock Select Register

#### Table 64: Analog Column Clock Select Register

Next, the user must select the source for the Acolumn0, Acolumn1, Acolumn2, and Acolumn3 system-clocking signals. The user will choose the clock for Acolumnx[1:0] bits in the Analog Column Clock Select Register (CLK\_CR0). Each analog PSoC block in a particular Analog Column is clocked from the Acolumn[x] system-clocking signal for that column. (Note that the Acolumn[x] signals have a 1:4 divider on them.)

| Bit #                                                                                                                                           | 7                             | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| POR                                                                                                                                             | 0                             | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| Read/<br>Write                                                                                                                                  | RW                            | RW              | RW              | RW              | RW              | RW              | RW              | RW              |

| Bit Name                                                                                                                                        | Acolumn3<br>[1]               | Acolumn3<br>[0] | Acolumn2<br>[1] | Acolumn2<br>[0] | Acolumn1<br>[1] | Acolumn1<br>[0] | Acolumn0<br>[1] | Acolumn0<br>[0] |

| 0 0 = 24V1<br>0 1 = 24V2<br>1 0 = ACLK0<br>1 1 = ACLK1<br><b>Bit [5:4]:</b> <u>AC</u><br>0 0 = 24V1<br>0 1 = 24V2<br>1 0 = ACLK0<br>1 1 = ACLK1 | 1<br><b>:olumn2 [1:0</b><br>) | 1               |                 |                 |                 |                 |                 |                 |

| 0 = 24V1<br>0 = 24V2<br>1 = 24V2<br>1 = ACLK0<br>1 = ACLK0                                                                                      | )                             | -               |                 |                 |                 |                 |                 |                 |

| <b>Bit [1:0]</b> : <u>Ac</u><br>0 0 = 24V1<br>0 1 = 24V2<br>1 0 = ACLK0<br>1 1 = ACLK2                                                          |                               | 1               |                 |                 |                 |                 |                 |                 |

### 10.7.2.2 Analog Continuous Time Block xx Control 1 Register

The PMux bits control the multiplexing of inputs to the non-inverting input of the op-amp. There are physically only 7 inputs.

The 8<sup>th</sup> code (111) will leave the input floating. This is not desirable, and should be avoided.

The NMux bits control the multiplexing of inputs to the inverting input of the op-amp. There are physically only 7 inputs.

CompBus controls a tri-state buffer that drives the comparator logic. If no PSoC block in the analog column is driving the comparator bus, it will be driven low externally to the blocks.

AnalogBus controls the analog output bus. A CMOS switch connects the op-amp output to the analog bus.

| Table 67: | Analog Continuous Time Block xx Control 1 Register |  |

|-----------|----------------------------------------------------|--|

|-----------|----------------------------------------------------|--|

| Bit #                                                                                                                   | 7                                                                                                                                                                                                                                                                                                                                                                        | 6                                                                            | 5                                                                                     | 4                                                                                     | 3     | 2     | 1     | 0     |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|--|

| POR                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                            | 0                                                                                     | 0                                                                                     | 0     | 0     | 0     | 0     |  |  |  |  |