Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | M8C                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 24MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                        |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 16KB (16K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                |

| Data Converters            | A/D 1x8b, 1x11b, 1x12b; D/A 1x9b                                          |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c26643-24ai |

|                            |                                                                           |

# **Getting Started in the PSoC World!**

The award winning PSoC Designer software and PSoC silicon are an integrated unit. The quickest path to understanding the PSoC silicon is through the PSoC Designer software GUI. This data sheet is useful for understanding the details of the PSoC integrated circuit, but is not a good starting point for a new PSoC developer seeking to get a general overview of this new technology.

PSoC developers are NOT required to build their own ADCs, DACs, and other peripherals. Embedded in the PSoC Designer software are the individual data sheets, performance graphs, and PSoC User Modules (graphically selected code packets) for the peripherals, such as the incremental ADCs, DACs, LCD controllers, op amps, low-pass filters, etc. With simple GUI-based selection, placement, and connection, the basic architecture of a design may be developed within PSoC Designer software without ever writing a single line of code.

Development Kits are available from the following distributors: Digi-Key, Avnet, Arrow, and Future. The Cypress Online Store also contains development kits, C compilers, and all accessories for PSoC development. Go to the Cypress Online Store web site at http://www.cypress.com, click the Online Store shopping cart icon at the bottom of the web page, and click PSoC (Programmable System-on-Chip) to view a current list of available items.

Free PSoC technical training is available for beginners and is taught by a marketing or application engineer over the phone. PSoC training classes cover designing, debugging, advanced analog, as well as application-specific classes covering topics such as PSoC and the LIN bus. Go to http://www.cypress.com, click on Design Support located on the left side of the web page, and select Technical Training for more details.

Certified PSoC Consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC Consultant go to http://www.cypress.com, click on Design Support located on the left side of the web page, and select CYPros Consultants.

PSoC application engineers take pride in fast and accurate response. They can be reached with a 4-hour guaranteed response at http://www.cypress.com/support/login.cfm.

Cypress Semiconductor 2700 162nd Street SW, Building D Lynnwood, WA 98037 Phone: 425.787.4400

Fax: 425.787.4641

Application Support Hotline: 425.787.4814

© Cypress Semiconductor Corporation. 2000-2005. All rights reserved. PSoC<sup>TM</sup>, PSoC Designer<sup>TM</sup>, and Programmable System-on-Chip<sup>TM</sup> are PSoC-related trademarks of Cypress Semiconductor Corporation. All other trademarks or registered trademarks referenced herein are property of the respective corporations.

The information contained herein is subject to change without notice. Cypress Semiconductor assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges. Cypress Semiconductor products are not warranted nor intended to be used for medical, life-support, life-saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress Semiconductor.

Note the following details of the Flash code protection features on Cypress Semiconductor PSoC devices.

Cypress Semiconductor products meet the specifications contained in their particular Cypress Semiconductor Data Sheets. Cypress Semiconductor believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress Semiconductor, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress Semiconductor nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable." Cypress Semiconductor is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress Semiconductor are committed to continuously improving the code protection features of our products.

| 10.8 Analog Switch Cap Type A PSoC Blocks              | 85  |

|--------------------------------------------------------|-----|

| 10.9 Analog Switch Cap Type B PSoC Blocks              |     |

| 10.10 Analog Comparator Bus                            | 101 |

| 10.11 Analog Synchronization                           | 101 |

| 10.12 Analog I/O                                       | 103 |

| 10.13 Analog Modulator                                 | 106 |

| 10.14 Analog PSoC Block Functionality                  | 107 |

| 10.15 Temperature Sensing Capability                   | 108 |

| 11.0 Special Features of the CPU                       | 109 |

| 11.1 Multiplier/Accumulator                            | 109 |

| 11.2 Decimator                                         | 112 |

| 11.3 Reset                                             | 114 |

| 11.4 Sleep States                                      |     |

| 11.5 Supply Voltage Monitor                            | 118 |

| 11.6 Switch Mode Pump                                  | 119 |

| 11.7 Internal Voltage Reference                        | 120 |

| 11.8 Supervisor ROM/System Supervisor Call Instruction | 120 |

| 11.9 Flash Program Memory Protection                   | 122 |

| 11.10 Programming Requirements and Step Descriptions   | 122 |

| 11.11 Programming Wave Forms                           | 124 |

| 11.12 Programming File Format                          | 124 |

| 12.0 Development Tools                                 | 125 |

| 12.1 Overview                                          | 125 |

| 12.2 Integrated Development Environment Subsystems     | 126 |

| 12.3 Hardware Tools                                    | 126 |

| 13.0 DC and AC Characteristics                         | 127 |

| 13.1 Absolute Maximum Ratings                          | 127 |

| 13.2 DC Characteristics                                | 129 |

| 13.3 AC Characteristics                                | 138 |

| 14.0 Packaging Information                             | 143 |

| 14.1 Thermal Impedances per Package                    | 148 |

| 15.0 Ordering Guide                                    | 149 |

| 16.0 Document Revision History                         | 150 |

| Fable 100: Flash Program Memory Protection                               | 122 |

|--------------------------------------------------------------------------|-----|

| Fable 101: Programmer Requirements                                       | 122 |

| Fable 102: Absolute Maximum Ratings                                      | 127 |

| Fable 103: Temperature Specifications                                    | 128 |

| Fable 104: DC Operating Specifications                                   | 129 |

| Fable 105: 5V DC Operational Amplifier Specifications                    | 130 |

| Fable 106: 3.3V DC Operational Amplifier Specifications                  | 131 |

| Fable 107: DC Analog Input Pin with Multiplexer Specifications           | 132 |

| Fable 108: DC Analog Input Pin to SC Block Specifications                | 132 |

| Fable 109: 5V DC Analog Output Buffer Specifications                     | 132 |

| Fable 110: 3.3V DC Analog Output Buffer Specifications                   | 133 |

| Fable 111: DC Switch Mode Pump Specifications                            | 134 |

| Fable 112: 5V DC Analog Reference Specifications                         | 135 |

| Fable 113: 3.3V DC Analog Reference Specifications                       | 136 |

| Fable 114: DC Analog PSoC Block Specifications                           | 136 |

| Fable 115: DC Programming Specifications                                 | 137 |

| Fable 116: AC Operating Specifications                                   | 138 |

| Fable 117: 5V AC Operational Amplifier Specifications                    | 139 |

| Fable 118: 3.3V AC Operational Amplifier Specifications                  | 140 |

| Fable 119: 5V AC Analog Output Buffer Specifications                     | 141 |

| Fable 120: 3.3V AC Analog Output Buffer Specifications                   | 142 |

| Fable 121: AC Programming Specifications                                 | 142 |

| Fable 122: Thermal Impedances                                            | 148 |

| Fable 123: Ordering Guide (Leaded)                                       | 149 |

| Fable 124: Ordering Guide (Pb-Free Denoted with an "X" in Ordering Code) |     |

| Fable 125: Document Revision History                                     |     |

| · · · · · · · · · · · · · · · · · · ·                                    |     |

### 1.0 Functional Overview

The CPU heart of this next generation family of microcontrollers is a high performance, 8-bit, M8C Harvard architecture microprocessor. Separate program and memory busses allow for faster overall throughput. Processor clock speeds to 24 MHz are available. The processor may also be run at lower clock speeds for powersensitive applications. A rich instruction set allows for efficient low-level language support.

All devices in this family include both analog and digital configurable peripherals (PSoC blocks). These blocks enable the user to define unique functions during configuration of the device. Included are twelve analog PSoC blocks and eight digital PSoC blocks. Potential applications for the digital PSoC blocks are timers, counters, UARTs, CRC generators, PWMs, and other functions. The analog PSoC blocks can be used for SAR ADCs, Multi-slope ADCs, programmable gain amplifiers, programmable filters, DACs, and other functions. Higher order User Modules such as modems, complex motor controllers, and complete sensor signal chains can be created from these building blocks. This allows for an unprecedented level of flexibility and integration in microcontroller-based systems.

A Multiplier/Accumulator (MAC) is available on all devices in this family. The MAC is implemented on this device as a peripheral that is mapped into the register space. When an instruction writes to the MAC input registers, the result of an 8x8 multiply and a 32-bit accumulate are available to be read from the output registers on the next instruction cycle.

The number of general purpose I/Os available in this family of parts range from 6 to 44. Each of these I/O pins has a variety of programmable options. In the output

mode, the user can select the drive strength desired. Any pin can serve as an interrupt source, and can be selected to trigger on positive edges, negative edges, or any change. Digital signal sources can be routed directly from a pin to the digital PSoC blocks. Some pins have additional capability to route analog signals to the analog PSoC blocks.

Multiple oscillator options are available for use in clocking the CPU, analog PSoC blocks and digital PSoC blocks. These options include an internal main oscillator running at 48/24 MHz, an external crystal oscillator for use with a 32.768 kHz watch crystal, and an internal low-speed oscillator for use in clocking the PSoC blocks and the Watchdog/Sleep timer. User selectable clock divisors allow for optimizing code execution speed and power trade-offs.

The different device types in this family provide various amounts of code and data memory. The code space ranges in size from 4K to 16K bytes of user programmable Flash memory. This memory can be programmed serially in either a programming Pod or on the user board. The endurance on the Flash memory is 50,000 erase/write cycles. The data space is 256 bytes of user SRAM.

A powerful and flexible protection model secures the user's sensitive information. This model allows the user to selectively lock blocks of memory for read and write protection. This allows partial code updates without exposing proprietary information.

Devices in this family range from 8 pins through 48 pins in PDIP, SOIC and SSOP packages.

# 1.1 Key Features

Table 1: Device Family Key Features

|                           | CY8C25122       | CY8C26233       | CY8C26443       | CY8C26643       |

|---------------------------|-----------------|-----------------|-----------------|-----------------|

| Operating Frequency       | 93.7kHz - 24MHz | 93.7kHz - 24MHz | 93.7kHz - 24MHz | 93.7kHz - 24MHz |

| Operating Voltage         | 3.0 - 5.25V     | 3.0 - 5.25V     | 3.0 - 5.25V     | 3.0 - 5.25V     |

| Program Memory (KBytes)   | 4               | 8               | 16              | 16              |

| Data Memory (Bytes)       | 256             | 256             | 256             | 256             |

| Digital PSoC Blocks       | 8               | 8               | 8               | 8               |

| Analog PSoC Blocks        | 12              | 12              | 12              | 12              |

| I/O Pins                  | 6               | 16              | 24              | 40/44           |

| External Switch Mode Pump | No              | Yes             | Yes             | Yes             |

| Available Packages        | 8 PDIP          | 20 PDIP         | 28 PDIP         | 48 PDIP         |

|                           |                 | 20 SOIC         | 28 SOIC         | 48 SSOP         |

|                           |                 | 20 SSOP         | 28 SSOP         | 44 TQFP         |

# 2.2 CPU Registers

## 2.2.1 Flags Register

The Flags Register can only be set or reset with logical instruction.

Table 8: Flags Register

| Bit #          | 7        | 6        | 5        | 4   | 3     | 2     | 1    | 0         |

|----------------|----------|----------|----------|-----|-------|-------|------|-----------|

| POR            | 0        | 0        | 0        | 0   | 0     | 0     | 1    | 0         |

| Read/<br>Write |          |          |          | RW  | R     | RW    | RW   | RW        |

| Bit Name       | Reserved | Reserved | Reserved | XIO | Super | Carry | Zero | Global IE |

Bit 7: Reserved

Bit 6: Reserved

Bit 5: Reserved

Bit 4: XIO Set by the user to select between the register banks

0 = Bank 0

1 = Bank 1

**Bit 3**: **Super** Indicates whether the CPU is executing user code or Supervisor Code. (This code cannot be accessed directly by the user and is not displayed in the ICE debugger.)

0 = User Code

1 = Supervisor Code

Bit 2: Carry Set by CPU to indicate whether there has been a carry in the previous logical/arithmetic operation

0 = No Carry

1 = Carry

Bit 1: Zero Set by CPU to indicate whether there has been a zero result in the previous logical/arithmetic operation

0 = Not Equal to Zero

1 = Equal to Zero

Bit 0: Global IE Determines whether all interrupts are enabled or disabled

0 = Disabled

1 = Enabled

## 2.2.2 Accumulator Register

Table 9: Accumulator Register (CPU\_A)

| Bit #      | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| POR        | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/Write | System <sup>1</sup> |

| Bit Name   | Data [7]            | Data [6]            | Data [5]            | Data [4]            | Data [3]            | Data [2]            | Data [1]            | Data [0]            |

Bit [7:0]: Data [7:0] 8-bit data value holds the result of any logical/arithmetic instruction that uses a source addressing mode

1. System - not directly accessible by the user

# 6.0 I/O Registers

## 6.1 Port Data Registers

Table 28: Port Data Registers

| Bit #      | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|

| POR        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| Read/Write | RW       |

| Bit Name   | Data [7] | Data [6] | Data [5] | Data [4] | Data [3] | Data [2] | Data [1] | Data [0] |

Bit [7:0]: Data [7:0] When written is the bits for output on port pins. When read is the state of the port pins

```

Port 0 Data Register (PRT0DR, Address = Bank 0, 00h)

```

Port 1 Data Register (PRT1DR, Address = Bank 0, 04h)

Port 2 Data Register (PRT2DR, Address = Bank 0, 08h)

Port 3 Data Register (PRT3DR, Address = Bank 0, 0Ch)

Port 4 Data Register (PRT4DR, Address = Bank 0, 10h)

Port 5 Data Register (PRT5DR, Address = Bank 0, 14h) Note: Port 5 is 4-bits wide, Bit [3:0]

## 6.2 Port Interrupt Enable Registers

Table 29: Port Interrupt Enable Registers

| Bit #      | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| POR        | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

| Read/Write | W          | W          | W          | W          | W          | W          | W          | W          |

| Bit Name   | Int En [7] | Int En [6] | Int En [5] | Int En [4] | Int En [3] | Int En [2] | Int En [1] | Int En [0] |

Bit [7:0]: Int En [7:0] When written sets the pin interrupt state

0 = Interrupt disabled for pin

1 = Interrupt enabled for pin

Port 0 Interrupt Enable Register (PRT0IE, Address = Bank 0, 01h)

Port 1 Interrupt Enable Register (PRT1IE, Address = Bank 0, 05h)

Port 2 Interrupt Enable Register (PRT2IE, Address = Bank 0, 09h)

Port 3 Interrupt Enable Register (PRT3IE, Address = Bank 0, 0Dh)

Port 4 Interrupt Enable Register (PRT4IE, Address = Bank 0, 11h)

Port 5 Interrupt Enable Register (PRT5IE, Address = Bank 0, 15h) Note: Port 5 is 4-bits wide

Table 36: Internal Low Speed Oscillator Trim Register

| Bit #          | 7        | 6       | 5               | 4               | 3               | 2               | 1               | 0               |

|----------------|----------|---------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| POR            | 0        | 0       | FS <sup>1</sup> |

| Read/<br>Write |          | W       | W               | W               | W               | W               | W               | W               |

| Bit Name       | Reserved | Disable | ILO Trim<br>[5] | ILO Trim<br>[4] | ILO Trim<br>[3] | ILO Trim<br>[2] | ILO Trim<br>[1] | ILO Trim<br>[0] |

#### Bit 7: Reserved

Bit 6: Disable

0 = Low Speed Oscillator is on

1 = Low Speed Oscillator is off (minimum power state)

Bit [5:0]: <u>ILO Trim [5:0]</u> Data value stored will alter the trimmed frequency of the Internal Low Speed Oscillator. (Not recommended for customer alteration)

1. FS = Factory set trim value

Internal Low Speed Oscillator Trim Register (ILO\_TR, Address = Bank 1, E9h)

## 7.1.3 External Crystal Oscillator

The Xtalln and XtalOut pins support connection of a 32.768 kHz watch crystal to drive the 32K clock. To connect to the external crystal, the XtalIn and XtalOut pins' drive modes must be set to High Z. To enable the external crystal oscillator, bit 7 of the Oscillator Control 0 Register (OSC\_CR0) must be set (default is off). Note that the Internal Low Speed Oscillator continues to run when this external function is selected. It runs until the oscillator is automatically switched over when the sleep timer reaches terminal count. External feedback capacitors to  $V_{\rm CC}$  are required.

The firmware steps involved in switching between the Internal Low Speed Oscillator and External Crystal Oscillator are as follows:

- At reset, the chip begins operation using the Internal Low Speed Oscillator.

- User immediately selects a sleep interval of 1 second in the Oscillator Control 0 Register (OSC\_CR0), as the oscillator stabilization interval.

- User selects External Crystal Oscillator by setting bit

in Oscillator Control 0 Register (OSC\_CR0) to 1.

- The External Crystal Oscillator becomes the selected 32.768 kHz source at the end of the 1-sec-

ond interval, created by the Sleep Interrupt logic. The 1-second interval gives the oscillator time to stabilize before it becomes the active source. The Sleep Interrupt need not be enabled for the switch over to occur. The user may want to reset the sleep timer (if this does not interfere with any ongoing real-time clock operation), to guarantee the interval length.

The user must wait the 1-second stabilization period prior to engaging the PLL mode to lock the Internal Main Oscillator frequency to the External Crystal Oscillator frequency.

If the proper settings are selected in PSoC Designer, the above steps are automatically done in *boot.asm*.

**Note**: Transitions between oscillator domains may produce glitches on the 32K clock bus. Functions that require accuracy on the 32K clock should be enabled after the transition in oscillator domains.

The External Crystal Oscillator Trim Register (ECO\_TR) sets the adjustment for the External Crystal Oscillator. The value placed in this register at reset is based on factory testing. This register does not adjust the frequency of the External Crystal Oscillator. It is recommended that the user not alter this value.

### 7.1.5 Phase-Locked Loop (PLL) Operation

The Phase-Locked Loop (PLL) function generates the system clock with crystal accuracy. It is designed to provide a 23.986 MHz oscillator when utilized with an external 32.768 kHz crystal. Although the PLL provides crystal accuracy it requires time to lock onto the reference frequency when first starting. After the External Crystal Oscillator has been selected and enabled, the following procedure should be followed to enable the PLL and allow for proper frequency lock:

- 1. Select a CPU frequency of 3 MHz or less.

- 2. Enable the PLL.

- Wait at least 10 ms.

- Set CPU to a faster frequency, if desired. To do this, write the bits CPU[2:0] in the OSC\_CR0 register.

The CPU frequency will immediately change when these bits are set.

If the proper settings are selected in PSoC Designer, the above steps are automatically done in *boot.asm*.

# 7.2 System Clocking Signals

There are twelve system-clocking signals that are used throughout the device. Referenced frequencies are

based on use of 32.768 kHz crystal. The names of these signals and their definitions are as follows:

Table 39: System Clocking Signals and Definitions

| Signal | Definition                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48M    | The direct 48 MHz output from the Internal Main Oscillator.                                                                                                                                                                                                                                                                                                                         |

| 24M    | The direct 24 MHz output from the Internal Main Oscillator.                                                                                                                                                                                                                                                                                                                         |

| 24V1   | The 24 MHz output from the Internal Main Oscillator that has been passed through a user-selectable 1 to 16 divider {F = 24 MHz / (1 to 16) = 24 MHz to 1.5 MHz}. The divider value is found in the Oscillator Control 1 Register (OSC_CR1). Note that the divider will be N+1, based on a value of N written into the register bits.                                                |

| 24V2   | The 24V1 signal that has been passed through an additional user-selectable 1 to 16 divider $\{F = 24 \text{ MHz} / ((1 \text{ to } 16) * (1 \text{ to } 16)) = 24 \text{ MHz} \text{ to } 93.7 \text{ kHz}\}$ . The divider value is found in the Oscillator Control 1 Register (OSC_CR1). Note that the divider will be N+1, based on a value of N written into the register bits. |

| 32K    | The multiplexed output of either the Internal Low Speed Oscillator or the External Crystal Oscillator.                                                                                                                                                                                                                                                                              |

| СРИ    | The output from the Internal Main Oscillator that has been passed through a divider that has 8 user selectable ratios ranging from 1:1 to 1:256, yielding frequencies ranging from 24 MHz to 93.7 kHz.                                                                                                                                                                              |

| SLP    | The <b>32K</b> system-clocking signal that has been passed through a divider that has 4 user selectable ratios ranging from 1:2 <sup>6</sup> to 1:2 <sup>15</sup> , yielding frequencies ranging from 512 Hz to 1 Hz. This signal is used to clock the sleep timer period.                                                                                                          |

# 8.4 Interrupt Masks

Table 44: General Interrupt Mask Register

| Bit #          | 7        | 6     | 5    | 4        | 3        | 2        | 1        | 0               |

|----------------|----------|-------|------|----------|----------|----------|----------|-----------------|

| POR            | 0        | 0     | 0    | 0        | 0        | 0        | 0        | 0               |

| Read/<br>Write | RW       | RW    | RW   | RW       | RW       | RW       | RW       | RW              |

| Bit Name       | Reserved | Sleep | GPIO | Acolumn3 | Acolumn2 | Acolumn1 | Acolumn0 | Voltage Monitor |

### Bit 7: Reserved

## Bit 6: Sleep Interrupt Enable Bit (see 11.4)

0 = Disabled

1 = Enabled

# Bit 5: GPIO Interrupt Enable Bit (see 8.6)

0 = Disabled

1 = Enabled

# Bit [4]: Acolumn 3 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

# Bit [3]: Acolumn 2 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

## Bit [2]: Acolumn 1 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

# Bit [1]: Acolumn 0 Interrupt Enable Bit (see 10.0)

0 = Disabled

1 = Enabled

## Bit 0: Voltage Monitor Interrupt Enable Bit (see 11.5)

0 = Disabled

1 = Enabled

General Interrupt Mask Register (INT\_MSK0, Address = Bank 0, E0h)

If the SPI Master block is being used to receive data, "dummy" bytes must be written to the TX Data Register in order to initiate transmission/reception of each byte.

### 9.5.8.3 Inputs

MISO (master-in, slave-out) is selected by the input multiplexer. The clock input multiplexer selects a clock that runs at twice the desired data rate. The SPIM function divides the input clock by 2 to obtain the 50% duty-cycle required for proper timing. The input multiplexer is controlled by the PSoC block Input Register (DCA04IN-DCA07IN).

### 9.5.8.4 **Outputs**

There are two outputs, both of which can be enabled onto the Global Output bus. The MOSI (master-out, slave-in) data line provides the output serial data. The second output is the bit-clock derived by dividing the input clock by 2 to ensure a 50% duty-cycle. The PSoC block Output Register (DCA04OU-DCA07OU) controls output options.

**Note**: The SPIM function does not provide the SS\_ signal that may be used by a corresponding SPI Slave. However, this can be implemented with a GPIO pin and supporting firmware if desired.

### 9.5.8.5 Interrupts

When enabled, the function generates an interrupt on TX Reg Empty status (Data Register 1 empty). If Mode[1] in the Function Register is set, the SPI Master will generate an interrupt on SPI Complete.

### 9.5.8.6 Usage Notes

### 1. Reading the Status

Reading Control Register 0, which contains the status bits, automatically resets the status bits to 0 with the exception of TX Reg Empty, which is cleared when a byte is written to the TX Data Register (Data Register 1), and the RX Reg Full, which is cleared when a byte is read from the RX Data Register (Data Register 2).

### 2. Using Interrupts

TX Reg Empty status or optionally SPI Complete status generates the block interrupt. Executing the

interrupt routine does not automatically clear status. If SPI Complete is selected as the interrupt source, Control Register 0 (status) must be read in the interrupt routine to clear the status. If TX Reg Empty status is selected, a byte must be written to the TX Data Register (Data Register 1) to clear the status. If the interrupting status is not cleared further interrupts will be suppressed.

# 9.5.9 SPI Slave - Serial Peripheral Interface (SPIS)

## 9.5.9.1 **Summary**

The SPI Slave function provides a full-duplex bi-directional synchronous data transceiver that requires an externally provided bit clock for the data. This function requires a Digital Communications Type PSoC block. It cannot be chained for longer data words. This Digital Communications Type PSoC block supports SPI modes for 0, 1, 2, and 3. See Figure 15: for waveforms of the supported modes.

### 9.5.9.2 Registers

Data Register 0 provides a shift register for both incoming and outgoing data. Output data is written to Data Register 1 (TX Data Register). Input data is read from Data Register 2 (RX Data Register). When Data Register 0 is empty, its value is updated from Data Register 1. As new data bits are shifted in, the transmit bits are shifted out. After the 8 bits are transmitted and received by Data Register 0, the received byte is transferred into Data Register 2 from which it can be read. Simultaneously, the next byte to transmit, if available, is transferred from Data Register 1 into Data Register 0. Control Register 0 (DCA04CR0-DCA07CR0) provides status information and configures the function for one of the four standard modes, which configure the interface based on clock polarity and phase with respect to data.

### 9.5.9.3 Inputs

The SPIS function has three inputs. The Input Register (DCA04IN-DCA07IN) controls the input multiplexer, which selects the MOSI data stream. It also controls the clock selection multiplexer from which the function obtains the master's bit clock. The AUX-IO bits of the Output Register (DCA04OU-DCA07OU) select a Global Input signal from which the SS\_ (Slave Select) signal is obtained. It is important to note that the SS\_ signal can

### 10.7.2.3 Analog Continuous Time Type A Block xx Control 2 Register

CPhase controls which internal clock phase the comparator data is latched on.

can be obtained if the amplifier is being used as a comparator.

CLatch controls whether the latch is active or if it is always transparent.

TestMux – selects block bypass mode for testing and characterization purposes.

CompCap controls whether the compensation capacitor is switched in or not in the op-amp. By not switching in the compensation capacitance, a much faster response Power – encoding for selecting 1 of 4 power levels. The blocks always power up in the off state.

Table 68: Analog Continuous Time Type A Block xx Control 2 Register

| Bit #          | 7      | 6      | 5       | 4          | 3          | 2          | 1        | 0        |

|----------------|--------|--------|---------|------------|------------|------------|----------|----------|

| POR            | 0      | 0      | 0       | 0          | 0          | 0          | 0        | 0        |

| Read/<br>Write | RW     | RW     | RW      | RW         | RW         | RW         | RW       | RW       |

| Bit Name       | CPhase | CLatch | CompCap | TestMux[2] | TestMux[1] | TestMux[0] | Power[1] | Power[0] |

### Bit 7: CPhase

- 0 = Comparator Control latch transparent on PHI1

- 1 = Comparator Control latch transparent on PHI2

### Bit 6: CLatch

- 0 = Comparator Control latch is always transparent

- 1 = Comparator Control latch is active

## Bit 5: CompCap

- 0 = Comparator Mode

- 1 = Op-amp Mode

### Bit [4:2]: TestMux [2:0] Select block bypass mode for testing and characterization purposes

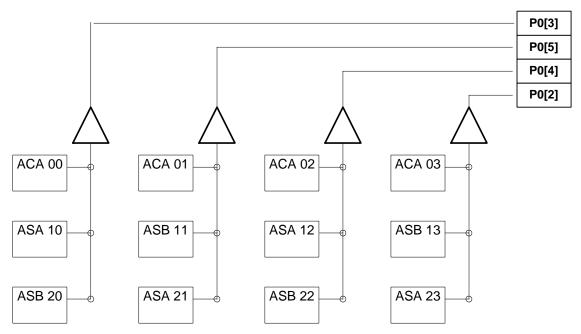

|                           | <u>ACA00</u> | <u>ACA01</u> | <u>ACA02</u> | <u>ACA03</u> |

|---------------------------|--------------|--------------|--------------|--------------|

| 1 0 0 = Positive Input to | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

| 1 0 1 = AGND to           | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

| 1 1 0 = REFLO to          | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

| 1 1 1 = REFHI to          | ABUS0        | ABUS1        | ABUS2        | ABUS3        |

|                           |              |              |              |              |

$0 \times x = All Paths Off$

### Bit [1:0]: Power [1:0] Encoding for selecting 1 of 4 power levels

0.0 = Off

$0.1 = Low (60 \mu A)$

$1.0 = Med (150 \mu A)$

$1.1 = High (500 \mu A)$

Analog Continuous Time Block 00 Control 2 Register (ACA00CR2, Address = Bank 0/1, 73h)

Analog Continuous Time Block 01 Control 2 Register (ACA01CR2, Address = Bank 0/1, 77h)

Analog Continuous Time Block 02 Control 2 Register (ACA02CR2, Address = Bank 0/1, 7Bh)

Analog Continuous Time Block 03 Control 2 Register (ACA03CR2, Address = Bank 0/1, 7Fh)

85

# 10.8 Analog Switch Cap Type A PSoC Blocks

### 10.8.1 Introduction

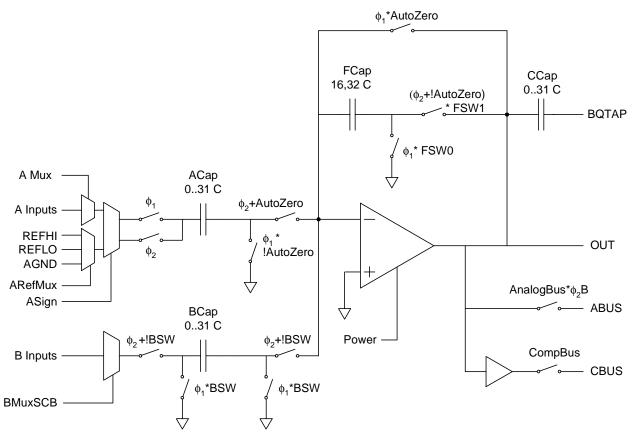

The Analog Switch Cap Type A PSoC blocks are built around an operational amplifier. There are several analog muxes that are controlled by register-bit settings in the control registers that determine the signal topology inside the block. There are also four arrays of unit value capacitors that are located in the feedback path for the op-amp, and are switched by two phase clocks, PHI1 and PHI2. These four capacitor arrays are labeled A Cap Array, B Cap Array, C Cap Array, and F Cap Array. There is also an analog comparator connected to the output OUT, which converts analog comparisons into digital signals.

There are three discrete outputs from this block. These outputs are:

- The analog output bus (ABUS), which is an analog bus resource that is shared by all of the analog blocks in the analog column for that block.

- The comparator bus (CBUS), which is a digital bus that is a resource that is shared by all of the analog blocks in a column for that block.

- The output bus (OUT), which is an analog bus resource that is shared by all of the analog blocks in a column and connects to one of the analog output buffers, to send a signal externally to the device.

SC Integrator Block A supports Delta-Sigma, Successive Approximation and Incremental A/D Conversion, Capacitor DACs, and SC filters. It has three input arrays of binarily-weighted switched capacitors, allowing user programmability of the capacitor weights. This provides summing capability of two (CDAC) scaled inputs, and a non-switched capacitor input. Since the input of SC Block A has this additional switched capacitor, it is configured for the input stage of such a switched capacitor biquad filter. When followed by an SC Block B Integrator, this combination of blocks can be used to provide a full Switched Capacitor Biquad.

### Table 69: Analog Switch Cap Type A Block xx Control 0 Register, continued

```

Bit 7: FCap F Capacitor value selection bit 0 = 16 capacitor units 1 = 32 capacitor units

```

**Bit 6**: <u>ClockPhase</u> Clock phase select, will invert clocks internal to the blocks. During normal operation of an SC block for the amplifier of a column enabled to drive the output bus, the connection is only made for the last half of PHI2 (during PHI1 and for the first half of PHI2, the output bus floats at the last voltage to which it was driven). This forms a sample and hold operation using the output bus and its associated capacitance. This design prevents the output bus from being perturbed by the intermediate states of the SC operation (often a reset state for PHI1 and settling to the valid state during PHI2)

Following are the exceptions: 1) If the ClockPhase bit in CR0 (for the SC block in question) is set to 1, then the output is enabled for the whole of PHI2. 2) If the SHDIS signal is set in bit 6 of the Analog Clock Select Register, then sample and hold operation is disabled for all columns and all enabled outputs of SC blocks are connected to their respective output busses for the entire period of their respective PHI2s

```

0 = Internal PHI1 = External PHI1

1 = Internal PHI2 = External PHI2

```

This bit also affects the latching of the comparator output (CBUS). Both clock phases, PHI1 and PHI2, are involved in the output latching mechanism. The capture of the next value to be output from the latch (capture point event) happens during the falling edge of one clock phase, and the rising edge of the other clock phase will cause the value to come out (output point event). This bit determines which clock phase triggers the capture point event, and the other clock will trigger the output point event. The value output to the comparator bus will remain stable between output point events.

0 = Capture Point Event triggered by Falling PHI2, Output Point Event triggered by Rising PHI1 1 = Capture Point Event triggered by Falling PHI1, Output Point Event triggered by Rising PHI2

### Bit 5: ASign

0 = Input sampled on Internal PHI1, Reference Input sampled on internal PHI2 1 = Input sampled on Internal PHI2, Reference Input sampled on internal PHI1

Bit [4:0]: ACap [4:0] Binary encoding for 32 possible capacitor sizes for A Capacitor:

```

0\ 0\ 0\ 0\ 0 = 0 Capacitor units in array

10000 = 16 Capacitor units in array

0\ 0\ 0\ 1 = 1 Capacitor units in array

1 0 0 0 1 = 17 Capacitor units in array

0\ 0\ 0\ 1\ 0 = 2 Capacitor units in array

1 0 0 1 0 = 18 Capacitor units in array

0\ 0\ 1\ 1 = 3 Capacitor units in array

1 0 0 1 1 = 19 Capacitor units in array

0\ 0\ 1\ 0\ 0 = 4 Capacitor units in array

1 0 1 0 0 = 20 Capacitor units in array

0\ 0\ 1\ 0\ 1 = 5 Capacitor units in array

1 0 1 0 1 = 21 Capacitor units in array

0.0110 = 6 Capacitor units in array

1010 = 22 Capacitor units in array

0\ 0\ 1\ 1\ 1 = 7 Capacitor units in array

1 0 1 1 1 = 23 Capacitor units in array

0.1000 = 8 Capacitor units in array

1\ 1\ 0\ 0\ 0 = 24 Capacitor units in array

0.1001 = 9 Capacitor units in array

1 1 0 0 1 = 25 Capacitor units in array

0.1010 = 10 Capacitor units in array

1 1 0 1 0 = 26 Capacitor units in array

1 1 0 1 1 = 27 Capacitor units in array

0.1011 = 11 Capacitor units in array

0.1100 = 12 Capacitor units in array

1\ 1\ 1\ 0\ 0 = 28 Capacitor units in array

0 1 1 0 1 = 13 Capacitor units in array

1 1 1 0 1 = 29 Capacitor units in array

0.1110 = 14 Capacitor units in array

1 1 1 1 0 = 30 Capacitor units in array

0.1111 = 15 Capacitor units in array

1 \ 1 \ 1 \ 1 = 31 Capacitor units in array

```

```

Analog Switch Cap Type A Block 10 Control 0 Register (ASA10CR0, Address = Bank 0/1, 80h) Analog Switch Cap Type A Block 12 Control 0 Register (ASA12CR0, Address = Bank 0/1, 88h) Analog Switch Cap Type A Block 21 Control 0 Register (ASA21CR0, Address = Bank 0/1, 94h) Analog Switch Cap Type A Block 23 Control 0 Register (ASA23CR0, Address = Bank 0/1, 9Ch)

```

### 10.8.3.2 Analog Switch Cap Type A Block xx Control 1 Register

ACMux controls the input muxing for both the A and C capacitor branches. The high order bit, ACMux[2], selects one of two inputs for the C branch. However, when the bit is high, it also overrides the two low order bits, forcing the A and C branches to the same source.

The resulting condition is used to construct low pass biquad filters.

The BCap bits set the value of the capacitor in the B path.

Table 70: Analog Switch Cap Type A Block xx Control 1 Register

| Bit #          | 7        | 6        | 5        | 4       | 3       | 2       | 1       | 0       |

|----------------|----------|----------|----------|---------|---------|---------|---------|---------|

| POR            | 0        | 0        | 0        | 0       | 0       | 0       | 0       | 0       |

| Read/<br>Write | RW       | RW       | RW       | RW      | RW      | RW      | RW      | RW      |

| Bit Name       | ACMux[2] | ACMux[1] | ACMux[0] | BCap[4] | BCap[3] | BCap[2] | BCap[1] | BCap[0] |

**Bit** [7:5] **ACMux** [2:0] Encoding for selecting A and C inputs. (Note that available mux inputs vary by individual PSoC block.)

| <u>ASA10</u>              | <u>ASA</u> | <u>\21</u> | AS/      | <u>\12</u> | ASA:       | <u>23</u> |

|---------------------------|------------|------------|----------|------------|------------|-----------|

| A Inputs C Inputs         | A Inputs   | C Inputs   | A Inputs | C Inputs   | A Inputs C | C Inputs  |

| 0 0 0 = ACA00 ACA00       | ASB11      | ASB11      | ACA02    | ACA02      | ASB13      | ASB13     |

| 0 0 1 = ASB11 ACA00       | ASB20      | ASB11      | ASB13    | ACA02      | ASB22      | ASB13     |

| 0 1 0 = REFHI ACA00       | REFHI      | ASB11      | REFHI    | ACA02      | REFHI      | ASB13     |

| 0 1 1 = ASB20 ACA00       | Vtemp      | ASB11      | ASB22    | ACA02      | ABUS3      | ASB13     |

| 1 0 0 = ACA01Reserved     | ASA10      | Reserved   | ACA03    | Reserved   | ASA12      | Reserved  |

| 1 0 1 = Reserved Reserved | Reserved   | Reserved   | Reserved | Reserved   | Reserved   | Reserved  |

| 1 1 0 = Reserved Reserved | Reserved   | Reserved   | Reserved | Reserved   | Reserved   | Reserved  |

| 1 1 1 = Reserved Reserved | Reserved   | Reserved   | Reserved | Reserved   | Reserved   | Reserved  |

### Bit [4:0]: BCap [4:0] Binary encoding for 32 possible capacitor sizes for B Capacitor:

```

0\ 0\ 0\ 0\ 0 = 0 Capacitor units in array

10000 = 16 Capacitor units in array

0\ 0\ 0\ 1 = 1 Capacitor units in array

1 0 0 0 1 = 17 Capacitor units in array

0\ 0\ 0\ 1\ 0 = 2 Capacitor units in array

1 0 0 1 0 = 18 Capacitor units in array

1 0 0 1 1 = 19 Capacitor units in array

0\ 0\ 0\ 1\ 1 = 3 Capacitor units in array

0\ 0\ 1\ 0\ 0 = 4 Capacitor units in array

1 0 1 0 0 = 20 Capacitor units in array

0 0 1 0 1 = 5 Capacitor units in array

1 0 1 0 1 = 21 Capacitor units in array

1 0 1 1 0 = 22 Capacitor units in array

0.0110 = 6 Capacitor units in array

0\ 0\ 1\ 1\ 1 = 7 Capacitor units in array

1 0 1 1 1 = 23 Capacitor units in array

0\ 1\ 0\ 0\ 0 = 8 Capacitor units in array

1 1 0 0 0 = 24 Capacitor units in array

0.1001 = 9 Capacitor units in array

1 1 0 0 1 = 25 Capacitor units in array

0.1010 = 10 Capacitor units in array

1 1 0 1 0 = 26 Capacitor units in array

1 1 0 1 1 = 27 Capacitor units in array

0.1011 = 11 Capacitor units in array

0 \ 1 \ 1 \ 0 \ 0 = 12 Capacitor units in array

1 1 1 0 0 = 28 Capacitor units in array

0.1101 = 13 Capacitor units in array

1 1 1 0 1 = 29 Capacitor units in array

0.1110 = 14 Capacitor units in array

1 1 1 1 0 = 30 Capacitor units in array

0.1111 = 15 Capacitor units in array

1 1 1 1 1 = 31 Capacitor units in array

```

```

Analog Switch Cap Type A Block 10 Control 1 Register (ASA10CR1, Address = Bank 0/1, 81h) Analog Switch Cap Type A Block 12 Control 1 Register (ASA12CR1, Address = Bank 0/1, 89h) Analog Switch Cap Type A Block 21 Control 1 Register (ASA21CR1, Address = Bank 0/1, 95h) Analog Switch Cap Type A Block 23 Control 1 Register (ASA23CR1, Address = Bank 0/1, 9Dh)

```

Figure 26: Analog Switch Cap Type B PSoC Blocks

## 10.9.2 Registers

## 10.9.2.1 Analog Switch Cap Type B Block xx Control 0 Register

FCap controls the size of the switched feedback capacitor in the integrator.

ClockPhase controls the internal clock phasing relative to the input clock phasing. ClockPhase affects the output of the analog column bus which is controlled by the AnalogBus bit in Control 2 Register (ASB11CR2, ASB13CR2, ASB20CR2, ASB22CR2).

ASign controls the switch phasing of the switches on the bottom plate of the A capacitor. The bottom plate samples the input or the reference.

The ACap bits set the value of the capacitor in the A path.

Table 73: Analog Switch Cap Type B Block xx Control 0 Register

| Bit #          | 7    | 6          | 5     | 4       | 3       | 2       | 1       | 0       |

|----------------|------|------------|-------|---------|---------|---------|---------|---------|

| POR            | 0    | 0          | 0     | 0       | 0       | 0       | 0       | 0       |

| Read/<br>Write | RW   | RW         | RW    | RW      | RW      | RW      | RW      | RW      |

| Bit Name       | FCap | ClockPhase | ASign | ACap[4] | ACap[3] | ACap[2] | ACap[1] | ACap[0] |

The SAR hardware accelerator is a block of specialized hardware designed to sequence the SAR algorithm for efficient A/D conversion. A SAR ADC is implemented conceptually with a DAC of the desired precision, and a comparator. This functionality can be configured from one or more PSoC blocks. For each conversion, the firmware should initialize the ASY\_CR register as defined below, and set the sign bit of the DAC as the first guess in the algorithm. A sequence of OR instructions (Read, Modify, Write) to the DAC (CR0) register is then executed. Each of these OR instructions causes the SAR hardware to read the current state of the comparator, checking the validity of the previous guess. It either clears it or leaves it set, accordingly. The next LSB in the DAC register is also set as the next guess. Six OR instructions will complete the conversion of a 6-bit DAC. The resulting DAC code, which matches the input voltage to within 1 LSB, is then read back from the DAC CR0 register.

### 10.11.1 Analog Stall and Analog Stall Lockup

Stall lockup affects the operation of stalled IO writes, such as DAC writes and the stalled IOR of the SAR hard-

ware accelerator. The DAC and SAR User Modules operate in this mode. The analog column clock frequency must not be a power of two multiple (2, 4, 8...) higher than the CPU clock frequency. Under this condition, the CPU will never recover from a stall.

See the list of relationships (in MHz) that will fail:

Table 78: Analog Frequency Relationships

| Analog Column Clock | CPU Clock              |

|---------------------|------------------------|

| 3.                  | 1.5, 0.75, .018, 0.093 |

| 1.5                 | 0.75, 0.18, 0.093      |

| 0.75                | 0.18, 0.093            |

| 0.37                | 0.18, 0.093            |

| 0.18                | 0.093                  |

You can still run the CPU clock slower than the column clock if the relationship is not a power of two multiple. For example, you can run at 0.6 MHz, which is not a power of two multiple of any CPU frequency and therefore any CPU frequency can be selected. If the CPU frequency is greater than or equal to the analog column clock, there is not a problem.

Table 79: Analog Synchronization Control Register

| Bit #          | 7        | 6               | 5               | 4               | 3            | 2             | 1             | 0           |

|----------------|----------|-----------------|-----------------|-----------------|--------------|---------------|---------------|-------------|

| POR            | 0        | 0               | 0               | 0               | 0            | 0             | 0             | 0           |

| Read/<br>Write |          | W               | W               | W               | RW           | RW            | RW            | RW          |

| Bit Name       | Reserved | SARCOUNT<br>[2] | SARCOUNT<br>[1] | SARCOUNT<br>[0] | SAR-<br>SIGN | SARCOL<br>[1] | SARCOL<br>[0] | SYN-<br>CEN |

### Bit 7: Reserved

**Bit [6:4]**: **SARCOUNT [2:0]** Initial SAR count. Load this field with the number of bits to process. In a typical 6-bit SAR, the value would be 6

**Bit 3**: **SARSIGN** Adjust the SAR comparator based on the type of block addressed. In a DAC configuration with more than one PSoC block (more than 6-bits), this bit would be 0 when processing the most significant block and 1 when processing the least significant block. This is because the least significant block of a DAC is an inverting input to the most significant block

**Bit [2:1]**: **SARCOL [1:0]** Column select for SAR comparator input. The DAC portion of the SAR can reside in any of the appropriate positions in the analog PSOC block array. However, once the comparator block is positioned (and it is possible to have the DAC and comparator in the same block), this should be the column selected

Bit 0: <u>SYNCEN</u> Set to 1, will stall the CPU until the rising edge of PHI1, if a write to a register within an analog Switch Cap block takes place

Analog Synchronization Control Register (ASY\_CR, Address = Bank 0, 65h)

# 10.12.3 Analog Output Buffers

The user has the option to output up to four analog signals on the pins of the device. This is done by enabling the analog output buffers associated with each Analog Column. The enable bits for the analog output buffers are contained in the Analog Output Buffer Control Register (ABF\_CR).

Figure 28: Analog Output Buffers

# 11.5 Supply Voltage Monitor

The Supply Voltage Monitor detector generates an interrupt whenever Vcc drops below a pre-programmed value. There are eight voltage trip points that are selectable by setting the VM [2:0] bit in the Voltage Monitor

Control Register (VLT\_CR). These bits also select the Switch Mode Pump trip points. The Supply Voltage Monitor will remain active when the device enters sleep mode.

Table 96: Voltage Monitor Control Register

| Bit #          | 7   | 6        | 5        | 4        | 3        | 2      | 1      | 0      |

|----------------|-----|----------|----------|----------|----------|--------|--------|--------|

| POR            | 0   | 0        | 0        | 0        | 0        | 0      | 0      | 0      |

| Read/<br>Write | W   |          |          |          |          | W      | W      | W      |

| Bit Name       | SMP | Reserved | Reserved | Reserved | Reserved | VM [2] | VM [1] | VM [0] |

Bit 7: SMP Disables SMP function

0 = Switch Mode Pump enabled, default

1 = Switch Mode Pump disabled

Bit 6: Reserved

Bit 5: Reserved

Bit 4: Reserved

Bit 3: Reserved

### Bit [2:0]: VM [2:0]

1 0 1 = 4.48 Trip Voltage 1 0 1 = 4.64 Trip Voltage 1 1 0 = 4.65 Trip Voltage 1 1 0 = 4.82 Trip Voltage

1 1 0 = 4.56 Trip Voltage 1 1 0 = 4.82 Trip Voltage 1 1 1 = 4.64 Trip Voltage 1 1 1 = 5.00 Trip Voltage

Voltage Monitor Control Register (VLT\_CR, Address = Bank 1, E3h)

<sup>1.</sup> Voltages are ideal typical values. Tolerances are in Table 104 on page 129.

133

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges, 3.3V +/- 10% and -40°C <=  $T_A$  <= 85°C. Typical parameters apply to 5V at 25°C and are for design guidance only. For 5V operation, see Table 109 on page 132.

Table 110: 3.3V DC Analog Output Buffer Specifications

| Symbol | 3.3V DC Analog Output Buffer Specifications                                             | Minimum                                                  | Typical    | Maximum                                                  | Unit     |

|--------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|------------|----------------------------------------------------------|----------|

|        | Input Offset Voltage (Absolute Value)                                                   | -                                                        | 3          | 12                                                       | mV       |

|        | Average Input Offset Voltage Drift                                                      | -                                                        | +6         | -                                                        | μV/°C    |

|        | Common-Mode Input Voltage Range                                                         | .5                                                       | -          | V <sub>cc</sub> - 1.0                                    | V        |

|        | Output Resistance Bias = Low Bias = High                                                | -                                                        | 1          | -                                                        | Ω        |

|        | High Output Voltage Swing (Load = 32 ohms to V <sub>CC</sub> /2) Bias = Low Bias = High | .5 x V <sub>cc</sub> + 1.3<br>.5 x V <sub>cc</sub> + 1.3 | -          | -                                                        | V<br>V   |

|        | Low Output Voltage Swing (Load = 32 ohms to $V_{cc}/2$ )<br>Bias = Low<br>Bias = High   | -                                                        | -          | .5 x V <sub>cc</sub> - 1.3<br>.5 x V <sub>cc</sub> - 1.3 | V<br>V   |

|        | Supply Current Including Bias Cell (No Load) Bias = Low Bias = High                     | -                                                        | 0.8<br>2.0 | 2.0<br>4.3                                               | mA<br>mA |

|        | Supply Voltage Rejection Ratio                                                          | 80                                                       | -          | -                                                        | dB       |

Table 113: 3.3V DC Analog Reference Specifications

| Symbol | 3.3V DC Analog Reference Specifications                                               | Minimum                | Typical                | Maximum                | Unit |  |

|--------|---------------------------------------------------------------------------------------|------------------------|------------------------|------------------------|------|--|

|        | AGND = Vcc/2 <sup>1</sup><br>CT Block Bias = High                                     | Vcc/2 - 0.007          | Vcc/2 - 0.003          | Vcc/2 + 0.002          | V    |  |

|        | AGND = 2*BandGap <sup>1</sup><br>CT Block Bias = High                                 |                        | Not Allowe             | ed                     |      |  |

|        | AGND = P2[4] (P2[4] = Vcc/2)<br>CT Block Bias = High                                  | P24 - 0.008            | P24 + 0.001            | P24 + 0.009            | V    |  |

|        | AGND Column to Column Variation (AGND=Vcc/<br>2) <sup>1</sup><br>CT Block Bias = High | -0.034                 | 0.000                  | 0.034                  | mV   |  |

|        | REFHI = Vcc/2 + BandGap<br>Ref Control Bias = High                                    |                        | Not Allowe             | ed                     |      |  |

|        | REFHI = 3*BandGap<br>Ref Control Bias = High                                          | Not Allowed            |                        |                        |      |  |

|        | REFHI = 2*BandGap + P2[6] (P2[6] = 0.5V)<br>Ref Control Bias = High                   | Not Allowed            |                        |                        |      |  |

|        | REFHI = P2[4] + BandGap (P2[4] = Vcc/2)<br>Ref Control Bias = High                    |                        | Not Allowe             | ed                     |      |  |

|        | REFHI = P2[4] + P2[6] (P2[4] = Vcc/2, P2[6] = 0.5V)<br>Ref Control Bias = High        | P2[4]+P2[6] -<br>0.075 | P2[4]+P2[6] -<br>0.009 | P2[4]+P2[6]+<br>0.057  | V    |  |

|        | REFLO = Vcc/2 - BandGap<br>Ref Control Bias = High                                    |                        | Not Allowe             | ed                     |      |  |

|        | REFLO = BandGap<br>Ref Control Bias = High                                            |                        | Not Allowe             | ed                     |      |  |

|        | REFLO = 2*BandGap - P2[6] (P2[6] = 0.5V)<br>Ref Control Bias = High                   | Not Allowed            |                        |                        |      |  |

|        | REFLO = P2[4] - BandGap (P2[4] = Vcc/2)<br>Ref Control Bias = High                    | Not Allowed            |                        |                        |      |  |

|        | REFLO = P2[4]-P2[6] (P2[4] = Vcc/2, P2[6] = 0.5V)<br>Ref Control Bias = High          | P2[4]-P2[6] -<br>0.048 | P24-P26 +<br>0.022     | P2[4]-P2[6] +<br>0.092 | V    |  |

<sup>1.</sup> AGND tolerance includes the offsets of the local buffer in the PSoC block. Bandgap voltage is  $1.3V \pm 2\%$

# 13.2.7 DC Analog PSoC Block Specifications

The following table lists guaranteed maximum and minimum specifications include both voltage ranges, 5V +/- 5% and 3.3V +/- 10% and the temperature range -40°C

<= T<sub>A</sub> <= 85°C. Typical parameters apply to 3.3V and 5V at 25°C and are for design guidance only.

Table 114: DC Analog PSoC Block Specifications

| Symbol | DC Analog PSoC Block Specifications   | Minimum | Typical | Maximum | Unit |

|--------|---------------------------------------|---------|---------|---------|------|

|        | Resistor Unit Value (Continuous Time) | -       | 45      | -       | kΩ   |

|        | Capacitor Unit Value (Switch Cap)     | -       | 70      | -       | fF   |