Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | SPI, UART/USART                                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 16KB (16K × 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 1x8b, 1x11b, 1x12b; D/A 1x9b                                            |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 48-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c26643-24pvxi |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 1: Block Diagram                                         | 13  |

|-----------------------------------------------------------------|-----|

| Figure 2: CY8C25122                                             | 15  |

| Figure 3: CY8C26233                                             | 15  |

| Figure 4: 26443 PDIP/SOIC/SSOP                                  | 16  |

| Figure 5: 26643 TQFP                                            |     |

| Figure 6: 26643 PDIP/SSOP                                       | 18  |

| Figure 7: General Purpose I/O Pins                              |     |

| Figure 8: External Crystal Oscillator Connections               | 37  |

| Figure 9: PSoC MCU Clock Tree of Signals                        | .39 |

| Figure 10: Interrupts Overview                                  | .43 |

| Figure 11: GPIO Interrupt Enable Diagram                        |     |

| Figure 12: Digital Basic and Digital Communications PSoC Blocks | .49 |

| Figure 13: Polynomial LFSR                                      | .65 |

| Figure 14: Polynomial PRS                                       | .65 |

| Figure 15: SPI Waveforms                                        | 68  |

| Figure 16: Array of Analog PSoC Blocks                          | 72  |

| Figure 17: Analog Reference Control Schematic                   | 73  |

| Figure 18: NMux Connections                                     |     |

| Figure 19: PMux Connections                                     | 79  |

| Figure 20: RBotMux Connections                                  | 79  |

| Figure 21: Analog Continuous Time PSoC Blocks                   | 81  |

| Figure 22: Analog Switch Cap Type A PSoC Blocks                 | 86  |

| Figure 23: AMux Connections                                     | 87  |

| Figure 24: CMux Connections                                     | 87  |

| Figure 25: BMuxSCA/SCB Connections                              | 88  |

| Figure 26: Analog Switch Cap Type B PSoC Blocks                 | 95  |

| Figure 27: Analog Input Muxing                                  |     |

| Figure 28: Analog Output Buffers                                | 105 |

| Figure 29: Multiply/Accumulate Block Diagram                    |     |

| Figure 30: Decimator Coefficients                               | 112 |

| Figure 31: Execution Reset                                      | 115 |

| Figure 32: Three Sleep States                                   |     |

| Figure 33: Switch Mode Pump                                     | 119 |

| Figure 34: Programming Wave Forms                               | 124 |

| Figure 35: PSoC Designer Functional Flow                        |     |

| Figure 36: CY8C25xxx/CY8C26xxx Voltage Frequency Graph          | 127 |

| Figure 37: 44-Lead Thin Plastic Quad Flat Pack A44              | 143 |

| Figure 38: 20-Pin Shrunk Small Outline Package O20              |     |

| Figure 39: 28-Lead (210-Mil) Shrunk Small Outline Package O28   | 145 |

| Figure 40: 48-Lead Shrunk Small Outline Package O48             | 145 |

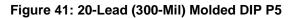

| Figure 41: 20-Lead (300-Mil) Molded DIP P5                      | 146 |

| Figure 42: 28-Lead (300-Mil) Molded DIP P21                     | 146 |

| Figure 43: 48-Lead (600-Mil) Molded DIP P25                     | 147 |

| Figure 44: 20-Lead (300-Mil) Molded SOIC S5                     |     |

| Figure 45: 28-Lead (300-Mil) Molded SOIC S21                    | 148 |

#### 2.2.3 Index Register

| Table 10: | Index Register (CPU_ | X) |

|-----------|----------------------|----|

|-----------|----------------------|----|

| Bit #          | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|----------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| POR            | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/<br>Write | System <sup>1</sup> |

| Bit Name       | Data [7]            | Data [6]            | Data [5]            | Data [4]            | Data [3]            | Data [2]            | Data [1]            | Data [0]            |

Bit [7:0]: Data [7:0] 8-bit data value holds an index for any instruction that uses an indexed addressing mode

1. System - not directly accessible by the user

#### 2.2.4 Stack Pointer Register

#### Table 11: Stack Pointer Register (CPU\_SP)

| Bit #          | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|----------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| POR            | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| Read/<br>Write | System <sup>1</sup> |

| Bit Name       | Data [7]            | Data [6]            | Data [5]            | Data [4]            | Data [3]            | Data [2]            | Data [1]            | Data [0]            |

|                |                     |                     |                     |                     |                     |                     |                     |                     |

Bit [7:0]: Data [7:0] 8-bit data value holds a pointer to the current top-of-stack

1. System - not directly accessible by the user

## 2.2.5 Program Counter Register

#### Table 12: Program Counter Register (CPU\_PC)

| Bit #          | 15           | 14           | 13           | 12           | 11           | 10           | 9           | 8           | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|----------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| POR            | 0            | 0            | 0            | 0            | 0            | 0            | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| Read/<br>Write | 1            | 1            | 1            | 1            | 1            | 1            | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           | 1           |

| Bit<br>Name    | Data<br>[15] | Data<br>[14] | Data<br>[13] | Data<br>[12] | Data<br>[11] | Data<br>[10] | Data<br>[9] | Data<br>[8] | Data<br>[7] | Data<br>[6] | Data<br>[5] | Data<br>[4] | Data<br>[3] | Data<br>[2] | Data<br>[1] | Data<br>[0] |

Bit [15:0]: Data [15:0] 16-bit data value is the low-order/high-order byte of the Program Counter

1. System - not directly accessible by the user

# 2.3 Addressing Modes

## 2.3.1 Source Immediate

The result of an instruction using this addressing mode is placed in the A register, the F register, the SP register, or the X register, which is specified as part of the instruction opcode. Operand 1 is an immediate value that serves as a source for the instruction. Arithmetic instructions require two sources. Instructions using this addressing mode are two bytes in length.

#### Table 13: Source Immediate

| Opcode      | Operand 1       |

|-------------|-----------------|

| Instruction | Immediate Value |

# 6.0 I/O Registers

# 6.1 **Port Data Registers**

#### Table 28:Port Data Registers

| Bit #      | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|

| POR        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| Read/Write | RW       |

| Bit Name   | Data [7] | Data [6] | Data [5] | Data [4] | Data [3] | Data [2] | Data [1] | Data [0] |

Bit [7:0]: Data [7:0] When written is the bits for output on port pins. When read is the state of the port pins

Port 0 Data Register (PRT0DR, Address = Bank 0, 00h) Port 1 Data Register (PRT1DR, Address = Bank 0, 04h) Port 2 Data Register (PRT2DR, Address = Bank 0, 08h) Port 3 Data Register (PRT3DR, Address = Bank 0, 0Ch) Port 4 Data Register (PRT4DR, Address = Bank 0, 10h) Port 5 Data Register (PRT5DR, Address = Bank 0, 14h) **Note**: Port 5 is 4-bits wide, Bit [3:0]

# 6.2 Port Interrupt Enable Registers

#### Table 29: Port Interrupt Enable Registers

| Bit #                                                                                                    | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |  |

|----------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|--|

| POR                                                                                                      | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |  |

| Read/Write                                                                                               | W          | W          | W          | W          | W          | W          | W          | W          |  |

| Bit Name                                                                                                 | Int En [7] | Int En [6] | Int En [5] | Int En [4] | Int En [3] | Int En [2] | Int En [1] | Int En [0] |  |

| <b>Bit [7:0]</b> : Int En [7:0] When written sets the pin interrupt state 0 = Interrupt disabled for pin |            |            |            |            |            |            |            |            |  |

1 = Interrupt enabled for pin

Port 0 Interrupt Enable Register (PRT0IE, Address = Bank 0, 01h) Port 1 Interrupt Enable Register (PRT1IE, Address = Bank 0, 05h) Port 2 Interrupt Enable Register (PRT2IE, Address = Bank 0, 09h) Port 3 Interrupt Enable Register (PRT3IE, Address = Bank 0, 0Dh) Port 4 Interrupt Enable Register (PRT4IE, Address = Bank 0, 11h) Port 5 Interrupt Enable Register (PRT5IE, Address = Bank 0, 15h) **Note**: Port 5 is 4-bits wide

# 7.0 Clocking

# 7.1 Oscillator Options

## 7.1.1 Internal Main Oscillator

The internal main oscillator outputs two frequencies, 48 MHz and 24 MHz. In the absence of a high-precision input source from the external oscillator, the accuracy of this circuit is +/- 2.5% (between 0°C and +85°C). No external components are required to achieve this level of accuracy. The Internal Main Oscillator Trim Register (IMO\_TR) is used to calibrate this oscillator into specified tolerance. Factory-programmed trim values are available for 5.0V and 3.3V operation. The 5.0V value is loaded in the IMO\_TR register upon reset. This register must be adjusted when the operating voltage is outside the range

for which factory calibration was set. The factory-programmed trim value is selected using the Table Read Supervisor Call, and is documented in 11.8.

There is an option to phase lock this oscillator to the External Crystal Oscillator. The choice of crystal and its inherent accuracy will determine the overall accuracy of the oscillator. The External Crystal Oscillator must be stable prior to locking the frequency of the Internal Main Oscillator to this reference source.

| Bit #      | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| POR        | FS <sup>1</sup> |

| Read/Write | W               | W               | W               | W               | W               | W               | W               | W               |

| Bit Name   | IMO Trim<br>[7] | IMO Trim<br>[6] | IMO Trim<br>[5] | IMO Trim<br>[4] | IMO Trim<br>[3] | IMO Trim<br>[2] | IMO Trim<br>[1] | IMO Trim<br>[0] |

|            |                 |                 |                 |                 |                 |                 |                 |                 |

Table 35:

Internal Main Oscillator Trim Register

Bit [7:0]: <u>IMO Trim [7:0]</u> Data value stored will alter the trimmed frequency of the Internal Main Oscillator. A larger value in this register will increase the speed of the Internal Main Oscillator

1. FS = Factory set trim value

Internal Main Oscillator Trim Register (IMO\_TR, Address = Bank 1, E8h)

## 7.1.2 Internal Low Speed Oscillator

An internal low speed oscillator of nominally 32 kHz is available to generate sleep wake-up interrupts and Watchdog resets if the user does not want to attach a 32.768 kHz watch crystal. This oscillator can also be used as a clocking source for the digital PSoC blocks.

The oscillator operates in two different modes. A trim value is written to the Internal Low Speed Oscillator Trim Register (ILO\_TR), shown below, upon reset. See section 13.0 for accuracy information. When the IC is put into sleep mode this oscillator drops into an ultra low current state and the accuracy is reduced.

This register sets the adjustment for the Internal Low Speed Oscillator. The value placed in this register is based on factory testing. It is recommended that the user not alter this value.

| Bit #                                                                                                                                                                              | 7                                                                                                                                                                                                                                                      | 6                                            | 5        | 4             | 3            | 2       | 1       | 0       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|---------------|--------------|---------|---------|---------|

| POR                                                                                                                                                                                | 0                                                                                                                                                                                                                                                      | 0                                            | 0        | 0             | 0            | 0       | 0       | 0       |

| Read/<br>Write                                                                                                                                                                     | RW                                                                                                                                                                                                                                                     | RW                                           | RW       | RW            | RW           | RW      | RW      | RW      |

| Bit Name                                                                                                                                                                           | 32k Select                                                                                                                                                                                                                                             | PLL Mode                                     | Reserved | Sleep [1]     | Sleep [0]    | CPU [2] | CPU [1] | CPU [0] |

| 1 = Externa<br><b>Bit</b> 6: <u>PLL I</u><br>0 = Disabled<br>1 = Enabled<br><b>Bit</b> 5: <b>Rese</b><br><b>Bit</b> [4:3]: <u>SI</u><br>0 0 = 512 H<br>0 1 = 64 Hz<br>1 0 = 8 Hz c | low precision<br>I Crystal Osci<br>I Crystal Osci<br>d<br>I, Internal Mai<br>rved<br>eep [1:0]<br>z or 1.95 ms p<br>or 15.6 ms p<br>or 15.6 ms p<br>or 15.6 ms p<br>or 125 ms period<br>PU [2:0]<br>Hz<br>Hz<br>Hz<br>Hz<br>MHz<br>MHz<br>KHz<br>5 KHz | llator<br>n Oscillator is<br>period<br>eriod |          | ternal Crysta | l Oscillator |         |         |         |

#### Table 40: Oscillator Control 0 Register

Oscillator Control 0 Register (OSC\_CR0, Address = Bank 1, E0h)

#### Table 41: Oscillator Control 1 Register

| Bit #          | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|----------------|----------|----------|----------|----------|----------|----------|----------|----------|

| POR            | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| Read/<br>Write | RW       |

| Bit Name       | 24V1 [3] | 24V1 [2] | 24V1 [1] | 24V1 [0] | 24V2 [3] | 24V2 [2] | 24V2 [1] | 24V2 [0] |

**Bit [7:4]**: <u>24V1 [3:0]</u> 4-bit data value determines the divider value for the **24V1** system-clocking signal. Note that the 4-bit data value equals n-1, where n is the desired divider value, as illustrated in PSoC MCU Clock Tree of Signals. See Table 42 on page 41.

**Bit [3:0]**: <u>**24V2 [3:0]**</u> 4-bit data value determines the divider value for the **24V2** system-clocking signal. Note that the 4-bit data value equals n-1, where n is the desired divider value, as illustrated in the PSoC MCU Clock Tree of Signals. See Table 42 on page 41.

Oscillator Control 1 Register (OSC\_CR1, Address = Bank 1, E1h)

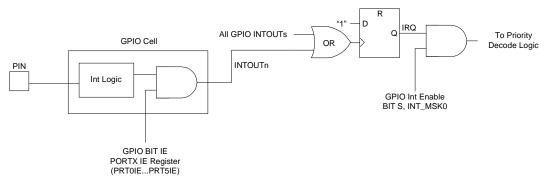

# 8.6 GPIO Interrupt

GPIO Interrupts are polarity configurable and pin-wise maskable (within each Port's pin configuration registers). They all share the same interrupt priority and vector.

Any general purpose I/O can be used as an interrupt source. The GPIO bit in the General Interrupt Mask Register (INT\_MSK0) must be set to enable pin interrupts, as well as the enable bits for each pin, which are located in the Port x Interrupt Enable Registers (PRTxIE). There are user selectable options to generate an interrupt on 1) any change from the last read state, 2) rising edge, and 3) falling edge.

When Interrupt on Change is selected, the state of the GPIO pin is stored when the port is read. Changes from this state will then assert the interrupt, if enabled.

#### Figure 11: GPIO Interrupt Enable Diagram

For a GPIO interrupt to occur, the following steps must be taken:

- 1. The pin Drive Mode must be set so the pin can be an input.

- The pin must be enabled to generate an interrupt by setting the appropriate bit in the Port interrupt Enable Register (PRTxIE).

- The edge type for the interrupt must be set in the Port Interrupt Control 0 and Control 1 Registers (PRTxIC0 and PRTxIC1). Edge type must be set to a value other than 00.

- 4. The GPIO bit must be set in the General Interrupt Mask Register (INT\_MSK0).

- 5. The Global Interrupt Enable bit must be set.

6. Because the GPIO interrupts all share the same interrupt vector, the source for the GPIO interrupt must be cleared before any other GPIO interrupt will occur (i.e., the <u>OR</u> gate in Figure 11: "ors" all of the INTOUTn signals together). If any of the INTOUTn signals are high, the flip-flop in Figure 11: will not see a rising edge and no IRQ will occur.

# 9.0 Digital PSoC Blocks

# 9.1 Introduction

PSoC blocks are user configurable system resources. On-chip digital PSoC blocks reduce the need for many MCU part types and external peripheral components. Digital PSoC blocks can be configured to provide a wide variety of peripheral functions. PSoC Designer Software Integrated Development Environment provides automated configuration of PSoC blocks by simply selecting the desired functions. PSoC Designer then generates the proper configuration information and can print a device data sheet unique to that configuration.

Digital PSoC blocks provide up to eight, 8-bit multipurpose timers/counters supporting multiple event timers, real-time clocks, Pulse Width Modulators (PWM), and CRCs. In addition to all PSoC block functions, communication PSoC blocks support full-duplex UARTs and SPI master or slave functions.

As shown in Figure 12:, there are a total of eight 8-bit digital PSoC blocks in this device family configured as a linear array. Four of these are the Digital Basic Type A blocks and four are the Digital Communications Type A blocks. Each of these digital PSoC blocks can be configured independently, or used in combination.

Each digital PSoC block has a unique Interrupt Vector and Interrupt Enable bit. Functions can be stopped or started with a user-accessible Enable bit.

The Timer/Counter/CRC/PRS/Deadband functions are available on the Digital Basic Type A blocks and also the Digital Communications Type A blocks. The UART and SPI communications functions are only available on the Digital Communications Type A blocks.

There are three configuration registers: the Function Register (DBA00FN-DCA07FN) to select the block function and mode, the Input Register (DBA00IN-DCA07IN) to select data input and clock selection, and the Output Register (DBA00OU-DCA07OU) to select and enable function outputs.

The three data registers are designated Data 0 (DBA00DR0-DCA07DR0), Data 1 (DBA00DR1-DCA07DR1), and Data 2 (DBA00DR2-DCA07DR2). The function of these registers and their bit mapping is

dependent on the overall block function selected by the user.

The one Control Register (DBA00CR0-DCA07CR0) is designated Control 0. The function of this register and its bit mapping is dependent on the overall block function selected by the user.

If the CPU frequency is 24 MHz and a PSoC timer/ counter of 24-bits or longer is operating at 48 MHz, a write to the block Control Register to enable it (for example, a call to Timer\_1\_Start) may not start the block properly. In the failure case, the first count will typically be indeterminate as the upper bytes fail to make the first count correctly. However, on the first terminal count, the correct period will be loaded and counted thereafter.

| Bit #                                                                                                                                                                                                                                                       | 7                                                                                                                                                                                            | 6                                                                                                                                                           | 5                                                                                 | 4                                                        | 3                                | 2                  | 1                 | 0            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|--------------------|-------------------|--------------|

| POR                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                            | 0                                                                                                                                                           | 0                                                                                 | 0                                                        | 0                                | 0                  | 0                 | 0            |

| Read/Write                                                                                                                                                                                                                                                  | RW                                                                                                                                                                                           | RW                                                                                                                                                          | RW                                                                                | RW                                                       | RW                               | RW                 | RW                | RW           |

| Bit Name                                                                                                                                                                                                                                                    | Reserved                                                                                                                                                                                     | Reserved                                                                                                                                                    | End                                                                               | Mode 1                                                   | Mode 0                           | Function [2]       | Function [1]      | Function [0] |

| <b>Bit 7: Reserved</b><br><b>Bit 6: Reserved</b><br><b>Bit 5: End</b><br>0 = PSoC block i<br>1 = PSoC block i                                                                                                                                               |                                                                                                                                                                                              |                                                                                                                                                             |                                                                                   | •                                                        |                                  | ) in block DCA07)  |                   |              |

| <b>Bit 4</b> : <u>Mode 1</u> Th<br>Timer: The Mode<br>0 = Less Than of<br>1 = Less Than<br>Counter: The Mode<br>0 = Less Than<br>CRC/PRS: The Mode<br>0 = Transmit: Inte<br>1 = Transmit: Inte<br>SPI: The Mode[1<br>0 = Master: Inter<br>1 = Master: Inter | ne definition of t<br>e [1] bit signifies<br>r Equal<br>ode [1] bit signifi<br>r Equal<br>Mode [1] bit is u<br>Mode [1] bit is u<br>e[1] bit signifies<br>errupt on TX_R<br>errupt on TX Reg | he Mode [1] b<br>the Compare<br>tes the Compare<br>nused in this<br>nused in this<br>the Interrupt<br>eg Empty<br>omplete<br>e Interrupt Ty<br>Empty, Slave | bit depe<br>Type<br>are Typ<br>function<br>function<br>Type (T<br>pe<br>e: Interr | ends on the b<br>e<br>n<br>Transmitter of<br>upt on RX R | lock function<br>nly)<br>eg Full |                    |                   |              |

| Bit 3: Mode 0 Th<br>Timer: The Mode<br>0 = Terminal Cou<br>1 = Compare Tru<br>Counter: The Mod<br>0 = Terminal Cou<br>1 = Compare Tru<br>CRC/PRS: The Mode<br>0 = Receive<br>1 = Transmit<br>SPI: The Mode [1<br>0 = Master<br>1 = Slave                    | e [0] bit signifies<br>unt<br>de<br>ode [0] bit signifi<br>unt<br>Mode [0] bit is u<br>Mode [0] bit is u<br>e [0] bit signifies                                                              | Interrupt Typ<br>ies Interrupt T<br>nused in this<br>inused in this<br>the Direction                                                                        | e<br>ype<br>function<br>functio                                                   | n                                                        | lock function                    | selected           |                   |              |

| <b>Bit [2:0]</b> : <u>Functi</u><br>0 0 0 = Timer (cf<br>0 1 = Counter<br>0 1 0 = CRC/PR<br>0 1 1 = Reserved<br>1 0 0 = Deadban<br>1 0 1 = UART (fu<br>1 1 0 = SPI (func<br>1 1 1 = Reserved                                                                | nainable)<br>(chainable)<br>S (Cyclical Red<br>d<br>for Pulse Wid<br>Inction only ava<br>tion only availa                                                                                    | undancy Che<br>Ith Modulator<br>illable on DCA                                                                                                              | cker or<br>A type b                                                               | Pseudo Ran<br>blocks)                                    |                                  | n determines the b | oasic hardware co | nfiguration  |

| Table 47: | Digital Basic Type A/ Communications Type A Block xx Function Register |

|-----------|------------------------------------------------------------------------|

|-----------|------------------------------------------------------------------------|

Digital Basic Type A Block 00 Function Register(DBA00FN, Address = Bank 1, 20h)Digital Basic Type A Block 01 Function Register(DBA01FN, Address = Bank 1, 24h)Digital Basic Type A Block 02 Function Register(DBA02FN, Address = Bank 1, 24h)Digital Basic Type A Block 03 Function Register(DBA03FN, Address = Bank 1, 28h)Digital Communications Type A Block 04 Function Register(DCA04FN, Address = Bank 1, 30h)

| Bit #          | 7        | 6        | 5                 | 4                 | 3                 | 2             | 1              | 0              |

|----------------|----------|----------|-------------------|-------------------|-------------------|---------------|----------------|----------------|

| POR            | 0        | 0        | 0                 | 0                 | 0                 | 0             | 0              | 0              |

| Read/<br>Write | RW       | RW       | RW                | RW                | RW                | RW            | RW             | RW             |

| Bit Name       | Reserved | Reserved | AUX Out<br>Enable | AUX IO Sel<br>[1] | AUX IO Sel<br>[0] | Out<br>Enable | Out Sel<br>[1] | Out Sel<br>[0] |

Table 50: Digital Basic Type A / Communications Type A Block xx Output Register

## Bit 7: Reserved

Bit 6: Reserved

#### Bit 5: AUX Out Enable

0 = Disable Auxiliary Output

1 = Enable Auxiliary Output (function dependent)

# Bit [4:3]: AUX IO Sel [1:0] Function-dependent selection of auxiliary input or output

0 0 = Drive Global Output[0] (for Digital Blocks 00 to 03) or

- Input from Global Input[4] or Drive Global Output [4] (for Digital Blocks 04 to 07)

- 0 1 = Drive Global Output[1] (for Digital Blocks 00 to 03) **or** Input from Global Input[5] or Drive Global Output[5] (for Digital Blocks 04 to 07)

- 1 0 = Drive Global Output[2] (for Digital Blocks 00 to 03) **or** Input from Global Input[6] or Drive Global Output[6] (for Digital Blocks 04 to 07)

- 1 1 = Drive Global Output[3] (for Digital Blocks 00 to 03) **or** Input from Global Input[7] or Drive Global Output[7] (for Digital Blocks 04 to 07)

#### Bit 2: Out Enable

0 = Disable Primary Output

1 = Enable Primary Output (function dependant)

#### Bit [1:0]: Out Sel [1:0] Primary Output

0 0 = Drive Global Output[0] (for Digital Blocks 00 to 03) or Drive Global Output[4] (for Digital Blocks 04 to 07)

0 1 = Drive Global Output[1] (for Digital Blocks 00 to 03) or Drive Global Output[5] (for Digital Blocks 04 to 07)

- 1 0 = Drive Global Output[2] (for Digital Blocks 00 to 03) or Drive Global Output[6] (for Digital Blocks 04 to 07)

- 1 1 = Drive Global Output[3] (for Digital Blocks 00 to 03) or Drive Global Output[7] (for Digital Blocks 04 to 07)

Digital Basic Type A Block 00 Output Register Digital Basic Type A Block 01 Output Register Digital Basic Type A Block 02 Output Register Digital Basic Type A Block 03 Output Register Digital Communications Type A Block 04 Output Register Digital Communications Type A Block 05 Output Register Digital Communications Type A Block 06 Output Register Digital Communications Type A Block 06 Output Register (DBA00OU, Address = Bank 1, 22h) (DBA01OU, Address = Bank 1, 26h) (DBA02OU, Address = Bank 1, 2Ah) (DBA03OU, Address = Bank 1, 2Eh) (DCA04OU, Address = Bank 1, 32h) (DCA05OU, Address = Bank 1, 36h) (DCA06OU, Address = Bank 1, 3Ah) (DCA07OU, Address = Bank 1, 3Eh)

The Primary Output is the source for "Previous Digital PSoC Block" or "Digital Block 03," selections for the "Clock Source Select" in the Digital Basic Type A/Communications Type A Block xx Input Register (Table 48 on page 51).

A digital PSoC block may have 0, 1, or 2 outputs depending on its function, as shown in the following table:

## 9.5.6.3 Inputs

A baud-rate clock running at 8 times the desired input bit rate is selected by the clock-input multiplexer The serial data input and clock input are controlled by the Input Register (DCA04IN-DCA07IN).

## 9.5.6.4 Outputs

None.

## 9.5.6.5 Interrupts

The function can be configured to generate an interrupt on RXREGFULL (Receive Register Full) status (Data Register 2 is full)

## 9.5.6.6 Usage Notes

1. Reading the Status

Reading Control Register 0, which contains the status bits, automatically resets all status bits to 0 with the exception of RX Reg Full. Reading Data Register 2 (Receive Data Register) clears the RX Reg Full status.

2. Using Interrupts

RX Reg Full status generates an interrupt but the Receive Data Register (Data Register 2) must be read to clear the RX Reg Full status. If this registers is not read in the interrupt routine, the status will not be cleared and further interrupts will be suppressed.

If the stop bit in a transmitted byte is missing, the receiver will declare a framing error. Once this occurs, this missing stop bit can be interpreted as the start bit of the next byte, which will produce another framing error.

## 9.5.7 Universal Asynchronous Transmitter

## 9.5.7.1 Summary

The Universal Asynchronous Transmitter implements the output half of a basic 8-bit UART. Start and Stop bits are generated. Parity bit generation and type are configurable features. This function requires a Digital Communications Type PSoC block. It cannot be chained for longer data words.

## 9.5.7.2 Registers

When Data Register 0 is empty and a new byte has been written to Data Register 1, the function transfers the byte to Data Register 0 and shifts it out along with a start bit, optionally a parity bit and a stop bit. Once Data Register 0 is loaded with the byte to shift out, Data Register 0 can be immediately loaded with the next byte to transmit, acting as a 1 byte transmit buffer. Data Register 2 is not used by this function. The PSoC block's Control Register 0 (DCA04CR0-DCA07CR0) configures the parity type and enable. It also provides status information to enable detection of transmission complete.

## 9.5.7.3 Inputs

A baud-rate clock running at 8 times the desired output bit rate is selected by the clock-input multiplexer controlled by the PSoC block Input Register (DCA04IN-DCA07IN). The Data Input multiplexer is ignored by this function.

# 9.5.7.4 Outputs

The transmitter's serial data output appears at the PSoC block output and may be driven onto one of the Global Output bus lines. The PSoC block Output Register (DCA04OU-DCA07OU) controls output options.

## 9.5.7.5 Interrupts

If enabled, the function will generate an interrupt when the TX Reg Empty status is set (Data Register 1 is empty). Optionally, the interrupt can be set to TX Complete status, which indicates all bits of a given byte have been sent, including framing bits. This option is selected based on the Mode[1] bit in the Function Register.

## 9.5.7.6 Usage Notes

1. TX Reg Empty Interrupt

An initial byte must be written to the TX Data Register (Data Register 1) to enable subsequent TX Reg Empty status interrupts. This does not apply if the TX Complete interrupt source is selected.

2. Reading the Status

Reading Control Register 0, which contains the status bits, automatically resets the status bits to 0, except for TX Reg Empty. TX Reg Empty is automatically cleared when a byte is written to the TX Data Register (Data Register 1).

3. Using CPU Interrupts

TX Reg Empty status or optionally TX Complete status generates the block interrupt. Executing the interrupt routine does not automatically clear status. If TX Complete is selected as the interrupt source, Control Register 0 (status) must be read in the interrupt routine to clear the status. If TX Reg Empty is selected, a byte must be written to the TX Data Register (Data Register 1) to clear the status. If the status is not cleared, further interrupts will be suppressed.

# 9.5.8 SPI Master - Serial Peripheral Interface (SPIM)

#### 9.5.8.1 Summary

The SPI Master function provides a full-duplex synchronous data transceiver that also generates a bit clock for the data. This function requires a Digital Communications Type PSoC block. It cannot be chained for longer data words. This Digital Communications Type PSoC block supports SPI modes for 0, 1, 2, and 3. See Figure 15: for waveforms of the Clock Phase modes.

| SS_ (required for slave)                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------|

| SCLK Polarity=0, Mode 0                                                                                                        |

| MOSI/MISO <u>Bit7</u> Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 Bit7                                                                  |

| Clock Phase 1 (Mode 2, 3)<br>Data output on the leading edge of the clock<br>Data registered on the trailing edge of the clock |

| SS_ (optional for slav e)                                                                                                      |

| Polarity=0, Mode 2       SCLK       Polarity=1, Mode 3                                                                         |

| MOSI/MISO Bit7 V Bit6 V Bit5 V Bit4 V Bit3 V Bit2 V Bit1 V Bit0                                                                |

|                                                                                                                                |

#### 9.5.8.2 Registers

Data Register 0 provides a shift register for both incoming and outgoing data. Output data is written to Data Register 1 (TX Data Register). When this block is idle, a write to the TX Data Register will initiate a transmission. Input data is read from Data Register 2 (RX Data Register). When Data Register 0 is empty, its value is updated from Data Register 1, if new data is available. As data bits are shifted in, the transmit bits are shifted out. After the 8 bits are transmitted and received by Data Register 0, the received byte is transferred into Data Register 2 from where it can be read. Simultaneously, the next byte to transmit, if available, is transferred from Data Register 1 into Data Register 0. Control Register 0 (DCA04CR0-DCA07CR0) provides status information and configures the function for one of the four standard modes, which configure the interface based on clock polarity and phase with respect to data.

Clock Phase 0 (Mode 0, 1) Data registered on the leading edge of the clock Data output on the trailing edge of the clock

## 10.7.2.2 Analog Continuous Time Block xx Control 1 Register

The PMux bits control the multiplexing of inputs to the non-inverting input of the op-amp. There are physically only 7 inputs.

The 8<sup>th</sup> code (111) will leave the input floating. This is not desirable, and should be avoided.

The NMux bits control the multiplexing of inputs to the inverting input of the op-amp. There are physically only 7 inputs.

CompBus controls a tri-state buffer that drives the comparator logic. If no PSoC block in the analog column is driving the comparator bus, it will be driven low externally to the blocks.

AnalogBus controls the analog output bus. A CMOS switch connects the op-amp output to the analog bus.

| Table 67: | Analog Continuous Time Block xx Control 1 Register |  |

|-----------|----------------------------------------------------|--|

|-----------|----------------------------------------------------|--|

| Bit #                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                     | 6                                                                               | 5                                                                                     | 4                                                                                     | 3     | 2     | 1     | 0     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| POR                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                     | 0                                                                               | 0                                                                                     | 0                                                                                     | 0     | 0     | 0     | 0     |  |

| Read/<br>Write                                                                                                                                                                                                                                                                                                                                                                                                               | RW                                                                                    | RW                                                                              | RW                                                                                    | RW                                                                                    | RW    | RW    | RW    | RW    |  |

| Bit Name                                                                                                                                                                                                                                                                                                                                                                                                                     | AnalogBus                                                                             | CompBus                                                                         | NMux2                                                                                 | NMux1                                                                                 | NMux0 | PMux2 | PMux1 | PMux0 |  |

| <ul> <li>Bit 7: AnalogBus Enable output to the analog bus</li> <li>0 = Disable analog bus driven by this block</li> <li>1 = Enable analog bus driven by this block</li> <li>Bit 6: CompBus Enable output to the comparator bus</li> <li>0 = Disable comparator bus driven by this block</li> <li>1 = Enable comparator bus driven by this block</li> <li>Bit [5:3]: NMux [2:0] Encoding for negative input select</li> </ul> |                                                                                       |                                                                                 |                                                                                       |                                                                                       |       |       |       |       |  |

| віт [5:3]: Мі                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                       | -                                                                               |                                                                                       |                                                                                       |       |       |       |       |  |

| $0 \ 0 \ 1 = 0 \ 1 \ 0 = 0 \ 1 \ 1 = 0 \ 1 \ 0 \ 1 \ 1 = 0 \ 1 \ 0 \ 1 \ 0 \ 1 = 0 \ 1 \ 0 \ 1 = 0 \ 1 \ 0 \ 1 = 0 \ 1 \ 0 \ 1 = 0 \ 1 \ 0 \ 1 = 0 \ 1 \ 0 \ 1 = 0 \ 1 \ 0 \ 0 = 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0 \ 0$                                                                                                                                                                                                              | REFLO<br>REFHI                                                                        | ACA01<br>ACA00<br>AGND<br>REFLO<br>REFHI<br>ACA01<br>ASB11<br>ASA10<br>Reserved | ACA02<br>ACA03<br>AGND<br>REFLO<br>REFHI<br>ACA02<br>ASA12<br>ASB13<br>Reserved       | ACA03<br>ACA02<br>AGND<br>REFLO<br>REFHI<br>ACA03<br>ASB13<br>ASA12<br>Reserved       |       |       |       |       |  |

| Bit [2:0]: PM                                                                                                                                                                                                                                                                                                                                                                                                                | Mux [2:0] End                                                                         | coding for pos                                                                  | sitive input se                                                                       | lect                                                                                  |       |       |       |       |  |

| 0 0 1 =<br>0 1 0 =<br>0 1 1 =<br>1 0 0 =<br>1 0 1 =<br>1 1 0 =                                                                                                                                                                                                                                                                                                                                                               | ACA00<br>REFLO<br>Port Inputs<br>ACA01<br>AGND<br>ASA10<br>ASB11<br>ABUS0<br>Reserved | ACA02<br>Port Inputs<br>ACA00<br>AGND<br>ASB11<br>ASA10<br>ABUS1<br>Reserved    | ACA02<br>ACA01<br>Port Inputs<br>ACA03<br>AGND<br>ASA12<br>ASB13<br>ABUS2<br>Reserved | ACA03<br>REFLO<br>Port Inputs<br>ACA02<br>AGND<br>ASB13<br>ASA12<br>ABUS3<br>Reserved |       |       |       |       |  |

1. This in fact is the feedback input of the MUX.

Analog Continuous Time Block 00 Control 1 Register (ACA00CR1, Address = Bank 0/1, 72h) Analog Continuous Time Block 01 Control 1 Register (ACA01CR1, Address = Bank 0/1, 76h) Analog Continuous Time Block 02 Control 1 Register (ACA02CR1, Address = Bank 0/1, 7Ah) Analog Continuous Time Block 03 Control 1 Register (ACA03CR1, Address = Bank 0/1, 7Eh)

#### Table 69: Analog Switch Cap Type A Block xx Control 0 Register, continued

Bit 7: <u>FCap</u> F Capacitor value selection bit

0 = 16 capacitor units

1 = 32 capacitor units

**Bit 6**: <u>ClockPhase</u> Clock phase select, will invert clocks internal to the blocks. During normal operation of an SC block for the amplifier of a column enabled to drive the output bus, the connection is only made for the last half of PHI2 (during PHI1 and for the first half of PHI2, the output bus floats at the last voltage to which it was driven). This forms a sample and hold operation using the output bus and its associated capacitance. This design prevents the output bus from being perturbed by the intermediate states of the SC operation (often a reset state for PHI1 and setting to the valid state during PHI2)

Following are the exceptions: 1) If the ClockPhase bit in CR0 (for the SC block in question) is set to 1, then the output is enabled for the whole of PHI2. 2) If the SHDIS signal is set in bit 6 of the Analog Clock Select Register, then sample and hold operation is disabled for all columns and all enabled outputs of SC blocks are connected to their respective output busses for the entire period of their respective PHI2s

0 = Internal PHI1 = External PHI1

1 = Internal PHI1 = External PHI2

This bit also affects the latching of the comparator output (CBUS). Both clock phases, PHI1 and PHI2, are involved in the output latching mechanism. The capture of the next value to be output from the latch (capture point event) happens during the falling edge of one clock phase, and the rising edge of the other clock phase will cause the value to come out (output point event). This bit determines which clock phase triggers the capture point event, and the other clock will trigger the output point event. The value output to the comparator bus will remain stable between output point events.

0 = Capture Point Event triggered by Falling PHI2, Output Point Event triggered by Rising PHI1 1 = Capture Point Event triggered by Falling PHI1, Output Point Event triggered by Rising PHI2

#### Bit 5: ASign

0 = Input sampled on Internal PHI1, Reference Input sampled on internal PHI2

1 = Input sampled on Internal PHI2, Reference Input sampled on internal PHI1

Bit [4:0]: <u>ACap [4:0]</u> Binary encoding for 32 possible capacitor sizes for A Capacitor:

| $0\ 0\ 0\ 0\ 0 = 0$ Capacitor units in array | 1 0 0 0 0 = 16 Capacitor units in array       |

|----------------------------------------------|-----------------------------------------------|

| $0\ 0\ 0\ 0\ 1 = 1$ Capacitor units in array | 10001 = 17 Capacitor units in array           |

| $0\ 0\ 0\ 1\ 0 = 2$ Capacitor units in array | 10010 = 18 Capacitor units in array           |

| $0\ 0\ 0\ 1\ 1=3$ Capacitor units in array   | 10011 = 19 Capacitor units in array           |

| $0\ 0\ 1\ 0\ 0 = 4$ Capacitor units in array | 10100 = 20 Capacitor units in array           |

| $0\ 0\ 1\ 0\ 1 = 5$ Capacitor units in array | 1 0 1 0 1 = 21 Capacitor units in array       |

| $0\ 0\ 1\ 1\ 0 = 6$ Capacitor units in array | 1 0 1 1 0 = 22 Capacitor units in array       |

| 0 0 1 1 1 = 7 Capacitor units in array       | 1 0 1 1 1 = 23 Capacitor units in array       |

| 0 1 0 0 0 = 8 Capacitor units in array       | 1 1 0 0 0 = 24 Capacitor units in array       |

| 0 1 0 0 1 = 9 Capacitor units in array       | 1 1 0 0 1 = 25 Capacitor units in array       |

| 0 1 0 1 0 = 10 Capacitor units in array      | $1\ 1\ 0\ 1\ 0 = 26$ Capacitor units in array |

| 0 1 0 1 1 = 11 Capacitor units in array      | 1 1 0 1 1 = 27 Capacitor units in array       |

| 0 1 1 0 0 = 12 Capacitor units in array      | 1 1 1 0 0 = 28 Capacitor units in array       |

| 0 1 1 0 1 = 13 Capacitor units in array      | 1 1 1 0 1 = 29 Capacitor units in array       |

| 0 1 1 1 0 = 14 Capacitor units in array      | 1 1 1 1 0 = 30 Capacitor units in array       |

| 0 1 1 1 1 = 15 Capacitor units in array      | 1 1 1 1 1 = 31 Capacitor units in array       |

Analog Switch Cap Type A Block 10 Control 0 Register (ASA10CR0, Address = Bank 0/1, 80h) Analog Switch Cap Type A Block 12 Control 0 Register (ASA12CR0, Address = Bank 0/1, 88h) Analog Switch Cap Type A Block 21 Control 0 Register (ASA21CR0, Address = Bank 0/1, 94h) Analog Switch Cap Type A Block 23 Control 0 Register (ASA23CR0, Address = Bank 0/1, 9Ch)

## 10.8.3.4 Analog Switch Cap Type A Block xx Control 3 Register

ARefMux selects the reference input of the A capacitor branch.

FSW1 is used to control a switch in the integrator capacitor path. It connects the output of the op-amp to the integrating cap. The state of the switch is affected by the state of the AutoZero bit in Control 2 Register (ASA10CR2, ASA12CR2, ASA21CR2, ASA23CR2). If the FSW1 bit is set to 0, the switch is always disabled. If the FSW1 bit is set to 1, the AutoZero bit determines the state of the switch. If the AutoZero bit is 0, the switch is enabled at all times. If the AutoZero bit is 1, the switch is enabled only when the internal PHI2 is high.

FSW0 is used to control a switch in the integrator capacitor path. It connects the output of the op-amp to analog ground.

BMuxSCA controls the muxing to the input of the B capacitor branch.

Power – encoding for selecting 1 of 4 power levels. The block always powers up in the off state.

Table 72:

Analog Switch Cap Type A Block xx Control 3 Register

| Bit #          | 7          | 6          | 5      | 4      | 3          | 2          | 1        | 0        |

|----------------|------------|------------|--------|--------|------------|------------|----------|----------|

| POR            | 0          | 0          | 0      | 0      | 0          | 0          | 0        | 0        |

| Read/<br>Write | RW         | RW         | RW     | RW     | RW         | RW         | RW       | RW       |

| Bit Name       | ARefMux[1] | ARefMux[0] | FSW[1] | FSW[0] | BMuxSCA[1] | BMuxSCA[0] | Power[1] | Power[0] |

Bit [7:6]: <u>ARefMux [1:0]</u> Encoding for selecting reference input

0 0 = Analog ground is selected

0 1 = REFHI input selected (This is usually the high reference)

1 0 = REFLO input selected (This is usually the low reference)

1 1 = Reference selection is driven by the comparator (When output comparator node is set high, the input is set to REFHI. When set low, the input is set to REFLO)

Bit 5: FSW1 Bit for controlling gated switches

0 =Switch is disabled

1 = If the FSW1 bit is set to 1, the state of the switch is determined by the AutoZero bit. If the AutoZero bit is 0, the switch is enabled at all times. If the AutoZero bit is 1, the switch is enabled only when the internal PHI2 is high

Bit 4: FSW0 Bits for controlling gated switches

0 =Switch is disabled

1 = Switch is enabled when PHI1 is high

Bit [3:2] <u>BMuxSCA [1:0]</u> Encoding for selecting B inputs. (Note that the available mux inputs vary by individual PSoC block.)

| <u>ASA10</u> | <u>ASA21</u>         | <u>ASA12</u> | <u>ASA23</u> |

|--------------|----------------------|--------------|--------------|

| 0 0 = ACA00  | ASB11                | ACA02        | ASB13        |

| 0 1 = ASB11  | ASB20                | ASB13        | ASB22        |

| 1 0 = P2.3   | ASB22                | ASB11        | P2.0         |

| 1 1 = ASB20  | T <sub>ref</sub> GND | ASB22        | ABUS3        |

Bit [1:0]: Power [1:0] Encoding for selecting 1 of 4 power levels 0 = Off0 1 = 10 µA, typical

$1 0 = 50 \mu A$ , typical

$1 = 200 \,\mu$ A, typical

```

Analog Switch Cap Type A Block 10 Control 3 Register (ASA10CR3, Address = Bank 0/1, 83h)

Analog Switch Cap Type A Block 12 Control 3 Register (ASA12CR3, Address = Bank 0/1, 8Bh)

Analog Switch Cap Type A Block 21 Control 3 Register (ASA21CR3, Address = Bank 0/1, 97h)

Analog Switch Cap Type A Block 23 Control 3 Register (ASA23CR3, Address = Bank 0/1, 9Fh)

```

| Bit #          | 7         | 6       | 5        | 4       | 3       | 2       | 1       | 0       |

|----------------|-----------|---------|----------|---------|---------|---------|---------|---------|

| POR            | 0         | 0       | 0        | 0       | 0       | 0       | 0       | 0       |

| Read/<br>Write | RW        | RW      | RW       | RW      | RW      | RW      | RW      | RW      |

| Bit Name       | AnalogBus | CompBus | AutoZero | CCap[4] | CCap[3] | CCap[2] | CCap[1] | CCap[0] |

#### Table 75: Analog Switch Cap Type B Block xx Control 2 Register

Bit 7: <u>AnalogBus</u> Enable output to the analog bus

0 = Disable output to analog column bus

1 = Enable output to analog column bus

(The output on the analog column bus is affected by the state of the ClockPhase bit in Control 0 Register (ASB11CR0, ASB13CR0, ASB20CR0, ASB22CR0). If AnalogBus is set to 0, the output to the analog column bus is tri-stated. If AnalogBus is set to 1, the ClockPhase bit selects the signal that is output to the analog column bus. If the ClockPhase bit is 0, the block output is gated by sampling clock on last part of PHI2. If the ClockPhase bit is 1, the block output continuously drives the analog column bus)

Bit 6: <u>CompBus</u> Enable output to the comparator bus

0 = Disable output to comparator bus

1 = Enable output to comparator bus

Bit 5: AutoZero Bit for controlling gated switches

0 = Shorting switch is not active. Input cap branches shorted to op-amp input

1 = Shorting switch is enabled during internal PHI1. Input cap branches shorted to analog ground during internal PHI1 and to op-amp input during internal PHI2.

Bit [4:0]: <u>CCap [4:0]</u> Binary encoding for 32 possible capacitor sizes for C Capacitor:

| $0\ 0\ 0\ 0\ 0 = 0$ Capacitor units in array | 1 0 0 0 0 = 16 Capacitor units in array |

|----------------------------------------------|-----------------------------------------|

| $0\ 0\ 0\ 0\ 1 = 1$ Capacitor units in array | 1 0 0 0 1 = 17 Capacitor units in array |

| $0\ 0\ 0\ 1\ 0 = 2$ Capacitor units in array | 1 0 0 1 0 = 18 Capacitor units in array |

| $0\ 0\ 0\ 1\ 1=3$ Capacitor units in array   | 1 0 0 1 1 = 19 Capacitor units in array |

| $0\ 0\ 1\ 0\ 0 = 4$ Capacitor units in array | 1 0 1 0 0 = 20 Capacitor units in array |

| $0\ 0\ 1\ 0\ 1 = 5$ Capacitor units in array | 1 0 1 0 1 = 21 Capacitor units in array |

| $0\ 0\ 1\ 1\ 0 = 6$ Capacitor units in array | 1 0 1 1 0 = 22 Capacitor units in array |

| $0\ 0\ 1\ 1\ 1=7$ Capacitor units in array   | 1 0 1 1 1 = 23 Capacitor units in array |

| 0 1 0 0 0 = 8 Capacitor units in array       | 1 1 0 0 0 = 24 Capacitor units in array |

| 0 1 0 0 1 = 9 Capacitor units in array       | 1 1 0 0 1 = 25 Capacitor units in array |

| 0 1 0 1 0 = 10 Capacitor units in array      | 1 1 0 1 0 = 26 Capacitor units in array |

| 0 1 0 1 1 = 11 Capacitor units in array      | 1 1 0 1 1 = 27 Capacitor units in array |

| 0 1 1 0 0 = 12 Capacitor units in array      | 1 1 1 0 0 = 28 Capacitor units in array |

| 0 1 1 0 1 = 13 Capacitor units in array      | 1 1 1 0 1 = 29 Capacitor units in array |

| 0 1 1 1 0 = 14 Capacitor units in array      | 1 1 1 1 0 = 30 Capacitor units in array |

| 0 1 1 1 1 = 15 Capacitor units in array      | 1 1 1 1 1 = 31 Capacitor units in array |

|                                              |                                         |

Analog Switch Cap Type B Block 11 Control 2 Register (ASB11CR2, Address = Bank 0/1, 86h) Analog Switch Cap Type B Block 13 Control 2 Register (ASB13CR2, Address = Bank 0/1, 8Eh) Analog Switch Cap Type B Block 20 Control 2 Register (ASB20CR2, Address = Bank 0/1, 92h) Analog Switch Cap Type B Block 22 Control 2 Register (ASB22CR2, Address = Bank 0/1, 9Ah)

# 11.0 Special Features of the CPU

# 11.1 Multiplier/Accumulator

A fast, on-chip signed 2's complement MAC (Multiply/ Accumulate) function is provided to assist the main CPU with digital signal processing applications. Multiply results, as well as the lower 2 bytes of the Accumulator, are available immediately after the input registers are written. The upper 2 bytes require a single instruction delay before reading. The MAC function is tied directly on the internal data bus, and is mapped into the register space. The following MAC block diagram provides data flow information. The user has the choice to either cause a multiply/accumulate function to take place, or a multiply only function. The user selects which operation is performed by the choice of input register. The multiply function occurs immediately whenever the MUL X or the MUL\_Y multiplier input registers are written, and the result is available in the MUL\_DH and MUL\_DL multiplier result registers. The Multiply/Accumulate function is executed whenever there is a write to the MAC\_X or the MAC\_Y Multiply/Accumulate input registers, and the result is available in the ACC DR3, ACC DR2, ACC\_DR1, and ACC\_DR0 accumulator result registers. A write to MUL\_X or MAC\_X is input as the X value to both the multiply and Multiply/Accumulate functions. A write to MUL\_Y or MAC\_Y is input as the Y value to both the multiply and Multiply/Accumulate functions. A write to the MAC\_CL0 or MAC\_CL1 registers will clear the value in the four accumulate registers.

Operation of the Multiply/Accumulate function relies on proper multiplicand input. The first value of each multiplicand must be placed into MUL\_X (or MUL\_Y) register to avoid causing a Multiply/Accumulate to occur. The second multiplicand must be placed into MAC\_Y (or MAC\_X) thereby triggering the Multiply/Accumulate function.

MUL\_X, MUL\_Y, MAC\_X, and MAC\_Y are 8-bit signed input registers. MUL\_DL and MUL\_DH form a 16-bit signed output. ACC\_DR0, ACC\_DR1, ACC\_DR2 and ACC\_DR3 form a 32-bit signed output. An extra instruction must be inserted between the following sequences of MAC operations to provide extra delay. If this is not done, the Accumulator results will be inaccurate.

#### a. Two MAC instructions in succession:

mov reg[MAC\_X],a

nop //add nop or any other instruction

mov reg[MAC\_X],a

For sequence a., there is no workaround, the nop or other instruction must be inserted.

b. A MAC instruction followed by a read of the most significant Accumulator bytes:

mov reg[MAC\_X],a

nop //add nop or any other instruction

mov a,[ACC DR2] // or ACC DR3

For sequence b., the least significant Accumulator bytes (ACC\_DR0, ACC\_DR1) may be reliably read directly after the MAC instruction.

Writing to the multiplier registers (MUL\_X, MUL\_Y), and reading the result back from the multiplier product registers (MUL\_DH, MUL\_DL), is not affected by this problem and does not have any restrictions.

| Bit #                                                                                    | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |  |

|------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|--|

| POR                                                                                      | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |  |

| Read/Write                                                                               | R        | R        | R        | R        | R        | R        | R        | R        |  |

| Bit Name                                                                                 | Data [7] | Data [6] | Data [5] | Data [4] | Data [3] | Data [2] | Data [1] | Data [0] |  |

| Bit [7:0]: Data [7:0] 8-bit data value is the high order result of the multiply function |          |          |          |          |          |          |          |          |  |

#### Table 85: Multiply Result High Register

Multiply Result High Register (MUL\_DH, Address = Bank 0, EAh)

#### Table 86: Multiply Result Low Register

| Bit #      | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|

| POR        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| Read/Write | R        | R        | R        | R        | R        | R        | R        | R        |

| Bit Name   | Data [7] | Data [6] | Data [5] | Data [4] | Data [3] | Data [2] | Data [1] | Data [0] |

|            |          |          |          |          |          |          |          |          |

Bit [7:0]: Data [7:0] 8-bit data value is the low order result of the multiply function

Multiply Result Low Register (MUL\_DL, Address = Bank 0, EBh)

#### Table 87: Accumulator Result 1 / Multiply/Accumulator Input X Register

| Bit #      | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|

| POR        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| Read/Write | RW       |

| Bit Name   | Data [7] | Data [6] | Data [5] | Data [4] | Data [3] | Data [2] | Data [1] | Data [0] |

|            |          |          |          |          |          |          |          |          |

#### Bit [7:0]: Data [7:0]

8-bit data value when read is the next to lowest order result of the multiply/accumulate function 8-bit data value when written is the X multiplier input to the multiply/accumulate function

Accumulator Result 1 / Multiply/Accumulator Input X Register (ACC\_DR1 / MAC\_X, Address = Bank 0, ECh)

| Table 88: | Accumulator Result 0 / | Multiply/Accumulator | Input Y Register |

|-----------|------------------------|----------------------|------------------|

|           |                        |                      |                  |

| Bit #      | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|------------|----------|----------|----------|----------|----------|----------|----------|----------|

| POR        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| Read/Write | RW       |

| Bit Name   | Data [7] | Data [6] | Data [5] | Data [4] | Data [3] | Data [2] | Data [1] | Data [0] |

#### Bit [7:0]: Data [7:0]

8-bit data value when read is the lowest order result of the multiply/accumulate function 8-bit data value when written is the Y multiplier input to the multiply/accumulate function

Accumulator Result 0 / Multiply/Accumulator Input Y Register (ACC\_DR0 / MAC\_Y, Address = Bank 0, EDh)

# **13.3 AC Characteristics**

| Table 116: | AC Operating Specifications |

|------------|-----------------------------|

|------------|-----------------------------|

| Symbol               | AC Operating Specifications                               | Minimum          | Typical             | Maximum             | Unit  |

|----------------------|-----------------------------------------------------------|------------------|---------------------|---------------------|-------|

| F <sub>CPU1</sub>    | CPU Frequency (5 V Nominal) <sup>1,2,3</sup>              | 91.35            | 2,400               | 2,460               | kHz   |

| F <sub>CPU2</sub>    | CPU Frequency (3.3V Nominal) <sup>4,3</sup>               | 91.35            | 1,200               | 1,230               | kHz   |

| F <sub>48M</sub>     | Digital PSoC Block Frequency                              |                  | 48                  | 49.2 <sup>1,5</sup> | MHz   |

| F <sub>24M</sub>     | Digital PSoC Block Frequency                              |                  | 24                  | 24.6 <sup>2,4</sup> | MHz   |

| F <sub>GPIO</sub>    | GPIO Operating Frequency                                  |                  | 12                  |                     | MHz   |

| F <sub>IMO</sub>     | Internal Main Oscillator Frequency<br>(0°C to +85°C)      | 23.4             | 24                  | 24.6                | MHz   |

| FIMOC                | Internal Main Oscillator Frequency Cold<br>(-40°C to 0°C) | 22.44            | 24                  | 24.6                | MHz   |

| F <sub>32K1</sub>    | Internal Low Speed Oscillator Frequency<br>(Non Sleep)    | 15 <sup>6</sup>  | 32                  | 50                  | kHz   |

| F <sub>32K2</sub>    | Internal Low Speed Oscillator Frequency (Sleep or Halt)   | 15 <sup>7</sup>  | 32                  | 64                  | kHz   |

| F <sub>32K3</sub>    | External Crystal Oscillator                               | -                | 32.768 <sup>8</sup> | -                   | kHz   |

| F <sub>pll</sub>     | PLL Frequency                                             | -                | 23.986 <sup>9</sup> | -                   | MHz   |

| T <sub>f</sub>       | Output Fall Time                                          | 2 <sup>10</sup>  | -                   | 12                  | ns    |

| т <sub>r</sub>       | Output Rise Time                                          | 3 <sup>10</sup>  | -                   | 18                  | ns    |

| T <sub>plislew</sub> | PLL Lock Time                                             | 0.5              | -                   | 10                  | ms    |

| SV <sub>dd</sub>     | V <sub>dd</sub> Rise Rate at Power Up                     | 80 <sup>11</sup> | -                   | -                   | mV/ms |

| T <sub>os</sub>      | External Crystal Oscillator Startup to 1%                 | -                | 100                 | 500 <sup>12</sup>   | ms    |

| T <sub>osacc</sub>   | External Crystal Oscillator Startup to 100 ppm            | -                | 150                 | 600 <sup>13</sup>   | ms    |

| T <sub>xrst</sub>    | External Reset Pulse Width                                | 10               | -                   | -                   | μs    |

1.  $4.75V < V_{cc} < 5.25V.$

2. Accuracy derived from Internal Main Oscillator with appropriate trim for  $V_{cc}$  range.

- 3.  $0^{\circ}$ C to +85°C.

- 4.  $3.0V < V_{cc} < 3.6V$ .

- 5. See Application Note AN2012 "Adjusting PSoC Microcontroller Trims for Dual Voltage-Range Operation" for information on maximum frequency for User Modules.

- 6. Limits are valid only when *not* in sleep mode.

- 7. Limits are valid only when in sleep mode.

- 8. Accuracy is capacitor and crystal dependent.

- 9. Is a multiple (x732) of crystal frequency.

- 10. Load capacitance = 50 pF.

- 11. To minimum allowable voltage for desired frequency.

- 12. The crystal oscillator frequency is guaranteed to be within 1% of its final value by the end of the 1s startup timer period. Timer period may be as short as 640 ms for the case where F<sub>32K1</sub> is 50 kHz. Correct operation assumes a properly loaded 1uW maximum drive level 32.768 kHz crystal.

- 13. The crystal oscillator frequency is within 100 ppm of its final value by the end of the  $T_{osacc}$  period. Correct operation assumes a properly loaded 1 uW maximum drive level 32.768 kHz crystal. 3.0V <=  $V_{cc}$  <= 5.5V, -40 °C <=  $T_A$

<= 85 °C.

51-85079 \*C

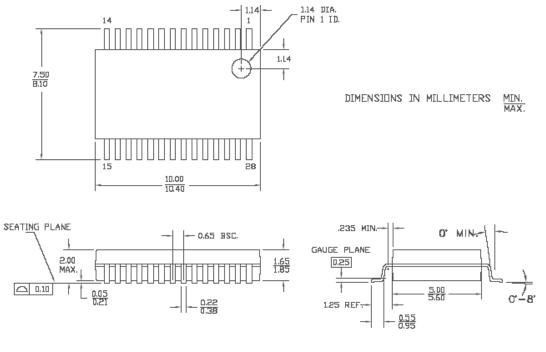

Figure 39: 28-Lead (210-Mil) Shrunk Small Outline Package O28

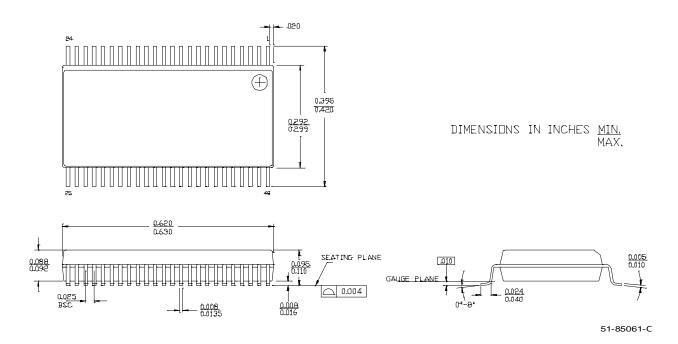

Figure 40: 48-Lead Shrunk Small Outline Package O48

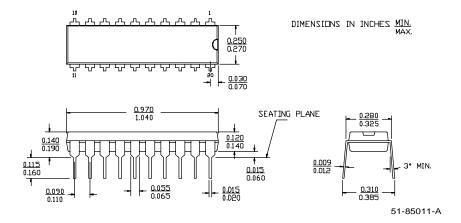

Figure 42: 28-Lead (300-Mil) Molded DIP P21