Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

|                            |                                                        |

| Product Status             | Active                                                 |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 20MHz                                                  |

| Connectivity               | UART/USART                                             |

| Peripherals                | DMA                                                    |

| Number of I/O              | 32                                                     |

| Program Memory Size        | -                                                      |

| Program Memory Type        | ROMIess                                                |

| EEPROM Size                | -                                                      |

| RAM Size                   | 128K x 8                                               |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                            |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 44-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z88c0120vsg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CUSTOMER PROCUREMENT SPECIFICATION

# Z88C00/01

CMOS SUPER8® ROMLESS MCU

### **GENERAL DESCRIPTION**

The CMOS Super8® offers new flexibility and sophistication in 8-bit microcontrollers. The Super8 offers all the features necessary for industrial, consumer, and automotive applications with an enhanced feature set in CMOS technology. At the same time, the CMOS Super8 retains full pin-for-pin compatibility with the NMOS Super8. Available in 48-pin DIP, and 44-, 68-pin PLCC, the CMOS Super8 is the last word in general purpose controllers.

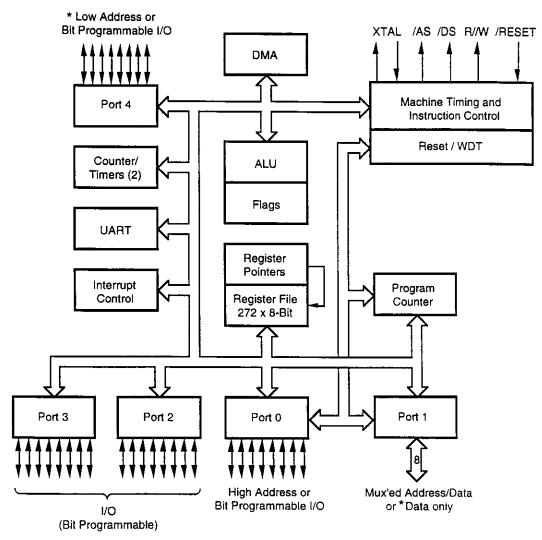

The Super8 features a full-duplex, Universal Asynchronous Receiver/Transmitter (UART) with on-chip baud rate generator, on-chip oscillator, and a Direct Memory Access controller (DMA).

#### Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.: B/W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

| Connection | Circuit | Device        |

|------------|---------|---------------|

| Power      | V       | V             |

| Ground     | GND     | $V_{ss}^{00}$ |

DC-4042-04 (5-17-93) 1

# **GENERAL DESCRIPTION** (Continued)

<sup>\*</sup> Only when used as demux'ed external memory bus.

### **Functional Block Diagram**

# **GENERAL DESCRIPTION** (Continued)

### 68-Lead PLCC Pin Identification

### 68-Lead PLCC Pin Assignments

| Pin #                            | Symbol                                                        | Function                                                                                           | Direction                                         |

|----------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1<br>2-7<br>8-10<br>11<br>12     | N/C<br>P15-10<br>N/C<br>V <sub>cc</sub><br>De-Mux             | Not Connected<br>Port 1, Pins 0,1,2,3,4,5<br>Not Connected<br>Power Supply<br>De-multiplex Pin     | In/Output<br>Input<br>Input                       |

| 13-14<br>15-16<br>17<br>18<br>19 | P17-16<br>P25-24<br>V <sub>cc</sub><br>GND<br>V <sub>cc</sub> | Port 1, Pins 6,7<br>Port 2, Pins 4,5<br>Power Supply<br>Ground<br>Power Supply                     | In/Output<br>In/Output<br>Input<br>Input<br>Input |

| 20<br>21<br>22-25<br>26-27<br>28 | XTAL2<br>XTAL1<br>P47-44<br>N/C<br>P22                        | Crystal Oscillator<br>Crystal Oscillator<br>Port 4, Pins 4,5,6,7<br>Not Connected<br>Port 2, Pin 2 | Output<br>Input<br>In/Output<br>In/Output         |

| 29<br>30-31<br>32-34<br>35<br>36 | N/C<br>P33-32<br>P23-21<br>P31<br>N/C                         | Not Connected<br>Port 3, Pins 2,3<br>Port 2, Pins 3,0,1<br>Port 3, Pin 1<br>Not Connected          | In/Output<br>In/Output<br>In/Output               |

| Pin #                               | Symbol                                            | Function                                                                                | Direction                                           |

|-------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|

| 37<br>38-39<br>40-41<br>42<br>43-44 | P30<br>P27-26<br>P37-36<br>/RESET<br>NC           | Port 3, Pin 0<br>Port 2, Pins 6,7<br>Port 3, Pins 7,6<br>RESET<br>Not Connected         | In/Output<br>In/Output<br>In/Output<br>Input        |

| 45<br>46-47<br>48-49<br>50-51<br>52 | R//W<br>P43-42<br>GND<br>P41-40<br>/DS            | READ/WRITE<br>Port 4, Pins 3,2<br>Ground<br>Port 4, Pins 1,0<br>Data Strobe             | Output<br>In/Output<br>Input<br>In/Output<br>Output |

| 53<br>54-55<br>56-57<br>58<br>59-61 | /AS<br>P35-34<br>P07-06<br>V <sub>cc</sub><br>N/C | Address Strobe<br>Port 3, Pins 4,5<br>Port 0, Pins 7,6<br>Power Supply<br>Not Connected | Output<br>In/Output<br>In/Output<br>Input           |

| 62-67<br>68                         | P05-00<br>GND                                     | Port 0, Pins 5,4,3,2,1,0<br>Ground                                                      | In/Output<br>Input                                  |

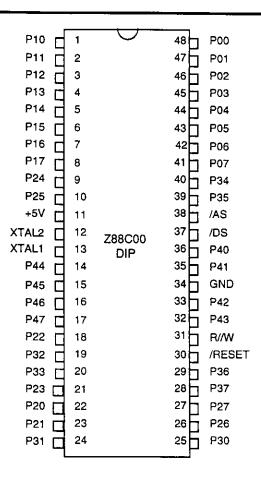

### 48-Lead DIP Pin Identification

### 48-Lead DIP Pin Assignments

| Pin # | Symbol          | Function                     | Direction |

|-------|-----------------|------------------------------|-----------|

| 1-8   | P17-10          | Port 1, Pins 0,1,2,3,4,5,6,7 | In/Output |

| 9-10  | P25-24          | Port 2, Pins 4,5             | In/Output |

| 11    | V <sub>cc</sub> | Power Supply                 | Input     |

| 12    | XTAL2           | Crystal Oscillator           | Output    |

| 13    | XTAL1           | Crystal Oscillator           | Input     |

| 14-17 | P47-44          | Port 4, Pins 4,5,6,7         | In/Output |

| 18    | P22             | Port 2, Pin 2                | In/Output |

| 19-20 | P33-32          | Port 3, Pins 2,3             | In/Output |

| 21-23 | P23-21          | Port 2, Pins 3,0,1           | In/Output |

| 24-25 | P31-30          | Port 3, Pins 1,0             | In/Output |

| 26-27 | P27-26          | Port 2, Pins 6,7             | In/Output |

| Pin # | Symbol | Function                     | Direction |

|-------|--------|------------------------------|-----------|

| 28-29 | P37-36 | Port 3, Pins 7,6             | In/Output |

| 30    | /RESET | RESET                        | Input     |

| 31    | R//W   | READ/WRITE                   | Output    |

| 32-33 | P43-42 | Port 4, Pins 3,2             | In/Output |

| 34    | GND    | Ground                       | Input     |

| 35-36 | P41-40 | Port 4, Pins 1,0             | In/Output |

| 37    | /DS    | Data Strobe                  | Output    |

| 38    | /AS    | Address Strobe               | Output    |

| 39-40 | P35-34 | Port 3, Pins 5,4             | In/Output |

| 41-48 | P07-00 | Port 0, Pins 7,6,5,4,3,2,1,0 | In/Output |

### ABSOLUTE MAXIMUM RATINGS

| Symbol                              | Description                                             | Min          | Max                | Units       |

|-------------------------------------|---------------------------------------------------------|--------------|--------------------|-------------|

| V <sub>CC</sub><br>T <sub>STG</sub> | Supply Voltage (*)<br>Storage Temp<br>Oper Ambient Temp | -0.3<br>-65° | +7.0<br>+150°<br>† | V<br>C<br>C |

#### Notes:

- \* Voltage on all pins with respect to GND.

- † See Ordering Information.

Stress greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for an extended period may affect device reliability.

# STANDARD TEST CONDITIONS

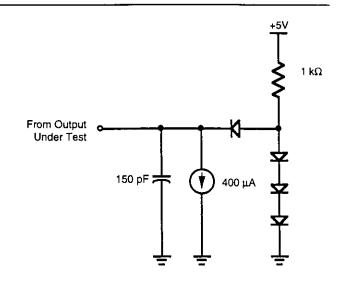

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to  $V_{\rm ss}$ . Positive current flows into the referenced pin (Standard Test Load).

Standard conditions are:

- 4.5V < V<sub>cc</sub> < 5.5V GND 0V

- -40°C <  $T_A$  < +105°C

Standard Test Load

### **ADDITIONAL FEATURE**

Weak Latches

All input pins on the Super8® will be provided with weak latches. Weak latches on inputs prevent them from floating and reduces unnecessary current flow. Weak latches on inputs are automatically disabled when the corresponding output is configured as open-drain.

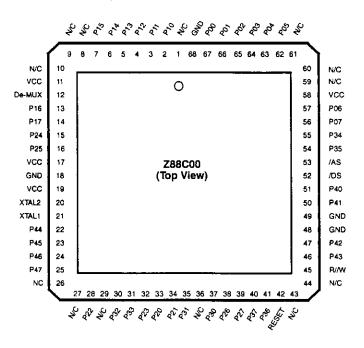

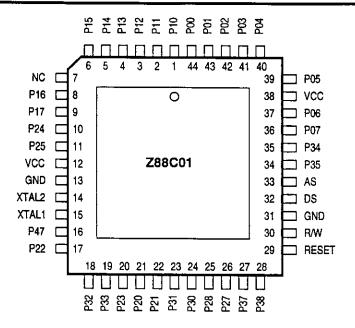

### 44-Lead PLCC Pin Identification

### 44-Lead PLCC Pin Identification

| Pin # | Symbol   | Function                 | Direction | Pin # | Symbol          | Function                 | Direction |

|-------|----------|--------------------------|-----------|-------|-----------------|--------------------------|-----------|

| 1-6   | P15-10   | Port 1, Pins 0,1,2,3,4,5 | In/Output | 23-24 | P31-30          | Port 3, Pins 1,0         | In/Output |

| /     | N/C      | Not Connected            |           | 25-26 | P27-26          | Port 2, Pins 8,7         | In/Output |

| 8-9   | P17-16   | Port 1, Pins 6,7         | In/Output | 27-28 | P37-36          | Port 3, Pins 7,8         | In/Output |

| 10-11 | P25-24   | Port 2, Pins 4,5         | In/Output | 29    | /RESET          | Reset                    | Input     |

| 12    | $V_{cc}$ | Power Supply             | Input     | 30    | R//W            | Read/Write               | Output    |

| 13    | GŇD      | Ground                   | Input     | 31    | GND             | Ground                   | Input     |

| 14    | XTAL2    | Crystal Oscillator       | Output    | 32    | /DS             | Data Strobe              | Output    |

| 15    | XTAL1    | Crystal Oscillator       | Input     | 33    | /AS             | Address Strobe           | Output    |

| 16    | P47      | Port 4, Pin 7            | In/Output | 34-35 | P35-34          | Port 3. Pins 5.4         | In/Output |

| 17    | P22      | Port 2, Pin 2            | In/Output | 36-37 | P07-06          | Port 0, Pins 7,6         | In/Output |

| 18-19 | P33-32   | Port 3, Pins 2,3         | In/Output | 38    | V <sub>cc</sub> | Power Supply             | Input     |

| 20-22 | P23-21   | Port 2, Pins 3,0,1       | In/Output | 39-44 | P05-00          | Port 0, Pins 5,4,3,2,1,0 | In/Output |

# **AC ELECTRICAL CHARACTERISTICS**

External I/O or Memory Read and Write Timing

|        |            |                                            | Nor | mai | Exte | ended |

|--------|------------|--------------------------------------------|-----|-----|------|-------|

| Number | Symbol     | Parameter                                  | Min | Max | Min  | Max   |

| 1      | TdA(AS)    | Address valid to /AS Rise Detay            | 25  |     | 50   |       |

| 2      | ThAS(A)    | /AS Rise to Address Valid Hold Time        | 35  |     | 85   |       |

| 3      | TdAS(DI)   | /AS Rise to Data in Required Valid Delay   |     | 150 |      | 335   |

| 4      | TwAS       | /AS Low Width                              | 35  |     | 85   |       |

| 5      | TdAZ (DSR) | Address Float to /DS (Read)                | 0   |     | 0    |       |

| 6      | TwDSR      | /DS (Read) Low Width                       | 125 |     | 275  |       |

| 7      | TwDSW      | /DS (Write) Low Width                      | 65  |     | 165  |       |

| 8      | TdDSR (DI) | /DS (Read) to Data In Required Valid Delay |     | 80  |      | 225   |

| 9      | ThDSR(DI)  | /DS Rise (Read) to Data In Hold Time       | 0   |     | 0    |       |

| 10     | TdDS (A)   | /DS Rise to Address Active Delay           | 20  |     | 70   |       |

| 11     | TdDA (AS)  | /DS Rise to /AS Delay                      | 30  |     | 80   |       |

| 12     | TdR/W (AS) | R/W to AS Rise Delay                       | 20  |     | 70   |       |

| 13     | TdDS (R/W) | DS Rise to R/W Valid Delay                 | 40  |     | 90   |       |

| 14     | TdDO (DSW) | Data Out to /DS (Write) Delay              | 10  |     | 50   |       |

| 15     | ThDSW (DO) | /DS Rise (Write) to Data Out Hold Time     | 20  |     | 85   |       |

| 16     | TdA (DI)   | Address to Data In Required Valid Delay    |     | 205 |      | 385   |

| 17     | TdAS (DSR) | /AS Rise to D/S (Read) Delay               | 50  |     | 95   |       |

| 19     | TdDM (AS)  | /DM to /AS Rise Delay                      | 28  |     | 70   |       |

| 20     | TdDS (DM)  | /DS Rise to /DM Valid Delay                | 33  |     | 85   |       |

| 21     | ThDS (A)   | /DS Rise to Address Valid Hold Time        | 36  |     | 90   |       |

| 22     | TwW        | Wait Width (One Wait) Window               | [1] |     | [1]  |       |

| 23     | TdAS (W)   | /AS Rise to Wait Delay                     |     | 90  |      | 335   |

#### Notes:

[1] Not characterized function, guaranteed by design.

The value of TsDI (DSR) has been measured for the NMOS part as mentioned below as TsDI (DSR) old. This "old" value needs to be relaxed as to the value described as

TsDI (DSR) new. This new value will allow the customer to use external memories with slower access times that immediately translates in lower cost.

# **DC CHARACTERISTICS**

| Symbol          | Parameter                       | Min                    | Max                                     | Unit | Condition                                            |

|-----------------|---------------------------------|------------------------|-----------------------------------------|------|------------------------------------------------------|

| V <sub>cH</sub> | Clock Input High Voltage        | 3.8                    | V <sub>cc</sub>                         | V    | Driven by External Clock Generator                   |

| V <sub>CL</sub> | Clock Input Low Voltage         | -0.3                   | V <sub>cc</sub><br>0.8                  | V    | Driven by External Clock Generator                   |

| V <sub>IH</sub> | Input High Voltage              | $0.7  \mathrm{V_{cc}}$ |                                         | V    |                                                      |

| V <sub>IL</sub> | Input Low Voltage               | -0.3ັ                  | V <sub>cc</sub><br>0.15 V <sub>cc</sub> | V    |                                                      |

| V <sub>RH</sub> | Reset Input High Voltage        | 3.8                    | V <sub>cc</sub>                         | V    |                                                      |

| V <sub>RL</sub> | Reset Input Low Voltage         | -0.3                   | 8.0                                     |      | · · · · · · · · · · · · · · · · · · ·                |

| V <sub>OH</sub> | Output High Voltage             | 2.4                    |                                         | V    | l <sub>au</sub> =-400 μA                             |

| V <sub>OL</sub> | Output Low Voltage              |                        | 0.4                                     | V    | l <sub>oH</sub> =-400 μA<br>l <sub>ot</sub> =+4.0 mA |

| V <sub>IL</sub> | Input Leakage                   | -10                    | 10                                      | μA   | OL .                                                 |

| l <sub>oL</sub> | Output Leakage                  | -10                    | 10                                      | μA   |                                                      |

| l <sub>in</sub> | Reset Input Current             |                        | -50                                     | μA   |                                                      |

| cc              | V <sub>cc</sub> Standby Current |                        | 90                                      | mΑ   | [1]                                                  |

### Notes:

Estimated Values

[1] In this case all outputs and I/O pins are floating.

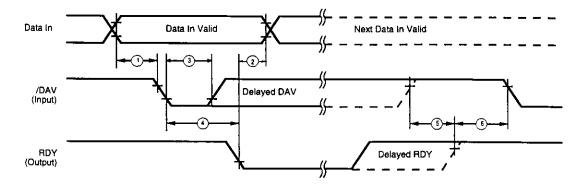

# INTERLOCKED MODE HANDSHAKE TIMING

Input Handshake Timing Fully Interlocked Mode

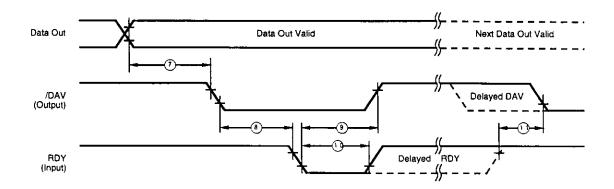

**Output Handshake Timing Fully Interlocked Mode**

# **AC ELECTRICAL CHARACTERISTICS**

Interlocked Mode Handshake Timing

| No. | Symbol       | Parameter                  | Notes (Data Direction) |

|-----|--------------|----------------------------|------------------------|

|     | TsDI (DAV)   | Data in Setup Time to /DAV | In                     |

| 2   | ThRDY (DI)   | RDY to Data in Hold Time   | ln                     |

| 3   | TwDAV        | /DAV Width                 | In                     |

| 4   | TdDAV (RDY)  | /DAV to RDY Delay          | In                     |

| 5   | TwDAV (RDY)  | DAV^ to RDY Wait Time      | In                     |

| 6   | TdRDY (DAV)  | RDY^ to /DAV Delay         | 1n                     |

| 7   | TdD0 (DAV)   | Data Out to /DAV Delay     | Out                    |

| 3   | TdDAVd (RDY) | DAV to RDY Delay           | Out                    |

| 9   | TdRDY (DAV)  | RDY to /DAV^ Delay         | Out                    |

| 10  | TwRDY        | RDY Width                  | Out                    |

| 11  | TwRDY (DAV)  | RDY^ to /DAV Wait Time     | Out                    |

# **20 MHZ NORMAL TIMING**

**External Memory Read And Write**

### **Z88C00 ERRATA**

#### 1. Handshake Port 4

Input handshake (strobe and fully interlocked mode) with DMA is not functional.

#### 2. UART Receive

Upon receiving a character, the RCA (receive character available) interrupt is serviced twice. The time between two consecutive interrupts at 14 MHz is 53  $\mu$ s. Although the UIO is read, which normally should clear the interrupt source, the RCA interrupt is asserted twice.

#### 3. TTL Levels

$V_{_{I\!H}}$ ,  $V_{_{I\!L}}$  do not meet the TTL specification when the port is used as control inputs for the counter/timers, UART, handshake, external wait and interrupts. Instead  $V_{_{I\!H}}$  = 0.7  $V_{_{C\!C}}$  and  $V_{_{I\!L}}$  = 0.15  $V_{_{C\!C}}$ .

### 4. DMA Usage

No DMA can be performed to external memories if the wait feature (hardware wait and software wait) is used.

### 5. Reset Software Sequence

After a hardware reset, program the P0M register before the PM register.

### 6. Counter/Timers

To obtain a 2.5 MHz signal from the counter/timers, load the Counter/Timer registers with FFFFH and count up. The equivalent operations for the NMOS part to obtain the 2.5 MHz signal is to load the counter/timers with 0000H and count down.

### Low Margin:

Customer is advised that this product does not meet Zilog's internal guardbanded test policies for the specification requested and is supplied on an exception basis. Customer is cautioned that delivery may be uncertain and that, in addition to all other limitations on Zilog liability

stated on the front and back of the acknowledgement, Zilog makes no claim as to quality and reliability under the CPS. The product remains subject to standard warranty for replacement due to defects in materials and workmanship.

© 1993 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of merchantability or fitness for any purpose. Zilog, Inc. shall not be responsible for any errors that may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056

# STROBE MODE HANDSHAKE TIMING

# Input Handshake Timing Strobed Mode

**Output Handshake Timing Strobed Mode**

# **AC ELECTRICAL CHARACTERISTICS**

Strobe Mode Handshake Timing

| No. | Symbol    | Parameter                  | Notes (Data Direction) |

|-----|-----------|----------------------------|------------------------|

| 1   | TsDI(DAV) | Data In to Setup Time /DAV | ln                     |

| 2   | ThDAV(DI) | Data in Hold Time          | In                     |

| 3   | TwDAV     | /DAV Width                 | ln                     |

| 4   | TdDO(DAV) | Data Out to /DAV Delay     | Out                    |

| 5   | TwDAV     | Data Available Width       | Out                    |