Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Obsolete                                                  |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 5MHz                                                      |  |

| Connectivity               | IrDA, UART/USART                                          |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |

| Number of I/O              | 24                                                        |  |

| Program Memory Size        | 1KB (1K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 256 x 8                                                   |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Surface Mount                                             |  |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113hj005eg |  |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

|   |   | • |

|---|---|---|

| А | v |   |

| External Reset Input                                |            |

|-----------------------------------------------------|------------|

|                                                     |            |

| On-Chip Debugger Initiated Reset                    |            |

| Stop Mode Recovery                                  |            |

| Stop Mode Recovery Using Watchdog Timer Time-Out    |            |

| Stop Mode Recovery Using a GPIO Port Pin Transition |            |

| Stop Mode Recovery Using the External RESET Pin     |            |

|                                                     |            |

| Low-Power Modes                                     |            |

| STOP Mode                                           |            |

| HALT Mode                                           |            |

| Peripheral-Level Power Control                      |            |

| Power Control Register Definitions                  | 1          |

| General-Purpose Input/Output                        | 3          |

| GPIO Port Availability By Device                    | 3          |

| Architecture                                        | 4          |

| GPIO Alternate Functions                            | 34         |

| Direct LED Drive                                    | 8          |

| Shared Reset Pin                                    | 9          |

| Shared Debug Pin                                    | 9          |

| Crystal Oscillator Override                         | 9          |

| 5 V Tolerance                                       | 9          |

| External Clock Setup                                | 0          |

| GPIO Interrupts                                     | 0          |

| GPIO Control Register Definitions                   | 0          |

| Port A–C Address Registers                          | 1          |

| Port A–C Control Registers                          | -2         |

| Port A–C Data Direction Subregisters                | 3          |

| Port A–C Alternate Function Subregisters            | 3          |

| Port A–C Input Data Registers                       | 60         |

| Port A–C Output Data Register                       | <i>i</i> 1 |

| LED Drive Enable Register 5                         | 1          |

| LED Drive Level High Register 5                     | 52         |

| LED Drive Level Low Register                        | 13         |

| Interrupt Controller                                | <i>i</i> 4 |

| Interrupt Vector Listing                            |            |

| Architecture                                        |            |

| Operation                                           |            |

| Master Interrupt Enable                             | 6          |

| Interrupt Vectors and Priority                      |            |

### Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| Flash Code Protection Against Accidental Program and Erasure | 137 |

|--------------------------------------------------------------|-----|

| Byte Programming                                             | 139 |

| Page Erase                                                   | 139 |

| Mass Erase                                                   | 139 |

| Flash Controller Bypass                                      | 140 |

| Flash Controller Behavior in DEBUG Mode                      | 140 |

| Flash Control Register Definitions                           | 141 |

| Flash Control Register                                       | 141 |

| Flash Status Register                                        | 142 |

| Flash Page Select Register                                   | 142 |

| Flash Sector Protect Register                                | 144 |

| Flash Frequency High and Low Byte Registers                  | 144 |

| Flash Option Bits                                            | 146 |

| Operation                                                    |     |

| Option Bit Configuration By Reset                            |     |

| Option Bit Types                                             |     |

| Reading the Flash Information Page                           |     |

| Flash Option Bit Control Register Definitions                |     |

| Trim Bit Address Register                                    |     |

| Trim Bit Data Register                                       |     |

| Flash Option Bit Address Space                               |     |

| Trim Bit Address Space                                       |     |

| Zilog Calibration Data                                       |     |

| ADC Calibration Data                                         |     |

| Serialization Data                                           |     |

| Randomized Lot Identifier                                    |     |

|                                                              |     |

| On-Chip Debugger                                             |     |

| Architecture                                                 |     |

| Operation                                                    |     |

| OCD Interface                                                |     |

| DEBUG Mode                                                   |     |

| OCD Data Format                                              |     |

| OCD Autobaud Detector/Generator                              |     |

| OCD Serial Errors                                            |     |

| OCD Unlock Sequence (8-Pin Devices Only)                     |     |

| Breakpoints                                                  |     |

| Runtime Counter                                              |     |

| On-Chip Debugger Commands                                    |     |

| On-Chip Debugger Control Register Definitions                |     |

| OCD Control Register                                         | 166 |

## Z8 Encore! XP<sup>®</sup> F0823 Series **Product Specification**

| Table 106. | Assembly Language Syntax Example 1                                         | . 175 |

|------------|----------------------------------------------------------------------------|-------|

| Table 107. | Assembly Language Syntax Example 2                                         | . 176 |

| Table 108. | Notational Shorthand                                                       | . 176 |

| Table 109. | Additional Symbols                                                         | . 177 |

| Table 110. | Arithmetic Instructions                                                    | . 178 |

| Table 111. | Bit Manipulation Instructions                                              | . 179 |

| Table 112. | Block Transfer Instructions                                                | . 179 |

| Table 113. | CPU Control Instructions                                                   | . 180 |

| Table 114. | Load Instructions                                                          | . 180 |

| Table 115. | Logical Instructions                                                       | . 181 |

| Table 116. | Program Control Instructions                                               | . 181 |

| Table 117. | Rotate and Shift Instructions                                              | . 181 |

| Table 118. | eZ8 CPU Instruction Summary                                                | . 182 |

| Table 119. | Opcode Map Abbreviations                                                   | . 193 |

| Table 120. | Absolute Maximum Ratings                                                   | . 196 |

| Table 121. | DC Characteristics                                                         | . 197 |

| Table 122. | Power Consumption                                                          | . 199 |

| Table 123. | AC Characteristics                                                         | . 200 |

| Table 124. | Internal Precision Oscillator Electrical Characteristics                   | . 200 |

| Table 125. | Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing | . 201 |

| Table 126. | Flash Memory Electrical Characteristics and Timing                         |       |

|            | Watchdog Timer Electrical Characteristics and Timing                       |       |

|            | Analog-to-Digital Converter Electrical Characteristics and Timing          |       |

|            | Comparator Electrical Characteristics                                      |       |

|            | GPIO Port Input Timing                                                     |       |

|            | GPIO Port Output Timing                                                    |       |

| Table 132. | On-Chip Debugger Timing                                                    | . 207 |

|            | UART Timing With CTS                                                       |       |

|            | UART Timing Without CTS                                                    |       |

| Table 135. | Z8 Encore! XP F0823 Series Ordering Matrix                                 | . 211 |

|            |                                                                            |       |

6

## **On-Chip Debugger**

F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

22

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

PAO and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. For more details, see the <u>Timers</u> chapter on page 69.

Caution: For pins with multiple alternate functions, Zilog recommends writing to the AFS1 and AFS2 subregisters before enabling the alternate function via the AF Subregister. This prevents spurious transitions through unwanted alternate function modes.

**Table 16. Port Alternate Function Mapping (8-Pin Parts)**

| Port   | Pin | Mnemonic          | Alternate Function Description    | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-----|-------------------|-----------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                     | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |     | Reserved          |                                   | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |     | Reserved          |                                   | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |     | T0OUT             | Timer 0 Output Complement         | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1 | T0OUT             | Timer 0 Output                    | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |     | Reserved          |                                   | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |     | CLKIN             | External Clock Input              | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input/V <sub>REF</sub> | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|        | PA2 | DE0               | UART 0 Driver Enable              | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        |     | RESET             | External Reset                    | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|        |     | T1OUT             | Timer 1 Output                    | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |     | Reserved          |                                   | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3 | CTS0              | UART 0 Clear to Send              | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |     | COUT              | Comparator Output                 | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |     | T1IN              | Timer 1 Input                     | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input                  | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4 | RXD0              | UART 0 Receive Data               | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |     | Reserved          |                                   | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |     | Reserved          |                                   | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (N)          | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5 | TXD0              | UART 0 Transmit Data              | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |     | T1OUT             | Timer 1 Output Complement         | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |     | Reserved          |                                   | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (P)          | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

Note: \*Analog Functions include ADC inputs, ADC reference and comparator inputs. Also, alternate function selection as described in the Port A-C Alternate Function Subregisters section on page 43 must be enabled.

**Table 18. GPIO Port Registers and Subregisters (Continued)**

| Port Register<br>Mnemonic | Port Register Name                |

|---------------------------|-----------------------------------|

| P <i>x</i> HDE            | High Drive Enable.                |

| P <i>x</i> SMRE           | Stop Mode Recovery Source Enable. |

| P <i>x</i> PUE            | Pull-up Enable.                   |

| PxAFS1                    | Alternate Function Set 1.         |

| PxAFS2                    | Alternate Function Set 2.         |

### Port A-C Address Registers

The Port A–C Address registers select the GPIO port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO port controls (Table 19).

Table 19. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7          | 6                       | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------------|-------------------------|---|---|---|---|---|---|

| Field   | PADDR[7:0] |                         |   |   |   |   |   |   |

| RESET   |            | 00H                     |   |   |   |   |   |   |

| R/W     | R/W        | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| Address |            | FD0H, FD4H, FD8H        |   |   |   |   |   |   |

| Bit   | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| [7:0] | Port Address                                                                                   |

| PADDR | The Port Address selects one of the subregisters accessible through the Port Control Register. |

|       | See Table 20 for each subregister function.                                                    |

Table 20. PADDR[7:0] Subregister Functions

|   | PADDR[7:0] | Port Control Subregister Accessible Using the Port A–C Control Registers       |

|---|------------|--------------------------------------------------------------------------------|

| - | 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| - | 01H        | Data Direction.                                                                |

| - | 02H        | Alternate Function.                                                            |

|   | 03H        | Output Control (Open-Drain).                                                   |

| - | 04H        | High Drive Enable                                                              |

#### Table 53. Timer 0–1 Reload High Byte Register (TxRH)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   | TRH |            |     |     |     |     |     |     |

| RESET   | 1   | 1          | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F02H, F0AH |     |     |     |     |     |     |

#### Table 54. Timer 0-1 Reload Low Byte Register (TxRL)

| Bit     | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|------------|-----|-----|-----|-----|-----|-----|

| Field   | TRL |            |     |     |     |     |     |     |

| RESET   | 1   | 1          | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     | F03H, F0BH |     |     |     |     |     |     |

| Bit | Description |

|-----|-------------|

| [7] |             |

| [6] |             |

| [5] |             |

| [4] |             |

| [3] |             |

| [2] |             |

| [1] |             |

| [0] |             |

TRH and TRL—Timer Reload Register High and Low These two bytes form the 16-bit reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In COMPARE Mode,

these two bytes form the 16-bit compare value.

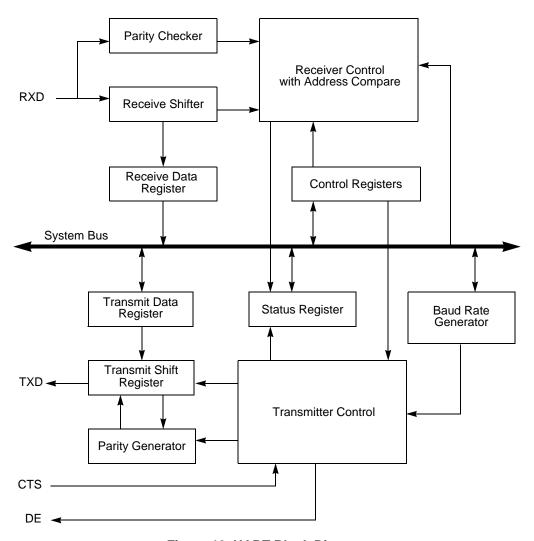

Figure 10. UART Block Diagram

# **Operation**

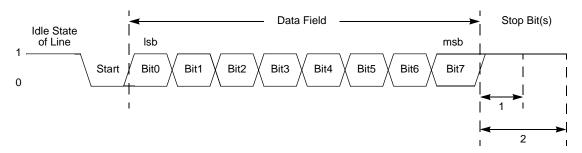

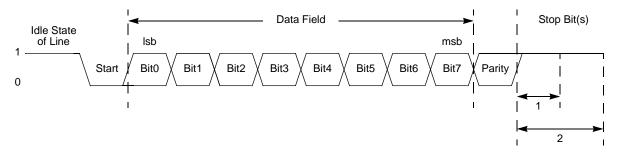

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

Figure 11. UART Asynchronous Data Format without Parity

Figure 12. UART Asynchronous Data Format with Parity

## Transmitting Data Using the Polled Method

Observe the following steps to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register, if MULTIPROCESSOR Mode is appropriate, to enable MULTIPROCESSOR (9-bit) Mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR Mode.

- 5. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR Mode is not enabled, and select either even or odd parity (PSEL)

### **UART Address Compare Register**

The UART Address Compare Register stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions only occur in the event of a match.

Table 70. UART Address Compare Register (U0ADDR)

| Bit     | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|---------|-----|-----------|-----|-----|-----|-----|-----|-----|--|--|--|

| Field   |     | COMP_ADDR |     |     |     |     |     |     |  |  |  |

| RESET   | 0   | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W     | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address |     |           |     | F4  | 5H  |     |     |     |  |  |  |

| Bit       | Description                                             |

|-----------|---------------------------------------------------------|

| [7:0]     | Compare Address                                         |

| COMP_ADDR | This 8-bit value is compared to incoming address bytes. |

## **UART Baud Rate High and Low Byte Registers**

The UART Baud Rate High and Low Byte registers (Table 71 and Table 72) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

Table 71. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | BF  | RH  |     |     |     |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F4  | 6H  |     |     |     |

Table 72. UART Baud Rate Low Byte Register (U0BRL)

| Bit     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Field   |     |     |     | BF  | ₹L  |     |     |     |

| RESET   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W     | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |     |     |     | F4  | 7H  |     |     |     |

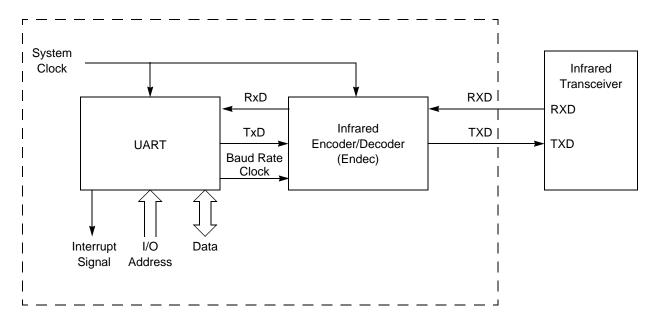

# Infrared Encoder/Decoder

Z8 Encore! XP F0823 Series products contain a fully-functional, high-performance UART with an infrared encoder/decoder (endec). The infrared endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

### **Architecture**

Figure 16 displays the architecture of the infrared endec.

Figure 16. Infrared Data Communication System Block Diagram

# **Operation**

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec, and

#### **Automatic Powerdown**

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control Register.

### **Single-Shot Conversion**

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Observe the following steps for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control Register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}

### **Option Bit Types**

This section describes the five types of Flash option bits offered in the F083A Series.

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device configurations. The information contained here is lost when page 0 in program memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in a Flash memory information page. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data Register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data Register returns the working value of the target trim data byte.

**Note:** The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in the Flash Information Area section on page 15.

#### Serialization Bits

As an optional feature, Zilog is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

#### Table 92. Trim Option Bits at 0001H

| Bit       | 7                             | 6            | 5              | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------|--------------|----------------|-----|-----|-----|-----|-----|--|--|--|

| Field     |                               | Reserved     |                |     |     |     |     |     |  |  |  |

| RESET     | U                             | U            | U              | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                           | R/W          | R/W            | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Address   | Information Page Memory 0021H |              |                |     |     |     |     |     |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | / = Read/Write | е.  |     |     |     |     |  |  |  |

| Bit   | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| [7:0] | Reserved                                                                                  |

|       | These bits are reserved. Altering this register may result in incorrect device operation. |

#### Table 93. Trim Option Bits at 0002H (TIPO)

| Bit       | 7           | 6            | 5            | 4           | 3           | 2    | 1 | 0 |  |  |  |

|-----------|-------------|--------------|--------------|-------------|-------------|------|---|---|--|--|--|

| Field     |             | IPO_TRIM     |              |             |             |      |   |   |  |  |  |

| RESET     |             |              |              | l           | J           |      |   |   |  |  |  |

| R/W       |             |              |              | R           | /W          |      |   |   |  |  |  |

| Address   |             |              | Infor        | mation Page | e Memory 00 | )22H |   |   |  |  |  |

| Note: U = | Unchanged b | y Reset. R/W | = Read/Write | e.          |             |      |   |   |  |  |  |

| Bit      | Description                                                   |

|----------|---------------------------------------------------------------|

| [7:0]    | Internal Precision Oscillator Trim Byte                       |

| IPO_TRIM | Contains trimming bits for the Internal Precision Oscillator. |

# **Zilog Calibration Data**

This section briefly describes the features of the following Flash Option Bit calibration registers.

ADC Calibration Data: see page 153

Serialization Data: see page 154

Randomized Lot Identifier: see page 154

bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous datastreams, the maximum recommended baud rate is the system clock frequency divided by eight. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by four, but this theoretical maximum is possible only for low noise designs with clean signals. Table 100 lists minimum and recommended maximum baud rates for sample crystal frequencies.

Table 100. OCD Baud-Rate Limits

| System Clock<br>Frequency (MHz) | Recommended<br>Maximum Baud Rate<br>(kbps) | Recommended<br>Standard PC Baud<br>Rate (bps) | Minimum Baud Rate (kbps) |

|---------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------|

| 5.5296                          | 1382.4                                     | 691,200                                       | 1.08                     |

| 0.032768 (32kHz)                | 4.096                                      | 2400                                          | 0.064                    |

If the OCD receives a Serial Break (nine or more continuous bits Low) the auto-baud detector/generator resets. Reconfigure the auto-baud detector/generator by sending 80H.

#### **OCD Serial Errors**

The OCD detects any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the auto-baud detector/generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the F0823 Series devices or when recovering from an error. A Serial Break from the host resets the autobaud generator/detector but does not reset the OCD Control Register. A Serial Break leaves the device in DEBUG Mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the opendrain nature of the DBG pin, the host sends a Serial Break to the OCD even if the OCD is transmitting a character.

Table 118. eZ8 CPU Instruction Summary (Continued)

| Assembly  |                           |     | ress<br>ode | _ Opcode(s) |   |   | Fla | ags |   |   | _ Fetch | Instr. |

|-----------|---------------------------|-----|-------------|-------------|---|---|-----|-----|---|---|---------|--------|

| Mnemonic  | Symbolic Operation        | dst | src         | (Hex)       |   | Z | S   | ٧   | D | Н | Cycles  |        |

| POPX dst  | dst ← @SP<br>SP ← SP + 1  | ER  |             | D8          | _ | - | _   | -   | - | - | 3       | 2      |

| PUSH src  | SP ← SP – 1               | R   |             | 70          | - | - | -   | -   | - | - | 2       | 2      |

|           | @SP ← src                 | IR  |             | 71          | • |   |     |     |   |   | 2       | 3      |

|           |                           | IM  |             | IF70        |   |   |     |     |   |   | 3       | 2      |

| PUSHX src | SP ← SP − 1<br>@SP ← src  | ER  |             | C8          | _ | _ | _   | _   | _ | _ | 3       | 2      |

| RCF       | C ← 0                     |     |             | CF          | 0 | _ | _   | _   | _ | _ | 1       | 2      |

| RET       | PC ← @SP<br>SP ← SP + 2   |     |             | AF          | - | - | -   | -   | - | - | 1       | 4      |

| RL dst    |                           | R   |             | 90          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 91          | - |   |     |     |   |   | 2       | 3      |

| RLC dst   | <u> </u>                  | R   |             | 10          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | C                         | IR  |             | 11          | - |   |     |     |   |   | 2       | 3      |

| RR dst    |                           | R   |             | E0          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | E1          | - |   |     |     |   |   | 2       | 3      |

| RRC dst   |                           | R   |             | C0          | * | * | *   | *   | _ | _ | 2       | 2      |

|           | D7 D6 D5 D4 D3 D2 D1 D0 C | IR  |             | C1          | • |   |     |     |   |   | 2       | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>-</sup> = Unaffected.

X = Undefined.

$<sup>0 = \</sup>text{Reset to } 0.$

<sup>1 =</sup> Set to 1.

**Table 122. Power Consumption**

|                           |                                              | $V_D$                | <sub>D</sub> = 2.7V to 3 | 3.6 V                |       |                                                                   |

|---------------------------|----------------------------------------------|----------------------|--------------------------|----------------------|-------|-------------------------------------------------------------------|

|                           | -                                            |                      | Maximum <sup>2</sup>     | Maximum <sup>3</sup> | -     |                                                                   |

| Symbol                    | Parameter                                    | Typical <sup>1</sup> | Std Temp                 | Ext Temp             | Units | Conditions                                                        |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode               | 0.1                  | 2                        | 7.5                  | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |

| I <sub>DD</sub> Halt      | Supply Current in HALT                       | 35                   | 55                       | 65                   | μΑ    | 32kHz.                                                            |

|                           | Mode (with all peripherals disabled)         | 520                  | 630                      | 700                  | μΑ    | 5.5MHz.                                                           |

| I <sub>DD</sub>           | Supply Current in                            | 2.8                  | 4.5                      | 4.8                  | mA    | 32kHz.                                                            |

|                           | ACTIVE Mode (with all peripherals disabled)  | 4.5                  | 5.2                      | 5.2                  | mA    | 5.5MHz.                                                           |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply Current                | 0.9                  | 1.0                      | 1.1                  | μA    |                                                                   |

| I <sub>DD</sub> IPO       | Internal Precision Oscillator Supply Current | 350                  | 500                      | 550                  | μA    |                                                                   |

| I <sub>DD</sub> VBO       | Voltage Brown-Out Supply Current             | 50                   |                          |                      | μΑ    | For 20-/28-pin devices (VBO only). <sup>4</sup>                   |

|                           | -                                            |                      |                          |                      |       | For 8-pin devices.4                                               |

| I <sub>DD</sub> ADC       | Analog-to-Digital Con-                       | 2.8                  | 3.1                      | 3.2                  | mΑ    | 32kHz.                                                            |

|                           | verter Supply Current                        | 3.1                  | 3.6                      | 3.7                  | mΑ    | 5.5MHz.                                                           |

|                           | (with External Reference)                    | 3.3                  | 3.7                      | 3.8                  | mA    | 10MHz.                                                            |

|                           | -                                            | 3.7                  | 4.2                      | 4.3                  | mΑ    | 20MHz.                                                            |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference Supply Current        | 0                    |                          |                      | μΑ    | See Note 4.                                                       |

| I <sub>DD</sub> CMP       | Comparator supply Current                    | 150                  | 180                      | 190                  | μA    | See Note 4.                                                       |

| I <sub>DD</sub> BG        | Band Gap Supply Cur-                         | 320                  | 480                      | 500                  | μΑ    | For 20-/28-pin devices.                                           |

|                           | rent                                         |                      |                          |                      |       | For 8-pin devices.                                                |

#### Notes:

- 1. Typical conditions are defined as  $V_{DD} = 3.3 \text{ V}$  and  $+30^{\circ}\text{C}$ . 2. Standard temperature is defined as  $T_{A} = 0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ ; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

- 3. Extended temperature is defined as  $T_A = -40$ °C to +105°C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

- 4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

212

Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

| Part Number                                | Flash<br>RAM | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |

|--------------------------------------------|--------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|

| Z8 Encore! XP F0823 Series with 8 KB Flash |              |           |            |                        |                     |                |                     |  |

| Standard Temperature: 0°C to 70°C          |              |           |            |                        |                     |                |                     |  |

| Z8F0813PB005SG                             | 8 KB 1 K     | B 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |

| Z8F0813QB005SG                             | 8 KB 1 K     | B 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |

| Z8F0813SB005SG                             | 8 KB 1 K     | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |

| Z8F0813SH005SG                             | 8 KB 1 K     | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |

| Z8F0813HH005SG                             | 8 KB 1 K     | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |

| Z8F0813PH005SG                             | 8 KB 1 K     | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |

| Z8F0813SJ005SG                             | 8 KB 1 K     | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |

| Z8F0813HJ005SG                             | 8 KB 1 K     | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |

| Z8F0813PJ005SG                             | 8 KB 1 K     | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |

| Extended Temperature: -40°C to 105°C       |              |           |            |                        |                     |                |                     |  |

| Z8F0813PB005EG                             | 8 KB 1 K     | В 6       | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |

| Z8F0813QB005EG                             | 8 KB 1 K     | В 6       | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |

| Z8F0813SB005EG                             | 8 KB 1 K     | В 6       | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |

| Z8F0813SH005EG                             | 8 KB 1 K     | B 16      | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |

| Z8F0813HH005EG                             | 8 KB 1 K     | B 16      | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |

| Z8F0813PH005EG                             | 8 KB 1 K     | B 16      | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |

| Z8F0813SJ005EG                             | 8 KB 1 K     | B 24      | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |

| Z8F0813HJ005EG                             | 8 KB 1 K     | B 24      | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |

| Z8F0813PJ005EG                             | 8 KB 1 K     | B 24      | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |

| LDEI 179, 180                                     | N                                    |

|---------------------------------------------------|--------------------------------------|

| LDX 180                                           | NOP (no operation) 180               |

| LEA 180                                           | notation                             |

| load 180                                          | b 176                                |

| load constant 179                                 | cc 176                               |

| load constant to/from program memory 180          | DA 176                               |

| load constant with auto-increment addresses 180   | ER 176                               |

| load effective address 180                        | IM 176                               |

| load external data 180                            | IR 176                               |

| load external data to/from data memory and auto-  | Ir 176                               |

| increment addresses 179                           | IRR 176                              |

| load external to/from data memory and auto-incre- | Irr 176                              |

| ment addresses 180                                | p 176                                |

| load instructions 180                             | R 176                                |

| load using extended addressing 180                | r 176                                |

| logical AND 181                                   | RA 177                               |

| logical AND/extended addressing 181               | RR 177                               |

| logical exclusive OR 181                          | rr 177                               |

| logical exclusive OR/extended addressing 181      | vector 177                           |

| logical instructions 181                          | X 177                                |

| logical OR 181                                    | notational shorthand 176             |

| logical OR/extended addressing 181                | notational shorthand 170             |

| low power modes 30                                |                                      |

|                                                   | 0                                    |

|                                                   | OCD                                  |

| M                                                 | architecture 156                     |

| master interrupt enable 56                        | auto-baud detector/generator 159     |

| memory                                            | baud rate limits 160                 |

| data 15                                           | block diagram 156                    |

| program 13                                        | breakpoints 161                      |

| mode                                              | commands 162                         |

| CAPTURE 89                                        | control register 166                 |

| CAPTURE/COMPARE 89                                | data format 159                      |

| CONTINUOUS 88                                     | DBG pin to RS-232 Interface 157      |

| COUNTER 89                                        | DEBUG mode 158                       |

| GATED 89                                          | debugger break 181                   |

| ONE-SHOT 88                                       | interface 157                        |

| PWM 89                                            | serial errors 160                    |

| modes 89                                          | status register 168                  |

| MULT 179                                          | timing 207                           |

| multiply 179                                      | OCD commands                         |

| MULTIPROCESSOR mode, UART 103                     | execute instruction (12H) 166        |

|                                                   | read data memory (0DH) 165           |

|                                                   | read OCD control register (05H) 163  |

|                                                   | 1000 000 0011101 10515101 (0011) 100 |