Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113pb005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ilog<sup>°</sup> Embedded in Life An ∎IXYS Company

5

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

# **10-Bit Analog-to-Digital Converter**

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

## **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

# **Reset Controller**

Z8 Encore!  $XP^{\text{(B)}}$  F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP Mode exit, or Voltage Brown-Out warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

An IXYS Company 6

# **On-Chip Debugger**

F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a richset of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

| Address (Hex) | Register Description    | Mnemonic | Reset (Hex) | Page<br>No.                                                                   |

|---------------|-------------------------|----------|-------------|-------------------------------------------------------------------------------|

| eZ8 CPU       |                         |          |             |                                                                               |

| FFC           | Flags                   | _        | XX          | Refe                                                                          |

| FFD           | Register Pointer        | RP       | XX          | to the                                                                        |

| FFE           | Stack Pointer High Byte | SPH      | XX          | - <u>eZ8</u><br>CPU                                                           |

| FFF           | Stack Pointer Low Byte  | SPL      | XX          | <u>Core</u><br><u>User</u><br><u>Man-</u><br><u>ual</u><br>(UM0<br><u>28)</u> |

#### Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

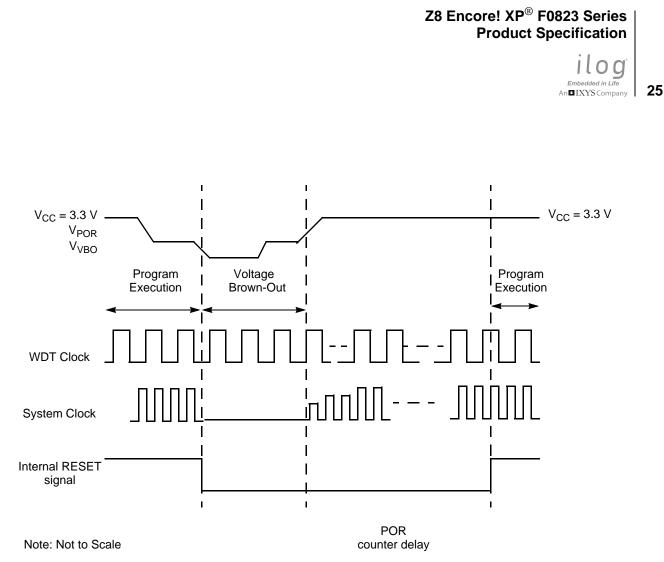

Figure 6. Voltage Brown-Out Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

# Watchdog Timer Reset

If the device is in NORMAL or STOP Mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

# 28

nbedded in Life

# Stop Mode Recovery Using the External RESET Pin

When a Z8 Encore! XP F0823 Series device is in STOP Mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see the <u>Electrical Characteristics</u> chapter on page 196.

# **Reset Register Definitions**

The following sections define the Reset registers.

### **Reset Status Register**

The Reset Status (RSTSTAT) Register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer Control Register, which is writeonly; see Table 12.

| Bit     | 7                            | 6    | 5 | 4   | 3        | 2 | 1 | 0 |  |

|---------|------------------------------|------|---|-----|----------|---|---|---|--|

| Field   | POR STOP WDT                 |      |   | EXT | Reserved |   |   |   |  |

| RESET   | See descriptions in Table 13 |      |   | 0   | 0        | 0 | 0 | 0 |  |

| R/W     | R R R                        |      |   | R   | R        | R | R | R |  |

| Address |                              | FFOH |   |     |          |   |   |   |  |

Table 12. Reset Status Register (RSTSTAT)

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>POR  | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a Power-On Reset event has occurred. This bit is reset to 0 if a WDT time-<br>out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read. For<br>POR/Stop Mode Recover event values, please see Table 13.                                                                                                                                                                                                                   |

| [6]<br>STOP | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set<br>to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and<br>the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset<br>by a POR or a WDT time-out that occurred while not in STOP Mode. Reading this register also<br>resets this bit. For POR/Stop Mode Recover event values, please see Table 13. |

| [5]<br>WDT  | <b>Watchdog Timer Time-Out Indicator</b><br>If this bit is set to 1, a WDT time-out has occurred. A POR resets this pin. A Stop Mode Recov-<br>ery from a change in an input pin also resets this bit. Reading this register resets this bit; this<br>read must occur before clearing the WDT interrupt. For POR/Stop Mode Recover event values,<br>please see Table 13.                                                                                                                                             |

#### ilog<sup>°</sup> Embedded in Life An IXYS Company 49

#### Port A–C Alternate Function Set 2 Subregisters

The Port A–C Alternate Function Set 2 Subregister (Table 29) is accessed through the Port A–C Control Register by writing 08H to the Port A–C Address Register. The Alternate Function Set 2 subregisters selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 15 in the section the <u>GPIO Alternate Functions</u> section on page 34.

| Bit     | 7                                                                  | 7         6         5         4         3         2         1         0               |        |        |        |        |        |        |  |  |

|---------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| Field   | PAFS27                                                             | PAFS26                                                                                | PAFS25 | PAFS24 | PAFS23 | PAFS22 | PAFS21 | PAFS20 |  |  |

| RESET   | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |                                                                                       |        |        |        |        |        |        |  |  |

| R/W     | R/W                                                                | R/W                                                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| Address | If 08H ir                                                          | If 08H in Port A–C Address Register, accessible through the Port A–C Control Register |        |        |        |        |        |        |  |  |

#### Bit Description

[7:0] Port Alternate Function Set 2

PAFS2x 0 = Port Alternate Function selected as defined in <u>Table 15</u> on page 33; also see the <u>GPIO</u> <u>Alternate Functions</u> section on page 34).

1 = Port Alternate Function selected as defined in Table 15.

Note: x indicates the specific GPIO port pin number (7–0).

#### ilog° Embedded in Life An TXYS Company

61

# **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 38) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 Register to determine if any interrupt requests are pending.

| Bit           | 7                                                                                                                                                                              | 6                                                                   | 5              | 4           | 3   | 2   | 1   | 0   |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------|-------------|-----|-----|-----|-----|--|--|

| Field         | Reserved PC3I PC2I PC1I F                                                                                                                                                      |                                                                     |                |             |     |     |     |     |  |  |

| RESET         | 0                                                                                                                                                                              | 0 0 0 0 0 0 0 0                                                     |                |             |     |     |     |     |  |  |

| R/W           | R/W                                                                                                                                                                            | R/W                                                                 | R/W            | R/W         | R/W | R/W | R/W | R/W |  |  |

| Address       |                                                                                                                                                                                | FC6H                                                                |                |             |     |     |     |     |  |  |

| Bit           | Description                                                                                                                                                                    |                                                                     |                |             |     |     |     |     |  |  |

| [7:4]         | Reserved<br>These bits                                                                                                                                                         | Reserved<br>These bits are reserved and must be programmed to 0000. |                |             |     |     |     |     |  |  |

| [3:0]<br>PCxI | Port C Pin x Interrupt Request         0 = No interrupt request is pending for GPIO Port C pin x.         1 = An interrupt request from GPIO Port C pin x is awaiting service. |                                                                     |                |             |     |     |     |     |  |  |

| Note: x in    | dicates the sp                                                                                                                                                                 | ecific GPIO F                                                       | Port C pin nun | nber (3–0). |     |     |     |     |  |  |

#### Table 38. Interrupt Request 2 Register (IRQ2)

# **IRQ0 Enable High and Low Bit Registers**

Table 39 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 40 and Table 41) form a priority-encoded enabling for interrupts in the Interrupt Request 0 Register. Priority is generated by setting bits in each register.

| Table 39. IRQ0 Enable and Priority Encoding |

|---------------------------------------------|

|---------------------------------------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Note: where x indicates the register bits from 0–7.

ilog° Embedded in Life An∎IXYS Company 95

#### Table 61. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|------|

| Field                                                                                         | WDTU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |   |   |   |   |      |

| RESET                                                                                         | 00H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |   |   |   |   |   |      |

| R/W                                                                                           | R/W*         R/W* <th< th=""><th>R/W*</th></th<> |   |   |   |   |   |   | R/W* |

| Address                                                                                       | ddress FF1H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |   |   |   |   |   |      |

| Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |   |   |   |   |      |

|                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |   |   |   |   |      |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value. |

### Table 62. Watchdog Timer Reload High Byte Register (WDTH)

| Bit       | 7                                                                                             | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-----------|-----------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| Field     | WDTH                                                                                          |      |      |      |      |      |      |      |  |  |

| RESET     | 04H                                                                                           |      |      |      |      |      |      |      |  |  |

| R/W       | R/W*                                                                                          | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| Address   | FF2H                                                                                          |      |      |      |      |      |      |      |  |  |

| Note: R/W | Note: R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, Bits[15:8], of the 24-bit WDT reload value. |

#### Table 63. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit       | 7           | 6             | 5            | 4            | 3             | 2             | 1        | 0    |  |  |  |

|-----------|-------------|---------------|--------------|--------------|---------------|---------------|----------|------|--|--|--|

| Field     | WDTL        |               |              |              |               |               |          |      |  |  |  |

| RESET     |             | 00H           |              |              |               |               |          |      |  |  |  |

| R/W       | R/W*        | R/W*          | R/W*         | R/W*         | R/W*          | R/W*          | R/W*     | R/W* |  |  |  |

| Address   | FF3H        |               |              |              |               |               |          |      |  |  |  |

| Note: R/W | *—Read retu | rns the curre | nt WDT count | value. Write | sets the appr | opriate Reloa | d Value. |      |  |  |  |

nbedded in Life

102

## **Receiving Data Using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following steps to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR Mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPRO-CESSOR modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control</li> <li>This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.</li> <li>When the UART receiver is not enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0.</li> <li>Reads from the Baud Rate High and Low Byte registers return the current BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG count value.</li> <li>When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.</li> <li>1 = Reads from the Baud Rate High and Low Byte registers return the High Byte is read.</li> </ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared encoder/decoder is disabled. UART operates normally.</li> <li>1 = Infrared encoder/decoder is enabled. The UART transmits and receives data through the infrared encoder/decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### ilog Embedded in Life An∎IXYS Company 130

# ADC Data High Byte Register

The ADC Data High Byte Register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit     | 7 | 6     | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |  |

|---------|---|-------|---|----|----|---|---|---|--|--|--|--|

| Field   |   | ADCDH |   |    |    |   |   |   |  |  |  |  |

| RESET   | Х | Х     | Х | Х  | Х  | Х | Х | Х |  |  |  |  |

| R/W     | R | R     | R | R  | R  | R | R | R |  |  |  |  |

| Address |   |       |   | F7 | 2H |   |   |   |  |  |  |  |

| Table 1 | 76. | ADC | Data | High          | <b>Byte</b> | Register | (ADCD | H) |

|---------|-----|-----|------|---------------|-------------|----------|-------|----|

|         |     |     |      | · · · · · · · | -,          |          | ····· | /  |

# Bit Description [7:0] ADC Data High Byte ADCDH This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

ILOG<sup>®</sup> Ibedded in Life IXYS Company 164

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG Mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

**Read Register (09H).** The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

Write Program Memory (0AH). The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device is not in DEBUG Mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

```

DBG \leftarrow 0AH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Program Memory (0BH).** The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

DBG  $\leftarrow$  0BH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\rightarrow$  1-65536 data bytes

Write Data Memory (0CH). The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG Mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

**Read Program Memory CRC (0EH).** The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The Step Instruction steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG Mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG ← 10H

> Embedded in Life An IXYS Company 181

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### Table 115. Logical Instructions

#### Table 116. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | —               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | _               | Return                        |

| TRAP     | vector          | Software Trap                 |

#### Table 117. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction               |

|----------|----------|---------------------------|

| BSWAP    | dst      | Bit Swap                  |

| RL       | dst      | Rotate Left               |

| RLC      | dst      | Rotate Left through Carry |

ilog<sup>®</sup> Embedded in Life 191 An∎IXYS Company

| Assembly      |                             | Address<br>Mode |     | _ Opcode(s) | Flags |   |   |   |   | Fetch | Instr. |   |

|---------------|-----------------------------|-----------------|-----|-------------|-------|---|---|---|---|-------|--------|---|

| Mnemonic      | Symbolic Operation          | dst             | src | (Hex)       | С     | Ζ | S | ۷ | D | Н     | Cycles |   |

| XOR dst, src  | $dst \gets dst \ XOR \ src$ | r               | r   | B2          | _     | * | * | 0 | _ | _     | 2      | 3 |

|               |                             | r               | lr  | B3          |       |   |   |   |   |       | 2      | 4 |

|               |                             | R               | R   | B4          |       |   |   |   |   |       | 3      | 3 |

|               |                             | R               | IR  | B5          |       |   |   |   |   |       | 3      | 4 |

|               |                             | R               | IM  | B6          |       |   |   |   |   |       | 3      | 3 |

|               |                             | IR              | IM  | B7          |       |   |   |   |   |       | 3      | 4 |

| XORX dst, src | $dst \gets dst \ XOR \ src$ | ER              | ER  | B8          | _     | * | * | 0 | _ | _     | 4      | 3 |

|               |                             | ER              | IM  | B9          |       |   |   |   |   |       | 4      | 3 |

#### Table 118. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation: \* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

PS024315-1011

# Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

| Symbol           | Parameter                    | Minimum             | Typical        | Maximum              | Units | Conditions                                                                                                                                                     |

|------------------|------------------------------|---------------------|----------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _              | 3.6                  | V     |                                                                                                                                                                |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -              | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -              | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -              | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -              | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -              | -                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -              | 0.6                  | V     | $I_{OL}$ = 20mA; $V_{DD}$ = 3.3 V<br>High Output Drive enabled.                                                                                                |

| V <sub>OH2</sub> | High Level Output<br>Voltage | 2.4                 | -              | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.002 | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.007 | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>TL</sub>  | Tristate Leakage<br>Current  | -                   | -              | <u>+</u> 5           | μA    |                                                                                                                                                                |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

|                   |                                       |         | -40°C to -<br>otherwise | ⊦105°C<br>specified) |       |                                                                               |  |

|-------------------|---------------------------------------|---------|-------------------------|----------------------|-------|-------------------------------------------------------------------------------|--|

| Symbol            | Parameter                             | Minimum | Typical                 | Maximum              | Units | Conditions                                                                    |  |

| I <sub>LED</sub>  | Controlled Current                    | 1.8     | 3                       | 4.5                  | mA    | {AFS2,AFS1} = {0,0}.                                                          |  |

|                   | Drive                                 | 2.8     | 7                       | 10.5                 | mA    | {AFS2,AFS1} = {0,1}.                                                          |  |

|                   |                                       | 7.8     | 13                      | 19.5                 | mA    | {AFS2,AFS1} = {1,0}.                                                          |  |

|                   |                                       | 12      | 20                      | 30                   | mA    | ${AFS2,AFS1} = {1,1}.$                                                        |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance          | -       | 8.0 <sup>2</sup>        | -                    | pF    |                                                                               |  |

| C <sub>XIN</sub>  | X <sub>IN</sub> Pad Capaci-<br>tance  | -       | 8.0 <sup>2</sup>        | -                    | pF    |                                                                               |  |

| C <sub>XOUT</sub> | X <sub>OUT</sub> Pad Capaci-<br>tance | -       | 9.5 <sup>2</sup>        | -                    | pF    |                                                                               |  |

| I <sub>PU</sub>   | Weak Pull-up Cur-<br>rent             | 30      | 100                     | 350                  | μA    | V <sub>DD</sub> = 3.0V–3.6V.                                                  |  |

| V <sub>RAM</sub>  | RAM Data Reten-<br>tion Voltage       | TBD     |                         |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed. |  |

#### Table 121. DC Characteristics (Continued)

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

ilog Embedded in Life An IXYS Company 202

|                                               | $T_A = -$ | = 2.7V to<br>-40°C to +<br>otherwise | 105°C   |        |                                                                                                                                                                  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                            |

| Flash Byte Read Time                          | 100       | _                                    | _       | ns     |                                                                                                                                                                  |

| Flash Byte Program Time                       | 20        | _                                    | 40      | μs     |                                                                                                                                                                  |

| Flash Page Erase Time                         | 10        | _                                    | _       | ms     |                                                                                                                                                                  |

| Flash Mass Erase Time                         | 200       | _                                    | _       | ms     |                                                                                                                                                                  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                  |

| Flash Row Program Time                        | -         | _                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This param-<br>eter is only an issue when<br>bypassing the Flash Controller. |

| Data Retention                                | 100       | _                                    | _       | years  | 25°C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                             |

#### Table 126. Flash Memory Electrical Characteristics and Timing

#### Table 127. Watchdog Timer Electrical Characteristics and Timing

|                          |                          | T <sub>A</sub> = - | = 2.7V to<br>-40°C to +<br>otherwise | 105°C       |       |                                                                                              |

|--------------------------|--------------------------|--------------------|--------------------------------------|-------------|-------|----------------------------------------------------------------------------------------------|

| Symbol                   | Parameter                | Minimum            | Typical                              | Maximum     | Units | Conditions                                                                                   |

| F <sub>WDT</sub>         | WDT Oscillator Frequency |                    | 10                                   |             | kHz   |                                                                                              |

| F <sub>WDT</sub>         | WDT Oscillator Error     |                    |                                      | <u>+</u> 50 | %     |                                                                                              |

| T <sub>WDT-</sub><br>CAL | WDT Calibrated Timeout   | 0.98               | 1                                    | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30°C                                            |

|                          |                          | 0.70               | 1                                    | 1.30        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = 0^{\circ} C \text{ to } 70^{\circ} C$           |

|                          |                          | 0.50               | 1                                    | 1.50        | S     | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40^{\circ} \text{C to } +105^{\circ} \text{C}$ |

> ilog Embedded in Life An IXYS Company 213

| Part Number                                                                    | Flash<br>RAM |      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------------------------------------------------------------|--------------|------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP F0823 Series with 4 KB Flash, 10-Bit Analog-to-Digital Converter |              |      |            |                        |                     |                |                     |

| Standard Temperature: 0°C to 70°C                                              |              |      |            |                        |                     |                |                     |

| Z8F0423PB005SG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: –40°C to 105°C                                           |              |      |            |                        |                     |                |                     |

| Z8F0423PB005EG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EG                                                                 | 4 KB 1 K     | B 6  | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EG                                                                 | 4 KB 1 K     | B 16 | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EG                                                                 | 4 KB 1 K     | B 22 | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

## Table 135. Z8 Encore! XP F0823 Series Ordering Matrix (Continued)

## G

GATED mode 89 general-purpose I/O 33 GPIO 4.33 alternate functions 34 architecture 34 control register definitions 40 input data sample timing 204 interrupts 40 port A-C pull-up enable sub-registers 47, 48, 49 port A-H address registers 41 port A-H alternate function sub-registers 43 port A-H control registers 42 port A-H data direction sub-registers 43 port A-H high drive enable sub-registers 45 port A-H input data registers 50 port A-H output control sub-registers 44 port A-H output data registers 51 port A-H stop mode recovery sub-registers 46 port availability by device 33 port input timing 205 port output timing 206

# Η

H 177 HALT 180 halt mode 31, 180 hexadecimal number prefix/suffix 177

# I

I2C 4 IM 176 immediate data 176 immediate operand prefix 177 INC 178 increment 178 increment word 178 INCW 178 indexed 177 indirect address prefix 177 indirect register 176 indirect register pair 176 indirect working register 176 indirect working register pair 176 infrared encoder/decoder (IrDA) 117 Instruction Set 174 instruction set, eZ8 CPU 174 instructions ADC 178 **ADCX 178** ADD 178 **ADDX 178** AND 181 **ANDX 181** arithmetic 178 **BCLR 179 BIT 179** bit manipulation 179 block transfer 179 **BRK 181 BSET 179** BSWAP 179, 181 BTJ 181 **BTJNZ 181 BTJZ 181 CALL 181** CCF 179, 180 **CLR 180** COM 181 CP 178 **CPC 178 CPCX 178** CPU control 180 **CPX 178** DA 178 **DEC 178 DECW 178** DI 180 DJNZ 181 EI 180 **HALT 180 INC 178 INCW 178 IRET 181** JP 181