Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113ph005eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2.7V to 3.6V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- $0^{\circ}$ C to +70°C and -40°C to +105°C for operating temperature ranges

# **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore!  $XP^{\text{®}}$  F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

Table 1. F0823 Series Family Part Selection Guide

| Program Memory Address (Hex)                                                                          | Function                 |

|-------------------------------------------------------------------------------------------------------|--------------------------|

| Z8F0123 and Z8F0113 Products                                                                          |                          |

| 0000–0001                                                                                             | Flash Option Bits        |

| 0002–0003                                                                                             | Reset Vector             |

| 0004–0005                                                                                             | WDT Interrupt Vector     |

| 0006–0007                                                                                             | Illegal Instruction Trap |

| 0008–0037                                                                                             | Interrupt Vectors*       |

| 0038–003D                                                                                             | Oscillator Fail Traps*   |

| 003E-03FF                                                                                             | Program Memory           |

| Note: *See the <u>Trap and Interrupt Vectors in C</u><br>for a list of the interrupt vectors and trap |                          |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

# **Data Memory**

Z8 Encore! XP F0823 Series does not use the eZ8 CPU's 64KB Data Memory address space.

# **Flash Information Area**

Table 7 lists the F0823 Series Flash Information Area. This 128B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory<br>Address (Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left-justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. F0823 Series Flash Memory Information Area Map

ilog<sup>®</sup> Embedded in Life An∎IXYS Company 19

| Address (Hex)    | Register Description                  | Mnemonic | Reset (Hex) | Page<br>No. |

|------------------|---------------------------------------|----------|-------------|-------------|

| GPIO Port B (co  | nt'd)                                 |          |             |             |

| FD6              | Port B Input Data                     | PBIN     | XX          | <u>43</u>   |

| FD7              | Port B Output Data                    | PBOUT    | 00          | <u>43</u>   |

| GPIO Port C      |                                       |          |             |             |

| FD8              | Port C Address                        | PCADDR   | 00          | <u>40</u>   |

| FD9              | Port C Control                        | PCCTL    | 00          | <u>42</u>   |

| FDA              | Port C Input Data                     | PCIN     | XX          | <u>43</u>   |

| FDB              | Port C Output Data                    | PCOUT    | 00          | <u>43</u>   |

| FDC-FEF          | Reserved                              |          | XX          |             |

| Watchdog Time    | r (WDT)                               |          |             |             |

| FF0              | Reset Status                          | RSTSTAT  | XX          | <u>94</u>   |

|                  | Watchdog Timer Control                | WDTCTL   | XX          | <u>94</u>   |

| FF1              | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | <u>95</u>   |

| FF2              | Watchdog Timer Reload High Byte       | WDTH     | FF          | <u>95</u>   |

| FF3              | Watchdog Timer Reload Low Byte        | WDTL     | FF          | <u>95</u>   |

| FF4–FF5          | Reserved                              | _        | XX          |             |

| Trim Bit Control | l                                     |          |             |             |

| FF6              | Trim Bit Address                      | TRMADR   | 00          | 148         |

| FF7              | Trim Data                             | TRMDR    | XX          | <u>149</u>  |

| Flash Memory C   | Controller                            |          |             |             |

| FF8              | Flash Control                         | FCTL     | 00          | 141         |

| FF8              | Flash Status                          | FSTAT    | 00          | 142         |

| FF9              | Flash Page Select                     | FPS      | 00          | <u>143</u>  |

|                  | Flash Sector Protect                  | FPROT    | 00          | <u>144</u>  |

| FFA              | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>145</u>  |

| FFB              | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>145</u>  |

## Table 8. Register File Address Map (Continued)

Note: XX=Undefined.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see **the** <u>Port A–C Control Registers</u> **section on page 42**), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overrightarrow{\text{RESET}}$  pin Low. The  $\overrightarrow{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

## **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control Register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) Register is set.

# **Stop Mode Recovery**

The device enters into STOP Mode when eZ8 CPU executes a STOP instruction. For more details about STOP Mode, see **the** Low-Power Modes **section on page 30**. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control Register (WDTCTL) and the Oscillator Control Register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

bedded in Life

40

PC[2:0]. All other signal pins are 5V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see the <u>Oscillator Control Register Definitions</u> section on page 171) such that the external oscillator is selected as the system clock. For 8-pin devices, use PA1 instead of PB3.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see the <u>Interrupt Controller</u> chapter on page 54.

# **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 18 lists these port registers. Use the Port A–D Address and Control registers together to provide access to subregisters for port configuration and control.

| Port Register<br>Mnemonic    | Port Register Name                                           |

|------------------------------|--------------------------------------------------------------|

| P <i>x</i> ADDR              | Port A–C Address Register (Selects subregisters).            |

| P <i>x</i> CTL               | Port A-C Control Register (Provides access to subregisters). |

| PxIN                         | Port A–C Input Data Register.                                |

| P <i>x</i> OUT               | Port A–C Output Data Register.                               |

| Port Subregister<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                | Data Direction.                                              |

| P <i>x</i> AF                | Alternate Function.                                          |

| P <i>x</i> OC                | Output Control (Open-Drain).                                 |

|                              |                                                              |

Table 18. GPIO Port Registers and Subregisters

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

| -        | 0004H                               | Watchdog Timer (see the Watchdog Timer section on page 91)                 |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          | 0036H                               | Port C Pin 0, both input edges                                             |

| Lowest   | 0038H                               | Reserved                                                                   |

## Table 35. Trap and Interrupt Vectors in Order of Priority

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CONTINUOUS Mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS Mode. After the first timer reload in CONTINUOUS Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

In CONTINUOUS Mode, the system clock always provides the timer input. The timer period is computed via the following equation:

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT Mode equation to determine the first time-out period.

#### **COUNTER Mode**

In COUNTER Mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER Mode, the prescaler is disabled.

**Caution:** The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.

Upon reaching the reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is

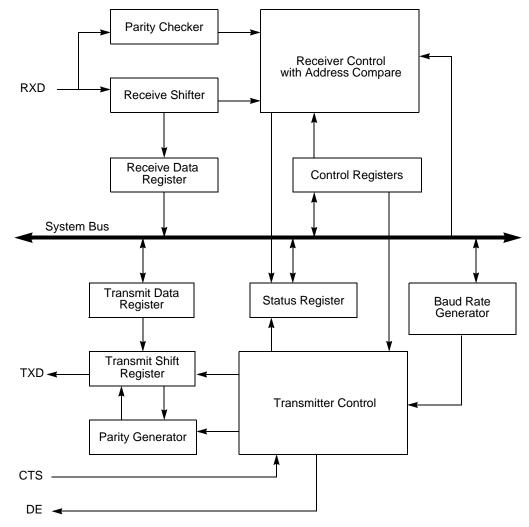

# Operation

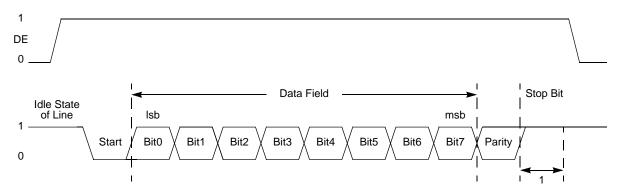

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

00

105

scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

## **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data Register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

Figure 14. UART Driver Enable Signal Timing (shown with 1 Stop Bit and Parity)

The Driver Enable to Start bit setup time is calculated as follows:

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

edded in Life

IXYS Company

119

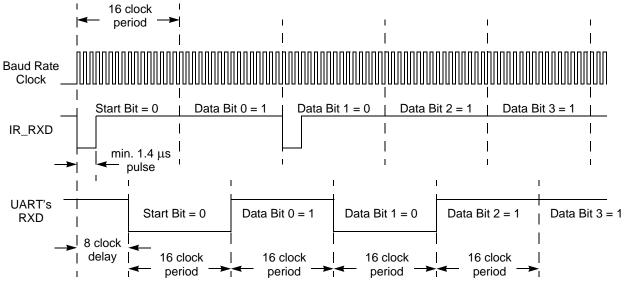

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the infrared endec and passed to the UART. The UART's baud rate clock is used by the infrared endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the infrared endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

## **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0MHz to ensure proper reception of the 1.4µs minimum width pulses allowed by the IrDA standard.

## **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens.

#### ilog<sup>\*</sup> Embedded in Life An IXYS Company 133

# **Comparator Control Register Definition**

The Comparator Control Register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

| Bit             | 7                                                                                                                                                                                                                                                          | 6                                                | 5             | 4             | 3             | 2           | 1                   | 0       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|---------------|---------------|-------------|---------------------|---------|

| Field           | INPSEL                                                                                                                                                                                                                                                     | INNSEL                                           |               | REFLVL Reserv |               |             |                     |         |

| RESET           | 0                                                                                                                                                                                                                                                          | 0                                                | 0             | 1             | 0             | 1           | 0                   | 0       |

| R/W             | R/W                                                                                                                                                                                                                                                        | R/W                                              | R/W           | R/W           | R/W           | R/W         | R/W                 | R/W     |

| Address         | F90H                                                                                                                                                                                                                                                       |                                                  |               |               |               |             |                     |         |

| Bit             | Descriptio                                                                                                                                                                                                                                                 | n                                                |               |               |               |             |                     |         |

| [7]<br>INPSEL   | 0 = GPIO p                                                                                                                                                                                                                                                 | ect for Posi<br>in used as p<br>ature sensor     | ositive com   |               |               |             |                     |         |

| [6]<br>INNSEL   | 0 = internal                                                                                                                                                                                                                                               | ect for Nega<br>reference d<br>reference e       | isabled, GP   |               |               |             | <sup>-</sup> input. |         |

| [5:2]<br>REFLVL | $\begin{array}{l} 0000 = 0.0^{\circ}\\ 0001 = 0.2^{\circ}\\ 0010 = 0.4^{\circ}\\ 0011 = 0.6^{\circ}\\ 0100 = 0.8^{\circ}\\ 0101 = 1.0^{\circ}\\ 0110 = 1.2^{\circ}\\ 0111 = 1.4^{\circ}\\ 1000 = 1.6^{\circ}\\ 1001 = 1.8^{\circ}\\ 1010-1111 \end{array}$ | V.<br>V.<br>V.<br>V.<br>V (Default).<br>V.<br>V. |               |               | C voltage ref | ference.    |                     |         |

| [1:0]           | Reserved<br>These bits a<br>read.                                                                                                                                                                                                                          | are reserved                                     | l; R/W bits n | nust be prog  | rammed to     | 00 during w | rites and to (      | 00 when |

ilog<sup>®</sup>

143

# Flash Status Register

The Flash Status Register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Bit     | 7          | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|---------|------------|-------|-------|---|---|---|---|---|

| Field   | Rese       | erved | FSTAT |   |   |   |   |   |

| RESET   | 0          | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W     | R          | R     | R     | R | R | R | R | R |

| Address |            | FF8H  |       |   |   |   |   |   |

| Bit     | Descriptio | n     |       |   |   |   |   |   |

| Table 82 | . Flash | Status | Register | (FSTAT) |

|----------|---------|--------|----------|---------|

|----------|---------|--------|----------|---------|

| Bit            | Description                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]          | <b>Reserved</b><br>These bits are reserved and must be programmed to 0 when read.                                                                                                                                                                                                                                                                                           |

| [5:0]<br>FSTAT | Flash Controller Status000000 = Flash Controller locked.000001 = First unlock command received (73H written).000010 = Second unlock command received (8CH written).000011 = Flash Controller unlocked.000100 = Sector protect register selected.001xxx = Program operation in progress.010xxx = Page erase operation in progress.100xxx = Mass erase operation in progress. |

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

> ilog Embedded in Life An TIXYS Company 144

#### Table 83. Flash Page Select Register (FPS)

| Bit     | 7       | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------|------|-----|-----|-----|-----|-----|-----|

| Field   | INFO_EN | PAGE |     |     |     |     |     |     |

| RESET   | 0       | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |         | FF9H |     |     |     |     |     |     |

#### Bit Description

## [7] Information Area Enable

INFO\_EN 0 = Information Area us not selected.

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### [6:0] Page Select

PAGE This 7-bit field identifies the Flash memory page for Page Erase and page unlocking.

• Program Memory Address[15:9] = PAGE[6:0].

• For Z8F04x3 devices, the upper 4 bits must always be 0.

• For Z8F02x3 devices, the upper 5 bits must always be 0.

• For Z8F01x3 devices, the upper 6 bits must always be 0.

nbedded in Life

148

These serial numbers are stored in the Flash information page (for more details, see the <u>Reading the Flash Information Page</u> section on page 148 and the <u>Serialization Data</u> section on page 154) and are unaffected by mass erasure of the device's Flash memory.

## **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

The randomized lot identifier is a 32-byte binary value, stored in the flash information page (for more details, see the <u>Reading the Flash Information Page</u> section on page 148 and the <u>Randomized Lot Identifier</u> section on page 154) and is unaffected by mass erasure of the device's flash memory.

# **Reading the Flash Information Page**

The following code example shows how to read data from the Flash Information Area.

; get value at info address 60 (FE60h) ldx FPS, #%80 ; enable access to flash info page ld R0, #%FE ld R1, #%60 ldc R2, @RR0 ; R2 now contains the calibration value

# **Flash Option Bit Control Register Definitions**

This section briefly describes the features of the Trim Bit Address and Data registers.

## **Trim Bit Address Register**

The Trim Bit Address (TRMADR) Register contains the target address for an access to the trim option bits.

| Bit     | 7                                     | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|---------------------------------------|------|-----|-----|-----|-----|-----|-----|

| Field   | TRMADR: Trim Bit Address (00H to 1FH) |      |     |     |     |     |     |     |

| RESET   | 0                                     | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W     | R/W                                   | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| Address |                                       | FF6H |     |     |     |     |     |     |

Table 87. Trim Bit Address Register (TRMADR)

150

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [3]<br>VBO_AO | <ul> <li>Voltage Brown-Out Protection Always ON</li> <li>0 = Voltage Brown-Out Protection can be disabled in STOP Mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see the <u>Power Control Register 0</u> section on page 31).</li> <li>1 = Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul> |  |  |  |  |  |

| [2]<br>FRP    | <ul> <li>Flash Read Protect</li> <li>0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.</li> <li>1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                         |  |  |  |  |  |

| [1]           | <b>Reserved</b><br>This bit is reserved and must be programmed to 1.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| [0]<br>FWP    | <ul> <li>Flash Write Protect</li> <li>This Option Bit provides Flash Program Memory protection:</li> <li>0 = Programming and erasure disabled for all of Flash Program Memory. Programming,<br/>Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available<br/>using the On-Chip Debugger.</li> <li>1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program mem-<br/>ory.</li> </ul>                                      |  |  |  |  |  |

## Table 90. Flash Options Bits at Program Memory Address 0001H

| Bit                                             | 7                    | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|-------------------------------------------------|----------------------|-----|-----|--------|----------|-----|-----|-----|

| Field                                           | Reserved             |     |     | XTLDIS | Reserved |     |     |     |

| RESET                                           | U                    | U   | U   | U      | U        | U   | U   | U   |

| R/W                                             | R/W                  | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| Address                                         | Program Memory 0001H |     |     |        |          |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |     |     |        |          |     |     |     |

nbedded in Life

170

ages to the Oscillator Control Desistor can actually stor the ship by

**Caution:** Unintentional accesses to the Oscillator Control Register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

## **OSC Control Register Unlocking/Locking**

To write to the Oscillator Control Register, unlock it by making two writes to the OSC-CTL Register with the values E7H followed by 18H. A third write to the OSCCTL Register changes the value of the actual register and returns the register to a locked state. Any other sequence of Oscillator Control Register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the Oscillator Control Register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

# **Clock Failure Detection and Recovery**

Should an oscillator or timer fail, there are methods of recovery, as this section describes.

## **Primary Oscillator Failure**

Z8 Encore! XP F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switch-over is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the the <u>Watchdog Timer</u> section on page 91.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below  $1 \text{ kHz} \pm 50\%$ . If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these

I

> Embedded in Life An IXYS Company 181

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| AND      | dst, src | Logical AND                                    |

| ANDX     | dst, src | Logical AND using Extended Addressing          |

| СОМ      | dst      | Complement                                     |

| OR       | dst, src | Logical OR                                     |

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### Table 115. Logical Instructions

## Table 116. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |  |  |

|----------|-----------------|-------------------------------|--|--|

| BRK      | _               | On-Chip Debugger Break        |  |  |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |  |  |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |  |  |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |  |  |

| CALL     | dst             | Call Procedure                |  |  |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |  |  |

| IRET     | —               | Interrupt Return              |  |  |

| JP       | dst             | Jump                          |  |  |

| JP cc    | dst             | Jump Conditional              |  |  |

| JR       | DA              | Jump Relative                 |  |  |

| JR cc    | DA              | Jump Relative Conditional     |  |  |

| RET      | _               | Return                        |  |  |

| TRAP     | vector          | Software Trap                 |  |  |

#### Table 117. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction               |

|----------|----------|---------------------------|

| BSWAP    | dst      | Bit Swap                  |

| RL       | dst      | Rotate Left               |

| RLC      | dst      | Rotate Left through Carry |

# Embedded in Life An IXYS Company

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the F0823 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 120 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                                       | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                                  | -40     | +105    | °C    |       |

| Storage temperature                                             | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>              | -0.3    | +5.5    | V     | 1     |

|                                                                 | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$                | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin             | -5      | +5      | μA    |       |

| Maximum output current from active output pin                   | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0°C to 70°C                   |         |         |       |       |

| Total power dissipation                                         |         | 220     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 430     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0°C to 70°C                  |         |         |       |       |

| Total power dissipation                                         |         | 450     | mW    |       |

| Maximum current into V <sub>DD</sub> or out of V <sub>SS</sub>  |         | 125     | mA    |       |

| Natas, Operating temperature is enacified in DC Characteristics |         |         |       |       |

| Table 1 | 20. Ab | solute N | laximum | Ratings |

|---------|--------|----------|---------|---------|

|---------|--------|----------|---------|---------|

Notes: Operating temperature is specified in DC Characteristics.

This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

2. This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# Embedded in Life An IXYS Company 197

# **DC Characteristics**

Table 121 lists the DC characteristics of the Z8 Encore! XP F0823 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  |                              |                     | -40°C to -<br>otherwise | ⊦105°C<br>specified) |       |                                                                                                                                                                |

|------------------|------------------------------|---------------------|-------------------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                 | Maximum              | Units | Conditions                                                                                                                                                     |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                       | 3.6                  | V     |                                                                                                                                                                |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                       | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                                |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                       | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all sig-<br>nal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                       | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when pro-<br>grammable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | -                       | 0.4                  | V     | I <sub>OL</sub> = 2mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                                   |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | -                       | -                    | V     | $I_{OH} = -2mA; V_{DD} = 3.0V$<br>High Output Drive disabled.                                                                                                  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                       | 0.6                  | V     | $I_{OL}$ = 20mA; $V_{DD}$ = 3.3 V<br>High Output Drive enabled.                                                                                                |

| V <sub>OH2</sub> | High Level Output<br>Voltage | 2.4                 | -                       | -                    | V     | I <sub>OH</sub> = -20mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                                 |

| I <sub>IH</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.002          | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>IL</sub>  | Input Leakage Cur-<br>rent   | -                   | <u>+</u> 0.007          | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V$                                                                                                                          |

| I <sub>TL</sub>  | Tristate Leakage<br>Current  | -                   | -                       | <u>+</u> 5           | μA    |                                                                                                                                                                |

| Table 121. | DC | Characteristics |

|------------|----|-----------------|

|            |    | •               |

Notes:

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

230

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <u>http://support.zilog.com</u>.

To learn more about this product, find additional documentation, or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://</u><u>zilog.com/kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.